JP6239975B2 - 固体撮像装置及びそれを用いた撮像システム - Google Patents

固体撮像装置及びそれを用いた撮像システム Download PDFInfo

- Publication number

- JP6239975B2 JP6239975B2 JP2013272655A JP2013272655A JP6239975B2 JP 6239975 B2 JP6239975 B2 JP 6239975B2 JP 2013272655 A JP2013272655 A JP 2013272655A JP 2013272655 A JP2013272655 A JP 2013272655A JP 6239975 B2 JP6239975 B2 JP 6239975B2

- Authority

- JP

- Japan

- Prior art keywords

- pixel

- output

- photodiodes

- signal

- pixels

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/10—Circuitry of solid-state image sensors [SSIS]; Control thereof for transforming different wavelengths into image signals

- H04N25/11—Arrangement of colour filter arrays [CFA]; Filter mosaics

- H04N25/13—Arrangement of colour filter arrays [CFA]; Filter mosaics characterised by the spectral characteristics of the filter elements

- H04N25/134—Arrangement of colour filter arrays [CFA]; Filter mosaics characterised by the spectral characteristics of the filter elements based on three different wavelength filter elements

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/40—Extracting pixel data from image sensors by controlling scanning circuits, e.g. by modifying the number of pixels sampled or to be sampled

- H04N25/46—Extracting pixel data from image sensors by controlling scanning circuits, e.g. by modifying the number of pixels sampled or to be sampled by combining or binning pixels

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/77—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components

- H04N25/778—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components comprising amplifiers shared between a plurality of pixels, i.e. at least one part of the amplifier must be on the sensor array itself

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/78—Readout circuits for addressed sensors, e.g. output amplifiers or A/D converters

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Physics & Mathematics (AREA)

- Spectroscopy & Molecular Physics (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

- Color Television Image Signal Generators (AREA)

Description

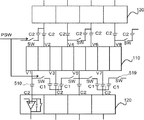

図1は本発明の第1の実施形態に係る固体撮像装置100の概略構成を示す図である。本実施形態に係る固体撮像装置100は例えばCMOSイメージセンサであり、被写体像を示す入射光を光電変換し、光電変換により得られた電気信号をデジタルデータとして外部に出力することで被写体の撮像を行う装置である。固体撮像装置100は、画素アレイ110、増幅回路120、A/D変換器130、垂直走査回路140、水平走査回路150、ランプ信号生成部170、カウンタ180、信号処理部190、及びタイミング制御部195を備える。

R(33)=(1列目の1、3、5行の加算)+2×(3列目の1、3、5行の加算)+

(5列目の1、3、5行の加算)

={B11+(A31+B31)+A51}+2×{B13+(A33+B33)+A53}+

{B15+(A35+B35)+A55}

Gr(35)=(4列目の1、3、5行の加算)+(6列目の1、3、5行の加算)

={B14+(A34+B34)+A54}+{B16+(A36+B36)+A56}

Gb(53)=(1列目の4、6行の加算)+2×(3列目の4、6行の加算)+(5列

目の4、6行の加算)

={(A41+B41)+(A61+B61)}+2×{(A43+B43)+(A63+

B63)}+{(A45+B45)+(A65+B65)}

B(55)=(4列目の4、6行の加算)+(6列目の4、6行の加算)

={(A44+B44)+(A64+B64)}+{(A46+B46)+(A66+B66)

}

本発明の第2の実施形態に係る固体撮像装置を以下に詳細に述べる。本実施形態は、第1の実施形態に対して画素の構成と列ごとに配置されている増幅回路の構成が異なるため、これらについてのみ詳細に説明する。

図11は、本発明の第1又は第2の実施形態に係る固体撮像装置を用いた撮像システムの構成を示す図である。撮像システム800は、固体撮像装置100、光学部810、記録・通信部840、システム制御部860、及び再生・表示部870を備える。固体撮像装置100は、上述のとおり、画素アレイ110、信号処理部190、タイミング制御部195を備える。

111 画素

119 列方向加算平均スイッチ

200 色フィルタ

201 分割画素

202 マイクロレンズ

510 入力容量

519 行方向加算平均スイッチ

Claims (11)

- マトリクス状に配列された複数の画素を有する画素アレイであって、各画素は、1つの色の色フィルタを有し、前記色フィルタを通過する入射光を各々が受光する複数のフォトダイオードを含む、画素アレイと、

加算回路とを備え、

前記複数の画素は、第1の画素、第2の画素、及び第3の画素を含み、

前記第1の画素、前記第2の画素、及び前記第3の画素の各々は、第1の色の色フィルタを有し、

前記加算回路は、(i)前記第1の画素の複数のフォトダイオードの一部のみの出力に基づく信号と、(ii)前記第2の画素の複数のフォトダイオードの出力に基づく信号と、(iii)前記第3の画素の複数のフォトダイオードの一部のみの出力に基づく信号との加算を行う、固体撮像装置。 - 前記複数の画素の各々は、マイクロレンズを有し、

前記第1の画素の前記複数のフォトダイオードの前記一部と、前記マイクロレンズとの相対位置が、前記第3の画素の前記複数のフォトダイオードの前記一部と、前記マイクロレンズとの相対位置と異なる、請求項1に記載の固体撮像装置。 - 前記複数の画素の色配列はベイヤ配列である、請求項1に記載の固体撮像装置。

- 前記加算回路は、前記画素アレイの1つの列において、複数の行の画素から出力される信号を加算する第1の加算回路と、前記画素アレイの1つの行において、複数の列の画素から出力される信号を加算平均する第2の加算回路とを含む、請求項3に記載の固体撮像装置。

- 前記第1の画素、前記第2の画素、及び前記第3の画素は、前記画素アレイの1つの列に配され、

第1の数が、前記第1の画素の前記複数のフォトダイオードの前記一部のみの前記出力に基づく前記信号を出力するために用いられるフォトダイオードの個数であり、

第2の数が、前記第2の画素の前記複数のフォトダイオードの前記出力に基づく前記信号を出力するために用いられるフォトダイオードの個数であり、

第3の数が、前記第3の画素の前記複数のフォトダイオードの前記一部のみの前記出力に基づく前記信号を出力するために用いられるフォトダイオードの個数であるとき、

前記第1の数と、前記第2の数と、前記第3の数との比が1:2:1である、請求項1に記載の固体撮像装置。 - 前記複数の画素は、前記画素アレイの前記1つの列に配された第4の画素及び第5の画素をさらに含み、

前記第4の画素の色フィルタの色と前記第5の画素の色フィルタの色は、前記第1の色とは異なる第2の色であり、

前記加算回路は、(iv)前記第4の画素の複数のフォトダイオードの一部のみの出力に基づく信号、及び(v)前記第5の画素の複数のフォトダイオードの一部のみの出力に基づく信号の加算を行い、

第4の数が、前記第4の画素の前記複数のフォトダイオードの前記一部のみの前記出力に基づく前記信号を出力するために用いられるフォトダイオードの個数であり、

第5の数が、前記第5の画素の前記複数のフォトダイオードの前記一部のみの前記出力に基づく前記信号を出力するために用いられるフォトダイオードの個数であるとき、

前記第4の数と前記第5の数の比が1:1である、請求項5に記載の固体撮像装置。 - 前記第1の画素、前記第2の画素、及び前記第3の画素は、前記画素アレイの1つの行に配され、

第1の数が、前記第1の画素の前記複数のフォトダイオードの前記一部のみの前記出力に基づく前記信号を出力するために用いられるフォトダイオードの個数であり、

第2の数が、前記第2の画素の前記複数のフォトダイオードの前記出力に基づく前記信号を出力するために用いられるフォトダイオードの個数であり、

第3の数が、前記第3の画素の前記複数のフォトダイオードの前記一部のみの前記出力に基づく前記信号を出力するために用いられるフォトダイオードの個数であるとき、

前記第1の数と、前記第2の数と、前記第3の数との比が1:2:1である、請求項1に記載の固体撮像装置。 - 前記複数の画素は、前記画素アレイの前記1つの行に配された第4の画素及び第5の画素をさらに含み、

前記第4の画素の色フィルタの色と前記第5の画素の色フィルタの色は、前記第1の色とは異なる第2の色であり、

前記加算回路は、(iv)前記第4の画素の複数のフォトダイオードの一部のみの出力に基づく信号、及び(v)前記第5の画素の複数のフォトダイオードの一部のみの出力に基づく信号の加算を行い、

第4の数が、前記第4の画素の前記複数のフォトダイオードの前記一部のみの前記出力に基づく前記信号を出力するために用いられるフォトダイオードの個数であり、

第5の数が、前記第5の画素の前記複数のフォトダイオードの前記一部のみの前記出力に基づく前記信号を出力するために用いられるフォトダイオードの個数であるとき、

前記第4の数と前記第5の数の比が1:1である、請求項7に記載の固体撮像装置。 - 前記第2の画素の位置は、前記第1の画素、前記第2の画素、及び前記第3の画素の各々から出力される信号の加算の重心位置である、請求項8に記載の固体撮像装置。

- 前記複数の画素の各々は、マイクロレンズを有し、

前記複数の画素の各々の前記複数のフォトダイオードは、前記マイクロレンズと前記色フィルタとをこの順に通過する入射光を受光する、請求項1に記載の固体撮像装置。 - 請求項1〜10のいずれか1項に記載の固体撮像装置と、

前記複数の画素に像を形成する光学系と、

前記固体撮像装置から出力された信号を処理して画像データを生成する信号処理部とを備える、撮像システム。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013272655A JP6239975B2 (ja) | 2013-12-27 | 2013-12-27 | 固体撮像装置及びそれを用いた撮像システム |

| US14/564,506 US9438839B2 (en) | 2013-12-27 | 2014-12-09 | Solid state imaging apparatus and imaging system using the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013272655A JP6239975B2 (ja) | 2013-12-27 | 2013-12-27 | 固体撮像装置及びそれを用いた撮像システム |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015128215A JP2015128215A (ja) | 2015-07-09 |

| JP2015128215A5 JP2015128215A5 (ja) | 2017-02-09 |

| JP6239975B2 true JP6239975B2 (ja) | 2017-11-29 |

Family

ID=53483412

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013272655A Active JP6239975B2 (ja) | 2013-12-27 | 2013-12-27 | 固体撮像装置及びそれを用いた撮像システム |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9438839B2 (ja) |

| JP (1) | JP6239975B2 (ja) |

Families Citing this family (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6234054B2 (ja) * | 2013-04-25 | 2017-11-22 | キヤノン株式会社 | 撮像装置および撮像装置の制御方法 |

| JP6176062B2 (ja) * | 2013-11-06 | 2017-08-09 | ソニー株式会社 | 固体撮像装置およびその駆動方法、並びに電子機器 |

| US9979916B2 (en) | 2014-11-21 | 2018-05-22 | Canon Kabushiki Kaisha | Imaging apparatus and imaging system |

| JP6218799B2 (ja) * | 2015-01-05 | 2017-10-25 | キヤノン株式会社 | 撮像素子及び撮像装置 |

| KR102219941B1 (ko) | 2015-03-10 | 2021-02-25 | 삼성전자주식회사 | 이미지 센서, 이를 포함하는 데이터 처리 시스템, 및 모바일 컴퓨팅 장치 |

| KR102382183B1 (ko) * | 2015-05-20 | 2022-04-01 | 삼성전자주식회사 | 신호대 잡음비 및 랜덤 노이즈를 개선하는 이미지 센서 및 이를 포함하는 이미지 처리 시스템 |

| US10313612B2 (en) | 2015-12-18 | 2019-06-04 | Guangdong Oppo Mobile Telecommunications Corp., Ltd. | Image sensor, control method, and electronic device |

| JP6711634B2 (ja) | 2016-02-16 | 2020-06-17 | キヤノン株式会社 | 撮像装置、撮像装置の駆動方法、及び撮像システム |

| JP6727856B2 (ja) * | 2016-03-02 | 2020-07-22 | キヤノン株式会社 | 撮像装置およびその制御方法 |

| JP2017183786A (ja) * | 2016-03-28 | 2017-10-05 | ルネサスエレクトロニクス株式会社 | 撮像装置、カメラシステム及び撮像方法 |

| JP6765860B2 (ja) * | 2016-06-01 | 2020-10-07 | キヤノン株式会社 | 撮像素子、撮像装置、および撮像信号処理方法 |

| WO2018012316A1 (ja) * | 2016-07-15 | 2018-01-18 | ソニーセミコンダクタソリューションズ株式会社 | 固体撮像素子および固体撮像素子の動作方法、撮像装置、並びに電子機器 |

| US10270987B2 (en) * | 2016-09-08 | 2019-04-23 | Gvbb Holdings S.A.R.L. | System and methods for dynamic pixel management of a cross pixel interconnected CMOS image sensor |

| JP6910009B2 (ja) | 2017-02-03 | 2021-07-28 | パナソニックIpマネジメント株式会社 | 撮像装置およびカメラシステム |

| JP7067907B2 (ja) * | 2017-12-01 | 2022-05-16 | キヤノン株式会社 | 固体撮像装置及び信号処理装置 |

| JP7082503B2 (ja) * | 2018-03-08 | 2022-06-08 | 浜松ホトニクス株式会社 | 光検出装置及び光検出方法 |

| JP7089390B2 (ja) | 2018-03-30 | 2022-06-22 | キヤノン株式会社 | 光電変換装置及びその駆動方法 |

| JP7280691B2 (ja) * | 2018-11-27 | 2023-05-24 | キヤノン株式会社 | 撮像素子およびその制御方法、及び撮像装置 |

| JP7227777B2 (ja) * | 2019-02-04 | 2023-02-22 | キヤノン株式会社 | 撮像装置 |

| JP7040509B2 (ja) * | 2019-11-28 | 2022-03-23 | 株式会社ニコン | 撮像素子及び撮像装置 |

| JP7383788B2 (ja) * | 2020-02-28 | 2023-11-20 | 富士フイルム株式会社 | 撮像装置及び撮像センサ |

| JP7247975B2 (ja) * | 2020-07-06 | 2023-03-29 | 株式会社ニコン | 撮像素子及び撮像装置 |

Family Cites Families (46)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TW421962B (en) | 1997-09-29 | 2001-02-11 | Canon Kk | Image sensing device using mos type image sensing elements |

| JPH11261046A (ja) | 1998-03-12 | 1999-09-24 | Canon Inc | 固体撮像装置 |

| JP3571909B2 (ja) | 1998-03-19 | 2004-09-29 | キヤノン株式会社 | 固体撮像装置及びその製造方法 |

| JP3728260B2 (ja) | 2002-02-27 | 2005-12-21 | キヤノン株式会社 | 光電変換装置及び撮像装置 |

| EP1341377B1 (en) | 2002-02-27 | 2018-04-11 | Canon Kabushiki Kaisha | Signal processing device for image pickup apparatus |

| JP4514188B2 (ja) | 2003-11-10 | 2010-07-28 | キヤノン株式会社 | 光電変換装置及び撮像装置 |

| JP4508619B2 (ja) | 2003-12-03 | 2010-07-21 | キヤノン株式会社 | 固体撮像装置の製造方法 |

| JP3793202B2 (ja) | 2004-02-02 | 2006-07-05 | キヤノン株式会社 | 固体撮像装置 |

| JP3890333B2 (ja) | 2004-02-06 | 2007-03-07 | キヤノン株式会社 | 固体撮像装置 |

| JP4067054B2 (ja) | 2004-02-13 | 2008-03-26 | キヤノン株式会社 | 固体撮像装置および撮像システム |

| JP5089017B2 (ja) | 2004-09-01 | 2012-12-05 | キヤノン株式会社 | 固体撮像装置及び固体撮像システム |

| JP4971586B2 (ja) | 2004-09-01 | 2012-07-11 | キヤノン株式会社 | 固体撮像装置 |

| JP4804254B2 (ja) | 2006-07-26 | 2011-11-02 | キヤノン株式会社 | 光電変換装置及び撮像装置 |

| JP5123601B2 (ja) | 2006-08-31 | 2013-01-23 | キヤノン株式会社 | 光電変換装置 |

| JP2008098971A (ja) * | 2006-10-12 | 2008-04-24 | Matsushita Electric Ind Co Ltd | 固体撮像装置 |

| JP4110193B1 (ja) | 2007-05-02 | 2008-07-02 | キヤノン株式会社 | 固体撮像装置および撮像システム |

| JP4941131B2 (ja) * | 2007-06-30 | 2012-05-30 | 株式会社ニコン | 固体撮像素子及び電子カメラ |

| JP5026951B2 (ja) * | 2007-12-26 | 2012-09-19 | オリンパスイメージング株式会社 | 撮像素子の駆動装置、撮像素子の駆動方法、撮像装置、及び撮像素子 |

| JP5268389B2 (ja) | 2008-02-28 | 2013-08-21 | キヤノン株式会社 | 固体撮像装置、その駆動方法及び撮像システム |

| JP5178266B2 (ja) | 2008-03-19 | 2013-04-10 | キヤノン株式会社 | 固体撮像装置 |

| JP5094498B2 (ja) | 2008-03-27 | 2012-12-12 | キヤノン株式会社 | 固体撮像装置及び撮像システム |

| JP5279352B2 (ja) | 2008-06-06 | 2013-09-04 | キヤノン株式会社 | 固体撮像装置 |

| JP5274166B2 (ja) | 2008-09-10 | 2013-08-28 | キヤノン株式会社 | 光電変換装置及び撮像システム |

| JP4891308B2 (ja) | 2008-12-17 | 2012-03-07 | キヤノン株式会社 | 固体撮像装置及び固体撮像装置を用いた撮像システム |

| US8913166B2 (en) * | 2009-01-21 | 2014-12-16 | Canon Kabushiki Kaisha | Solid-state imaging apparatus |

| JP5511220B2 (ja) | 2009-05-19 | 2014-06-04 | キヤノン株式会社 | 固体撮像装置 |

| GB2486428A (en) * | 2010-12-14 | 2012-06-20 | St Microelectronics Res & Dev | Image sensor utilising analogue binning with ADC architecture |

| JP5791338B2 (ja) | 2011-04-07 | 2015-10-07 | キヤノン株式会社 | 固体撮像装置及びその駆動方法 |

| EP2717561B1 (en) * | 2011-05-24 | 2019-03-27 | Sony Semiconductor Solutions Corporation | Solid-state imaging element and camera system |

| JP5762199B2 (ja) | 2011-07-28 | 2015-08-12 | キヤノン株式会社 | 固体撮像装置 |

| JP2013066140A (ja) | 2011-08-31 | 2013-04-11 | Sony Corp | 撮像装置、および信号処理方法、並びにプログラム |

| JP5901186B2 (ja) | 2011-09-05 | 2016-04-06 | キヤノン株式会社 | 固体撮像装置及びその駆動方法 |

| JP5858695B2 (ja) | 2011-09-08 | 2016-02-10 | キヤノン株式会社 | 固体撮像装置及び固体撮像装置の駆動方法 |

| JP5806566B2 (ja) | 2011-09-15 | 2015-11-10 | キヤノン株式会社 | A/d変換器および固体撮像装置 |

| JP5935274B2 (ja) * | 2011-09-22 | 2016-06-15 | ソニー株式会社 | 固体撮像装置、固体撮像装置の制御方法および固体撮像装置の制御プログラム |

| JP5901212B2 (ja) | 2011-10-07 | 2016-04-06 | キヤノン株式会社 | 光電変換システム |

| JP5484422B2 (ja) | 2011-10-07 | 2014-05-07 | キヤノン株式会社 | 固体撮像装置 |

| JP5930651B2 (ja) | 2011-10-07 | 2016-06-08 | キヤノン株式会社 | 固体撮像装置 |

| WO2013069445A1 (ja) * | 2011-11-11 | 2013-05-16 | 富士フイルム株式会社 | 立体撮像装置及び画像処理方法 |

| JP5979849B2 (ja) * | 2011-11-21 | 2016-08-31 | キヤノン株式会社 | 撮像素子及び撮像装置 |

| JP5967955B2 (ja) * | 2012-01-31 | 2016-08-10 | キヤノン株式会社 | 光電変換装置および撮像システム |

| JP5893573B2 (ja) | 2012-02-09 | 2016-03-23 | キヤノン株式会社 | 固体撮像装置 |

| JP6319946B2 (ja) | 2013-04-18 | 2018-05-09 | キヤノン株式会社 | 固体撮像装置及び撮像システム |

| JP6100074B2 (ja) | 2013-04-25 | 2017-03-22 | キヤノン株式会社 | 光電変換装置及び撮像システム |

| JP6274788B2 (ja) * | 2013-08-28 | 2018-02-07 | キヤノン株式会社 | 撮像装置、撮像システム及び撮像装置の駆動方法 |

| JP5886806B2 (ja) | 2013-09-17 | 2016-03-16 | キヤノン株式会社 | 固体撮像装置 |

-

2013

- 2013-12-27 JP JP2013272655A patent/JP6239975B2/ja active Active

-

2014

- 2014-12-09 US US14/564,506 patent/US9438839B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2015128215A (ja) | 2015-07-09 |

| US20150189249A1 (en) | 2015-07-02 |

| US9438839B2 (en) | 2016-09-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6239975B2 (ja) | 固体撮像装置及びそれを用いた撮像システム | |

| JP4611296B2 (ja) | 電荷ビニング型イメージセンサ | |

| US8023018B2 (en) | Drive method for solid-state imaging device, solid-state imaging device, and imaging apparatus | |

| JP5546257B2 (ja) | 固体撮像装置 | |

| US8405750B2 (en) | Image sensors and image reconstruction methods for capturing high dynamic range images | |

| US8077232B2 (en) | Imaging device for adding signals including same color component | |

| KR101136222B1 (ko) | 촬상소자, 촬상소자의 구동장치, 촬상소자의 구동방법, 화상처리장치, 프로그램을 기록한 컴퓨터 판독 가능한 기록 매체 및 촬상장치 | |

| US9036052B2 (en) | Image pickup apparatus that uses pixels different in sensitivity, method of controlling the same, and storage medium | |

| US10477165B2 (en) | Solid-state imaging apparatus, driving method therefor, and imaging system | |

| JP2006253876A (ja) | 物理量分布検知装置および物理量分布検知装置の駆動方法 | |

| JP5895525B2 (ja) | 撮像素子 | |

| EP1569278A2 (en) | Amplifying solid-state image pickup device | |

| US8754971B2 (en) | Image sensing apparatus and image capturing system | |

| US20100245628A1 (en) | Imaging apparatus and imaging system | |

| JP2009272820A (ja) | 固体撮像装置 | |

| JP2017022624A (ja) | 撮像素子及びその駆動方法、及び撮像装置 | |

| US8582006B2 (en) | Pixel arrangement for extended dynamic range imaging | |

| JP3956875B2 (ja) | 固体撮像装置 | |

| JP2006148509A (ja) | 物理情報取得方法および物理情報取得装置並びに物理量分布検知の半導体装置 | |

| JP6700850B2 (ja) | 撮像素子の駆動制御回路 | |

| JP5511205B2 (ja) | 撮像装置及び撮像方法 | |

| JP2015173387A (ja) | 撮像素子、その駆動方法、およびプログラム | |

| JP2013239763A (ja) | 固体撮像素子及びこれを用いた撮像装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161226 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20161226 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170925 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20171005 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20171102 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6239975 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |