JP6077868B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP6077868B2 JP6077868B2 JP2013018105A JP2013018105A JP6077868B2 JP 6077868 B2 JP6077868 B2 JP 6077868B2 JP 2013018105 A JP2013018105 A JP 2013018105A JP 2013018105 A JP2013018105 A JP 2013018105A JP 6077868 B2 JP6077868 B2 JP 6077868B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- oxide

- insulating film

- oxide semiconductor

- metal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D99/00—Subject matter not provided for in other groups of this subclass

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6729—Thin-film transistors [TFT] characterised by the electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6729—Thin-film transistors [TFT] characterised by the electrodes

- H10D30/6737—Thin-film transistors [TFT] characterised by the electrodes characterised by the electrode materials

- H10D30/6739—Conductor-insulator-semiconductor electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/80—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials

-

- H10D64/011—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/60—Electrodes characterised by their materials

- H10D64/66—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes

- H10D64/665—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes the conductor comprising a layer of elemental metal contacting the insulator, e.g. tungsten or molybdenum

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/60—Electrodes characterised by their materials

- H10D64/66—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes

- H10D64/68—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator

- H10D64/691—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator comprising metallic compounds, e.g. metal oxides or metal silicates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/421—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer

- H10D86/423—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer comprising semiconductor materials not belonging to the Group IV, e.g. InGaZnO

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

-

- H10P14/2901—

-

- H10P14/3434—

-

- H10P14/6314—

-

- H10P14/69391—

-

- H10P30/202—

-

- H10P32/12—

-

- H10P32/17—

-

- H10P50/282—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B10/00—Static random access memory [SRAM] devices

- H10B10/12—Static random access memory [SRAM] devices comprising a MOSFET load element

- H10B10/125—Static random access memory [SRAM] devices comprising a MOSFET load element the MOSFET being a thin film transistor [TFT]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/05—Making the transistor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/70—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates the floating gate being an electrode shared by two or more components

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Thin Film Transistor (AREA)

- Semiconductor Memories (AREA)

- Chemical & Material Sciences (AREA)

- Materials Engineering (AREA)

- Formation Of Insulating Films (AREA)

- Health & Medical Sciences (AREA)

- Toxicology (AREA)

Description

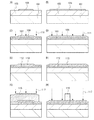

本実施の形態では、電気特性の優れたトランジスタの構造、及びそれを生産性高く作製する方法について、図1乃至図4を用いて説明する。

ハードマスクとして用いる絶縁膜は、スパッタリング法、CVD法、蒸着法等で絶縁膜を形成する。

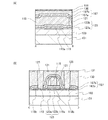

本実施の形態では、金属膜を酸化した金属酸化膜をゲート絶縁膜に用いたトランジスタ及びその作製方法について、図1乃至図5を用いて説明する。なお、実施の形態1と比較して、ゲート絶縁膜が、金属膜に酸素を導入し酸化した金属酸化膜のみである点が異なる。

本実施の形態では、金属膜を酸化した金属酸化膜をトランジスタの保護膜に用いたトランジスタ及びその作製方法について、図1乃至図3、及び図6を用いて説明する。

本実施の形態では、金属膜を酸化した金属酸化膜をトランジスタの保護膜に用いたトランジスタ及びその作製方法について、図1乃至図3、及び図8を用いて説明する。なお、実施の形態3と比較して、トランジスタの保護膜が、金属膜に酸素を導入し酸化した金属酸化膜のみである点が異なる。

本実施の形態では、酸化物半導体膜のソース領域及びドレイン領域を低抵抗化する方法について、図2、図3、及び図9を用いて説明する。なお、本実施の形態では、実施の形態1を用いて説明するが、適宜実施の形態2乃至実施の形態4に本実施の形態を適用することができる。

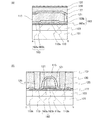

本実施の形態では、下部に第1の半導体材料を用いたトランジスタを有し、上部に第2の半導体材料を用いたトランジスタを有する半導体装置であって、第1の半導体材料を用いたトランジスタに半導体基板を用いた構造を、図10乃至図13を用いて説明する。

本実施の形態では、下部に第1の半導体材料を用いたトランジスタを有し、上部に第2の半導体材料を用いたトランジスタを有する半導体装置であって、第1の半導体材料を用いたトランジスタにSOI基板を用いた構造を、図14を用いて説明する。すなわち実施の形態6において、第1の半導体材料を用いたトランジスタに半導体基板を用いているのに対して、本実施の形態ではSOI基板を用いている点において異なる。

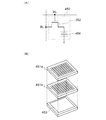

本実施の形態では、本明細書に示すトランジスタを使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置の一例を、図面を用いて説明する。なお、ここでは、半導体装置の一例として記憶装置を用いて説明する。

本実施の形態においては、実施の形態1乃至実施の形態7に示すトランジスタを使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置について、実施の形態8に示した構成と異なる構成について、図16及び図17を用いて説明を行う。なお、ここでは、半導体装置の一例として記憶装置を用いて説明する。

先の実施の形態で示した半導体装置の一例としては、中央演算処理装置、マイクロプロセッサ、マイクロコンピュータ、ランダムアクセスメモリ等の記憶装置、イメージセンサ、電気光学装置、発光表示装置、パワートランジスタ、コンバータ、サイリスタ等がある。また、該半導体装置をさまざまな電子機器に適用することができる。電子機器としては、例えば、表示装置、照明装置、パーソナルコンピュータ、ワードプロセッサ、画像再生装置、ポータブルCDプレーヤ、ラジオ、テープレコーダ、ヘッドホンステレオ、ステレオ、時計、コードレス電話子機、トランシーバ、携帯無線機、携帯電話、スマートフォン、電子書籍、自動車電話、携帯型ゲーム機、電卓、携帯情報端末、電子手帳、電子翻訳機、音声入力機器、ビデオカメラ、デジタルスチルカメラ、玩具、電気シェーバ、高周波加熱装置、電気炊飯器、電気洗濯機、電気掃除機、温水器、扇風機、毛髪乾燥機、エアコンディショナー、加湿器、除湿器、空調設備、食器洗浄器、食器乾燥器、衣類乾燥器、布団乾燥器、電気冷蔵庫、電気冷凍庫、電気冷凍冷蔵庫、DNA保存用冷凍庫、懐中電灯、電動工具、煙感知器、医療機器、誘導灯、信号機、ベルトコンベア、エレベータ、エスカレータ、産業用ロボット、電力貯蔵システム、電気自動車、ハイブリッド車、プラグインハイブリッド車、装軌車両、原動機付自転車、自動二輪車、電動車椅子、ゴルフ用カート、船舶、潜水艦、ヘリコプター、航空機、ロケット、人工衛星、宇宙探査機や惑星探査機、宇宙船等がある。本実施の形態では、先の実施の形態で示した半導体装置を、携帯電話、スマートフォン、電子書籍などの携帯機器に応用した場合の例を図18乃至図21を用いて説明する。

103 酸化絶縁膜

105 酸化物半導体膜

107 酸化絶縁膜

109 金属膜

111 酸素

112 酸化絶縁膜

113 金属酸化膜

115 ゲート電極

117 ドーパント

119 酸化物半導体膜

119a 領域

119b 領域

121 サイドウォール

123 ゲート絶縁膜

123a 酸化絶縁膜

123b 金属酸化膜

125 コンタクトプラグ

127 絶縁膜

130 層間絶縁膜

131 層間絶縁膜

132 ビアホール

153 ゲート絶縁膜

163 ゲート絶縁膜

163a ゲート絶縁膜

163b ゲート絶縁膜

164 酸化絶縁膜

165 金属膜

167 保護膜

167a 酸化絶縁膜

167b 金属酸化膜

177 金属酸化膜

180 金属膜

181 酸化物半導体膜

181a 領域

181b 領域

181c 領域

182 金属酸化膜

201 基板

202 STI

203 ウェル

204a トランジスタ

204b トランジスタ

204c トランジスタ

205 不純物領域

206 ゲート絶縁膜

207 ゲート電極

208 ゲート電極

209 絶縁膜

210 サイドウォール

211 層間絶縁膜

212 層間絶縁膜

213 層間絶縁膜

214a コンタクトプラグ

214b コンタクトプラグ

215 層間絶縁膜

216 層間絶縁膜

217 バリア膜

218 配線

219 バリア膜

220 層間絶縁膜

221 層間絶縁膜

222 バリア膜

223 配線

224 バリア膜

225 酸化絶縁膜

226 トランジスタ

227 絶縁膜

228 層間絶縁膜

229 層間絶縁膜

230a コンタクトプラグ

230b コンタクトプラグ

231 層間絶縁膜

232 層間絶縁膜

233 バリア膜

234a 配線

234b 配線

235 バリア膜

236 層間絶縁膜

237 層間絶縁膜

238 バリア膜

239 配線

240 バリア膜

241 層間絶縁膜

242 層間絶縁膜

243 バリア膜

244 配線

245 バリア膜

246 保護膜

247 保護膜

248 保護膜

249a ビアホール

249b ビアホール

280 半導体基板

281 埋め込み酸化膜

282 SOI層

283a トランジスタ

283b トランジスタ

283c トランジスタ

300 基板

301 STI

302 不純物領域

303 ゲート絶縁膜

304 上部電極

305 上部電極

306 層間絶縁膜

307 層間絶縁膜

308 層間絶縁膜

309a コンタクトプラグ

309b コンタクトプラグ

310 層間絶縁膜

311 層間絶縁膜

312 バリア膜

313 配線

314 バリア膜

315 層間絶縁膜

316 層間絶縁膜

317 バリア膜

318 配線

319 バリア膜

320 酸化絶縁膜

321 絶縁膜

322 層間絶縁膜

323 層間絶縁膜

324a コンタクトプラグ

324b コンタクトプラグ

324c コンタクトプラグ

325 層間絶縁膜

326 層間絶縁膜

327 バリア膜

328a 配線

328b 配線

329 バリア膜

360 トランジスタ

362 トランジスタ

363 酸化物半導体膜

364 容量素子

450 メモリセル

451 メモリセルアレイ

451a メモリセルアレイ

451b メモリセルアレイ

453 周辺回路

454 容量素子

470 絶縁膜

471 酸化絶縁膜

472 酸化物半導体膜

472a 領域

472b 領域

473 ゲート絶縁膜

473a ゲート絶縁膜

473b ゲート絶縁膜

474 ゲート電極

475 サイドウォール

476 絶縁膜

477 層間絶縁膜

478 層間絶縁膜

479a コンタクトプラグ

479b コンタクトプラグ

480 層間絶縁膜

481 バリア膜

482a 配線

482b 配線

483 バリア膜

484 高誘電体膜

485 絶縁膜

486 層間絶縁膜

487 層間絶縁膜

488 バリア膜

489 配線

490 バリア膜

491 層間絶縁膜

492 層間絶縁膜

493 バリア膜

494 配線

495 バリア膜

801 トランジスタ

802 トランジスタ

803 トランジスタ

804 トランジスタ

805 トランジスタ

806 トランジスタ

807 Xデコーダー

808 Yデコーダー

811 トランジスタ

812 保持容量

813 Xデコーダー

814 Yデコーダー

901 RF回路

902 アナログベースバンド回路

903 デジタルベースバンド回路

904 バッテリー

905 電源回路

906 アプリケーションプロセッサ

907 CPU

908 DSP

909 IF

910 フラッシュメモリ

911 ディスプレイコントローラ

912 メモリ回路

913 ディスプレイ

914 表示部

915 ソースドライバ

916 ゲートドライバ

917 音声回路

918 キーボード

919 タッチセンサ

950 メモリ回路

951 メモリコントローラ

952 メモリ

953 メモリ

954 スイッチ

955 スイッチ

956 ディスプレイコントローラ

957 ディスプレイ

1001 バッテリー

1002 電源回路

1003 マイクロプロセッサ

1004 フラッシュメモリ

1005 音声回路

1006 キーボード

1007 メモリ回路

1008 タッチパネル

1009 ディスプレイ

1010 ディスプレイコントローラ

Claims (15)

- 酸化絶縁膜上に酸化物半導体膜を形成し、

前記酸化物半導体膜をエッチングして島状の酸化物半導体膜を形成し、

前記島状の酸化物半導体膜上に金属膜を形成し、

前記金属膜に酸素を導入して金属酸化膜を形成するとともに、前記島状の酸化物半導体膜に酸素を導入し、

前記金属酸化膜上にゲート電極を形成し、

前記ゲート電極の側面に接するサイドウォールを形成し、

前記ゲート電極及び前記サイドウォールと重ならない前記金属酸化膜をエッチングし、

前記ゲート電極、前記サイドウォール及び前記島状の酸化物半導体膜上に層間絶縁膜を形成し、

前記層間絶縁膜に形成した開口部を介して、前記島状の酸化物半導体膜と電気的に接続する一対のコンタクトプラグを形成することを特徴とする半導体装置の作製方法。 - 酸化絶縁膜上に酸化物半導体膜を形成し、

前記酸化物半導体膜をエッチングして島状の酸化物半導体膜を形成し、

前記島状の酸化物半導体膜上に酸化絶縁膜を形成し、

前記酸化絶縁膜上に金属膜を形成し、

前記金属膜に酸素を導入して金属酸化膜を形成するとともに、前記酸化絶縁膜に酸素を導入し、

前記金属酸化膜上にゲート電極を形成し、

前記ゲート電極の側面に接するサイドウォールを形成し、

前記ゲート電極及び前記サイドウォールと重ならない前記金属酸化膜をエッチングし、

前記ゲート電極、前記サイドウォール及び前記島状の酸化物半導体膜上に層間絶縁膜を形成し、

前記層間絶縁膜に形成した開口部を介して、前記島状の酸化物半導体膜と電気的に接続する一対のコンタクトプラグを形成することを特徴とする半導体装置の作製方法。 - 酸化絶縁膜上に酸化物半導体膜を形成し、

前記酸化物半導体膜をエッチングして島状の酸化物半導体膜を形成し、

前記島状の酸化物半導体膜上に絶縁膜を形成し、

前記絶縁膜上にゲート電極を形成し、

前記ゲート電極の側面に接するサイドウォールを形成し、

前記ゲート電極及び前記サイドウォールと重ならない前記絶縁膜をエッチングしてゲート絶縁膜を形成し、

前記ゲート電極、前記サイドウォール及び前記島状の酸化物半導体膜上に酸化絶縁膜を形成し、

前記酸化絶縁膜上に金属膜を形成し、

前記金属膜に酸素を導入して金属酸化膜を形成するとともに、前記酸化絶縁膜に酸素を導入し、

前記金属酸化膜上に層間絶縁膜を形成し、

前記層間絶縁膜、前記金属酸化膜及び前記酸化絶縁膜に形成した開口部を介して、前記島状の酸化物半導体膜と電気的に接続する一対のコンタクトプラグを形成することを特徴とする半導体装置の作製方法。 - 酸化絶縁膜上に酸化物半導体膜を形成し、

前記酸化物半導体膜をエッチングして島状の酸化物半導体膜を形成し、

前記島状の酸化物半導体膜上に第1の酸化絶縁膜を形成し、

前記第1の酸化絶縁膜上に第1の金属膜を形成し、

前記第1の金属膜に酸素を導入して第1の金属酸化膜を形成するとともに、前記第1の酸化絶縁膜に酸素を導入し、

前記第1の金属酸化膜上にゲート電極を形成し、

前記ゲート電極の側面に接するサイドウォールを形成し、

前記ゲート電極及び前記サイドウォールと重ならない前記第1の金属酸化膜をエッチングし、

前記ゲート電極、前記サイドウォール及び前記島状の酸化物半導体膜を覆う第2の酸化絶縁膜を形成し、

前記第2の酸化絶縁膜上に第2の金属膜を形成し、

前記第2の金属膜に酸素を導入して第2の金属酸化膜を形成するとともに、前記第2の酸化絶縁膜に酸素を導入し、

前記第2の金属酸化膜上に層間絶縁膜を形成し、

前記層間絶縁膜、前記第2の金属酸化膜及び前記第2の酸化絶縁膜に形成した開口部を介して、前記島状の酸化物半導体膜と電気的に接続する一対のコンタクトプラグを形成することを特徴とする半導体装置の作製方法。 - 酸化絶縁膜上に酸化物半導体膜を形成し、

前記酸化物半導体膜をエッチングして島状の酸化物半導体膜を形成し、

前記島状の酸化物半導体膜上に第1の金属膜を形成し、

前記第1の金属膜に酸素を導入して第1の金属酸化膜を形成するとともに、前記島状の酸化物半導体膜に酸素を導入し、

前記第1の金属酸化膜上にゲート電極を形成し、

前記ゲート電極の側面に接するサイドウォールを形成し、

前記ゲート電極及び前記サイドウォールと重ならない前記第1の金属酸化膜をエッチングし、

前記ゲート電極、前記サイドウォール及び前記島状の酸化物半導体膜上に酸化絶縁膜を形成し、

前記酸化絶縁膜上に第2の金属膜を形成し、

前記第2の金属膜に酸素を導入して第2の金属酸化膜を形成するとともに、前記酸化絶縁膜に酸素を導入し、

前記第2の金属酸化膜上に層間絶縁膜を形成し、

前記層間絶縁膜、前記第2の金属酸化膜及び前記酸化絶縁膜に形成した開口部を介して、前記島状の酸化物半導体膜と電気的に接続する一対のコンタクトプラグを形成することを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項3のいずれか一項において、

前記金属膜の材料は、アルミニウム、ガリウム、ハフニウム、又はイットリウムであり、

前記金属酸化膜は、前記金属膜に対応する酸化膜又は酸化窒化膜であることを特徴とする半導体装置の作製方法。 - 請求項4又は5において、

前記第1又は第2の金属膜は、アルミニウム膜、ハフニウム膜、又はイットリウム膜であり、

前記第1又は第2の金属酸化膜は、前記第1又は第2の金属膜に対応する酸化膜又は酸化窒化膜であることを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項7のいずれか一項において、

前記ゲート電極を形成した後、前記ゲート電極をマスクとして、前記島状の酸化物半導体膜にドーパントを導入して前記島状の酸化物半導体膜に低抵抗領域を形成し、

前記低抵抗領域を有する島状の酸化物半導体膜上に前記サイドウォールを形成することを特徴とする半導体装置の作製方法。 - 請求項8において、

前記ドーパントは、ホウ素、窒素、リン、及びヒ素の少なくとも一以上であることを特徴とする半導体装置の作製方法。 - 請求項8において、

前記ドーパントは、ヘリウム、ネオン、アルゴン、クリプトン、及びキセノンの少なくとも一以上であることを特徴とする半導体装置の作製方法。 - 請求項8乃至請求項10のいずれか一項において、

前記低抵抗領域には、前記ドーパントが、5×1018atoms/cm3以上1×1022atoms/cm3以下の濃度で含まれていることを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項11のいずれか一項において、

前記島状の酸化物半導体膜は、In、Ga、Sn及びZnから選ばれた一種以上の元素を含むことを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項12のいずれか一項において、

半導体基板にトランジスタを形成し、

前記トランジスタ上に平坦化絶縁膜を形成し、

前記平坦化絶縁膜に形成した開口部を介して、前記トランジスタと電気的に接続する配線を形成し、

前記平坦化絶縁膜及び前記配線上に前記酸化絶縁膜を形成し、

前記層間絶縁膜及び前記平坦化絶縁膜に形成した開口部を介して、前記コンタクトプラグと前記配線とを電気的に接続させることを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項12のいずれか一項において、

SOI基板が有する半導体膜にトランジスタを形成し、

前記トランジスタ上に平坦化絶縁膜を形成し、

前記平坦化絶縁膜に形成した開口部を介して、前記トランジスタと電気的に接続する配線を形成し、

前記平坦化絶縁膜及び前記配線上に前記酸化絶縁膜を形成し、

前記層間絶縁膜及び前記平坦化絶縁膜に形成した開口部を介して、前記コンタクトプラグと前記配線とを電気的に接続させることを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項14のいずれか一項において、

前記半導体装置は、中央演算処理装置、マイクロプロセッサ、ランダムアクセスメモリ、コンバータ、パワートランジスタ、サイリスタ、イメージセンサ、電気光学装置又は発光表示装置であることを特徴とする半導体装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013018105A JP6077868B2 (ja) | 2012-02-07 | 2013-02-01 | 半導体装置の作製方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012024010 | 2012-02-07 | ||

| JP2012024010 | 2012-02-07 | ||

| JP2013018105A JP6077868B2 (ja) | 2012-02-07 | 2013-02-01 | 半導体装置の作製方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2013179286A JP2013179286A (ja) | 2013-09-09 |

| JP6077868B2 true JP6077868B2 (ja) | 2017-02-08 |

Family

ID=48903242

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013018105A Active JP6077868B2 (ja) | 2012-02-07 | 2013-02-01 | 半導体装置の作製方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (3) | US8916424B2 (ja) |

| JP (1) | JP6077868B2 (ja) |

Families Citing this family (69)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8956912B2 (en) * | 2012-01-26 | 2015-02-17 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| US20130221345A1 (en) | 2012-02-28 | 2013-08-29 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| JP6224931B2 (ja) | 2012-07-27 | 2017-11-01 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| TWI595659B (zh) | 2012-09-14 | 2017-08-11 | 半導體能源研究所股份有限公司 | 半導體裝置及其製造方法 |

| TWI614813B (zh) | 2013-01-21 | 2018-02-11 | 半導體能源研究所股份有限公司 | 半導體裝置的製造方法 |

| US9601591B2 (en) | 2013-08-09 | 2017-03-21 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| KR102304824B1 (ko) | 2013-08-09 | 2021-09-23 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| KR102281300B1 (ko) | 2013-09-11 | 2021-07-26 | 삼성디스플레이 주식회사 | 박막 트랜지스터, 박막 트랜지스터의 제조 방법 및 박막 트랜지스터를 포함하는 표시장치 |

| US9397153B2 (en) | 2013-09-23 | 2016-07-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP6384822B2 (ja) * | 2013-11-07 | 2018-09-05 | Tianma Japan株式会社 | イメージセンサ及びその製造方法 |

| JP6506545B2 (ja) | 2013-12-27 | 2019-04-24 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| KR102320576B1 (ko) * | 2013-12-27 | 2021-11-02 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| CN117690933A (zh) * | 2013-12-27 | 2024-03-12 | 株式会社半导体能源研究所 | 发光装置 |

| US9397149B2 (en) * | 2013-12-27 | 2016-07-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US9318618B2 (en) * | 2013-12-27 | 2016-04-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US9472678B2 (en) * | 2013-12-27 | 2016-10-18 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| KR102360695B1 (ko) | 2014-01-23 | 2022-02-08 | 글로벌웨이퍼스 씨오., 엘티디. | 고 비저항 soi 웨이퍼 및 그 제조 방법 |

| US9443876B2 (en) | 2014-02-05 | 2016-09-13 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, display device including the semiconductor device, display module including the display device, and electronic device including the semiconductor device, the display device, and the display module |

| JP6585354B2 (ja) * | 2014-03-07 | 2019-10-02 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US9443872B2 (en) * | 2014-03-07 | 2016-09-13 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US10361290B2 (en) | 2014-03-14 | 2019-07-23 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device comprising adding oxygen to buffer film and insulating film |

| TWI656631B (zh) * | 2014-03-28 | 2019-04-11 | 日商半導體能源研究所股份有限公司 | 攝像裝置 |

| JP6616102B2 (ja) * | 2014-05-23 | 2019-12-04 | 株式会社半導体エネルギー研究所 | 記憶装置及び電子機器 |

| KR20250019744A (ko) | 2014-05-30 | 2025-02-10 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 발광 장치 |

| US9831238B2 (en) | 2014-05-30 | 2017-11-28 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device including insulating film having opening portion and conductive film in the opening portion |

| JP6417125B2 (ja) * | 2014-06-25 | 2018-10-31 | 株式会社ジャパンディスプレイ | 半導体装置 |

| US9461179B2 (en) * | 2014-07-11 | 2016-10-04 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor device (TFT) comprising stacked oxide semiconductor layers and having a surrounded channel structure |

| US9679812B2 (en) * | 2014-07-24 | 2017-06-13 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor device with self-aligned contact |

| US10115830B2 (en) | 2014-07-29 | 2018-10-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, manufacturing method thereof, and electronic device |

| US9722091B2 (en) | 2014-09-12 | 2017-08-01 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| KR102202603B1 (ko) * | 2014-09-19 | 2021-01-14 | 삼성전자주식회사 | 반도체 장치 및 이의 제조 방법 |

| WO2016125051A1 (en) | 2015-02-04 | 2016-08-11 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| US10249644B2 (en) | 2015-02-13 | 2019-04-02 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method of the same |

| US9653613B2 (en) * | 2015-02-27 | 2017-05-16 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP6744108B2 (ja) | 2015-03-02 | 2020-08-19 | 株式会社半導体エネルギー研究所 | トランジスタ、トランジスタの作製方法、半導体装置および電子機器 |

| KR102582523B1 (ko) * | 2015-03-19 | 2023-09-26 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 전자 기기 |

| US10460984B2 (en) | 2015-04-15 | 2019-10-29 | Semiconductor Energy Laboratory Co., Ltd. | Method for fabricating electrode and semiconductor device |

| US10002970B2 (en) | 2015-04-30 | 2018-06-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, manufacturing method of the same, or display device including the same |

| CN104934330A (zh) * | 2015-05-08 | 2015-09-23 | 京东方科技集团股份有限公司 | 一种薄膜晶体管及其制备方法、阵列基板和显示面板 |

| TWI693719B (zh) * | 2015-05-11 | 2020-05-11 | 日商半導體能源研究所股份有限公司 | 半導體裝置的製造方法 |

| JP2016225614A (ja) * | 2015-05-26 | 2016-12-28 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US11024725B2 (en) | 2015-07-24 | 2021-06-01 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device including metal oxide film |

| CN106409919A (zh) * | 2015-07-30 | 2017-02-15 | 株式会社半导体能源研究所 | 半导体装置以及包括该半导体装置的显示装置 |

| JP2017085093A (ja) * | 2015-10-29 | 2017-05-18 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| SG10201608814YA (en) | 2015-10-29 | 2017-05-30 | Semiconductor Energy Lab Co Ltd | Semiconductor device and method for manufacturing the semiconductor device |

| WO2017081579A1 (en) * | 2015-11-13 | 2017-05-18 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| US10700212B2 (en) | 2016-01-28 | 2020-06-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, semiconductor wafer, module, electronic device, and manufacturing method thereof |

| CN115172467A (zh) | 2016-02-18 | 2022-10-11 | 株式会社半导体能源研究所 | 半导体装置、其制造方法、显示装置以及电子设备 |

| JP6539873B2 (ja) * | 2016-03-16 | 2019-07-10 | 株式会社Joled | 薄膜トランジスタ、及び薄膜トランジスタを備えた表示装置 |

| KR20170119801A (ko) * | 2016-04-19 | 2017-10-30 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치 및 유기 발광 표시 장치의 제조 방법 |

| CN115799342A (zh) * | 2016-07-26 | 2023-03-14 | 株式会社半导体能源研究所 | 半导体装置 |

| DE102016122318A1 (de) | 2016-11-21 | 2018-05-24 | Infineon Technologies Ag | Anschlussstruktur eines Leistungshalbleiterbauelements |

| JP7126823B2 (ja) | 2016-12-23 | 2022-08-29 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US10263107B2 (en) * | 2017-05-01 | 2019-04-16 | The Regents Of The University Of California | Strain gated transistors and method |

| US20180323246A1 (en) * | 2017-05-02 | 2018-11-08 | Shenzhen China Star Optoelectronics Technology Co., Ltd. | Organic light-emitting diode display panel and manufacturing method thereof |

| US10304782B2 (en) * | 2017-08-25 | 2019-05-28 | Infineon Technologies Ag | Compressive interlayer having a defined crack-stop edge extension |

| US11127693B2 (en) * | 2017-08-25 | 2021-09-21 | Infineon Technologies Ag | Barrier for power metallization in semiconductor devices |

| CN111373515B (zh) * | 2017-11-24 | 2024-03-05 | 株式会社半导体能源研究所 | 半导体材料及半导体装置 |

| TW202006945A (zh) | 2018-07-12 | 2020-02-01 | 日商Flosfia股份有限公司 | 半導體裝置和半導體系統 |

| US10734320B2 (en) | 2018-07-30 | 2020-08-04 | Infineon Technologies Austria Ag | Power metallization structure for semiconductor devices |

| US11167375B2 (en) | 2018-08-10 | 2021-11-09 | The Research Foundation For The State University Of New York | Additive manufacturing processes and additively manufactured products |

| US11121025B2 (en) * | 2018-09-27 | 2021-09-14 | Taiwan Semiconductor Manufacturing Company, Ltd. | Layer for side wall passivation |

| JPWO2020089762A1 (ja) | 2018-11-02 | 2020-05-07 | ||

| US11031321B2 (en) | 2019-03-15 | 2021-06-08 | Infineon Technologies Ag | Semiconductor device having a die pad with a dam-like configuration |

| JP2021044502A (ja) * | 2019-09-13 | 2021-03-18 | キオクシア株式会社 | 半導体装置およびその製造方法 |

| CN111403352A (zh) * | 2020-03-24 | 2020-07-10 | 长江存储科技有限责任公司 | 一种三维存储器、cmos晶体管及其制造方法 |

| CN111725324B (zh) * | 2020-06-11 | 2021-11-02 | 武汉华星光电半导体显示技术有限公司 | 薄膜晶体管、阵列基板及其制造方法 |

| CN113964119A (zh) * | 2020-07-21 | 2022-01-21 | 联华电子股份有限公司 | 半导体元件 |

| KR102777683B1 (ko) * | 2020-08-04 | 2025-03-10 | 에스케이하이닉스 주식회사 | 웨이퍼 대 웨이퍼 본딩 구조를 갖는 반도체 장치 및 그 제조방법 |

Family Cites Families (130)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60198861A (ja) | 1984-03-23 | 1985-10-08 | Fujitsu Ltd | 薄膜トランジスタ |

| JPH0244256B2 (ja) | 1987-01-28 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn2o5deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244260B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn5o8deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPS63210023A (ja) | 1987-02-24 | 1988-08-31 | Natl Inst For Res In Inorg Mater | InGaZn↓4O↓7で示される六方晶系の層状構造を有する化合物およびその製造法 |

| JPH0244258B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn3o6deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244262B2 (ja) | 1987-02-27 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn6o9deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244263B2 (ja) | 1987-04-22 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn7o10deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH05251705A (ja) | 1992-03-04 | 1993-09-28 | Fuji Xerox Co Ltd | 薄膜トランジスタ |

| JP3298974B2 (ja) | 1993-03-23 | 2002-07-08 | 電子科学株式会社 | 昇温脱離ガス分析装置 |

| JP3479375B2 (ja) | 1995-03-27 | 2003-12-15 | 科学技術振興事業団 | 亜酸化銅等の金属酸化物半導体による薄膜トランジスタとpn接合を形成した金属酸化物半導体装置およびそれらの製造方法 |

| JPH11505377A (ja) | 1995-08-03 | 1999-05-18 | フィリップス エレクトロニクス ネムローゼ フェンノートシャップ | 半導体装置 |

| JP3625598B2 (ja) | 1995-12-30 | 2005-03-02 | 三星電子株式会社 | 液晶表示装置の製造方法 |

| JP4170454B2 (ja) | 1998-07-24 | 2008-10-22 | Hoya株式会社 | 透明導電性酸化物薄膜を有する物品及びその製造方法 |

| JP2000150861A (ja) | 1998-11-16 | 2000-05-30 | Tdk Corp | 酸化物薄膜 |

| JP3276930B2 (ja) | 1998-11-17 | 2002-04-22 | 科学技術振興事業団 | トランジスタ及び半導体装置 |

| TW460731B (en) | 1999-09-03 | 2001-10-21 | Ind Tech Res Inst | Electrode structure and production method of wide viewing angle LCD |

| JP4089858B2 (ja) | 2000-09-01 | 2008-05-28 | 国立大学法人東北大学 | 半導体デバイス |

| KR20020038482A (ko) | 2000-11-15 | 2002-05-23 | 모리시타 요이찌 | 박막 트랜지스터 어레이, 그 제조방법 및 그것을 이용한표시패널 |

| JP3997731B2 (ja) | 2001-03-19 | 2007-10-24 | 富士ゼロックス株式会社 | 基材上に結晶性半導体薄膜を形成する方法 |

| JP2002289859A (ja) | 2001-03-23 | 2002-10-04 | Minolta Co Ltd | 薄膜トランジスタ |

| JP4090716B2 (ja) | 2001-09-10 | 2008-05-28 | 雅司 川崎 | 薄膜トランジスタおよびマトリクス表示装置 |

| JP3925839B2 (ja) | 2001-09-10 | 2007-06-06 | シャープ株式会社 | 半導体記憶装置およびその試験方法 |

| JP4164562B2 (ja) | 2002-09-11 | 2008-10-15 | 独立行政法人科学技術振興機構 | ホモロガス薄膜を活性層として用いる透明薄膜電界効果型トランジスタ |

| EP1443130B1 (en) | 2001-11-05 | 2011-09-28 | Japan Science and Technology Agency | Natural superlattice homologous single crystal thin film, method for preparation thereof, and device using said single crystal thin film |

| CN100468638C (zh) | 2001-12-18 | 2009-03-11 | 松下电器产业株式会社 | 半导体元件的制造方法 |

| JP4083486B2 (ja) | 2002-02-21 | 2008-04-30 | 独立行政法人科学技術振興機構 | LnCuO(S,Se,Te)単結晶薄膜の製造方法 |

| US7049190B2 (en) | 2002-03-15 | 2006-05-23 | Sanyo Electric Co., Ltd. | Method for forming ZnO film, method for forming ZnO semiconductor layer, method for fabricating semiconductor device, and semiconductor device |

| JP3933591B2 (ja) | 2002-03-26 | 2007-06-20 | 淳二 城戸 | 有機エレクトロルミネッセント素子 |

| US7339187B2 (en) | 2002-05-21 | 2008-03-04 | State Of Oregon Acting By And Through The Oregon State Board Of Higher Education On Behalf Of Oregon State University | Transistor structures |

| JP2004022625A (ja) | 2002-06-13 | 2004-01-22 | Murata Mfg Co Ltd | 半導体デバイス及び該半導体デバイスの製造方法 |

| US7105868B2 (en) | 2002-06-24 | 2006-09-12 | Cermet, Inc. | High-electron mobility transistor with zinc oxide |

| US7067843B2 (en) | 2002-10-11 | 2006-06-27 | E. I. Du Pont De Nemours And Company | Transparent oxide semiconductor thin film transistors |

| JP4166105B2 (ja) | 2003-03-06 | 2008-10-15 | シャープ株式会社 | 半導体装置およびその製造方法 |

| JP2004273732A (ja) | 2003-03-07 | 2004-09-30 | Sharp Corp | アクティブマトリクス基板およびその製造方法 |

| JP4108633B2 (ja) | 2003-06-20 | 2008-06-25 | シャープ株式会社 | 薄膜トランジスタおよびその製造方法ならびに電子デバイス |

| JP3851914B2 (ja) | 2003-07-09 | 2006-11-29 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| US7262463B2 (en) | 2003-07-25 | 2007-08-28 | Hewlett-Packard Development Company, L.P. | Transistor including a deposited channel region having a doped portion |

| US7145174B2 (en) | 2004-03-12 | 2006-12-05 | Hewlett-Packard Development Company, Lp. | Semiconductor device |

| KR20070116889A (ko) | 2004-03-12 | 2007-12-11 | 도꾸리쯔교세이호징 가가꾸 기쥬쯔 신꼬 기꼬 | 아몰퍼스 산화물 박막의 기상성막방법 |

| US7282782B2 (en) | 2004-03-12 | 2007-10-16 | Hewlett-Packard Development Company, L.P. | Combined binary oxide semiconductor device |

| US7297977B2 (en) | 2004-03-12 | 2007-11-20 | Hewlett-Packard Development Company, L.P. | Semiconductor device |

| US7211825B2 (en) | 2004-06-14 | 2007-05-01 | Yi-Chi Shih | Indium oxide-based thin film transistors and circuits |

| JP2006100760A (ja) | 2004-09-02 | 2006-04-13 | Casio Comput Co Ltd | 薄膜トランジスタおよびその製造方法 |

| US7285501B2 (en) | 2004-09-17 | 2007-10-23 | Hewlett-Packard Development Company, L.P. | Method of forming a solution processed device |

| US7298084B2 (en) | 2004-11-02 | 2007-11-20 | 3M Innovative Properties Company | Methods and displays utilizing integrated zinc oxide row and column drivers in conjunction with organic light emitting diodes |

| EP1810335B1 (en) | 2004-11-10 | 2020-05-27 | Canon Kabushiki Kaisha | Light-emitting device |

| US7453065B2 (en) | 2004-11-10 | 2008-11-18 | Canon Kabushiki Kaisha | Sensor and image pickup device |

| AU2005302964B2 (en) | 2004-11-10 | 2010-11-04 | Canon Kabushiki Kaisha | Field effect transistor employing an amorphous oxide |

| KR100939998B1 (ko) | 2004-11-10 | 2010-02-03 | 캐논 가부시끼가이샤 | 비정질 산화물 및 전계 효과 트랜지스터 |

| US7863611B2 (en) | 2004-11-10 | 2011-01-04 | Canon Kabushiki Kaisha | Integrated circuits utilizing amorphous oxides |

| US7829444B2 (en) | 2004-11-10 | 2010-11-09 | Canon Kabushiki Kaisha | Field effect transistor manufacturing method |

| US7791072B2 (en) | 2004-11-10 | 2010-09-07 | Canon Kabushiki Kaisha | Display |

| US7579224B2 (en) | 2005-01-21 | 2009-08-25 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a thin film semiconductor device |

| TWI481024B (zh) | 2005-01-28 | 2015-04-11 | 半導體能源研究所股份有限公司 | 半導體裝置,電子裝置,和半導體裝置的製造方法 |

| TWI562380B (en) | 2005-01-28 | 2016-12-11 | Semiconductor Energy Lab Co Ltd | Semiconductor device, electronic device, and method of manufacturing semiconductor device |

| US7858451B2 (en) | 2005-02-03 | 2010-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device, semiconductor device and manufacturing method thereof |

| US7948171B2 (en) | 2005-02-18 | 2011-05-24 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device |

| US20060197092A1 (en) | 2005-03-03 | 2006-09-07 | Randy Hoffman | System and method for forming conductive material on a substrate |

| US8681077B2 (en) | 2005-03-18 | 2014-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, and display device, driving method and electronic apparatus thereof |

| WO2006105077A2 (en) | 2005-03-28 | 2006-10-05 | Massachusetts Institute Of Technology | Low voltage thin film transistor with high-k dielectric material |

| US7645478B2 (en) | 2005-03-31 | 2010-01-12 | 3M Innovative Properties Company | Methods of making displays |

| US8300031B2 (en) | 2005-04-20 | 2012-10-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising transistor having gate and drain connected through a current-voltage conversion element |

| JP2006344849A (ja) | 2005-06-10 | 2006-12-21 | Casio Comput Co Ltd | 薄膜トランジスタ |

| US7402506B2 (en) | 2005-06-16 | 2008-07-22 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7691666B2 (en) | 2005-06-16 | 2010-04-06 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7507618B2 (en) | 2005-06-27 | 2009-03-24 | 3M Innovative Properties Company | Method for making electronic devices using metal oxide nanoparticles |

| KR100711890B1 (ko) | 2005-07-28 | 2007-04-25 | 삼성에스디아이 주식회사 | 유기 발광표시장치 및 그의 제조방법 |

| JP2007059128A (ja) | 2005-08-23 | 2007-03-08 | Canon Inc | 有機el表示装置およびその製造方法 |

| JP4850457B2 (ja) | 2005-09-06 | 2012-01-11 | キヤノン株式会社 | 薄膜トランジスタ及び薄膜ダイオード |

| JP5116225B2 (ja) | 2005-09-06 | 2013-01-09 | キヤノン株式会社 | 酸化物半導体デバイスの製造方法 |

| JP4280736B2 (ja) | 2005-09-06 | 2009-06-17 | キヤノン株式会社 | 半導体素子 |

| JP2007073705A (ja) | 2005-09-06 | 2007-03-22 | Canon Inc | 酸化物半導体チャネル薄膜トランジスタおよびその製造方法 |

| JP5216201B2 (ja) * | 2005-09-27 | 2013-06-19 | 株式会社半導体エネルギー研究所 | 半導体装置、半導体装置の作製方法、液晶表示装置、rfidタグ、発光装置及び電子機器 |

| EP1998374A3 (en) | 2005-09-29 | 2012-01-18 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device having oxide semiconductor layer and manufacturing method thereof |

| JP5078246B2 (ja) | 2005-09-29 | 2012-11-21 | 株式会社半導体エネルギー研究所 | 半導体装置、及び半導体装置の作製方法 |

| JP5064747B2 (ja) | 2005-09-29 | 2012-10-31 | 株式会社半導体エネルギー研究所 | 半導体装置、電気泳動表示装置、表示モジュール、電子機器、及び半導体装置の作製方法 |

| JP5037808B2 (ja) | 2005-10-20 | 2012-10-03 | キヤノン株式会社 | アモルファス酸化物を用いた電界効果型トランジスタ、及び該トランジスタを用いた表示装置 |

| KR101397571B1 (ko) | 2005-11-15 | 2014-05-22 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체장치 및 그의 제조방법 |

| TWI292281B (en) | 2005-12-29 | 2008-01-01 | Ind Tech Res Inst | Pixel structure of active organic light emitting diode and method of fabricating the same |

| US7867636B2 (en) | 2006-01-11 | 2011-01-11 | Murata Manufacturing Co., Ltd. | Transparent conductive film and method for manufacturing the same |

| JP4977478B2 (ja) | 2006-01-21 | 2012-07-18 | 三星電子株式会社 | ZnOフィルム及びこれを用いたTFTの製造方法 |

| US7576394B2 (en) | 2006-02-02 | 2009-08-18 | Kochi Industrial Promotion Center | Thin film transistor including low resistance conductive thin films and manufacturing method thereof |

| US7977169B2 (en) | 2006-02-15 | 2011-07-12 | Kochi Industrial Promotion Center | Semiconductor device including active layer made of zinc oxide with controlled orientations and manufacturing method thereof |

| KR20070101595A (ko) | 2006-04-11 | 2007-10-17 | 삼성전자주식회사 | ZnO TFT |

| US20070252928A1 (en) | 2006-04-28 | 2007-11-01 | Toppan Printing Co., Ltd. | Structure, transmission type liquid crystal display, reflection type display and manufacturing method thereof |

| JP5028033B2 (ja) | 2006-06-13 | 2012-09-19 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4999400B2 (ja) | 2006-08-09 | 2012-08-15 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4609797B2 (ja) | 2006-08-09 | 2011-01-12 | Nec液晶テクノロジー株式会社 | 薄膜デバイス及びその製造方法 |

| JP4332545B2 (ja) | 2006-09-15 | 2009-09-16 | キヤノン株式会社 | 電界効果型トランジスタ及びその製造方法 |

| JP4274219B2 (ja) | 2006-09-27 | 2009-06-03 | セイコーエプソン株式会社 | 電子デバイス、有機エレクトロルミネッセンス装置、有機薄膜半導体装置 |

| JP5164357B2 (ja) | 2006-09-27 | 2013-03-21 | キヤノン株式会社 | 半導体装置及び半導体装置の製造方法 |

| US7622371B2 (en) | 2006-10-10 | 2009-11-24 | Hewlett-Packard Development Company, L.P. | Fused nanocrystal thin film semiconductor and method |

| US7772021B2 (en) | 2006-11-29 | 2010-08-10 | Samsung Electronics Co., Ltd. | Flat panel displays comprising a thin-film transistor having a semiconductive oxide in its channel and methods of fabricating the same for use in flat panel displays |

| JP2008140684A (ja) | 2006-12-04 | 2008-06-19 | Toppan Printing Co Ltd | カラーelディスプレイおよびその製造方法 |

| KR101303578B1 (ko) | 2007-01-05 | 2013-09-09 | 삼성전자주식회사 | 박막 식각 방법 |

| US8207063B2 (en) | 2007-01-26 | 2012-06-26 | Eastman Kodak Company | Process for atomic layer deposition |

| KR100851215B1 (ko) | 2007-03-14 | 2008-08-07 | 삼성에스디아이 주식회사 | 박막 트랜지스터 및 이를 이용한 유기 전계 발광표시장치 |

| US7795613B2 (en) | 2007-04-17 | 2010-09-14 | Toppan Printing Co., Ltd. | Structure with transistor |

| KR101325053B1 (ko) | 2007-04-18 | 2013-11-05 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판 및 이의 제조 방법 |

| KR20080094300A (ko) | 2007-04-19 | 2008-10-23 | 삼성전자주식회사 | 박막 트랜지스터 및 그 제조 방법과 박막 트랜지스터를포함하는 평판 디스플레이 |

| KR101334181B1 (ko) | 2007-04-20 | 2013-11-28 | 삼성전자주식회사 | 선택적으로 결정화된 채널층을 갖는 박막 트랜지스터 및 그제조 방법 |

| US8274078B2 (en) | 2007-04-25 | 2012-09-25 | Canon Kabushiki Kaisha | Metal oxynitride semiconductor containing zinc |

| KR101345376B1 (ko) | 2007-05-29 | 2013-12-24 | 삼성전자주식회사 | ZnO 계 박막 트랜지스터 및 그 제조방법 |

| JP5215158B2 (ja) | 2007-12-17 | 2013-06-19 | 富士フイルム株式会社 | 無機結晶性配向膜及びその製造方法、半導体デバイス |

| KR101549530B1 (ko) * | 2008-05-23 | 2015-09-02 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체장치 |

| JP5584960B2 (ja) | 2008-07-03 | 2014-09-10 | ソニー株式会社 | 薄膜トランジスタおよび表示装置 |

| JP4623179B2 (ja) | 2008-09-18 | 2011-02-02 | ソニー株式会社 | 薄膜トランジスタおよびその製造方法 |

| JP5552753B2 (ja) * | 2008-10-08 | 2014-07-16 | ソニー株式会社 | 薄膜トランジスタおよび表示装置 |

| JP5451280B2 (ja) | 2008-10-09 | 2014-03-26 | キヤノン株式会社 | ウルツ鉱型結晶成長用基板およびその製造方法ならびに半導体装置 |

| TWI487104B (zh) * | 2008-11-07 | 2015-06-01 | 半導體能源研究所股份有限公司 | 半導體裝置和其製造方法 |

| JP2010205987A (ja) | 2009-03-04 | 2010-09-16 | Sony Corp | 薄膜トランジスタおよびその製造方法並びに表示装置 |

| US20110006349A1 (en) * | 2009-07-13 | 2011-01-13 | Toshiba America Electronic Components, Inc. | Field effect transistor having channel silicon germanium |

| KR102321812B1 (ko) * | 2009-10-29 | 2021-11-03 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| US8334148B2 (en) * | 2009-11-11 | 2012-12-18 | Samsung Electronics Co., Ltd. | Methods of forming pattern structures |

| KR20130025871A (ko) | 2010-02-26 | 2013-03-12 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치를 제작하기 위한 방법 |

| JP5708910B2 (ja) * | 2010-03-30 | 2015-04-30 | ソニー株式会社 | 薄膜トランジスタおよびその製造方法、並びに表示装置 |

| WO2011132591A1 (en) | 2010-04-23 | 2011-10-27 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| KR101800844B1 (ko) | 2010-04-23 | 2017-11-23 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치의 제작 방법 |

| CN103500709B (zh) | 2010-04-23 | 2015-09-23 | 株式会社半导体能源研究所 | 半导体装置的制造方法 |

| WO2011155502A1 (en) | 2010-06-11 | 2011-12-15 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| CN107452630B (zh) | 2010-07-02 | 2020-11-27 | 株式会社半导体能源研究所 | 半导体装置 |

| TWI572009B (zh) * | 2011-01-14 | 2017-02-21 | 半導體能源研究所股份有限公司 | 半導體記憶裝置 |

| TW202211311A (zh) | 2011-01-26 | 2022-03-16 | 日商半導體能源研究所股份有限公司 | 半導體裝置及其製造方法 |

| TWI541904B (zh) | 2011-03-11 | 2016-07-11 | 半導體能源研究所股份有限公司 | 半導體裝置的製造方法 |

| JP6005401B2 (ja) | 2011-06-10 | 2016-10-12 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US9287405B2 (en) | 2011-10-13 | 2016-03-15 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising oxide semiconductor |

| US8785258B2 (en) | 2011-12-20 | 2014-07-22 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| JP5917385B2 (ja) | 2011-12-27 | 2016-05-11 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| KR102100425B1 (ko) | 2011-12-27 | 2020-04-13 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 반도체 장치의 제작 방법 |

| US8956912B2 (en) | 2012-01-26 | 2015-02-17 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

-

2013

- 2013-01-31 US US13/755,862 patent/US8916424B2/en not_active Expired - Fee Related

- 2013-02-01 JP JP2013018105A patent/JP6077868B2/ja active Active

-

2014

- 2014-12-22 US US14/578,578 patent/US9117662B2/en active Active

-

2015

- 2015-08-21 US US14/831,972 patent/US9496375B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20150380529A1 (en) | 2015-12-31 |

| US20130203214A1 (en) | 2013-08-08 |

| JP2013179286A (ja) | 2013-09-09 |

| US9496375B2 (en) | 2016-11-15 |

| US20150140731A1 (en) | 2015-05-21 |

| US8916424B2 (en) | 2014-12-23 |

| US9117662B2 (en) | 2015-08-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6077868B2 (ja) | 半導体装置の作製方法 | |

| US12414334B2 (en) | Insulating film, method for manufacturing semiconductor device, and semiconductor device | |

| JP6184698B2 (ja) | 半導体装置の作製方法 | |

| US9054200B2 (en) | Semiconductor device | |

| JP2018117144A (ja) | 半導体装置の作製方法 | |

| JP2018121065A (ja) | 半導体装置 | |

| JP6505769B2 (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20151222 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20161130 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20161220 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170113 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6077868 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |