JP6073705B2 - ヒューズ回路及び半導体集積回路装置 - Google Patents

ヒューズ回路及び半導体集積回路装置 Download PDFInfo

- Publication number

- JP6073705B2 JP6073705B2 JP2013036212A JP2013036212A JP6073705B2 JP 6073705 B2 JP6073705 B2 JP 6073705B2 JP 2013036212 A JP2013036212 A JP 2013036212A JP 2013036212 A JP2013036212 A JP 2013036212A JP 6073705 B2 JP6073705 B2 JP 6073705B2

- Authority

- JP

- Japan

- Prior art keywords

- fuse

- circuit

- semiconductor integrated

- potential

- integrated circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 44

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 15

- 229920005591 polysilicon Polymers 0.000 claims description 15

- 239000000758 substrate Substances 0.000 claims description 7

- 238000001514 detection method Methods 0.000 description 38

- 238000010586 diagram Methods 0.000 description 12

- 239000000463 material Substances 0.000 description 7

- 238000004519 manufacturing process Methods 0.000 description 4

- 230000003321 amplification Effects 0.000 description 3

- 238000003199 nucleic acid amplification method Methods 0.000 description 3

- 238000006243 chemical reaction Methods 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 230000001133 acceleration Effects 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- -1 for example Substances 0.000 description 1

- 230000001771 impaired effect Effects 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 230000005389 magnetism Effects 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01H—ELECTRIC SWITCHES; RELAYS; SELECTORS; EMERGENCY PROTECTIVE DEVICES

- H01H85/00—Protective devices in which the current flows through a part of fusible material and this current is interrupted by displacement of the fusible material when this current becomes excessive

- H01H85/02—Details

- H01H85/0241—Structural association of a fuse and another component or apparatus

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01H—ELECTRIC SWITCHES; RELAYS; SELECTORS; EMERGENCY PROTECTIVE DEVICES

- H01H85/00—Protective devices in which the current flows through a part of fusible material and this current is interrupted by displacement of the fusible material when this current becomes excessive

- H01H85/02—Details

- H01H85/0241—Structural association of a fuse and another component or apparatus

- H01H2085/0283—Structural association with a semiconductor device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/525—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body with adaptable interconnections

- H01L23/5256—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body with adaptable interconnections comprising fuses, i.e. connections having their state changed from conductive to non-conductive

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

- Semiconductor Integrated Circuits (AREA)

Description

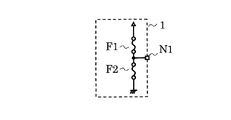

ヒューズ回路1は、ヒューズF1とヒューズF2とで構成される。ヒューズF1とヒューズF2は、それぞれ2つの接続端子を有し、各ヒューズの一方の接続端子は共通に接続される。この接続点は、ヒューズ回路1の出力端子N1である。各ヒューズのもう一方の接続端子は、それぞれ異なる電位の配線に接続される。説明のために、この異なる電位を電位VSSと、電位VSSよりも高い電位の電位VDDとする。また、ヒューズF1の抵抗値をRf1、ヒューズF2の抵抗値をRf2、出力端子N1の電位をV1とする。

ヒューズF1およびヒューズF2を切断していない状態においては、出力端子N1の電位V1と、VDDからヒューズF1とヒューズF2を経由してVSSに流れる電流IFは、次式で表される。

IF=(VDD−VSS)÷(Rf1+Rf2)・・・(2)

抵抗体の抵抗値は、シート抵抗と抵抗の幅Wと長さLとで求まる。ヒューズF1とヒューズF2は略同一のレイアウト形状であるから、幅Wと長さLは略同一であり、ヒューズF1を構成する抵抗体のシート抵抗はヒューズF2を構成する抵抗体のシート抵抗よりも高い。即ち、抵抗値Rf1は抵抗値Rf2よりも大きくなる。従って、どちらのヒューズも切断していない状態においては、出力端子N1の電位V1は、VDDとVSSとの中点電位よりも、VSSに近い電位となる。

V1−VSS=(1÷5)・(VDD−VSS)・・・(3)

となる。これは、一般的にスイッチやNOT回路の状態を確定するのに十分な電位である。

V1−VSS=(1÷1001)×(VDD−VSS)・・・(4)

となる。すなわち電位V1はほぼVSSの電位に等しくなるから、本実施形態において好適である。

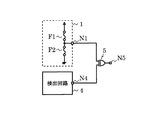

ヒューズF1を切断した場合には、出力端子N1の電位はVSSレベルになるから論理値は「0」となる。従って、検出回路4の出力N4が検出状態「1」の場合に出力N5は「1」となり、検出回路4の出力N4が非検出状態「0」の場合に出力N5は「0」となる。一方、ヒューズF2を切断した場合には、出力端子N1の電位はVDDレベルになるから論理値は「1」となる。

検出回路4は、磁電変換素子であるホール素子4aと、増幅回路4bと、比較回路4cと、基準電圧回路4dで構成される。ホール素子4aの4つの端子のうち対向する2つの端子にはそれぞれ電源端子が接続され、残りの2つの端子は増幅回路4bの入力に接続される。増幅回路4bの出力は比較回路4cの入力の一方に接続され、比較回路4cのもう一方の端子には基準電圧回路4dの一方の端子に接続される。比較回路4cの出力は検出回路4の出力端子N4に接続され、基準電圧回路4dのもう一方の端子は電源端子に接続される。図6に示した検出回路4は以上のように構成され、次のように動作する。

2 スイッチ回路

4 検出回路

4a ホール素子

4b 増幅回路

4c 比較回路

4d 基準電圧回路

Claims (3)

- 異なる電位の端子の間に直列に接続された第一のヒューズと第二のヒューズを備え、

前記第一のヒューズと前記第二のヒューズは、シート抵抗が異なる抵抗体であって、前記第一のヒューズの抵抗値と前記第二のヒューズの抵抗値が異なることを特徴とするヒューズ回路。 - 前記第一のヒューズと前記第二のヒューズは、一方が低抵抗ポリシリコンであり、他方が高抵抗ポリシリコンであることを特徴とする請求項1に記載のヒューズ回路。

- 半導体基板上に集積された半導体集積回路装置であって

請求項1に記載のヒューズ回路と、

前記ヒューズ回路の出力端子に接続された論理回路と、を備えたことを特徴とする半導体集積回路装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013036212A JP6073705B2 (ja) | 2013-02-26 | 2013-02-26 | ヒューズ回路及び半導体集積回路装置 |

| TW103103931A TWI585802B (zh) | 2013-02-26 | 2014-02-06 | 保險絲電路及半導體積體電路裝置 |

| CN201410049847.9A CN104009033B (zh) | 2013-02-26 | 2014-02-13 | 半导体集成电路装置 |

| KR1020140021821A KR20140106438A (ko) | 2013-02-26 | 2014-02-25 | 퓨즈 회로 및 반도체 집적 회로 장치 |

| US14/190,612 US10283303B2 (en) | 2013-02-26 | 2014-02-26 | Fuse circuit and semiconductor integrated circuit device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013036212A JP6073705B2 (ja) | 2013-02-26 | 2013-02-26 | ヒューズ回路及び半導体集積回路装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014165390A JP2014165390A (ja) | 2014-09-08 |

| JP2014165390A5 JP2014165390A5 (ja) | 2016-01-28 |

| JP6073705B2 true JP6073705B2 (ja) | 2017-02-01 |

Family

ID=51369629

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013036212A Active JP6073705B2 (ja) | 2013-02-26 | 2013-02-26 | ヒューズ回路及び半導体集積回路装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US10283303B2 (ja) |

| JP (1) | JP6073705B2 (ja) |

| KR (1) | KR20140106438A (ja) |

| CN (1) | CN104009033B (ja) |

| TW (1) | TWI585802B (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7370291B2 (ja) * | 2020-03-30 | 2023-10-27 | エイブリック株式会社 | 半導体装置 |

| CN113985335B (zh) * | 2021-09-22 | 2023-07-14 | 成都欧开科技有限公司 | 一种用于程控电阻的阻值校准方法 |

Family Cites Families (30)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5151611A (en) * | 1990-12-10 | 1992-09-29 | Westinghouse Electric Corp. | Programmable device for integrated circuits |

| JPH09213097A (ja) * | 1996-02-07 | 1997-08-15 | Hitachi Ltd | ヒューズ装置及びそれを用いた半導体集積回路装置 |

| WO1998038519A1 (fr) * | 1997-02-28 | 1998-09-03 | Asahi Kasei Electronics Co., Ltd. | Detecteur magnetique |

| JPH11233634A (ja) * | 1998-02-12 | 1999-08-27 | Mitsubishi Electric Corp | 半導体集積回路 |

| US6255893B1 (en) * | 1999-07-07 | 2001-07-03 | Intel Corporation | Method and apparatus for detection of electrical overstress |

| JP2001244338A (ja) * | 2000-02-25 | 2001-09-07 | Toshiba Corp | 半導体集積回路装置、半導体集積回路実装基板装置および半導体集積回路装置の入力保護機能解除方法 |

| JP2002076281A (ja) * | 2000-08-30 | 2002-03-15 | Seiko Instruments Inc | 半導体装置およびその製造方法 |

| TW516208B (en) * | 2001-10-03 | 2003-01-01 | Taiwan Semiconductor Mfg | Fuse structure of integrated circuits |

| JP3787591B2 (ja) * | 2002-02-14 | 2006-06-21 | セイコーインスツル株式会社 | 抵抗回路 |

| JP2004096036A (ja) * | 2002-09-04 | 2004-03-25 | Fujitsu Ten Ltd | 抵抗装置、該抵抗装置のトリミング方法、及び電源回路 |

| JP2004266173A (ja) * | 2003-03-04 | 2004-09-24 | Toshiba Corp | 半導体装置 |

| EP1609185B1 (en) * | 2003-03-20 | 2010-07-21 | Microbridge Technologies Inc. | Method for bidirectional thermal trimming of electrical resistance |

| WO2004102664A1 (ja) * | 2003-05-13 | 2004-11-25 | Fujitsu Limited | ヒューズ回路および半導体集積回路装置 |

| JP4761431B2 (ja) * | 2003-09-09 | 2011-08-31 | セイコーインスツル株式会社 | 半導体装置の製造方法 |

| US6879021B1 (en) * | 2003-10-06 | 2005-04-12 | International Business Machines Corporation | Electronically programmable antifuse and circuits made therewith |

| JP4521598B2 (ja) * | 2004-10-13 | 2010-08-11 | ルネサスエレクトロニクス株式会社 | 半導体集積回路装置、非接触電子装置並びに携帯情報端末 |

| US7208388B2 (en) * | 2005-04-08 | 2007-04-24 | Texas Instruments Incorporated | Thin film resistor head structure and method for reducing head resistivity variance |

| US7579673B2 (en) * | 2005-08-24 | 2009-08-25 | Nec Electronics Corporation | Semiconductor device having electrical fuse |

| JP4865302B2 (ja) | 2005-11-11 | 2012-02-01 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| JP5186925B2 (ja) * | 2008-01-11 | 2013-04-24 | 株式会社リコー | 半導体装置及びその製造方法 |

| JP5217468B2 (ja) * | 2008-02-01 | 2013-06-19 | 株式会社リコー | 二次電池保護用半導体装置および該二次電池保護用半導体装置を用いた電池パック、ならびに該電池パックを用いた電子機器 |

| US7915950B2 (en) * | 2008-06-20 | 2011-03-29 | Conexant Systems, Inc. | Method and algorithm of high precision on-chip global biasing using integrated resistor calibration circuits |

| JP5266920B2 (ja) * | 2008-07-15 | 2013-08-21 | 富士通セミコンダクター株式会社 | ヒューズ素子読み出し回路 |

| KR20100079186A (ko) * | 2008-12-30 | 2010-07-08 | 주식회사 동부하이텍 | 퓨징 스파크를 방지할 수 있는 퓨징 회로를 포함하는 집적 회로 |

| JP2010177612A (ja) | 2009-02-02 | 2010-08-12 | Renesas Electronics Corp | 半導体集積回路装置 |

| JP2010287644A (ja) * | 2009-06-10 | 2010-12-24 | New Japan Radio Co Ltd | 半導体装置及びその製造方法 |

| JP5558964B2 (ja) * | 2009-09-30 | 2014-07-23 | セイコーインスツル株式会社 | ボルテージレギュレータ |

| JP2012009516A (ja) * | 2010-06-22 | 2012-01-12 | Fujitsu Semiconductor Ltd | 半導体集積回路 |

| JP5752994B2 (ja) * | 2011-05-24 | 2015-07-22 | セイコーインスツル株式会社 | トリミング回路及び半導体装置 |

| MX2012006986A (es) * | 2011-06-17 | 2012-12-17 | Rab Lighting Inc | Controlador de diodo emisor de luz controlado por fotocelda. |

-

2013

- 2013-02-26 JP JP2013036212A patent/JP6073705B2/ja active Active

-

2014

- 2014-02-06 TW TW103103931A patent/TWI585802B/zh not_active IP Right Cessation

- 2014-02-13 CN CN201410049847.9A patent/CN104009033B/zh not_active Expired - Fee Related

- 2014-02-25 KR KR1020140021821A patent/KR20140106438A/ko not_active Application Discontinuation

- 2014-02-26 US US14/190,612 patent/US10283303B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20140240080A1 (en) | 2014-08-28 |

| US10283303B2 (en) | 2019-05-07 |

| TWI585802B (zh) | 2017-06-01 |

| CN104009033B (zh) | 2019-03-22 |

| JP2014165390A (ja) | 2014-09-08 |

| KR20140106438A (ko) | 2014-09-03 |

| TW201445606A (zh) | 2014-12-01 |

| CN104009033A (zh) | 2014-08-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8403559B2 (en) | Two-terminal semiconductor sensor device | |

| TWI442206B (zh) | Voltage divider circuit and magnetic sensor circuit | |

| US8525583B2 (en) | Circuit, an adjusting method, and use of a control loop | |

| US7857510B2 (en) | Temperature sensing circuit | |

| JP2014025731A (ja) | センサ装置 | |

| JP2016223974A (ja) | 温度補償回路およびセンサ装置 | |

| JP6073705B2 (ja) | ヒューズ回路及び半導体集積回路装置 | |

| JP6250418B2 (ja) | ボルテージレギュレータ | |

| JP5981890B2 (ja) | ホール素子駆動回路 | |

| US7449896B2 (en) | Current sensor using level shift circuit | |

| JP6588229B2 (ja) | 過熱保護回路並びにこれを用いた半導体集積回路装置及び車両 | |

| US9454174B2 (en) | Power supply voltage monitoring circuit, and electronic circuit including the power supply voltage monitoring circuit | |

| JP6476049B2 (ja) | 温度センサ回路 | |

| WO2020165250A1 (en) | Threshold detector of a power on reset circuit with improved accuracy for switching levels over temperature variations | |

| JP7391720B2 (ja) | 半導体集積回路装置および電流検出回路 | |

| JP2008175770A (ja) | 電位変動検出装置 | |

| TWI707221B (zh) | 電流產生電路 | |

| CN113311211B (zh) | 一种提高电源电压检测精准度的版图连接方法 | |

| US7868622B2 (en) | Circuit for detecting power supply voltage drop | |

| JP2005136664A (ja) | 発振回路 | |

| JP2016194462A (ja) | センサ装置 | |

| JP2017166890A (ja) | センサ装置 | |

| Harada | Multi-Output Octagonal MOSFET for the Common Device of Both Sensor and Circuit Design | |

| JP2016157706A (ja) | 半導体装置 | |

| US20180127264A1 (en) | Sensing device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20151204 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20151204 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20160112 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160923 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160927 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20161220 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170105 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6073705 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |