JP5573176B2 - リードフレームおよびその製造方法、ならびに半導体装置およびその製造方法 - Google Patents

リードフレームおよびその製造方法、ならびに半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP5573176B2 JP5573176B2 JP2010006035A JP2010006035A JP5573176B2 JP 5573176 B2 JP5573176 B2 JP 5573176B2 JP 2010006035 A JP2010006035 A JP 2010006035A JP 2010006035 A JP2010006035 A JP 2010006035A JP 5573176 B2 JP5573176 B2 JP 5573176B2

- Authority

- JP

- Japan

- Prior art keywords

- recess

- die pad

- lead frame

- lead

- semiconductor element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32245—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32245—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

- H01L2224/32257—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic the layer connector connecting to a bonding area disposed in a recess of the surface of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48245—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

- H01L2224/48247—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/8338—Bonding interfaces outside the semiconductor or solid-state body

- H01L2224/83385—Shape, e.g. interlocking features

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/91—Methods for connecting semiconductor or solid state bodies including different methods provided for in two or more of groups H01L2224/80 - H01L2224/90

- H01L2224/92—Specific sequence of method steps

- H01L2224/922—Connecting different surfaces of the semiconductor or solid-state body with connectors of different types

- H01L2224/9222—Sequential connecting processes

- H01L2224/92242—Sequential connecting processes the first connecting process involving a layer connector

- H01L2224/92247—Sequential connecting processes the first connecting process involving a layer connector the second connecting process involving a wire connector

Description

以下、本発明の第1の実施の形態について、図1乃至図10を参照して説明する。

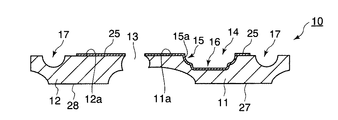

まず、図1および図2により、本実施の形態によるリードフレームの概略について説明する。図1(a)は、本実施の形態によるリードフレームを示す平面図、図1(b)は図1(a)中のAA’線に沿った断面図であり、図2は、ダイパッドの載置凹部を示す部分拡大断面図である。図3は、本実施の形態によるリードフレームの変形例を示す断面図である。

次に図4により、本実施の形態による樹脂付リードフレームの概略について説明する。図4は、本実施の形態による樹脂付リードフレームを示す断面図である。

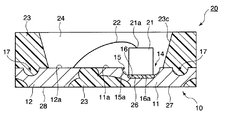

次に、図5により、本実施の形態による半導体装置について説明する。図5は、本実施の形態による半導体装置(SONタイプ)を示す断面図である。以下において、半導体素子21がLED素子からなる場合について説明するが、半導体素子21としてLED素子以外の半導体素子を用いることも可能である。

次に、図1(a)(b)に示すリードフレーム10の製造方法について、図6(a)−(f)を用いて説明する。図6(a)−(f)は、本実施の形態によるリードフレームの製造方法を示す断面図である。なお図6(a)−(f)において、リードフレーム10が複数のダイパッド11および複数のリード部12を有する場合を例にとって説明する。

次に、図5に示す半導体装置20の製造方法について、図7(a)−(f)により説明する。図7(a)−(f)は、本実施の形態による半導体装置の製造方法を示す断面図である。

次にこのような構成からなる本実施の形態の作用効果について、図8乃至図10を用いて説明する。図8は、本実施の形態による半導体装置の部分拡大断面図であり、図9は、本実施の形態による半導体装置と、比較例としての半導体装置(比較例1)とを比較して示す断面図である。図10(a)(b)は、それぞれ半導体装置の比較例2、3を示す部分拡大断面図である。

次に、本発明の第2の実施の形態による半導体装置について、図11を参照して説明する。図11は、本実施の形態による半導体装置を示す断面図である。図11に示す実施の形態は、外側樹脂部23が設けられていない点が異なるものであり、他の構成は上述した図1乃至図9に示す実施の形態と略同一である。図11において、図1乃至図9に示す実施の形態と同一部分には同一の符号を付して、詳細な説明は省略する。

次に、本発明の第3の実施の形態によるリードフレームおよび半導体装置について、図12を参照して説明する。図12は、本実施の形態によるリードフレームおよび半導体装置を示す断面図である。図12に示す実施の形態は、ダイパッド11の周囲に、リード部12が2つ設けられている点が異なるものであり、他の構成は上述した図1乃至図9に示す実施の形態と略同一である。図12において、図1乃至図9に示す実施の形態と同一部分には同一の符号を付して、詳細な説明は省略する。

11 ダイパッド

12 リード部

14 載置凹部

15 第1凹部

16 第2凹部

17 アンカー溝

18 補助接続部材

20、40、50 半導体装置

21 半導体素子

22 ボンディングワイヤ(導電部)

23 外側樹脂部

24 封止樹脂部

26 取付材料

30 樹脂付リードフレーム

Claims (13)

- LED素子を載置するリードフレームにおいて、

LED素子を載置する載置面を有するダイパッドと、

ダイパッド周囲に設けられるとともに導電部が接続されるボンディング面を有するリード部とを備え、

ダイパッドの載置面およびリード部のボンディング面には、LED素子及び導電部を取り囲む凹部を有する外側樹脂部の脱落を防止する平面角丸矩形状のアンカー溝が形成され、

前記平面角丸矩形状のアンカー溝は、ダイパッド及びリード部の前記外側樹脂部と接する面に形成されるとともに、ダイパッドとリード部との間の空間を除き、ダイパッドとリード部の双方にまたがるように形成されていることを特徴とするリードフレーム。 - 樹脂付リードフレームにおいて、

リードフレームと、

リードフレームに設けられた外側樹脂部とを備え、

リードフレームは、

LED素子を載置する載置面を有するダイパッドと、

ダイパッド周囲に設けられるとともに導電部が接続されるボンディング面を有するリード部とを有し、

ダイパッドの載置面およびリード部のボンディング面には、LED素子及び導電部を取り囲む凹部を有する外側樹脂部の脱落を防止する平面角丸矩形状のアンカー溝が形成され、

前記平面角丸矩形状のアンカー溝は、ダイパッド及びリード部の前記外側樹脂部と接する面に形成されるとともに、ダイパッドとリード部との間の空間を除き、ダイパッドとリード部の双方にまたがるように形成されていることを特徴とする樹脂付リードフレーム。 - 半導体装置において、

ダイパッドと、ダイパッド周囲に設けられたリード部とを有するリードフレームと、

リードフレームに設けられた外側樹脂部と、

リードフレームのダイパッドに載置されたLED素子と、

リードフレームのリード部と半導体素子とを電気的に接続する導電部と、

半導体素子と導電部とを封止する封止樹脂部とを備え、

リードフレームのダイパッドは、LED素子を載置する載置面を有し、

リード部は、導電部が接続されるボンディング面を有し、

ダイパッドの載置面およびリード部のボンディング面には、LED素子及び導電部を取り囲む凹部を有する外側樹脂部の脱落を防止する平面角丸矩形状のアンカー溝が形成され、

前記平面角丸矩形状のアンカー溝は、ダイパッド及びリード部の前記外側樹脂部と接する面に形成されるとともに、ダイパッドとリード部との間の空間を除き、ダイパッドとリード部の双方にまたがるように形成されていることを特徴とする半導体装置。 - 半導体素子を載置するリードフレームにおいて、

半導体素子を載置する載置面を有するダイパッドと、

ダイパッド周囲に設けられたリード部とを備え、

ダイパッドの載置面に、深さが浅い第1凹部と、第1凹部中央に位置するとともに深さが深い第2凹部とからなる載置凹部を形成したことを特徴とするリードフレーム。 - 半導体素子はLED素子からなり、第1凹部の側壁は、ダイパッドの表面側から第2凹部側に向かう湾曲面を形成し、この湾曲面は、LED素子からの光を反射する反射面として機能することを特徴とする請求項4記載のリードフレーム。

- 第1凹部はエッチングにより形成され、第2凹部はプレスにより形成されることを特徴とする請求項4または5記載のリードフレーム。

- 半導体装置において、

ダイパッドと、ダイパッド周囲に設けられたリード部とを有するリードフレームと、

リードフレームのダイパッドに載置された半導体素子と、

リードフレームのリード部と半導体素子とを電気的に接続する導電部と、

半導体素子と導電部とを封止する封止樹脂部とを備え、

リードフレームのダイパッドは、半導体素子を載置する載置面を有し、

ダイパッドの載置面に、深さが浅い第1凹部と、第1凹部中央に位置するとともに深さが深い第2凹部とからなる載置凹部を形成し、この載置凹部内に半導体素子を載置したことを特徴とする半導体装置。 - 半導体素子は、載置凹部の第2凹部内に収容された取付材料を介して載置凹部内に載置されていることを特徴とする請求項7記載の半導体装置。

- 半導体素子はLED素子からなり、このLED素子を取り囲む凹部を有する外側樹脂部が設けられ、封止樹脂部は、外側樹脂部の凹部内に充填されていることを特徴とする請求項7または8記載の半導体装置。

- 半導体素子はLED素子からなり、第1凹部の側壁は、ダイパッドの表面側から第2凹部側に向かう湾曲面を形成し、この湾曲面は、LED素子からの光を反射する反射面として機能することを特徴とする請求項7乃至9のいずれか一項記載の半導体装置。

- 第1凹部はエッチングにより形成され、第2凹部はプレスにより形成されることを特徴とする請求項7乃至10のいずれか一項記載の半導体装置。

- 半導体素子を載置する載置面を有するダイパッドと、ダイパッド周囲に設けられたリード部とを有するリードフレームの製造方法において、

金属基板を準備する工程と、

金属基板の表裏に、それぞれエッチング用レジスト層を形成する工程と、

エッチング用レジスト層を耐腐蝕膜として金属基板の表裏にエッチングを施すことにより、ダイパッドおよびリード部を形成するとともに、ダイパッドの載置面に、深さが浅い第1凹部を形成する工程と、

第1凹部の中央に、プレスにより、第1凹部より深さが深い第2凹部を形成する工程とを備えたことを特徴とするリードフレームの製造方法。 - 半導体装置の製造方法において、

請求項12記載のリードフレームの製造方法によりリードフレームを製造する工程と、 リードフレームのダイパッドの載置凹部内に半導体素子を載置する工程と、

半導体素子とリード部とを導電部により接続する工程と、

半導体素子と導電部とを封止樹脂部により封止する工程とを備えたことを特徴とする半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010006035A JP5573176B2 (ja) | 2010-01-14 | 2010-01-14 | リードフレームおよびその製造方法、ならびに半導体装置およびその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010006035A JP5573176B2 (ja) | 2010-01-14 | 2010-01-14 | リードフレームおよびその製造方法、ならびに半導体装置およびその製造方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014137195A Division JP5939474B2 (ja) | 2014-07-02 | 2014-07-02 | リードフレームおよびその製造方法、ならびに半導体装置およびその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011146524A JP2011146524A (ja) | 2011-07-28 |

| JP2011146524A5 JP2011146524A5 (ja) | 2013-10-24 |

| JP5573176B2 true JP5573176B2 (ja) | 2014-08-20 |

Family

ID=44461119

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010006035A Active JP5573176B2 (ja) | 2010-01-14 | 2010-01-14 | リードフレームおよびその製造方法、ならびに半導体装置およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5573176B2 (ja) |

Families Citing this family (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101888603B1 (ko) * | 2011-07-29 | 2018-08-14 | 엘지이노텍 주식회사 | 발광 소자 패키지 및 표시장치 |

| JP2013058739A (ja) * | 2011-08-17 | 2013-03-28 | Dainippon Printing Co Ltd | 光半導体装置用リードフレーム、樹脂付き光半導体装置用リードフレーム、光半導体装置、および、光半導体装置用リードフレームの製造方法 |

| JP5935577B2 (ja) * | 2011-08-23 | 2016-06-15 | 大日本印刷株式会社 | 光半導体装置用リードフレーム、樹脂付き光半導体装置用リードフレーム、および光半導体装置 |

| JP6205686B2 (ja) * | 2011-08-23 | 2017-10-04 | 大日本印刷株式会社 | 光半導体装置 |

| JP2013125776A (ja) * | 2011-12-13 | 2013-06-24 | Dainippon Printing Co Ltd | リードフレーム、樹脂付リードフレームおよびその製造方法、ならびに半導体装置の製造方法 |

| JP6078948B2 (ja) | 2012-01-20 | 2017-02-15 | 日亜化学工業株式会社 | 発光装置用パッケージ成形体及びそれを用いた発光装置 |

| JP2013179271A (ja) * | 2012-01-31 | 2013-09-09 | Rohm Co Ltd | 発光装置および発光装置の製造方法 |

| KR101888444B1 (ko) * | 2012-02-28 | 2018-08-16 | 엘지디스플레이 주식회사 | 발광 다이오드 패키지 및 그 제조 방법 |

| JP5888098B2 (ja) * | 2012-04-27 | 2016-03-16 | 大日本印刷株式会社 | Led素子搭載用リードフレーム、樹脂付リードフレーム、多面付ledパッケージ、ledパッケージの製造方法および半導体素子搭載用リードフレーム |

| JP6071034B2 (ja) * | 2012-04-27 | 2017-02-01 | 大日本印刷株式会社 | Led素子搭載用リードフレーム、樹脂付リードフレーム、多面付ledパッケージ、ledパッケージの製造方法および半導体素子搭載用リードフレーム |

| JP2013008979A (ja) * | 2012-08-02 | 2013-01-10 | Toshiba Corp | 半導体パッケージ |

| US9548261B2 (en) * | 2013-03-05 | 2017-01-17 | Nichia Corporation | Lead frame and semiconductor device |

| JP6291713B2 (ja) | 2013-03-14 | 2018-03-14 | 日亜化学工業株式会社 | 発光素子実装用基体及びそれを備える発光装置、並びにリードフレーム |

| KR102066093B1 (ko) * | 2013-09-11 | 2020-01-14 | 엘지디스플레이 주식회사 | 발광 다이오드 패키지와 이를 이용한 백라이트 유닛 및 액정 표시 장치 |

| JP6460390B2 (ja) * | 2015-02-04 | 2019-01-30 | 大口マテリアル株式会社 | リードフレーム、光半導体装置用樹脂付きリードフレーム及びこれらの製造方法、並びに光半導体装置 |

| JP6056914B2 (ja) * | 2015-07-07 | 2017-01-11 | 大日本印刷株式会社 | 樹脂付リードフレーム、半導体装置および照明装置 |

| JP2017076809A (ja) * | 2016-12-05 | 2017-04-20 | 大日本印刷株式会社 | 樹脂付リードフレーム、半導体装置、照明装置 |

| JP6350683B2 (ja) * | 2017-01-06 | 2018-07-04 | 大日本印刷株式会社 | Led素子搭載用リードフレーム、樹脂付リードフレーム、多面付ledパッケージ、ledパッケージの製造方法および半導体素子搭載用リードフレーム |

| KR101810494B1 (ko) * | 2017-06-07 | 2017-12-20 | 주식회사 정진넥스텍 | 발광다이오드 패키지용 리드 프레임 조립체, 그 제조 방법 및 발광다이오드 패키지 |

| US10707384B2 (en) * | 2017-07-06 | 2020-07-07 | Nichia Corporation | Light-emitting device |

| JP7064325B2 (ja) * | 2017-12-18 | 2022-05-10 | スタンレー電気株式会社 | 半導体発光装置、および、それを用いた半導体発光装置の製造方法 |

| JP2019161238A (ja) * | 2019-06-17 | 2019-09-19 | マクセルホールディングス株式会社 | 半導体装置用基板およびその製造方法、半導体装置 |

| JP6733786B2 (ja) * | 2019-07-16 | 2020-08-05 | 日亜化学工業株式会社 | パッケージ、発光装置及びそれらの製造方法 |

| JP7011685B2 (ja) * | 2020-07-10 | 2022-01-27 | マクセル株式会社 | 半導体装置 |

| JP7389363B2 (ja) * | 2021-05-26 | 2023-11-30 | 日亜化学工業株式会社 | 発光装置 |

| CN113359248B (zh) * | 2021-06-02 | 2022-11-15 | 青岛海信宽带多媒体技术有限公司 | 一种光模块 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100335480B1 (ko) * | 1999-08-24 | 2002-05-04 | 김덕중 | 칩 패드가 방열 통로로 사용되는 리드프레임 및 이를 포함하는반도체 패키지 |

| JP2001185651A (ja) * | 1999-12-27 | 2001-07-06 | Matsushita Electronics Industry Corp | 半導体装置およびその製造方法 |

| JP5183583B2 (ja) * | 2000-12-28 | 2013-04-17 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP2004214265A (ja) * | 2002-12-27 | 2004-07-29 | Kyushu Hitachi Maxell Ltd | 半導体装置および半導体装置の製造方法 |

| JP4359195B2 (ja) * | 2004-06-11 | 2009-11-04 | 株式会社東芝 | 半導体発光装置及びその製造方法並びに半導体発光ユニット |

| JP4865525B2 (ja) * | 2006-08-03 | 2012-02-01 | イッツウェル カンパニー リミテッド | Sml型発光ダイオードランプ用素子およびその製造方法 |

| JP5004601B2 (ja) * | 2007-01-22 | 2012-08-22 | パナソニック株式会社 | パッケージ部品の製造方法および半導体装置の製造方法 |

-

2010

- 2010-01-14 JP JP2010006035A patent/JP5573176B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2011146524A (ja) | 2011-07-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5573176B2 (ja) | リードフレームおよびその製造方法、ならびに半導体装置およびその製造方法 | |

| JP5582382B2 (ja) | リードフレームおよびその製造方法、ならびに半導体装置およびその製造方法 | |

| JP6187549B2 (ja) | 光半導体装置用リードフレーム、樹脂付き光半導体装置用リードフレーム、光半導体装置、および、光半導体装置用リードフレームの製造方法 | |

| JP5818149B2 (ja) | 樹脂付リードフレーム、半導体装置、照明装置、樹脂付リードフレームの製造方法および半導体装置の製造方法 | |

| JP5710128B2 (ja) | 樹脂付リードフレームの製造方法 | |

| WO2013024560A1 (ja) | 発光装置 | |

| JP2017220684A (ja) | 光半導体装置用リードフレーム、樹脂付き光半導体装置用リードフレーム、光半導体装置、および、樹脂付き光半導体装置用リードフレームの製造方法、ならびに光半導体装置の製造方法 | |

| JP6103409B2 (ja) | 光半導体装置用リードフレーム、樹脂付き光半導体装置用リードフレーム、および光半導体装置 | |

| JP5375630B2 (ja) | 樹脂付リードフレームおよびその製造方法、ならびにled素子パッケージおよびその製造方法 | |

| JP5817894B2 (ja) | リードフレームおよびその製造方法、ならびに半導体装置およびその製造方法 | |

| JP5758459B2 (ja) | 樹脂付リードフレーム、リードフレーム、半導体装置および樹脂付リードフレームの製造方法 | |

| JP6115836B2 (ja) | 樹脂付リードフレーム、リードフレーム、半導体装置および樹脂付リードフレームの製造方法 | |

| JP6065081B2 (ja) | リードフレームおよびその製造方法、ならびに半導体装置およびその製造方法 | |

| JP6103410B2 (ja) | 光半導体装置用リードフレーム、樹脂付き光半導体装置用リードフレーム、および光半導体装置 | |

| JP5939474B2 (ja) | リードフレームおよびその製造方法、ならびに半導体装置およびその製造方法 | |

| JP2017076809A (ja) | 樹脂付リードフレーム、半導体装置、照明装置 | |

| JP2017076806A (ja) | 樹脂付リードフレーム、リードフレーム、半導体装置および樹脂付リードフレームの製造方法 | |

| JP6026397B2 (ja) | 樹脂付リードフレームの製造方法 | |

| JP5908874B2 (ja) | 樹脂付リードフレーム、リードフレーム、半導体装置および樹脂付リードフレームの製造方法 | |

| JP5941614B2 (ja) | 半導体装置およびその製造方法 | |

| JP2013165221A (ja) | リードフレーム、樹脂付リードフレーム、及び半導体装置 | |

| JP5867261B2 (ja) | 光半導体装置用リードフレーム、光半導体装置、および、それらの製造方法 | |

| JP6056914B2 (ja) | 樹脂付リードフレーム、半導体装置および照明装置 | |

| JP5998609B2 (ja) | 光半導体装置 | |

| JP6123200B2 (ja) | 光半導体装置用リードフレーム、樹脂付き光半導体装置用リードフレーム、リードフレームの多面付け体、樹脂付きリードフレームの多面付け体、光半導体装置、光半導体装置の多面付け体 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20121109 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130909 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140304 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140502 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140603 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140616 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5573176 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: R3D02 |