JP5476127B2 - ポスト−シード成層工程 - Google Patents

ポスト−シード成層工程 Download PDFInfo

- Publication number

- JP5476127B2 JP5476127B2 JP2009549722A JP2009549722A JP5476127B2 JP 5476127 B2 JP5476127 B2 JP 5476127B2 JP 2009549722 A JP2009549722 A JP 2009549722A JP 2009549722 A JP2009549722 A JP 2009549722A JP 5476127 B2 JP5476127 B2 JP 5476127B2

- Authority

- JP

- Japan

- Prior art keywords

- seed layer

- photoresist

- seed

- wafer

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000000034 method Methods 0.000 title claims description 56

- 230000008569 process Effects 0.000 title claims description 20

- 238000013517 stratification Methods 0.000 title description 6

- 239000002184 metal Substances 0.000 claims description 39

- 238000007747 plating Methods 0.000 claims description 18

- 238000000151 deposition Methods 0.000 claims description 12

- 239000007787 solid Substances 0.000 claims description 12

- 238000007772 electroless plating Methods 0.000 claims description 3

- 238000009713 electroplating Methods 0.000 claims description 3

- 239000012212 insulator Substances 0.000 claims 1

- 229920002120 photoresistant polymer Polymers 0.000 description 54

- 239000010410 layer Substances 0.000 description 42

- 235000012431 wafers Nutrition 0.000 description 25

- 239000002344 surface layer Substances 0.000 description 15

- 230000008901 benefit Effects 0.000 description 12

- 239000000463 material Substances 0.000 description 10

- 230000008021 deposition Effects 0.000 description 6

- 230000000694 effects Effects 0.000 description 6

- 238000000059 patterning Methods 0.000 description 6

- 238000005530 etching Methods 0.000 description 4

- 238000012545 processing Methods 0.000 description 4

- BGTFCAQCKWKTRL-YDEUACAXSA-N chembl1095986 Chemical compound C1[C@@H](N)[C@@H](O)[C@H](C)O[C@H]1O[C@@H]([C@H]1C(N[C@H](C2=CC(O)=CC(O[C@@H]3[C@H]([C@@H](O)[C@H](O)[C@@H](CO)O3)O)=C2C=2C(O)=CC=C(C=2)[C@@H](NC(=O)[C@@H]2NC(=O)[C@@H]3C=4C=C(C(=C(O)C=4)C)OC=4C(O)=CC=C(C=4)[C@@H](N)C(=O)N[C@@H](C(=O)N3)[C@H](O)C=3C=CC(O4)=CC=3)C(=O)N1)C(O)=O)=O)C(C=C1)=CC=C1OC1=C(O[C@@H]3[C@H]([C@H](O)[C@@H](O)[C@H](CO[C@@H]5[C@H]([C@@H](O)[C@H](O)[C@@H](C)O5)O)O3)O[C@@H]3[C@H]([C@@H](O)[C@H](O)[C@@H](CO)O3)O[C@@H]3[C@H]([C@H](O)[C@@H](CO)O3)O)C4=CC2=C1 BGTFCAQCKWKTRL-YDEUACAXSA-N 0.000 description 3

- 239000006059 cover glass Substances 0.000 description 3

- 230000000873 masking effect Effects 0.000 description 3

- 239000000047 product Substances 0.000 description 3

- 230000015572 biosynthetic process Effects 0.000 description 2

- 230000002411 adverse Effects 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 239000006227 byproduct Substances 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000001627 detrimental effect Effects 0.000 description 1

- 230000009969 flowable effect Effects 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 238000010297 mechanical methods and process Methods 0.000 description 1

- 230000005226 mechanical processes and functions Effects 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000008520 organization Effects 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 239000012056 semi-solid material Substances 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 239000011343 solid material Substances 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 239000011345 viscous material Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76898—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics formed through a semiconductor substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/481—Internal lead connections, e.g. via connections, feedthrough structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1204—Optical Diode

- H01L2924/12044—OLED

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Electroplating Methods And Accessories (AREA)

Description

Claims (12)

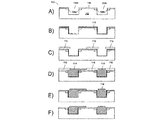

- バイアを有するウェハ上にシード層を成層する工程と、

前記シード層の上部にパターン付きレジストを形成する工程であって、前記パターン付きレジストは、前記シード層の少なくとも一部分を露出する1つ以上の開口を有し、前記パターン付きレジストが前記バイアの少なくとも一部に覆いかぶさるように、前記1つ以上の開口は、少なくとも部分的に、前記シード層を内部に有するバイア上に配置される、工程と、

前記シード層の前記露出した少なくとも一部分を金属層でめっきする工程であって、前記金属層は、前記シード層の上面の上方に延在する、工程と、

前記レジストを除去する工程と、

前記レジストを除去する工程によって露出した前記シード層の少なくとも一部分を除去する工程と、

を備える方法。 - 前記シード層の前記露出した少なくとも一部分を金属層でめっきする前記工程は、前記シード層の前記露出した少なくとも一部分に無電解めっきプロセスを行う工程を備える、請求項1記載の方法。

- 前記シード層の前記露出した少なくとも一部分を金属層でめっきする前記工程は、前記シード層の前記露出した少なくとも一部分に電気めっきプロセスを行う工程を備える、請求項1記載の方法。

- 前記シード層の少なくとも一部分を除去する前記工程は、前記金属層の高さが少なくとも前記シード層の厚さ分減少するまで、前記シード層の前記露出した少なくとも一部分と前記金属層とを同時にエッチングする工程を備える、請求項1記載の方法。

- 前記パターン付きレジストは、前記ウェハの表面上に配置された少なくとも1つの開口であって、前記ウェハの表面に沿って集積回路経路の少なくとも一部分を画成するように構成された少なくとも1つの開口を有する、請求項1記載の方法。

- 前記パターン付きレジストは、前記バイアに充填された前記金属層の隆起領域を画成するように構成された少なくとも1つの開口を有する、請求項1記載の方法。

- 前記パターン付きレジストは、前記バイアの前記開口の少なくとも一部分を覆うように構成された固体レジストである、請求項1記載の方法。

- 前記金属層の一部分が、前記バイアの前記開口を超えて延在し、かつ、配線パターンを与えるように構成される、請求項1記載の方法。

- 前記レジストを除去する前記工程は、前記金属層の側部を露出する工程を備える、請求項1記載の方法。

- 前記シード層が前記ウェハ上に成層される前に、前記ウェハ上に絶縁体を成層する工程を更に備える、請求項1記載の方法。

- 前記レジストは固体レジストである、請求項1記載の方法。

- 請求項1乃至11のいずれか1項に記載の方法を用いて形成されるデバイス。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/675,268 US7598163B2 (en) | 2007-02-15 | 2007-02-15 | Post-seed deposition process |

| US11/675,268 | 2007-02-15 | ||

| PCT/US2008/053982 WO2008101093A1 (en) | 2007-02-15 | 2008-02-14 | Post-seed deposition process |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010519738A JP2010519738A (ja) | 2010-06-03 |

| JP2010519738A5 JP2010519738A5 (ja) | 2010-10-28 |

| JP5476127B2 true JP5476127B2 (ja) | 2014-04-23 |

Family

ID=39512688

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009549722A Active JP5476127B2 (ja) | 2007-02-15 | 2008-02-14 | ポスト−シード成層工程 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US7598163B2 (ja) |

| EP (1) | EP2111635A1 (ja) |

| JP (1) | JP5476127B2 (ja) |

| KR (1) | KR101118798B1 (ja) |

| CN (1) | CN101632166B (ja) |

| WO (1) | WO2008101093A1 (ja) |

Families Citing this family (28)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5065674B2 (ja) * | 2006-12-28 | 2012-11-07 | ルネサスエレクトロニクス株式会社 | 半導体集積回路装置の製造方法 |

| JP5302522B2 (ja) | 2007-07-02 | 2013-10-02 | スパンション エルエルシー | 半導体装置及びその製造方法 |

| WO2009023462A1 (en) * | 2007-08-10 | 2009-02-19 | Spansion Llc | Semiconductor device and method for manufacturing thereof |

| US8264065B2 (en) * | 2009-10-23 | 2012-09-11 | Synopsys, Inc. | ESD/antenna diodes for through-silicon vias |

| TWI392069B (zh) * | 2009-11-24 | 2013-04-01 | Advanced Semiconductor Eng | 封裝結構及其封裝製程 |

| TWI446420B (zh) | 2010-08-27 | 2014-07-21 | Advanced Semiconductor Eng | 用於半導體製程之載體分離方法 |

| TWI445152B (zh) | 2010-08-30 | 2014-07-11 | Advanced Semiconductor Eng | 半導體結構及其製作方法 |

| US9007273B2 (en) | 2010-09-09 | 2015-04-14 | Advances Semiconductor Engineering, Inc. | Semiconductor package integrated with conformal shield and antenna |

| TWI434387B (zh) | 2010-10-11 | 2014-04-11 | Advanced Semiconductor Eng | 具有穿導孔之半導體裝置及具有穿導孔之半導體裝置之封裝結構及其製造方法 |

| TWI527174B (zh) | 2010-11-19 | 2016-03-21 | 日月光半導體製造股份有限公司 | 具有半導體元件之封裝結構 |

| TWI445155B (zh) | 2011-01-06 | 2014-07-11 | Advanced Semiconductor Eng | 堆疊式封裝結構及其製造方法 |

| US8853819B2 (en) | 2011-01-07 | 2014-10-07 | Advanced Semiconductor Engineering, Inc. | Semiconductor structure with passive element network and manufacturing method thereof |

| US8541883B2 (en) | 2011-11-29 | 2013-09-24 | Advanced Semiconductor Engineering, Inc. | Semiconductor device having shielded conductive vias |

| US8975157B2 (en) | 2012-02-08 | 2015-03-10 | Advanced Semiconductor Engineering, Inc. | Carrier bonding and detaching processes for a semiconductor wafer |

| US8963316B2 (en) | 2012-02-15 | 2015-02-24 | Advanced Semiconductor Engineering, Inc. | Semiconductor device and method for manufacturing the same |

| US8786060B2 (en) | 2012-05-04 | 2014-07-22 | Advanced Semiconductor Engineering, Inc. | Semiconductor package integrated with conformal shield and antenna |

| US9153542B2 (en) | 2012-08-01 | 2015-10-06 | Advanced Semiconductor Engineering, Inc. | Semiconductor package having an antenna and manufacturing method thereof |

| US8937387B2 (en) | 2012-11-07 | 2015-01-20 | Advanced Semiconductor Engineering, Inc. | Semiconductor device with conductive vias |

| US8952542B2 (en) | 2012-11-14 | 2015-02-10 | Advanced Semiconductor Engineering, Inc. | Method for dicing a semiconductor wafer having through silicon vias and resultant structures |

| US9406552B2 (en) | 2012-12-20 | 2016-08-02 | Advanced Semiconductor Engineering, Inc. | Semiconductor device having conductive via and manufacturing process |

| KR101441632B1 (ko) * | 2012-12-28 | 2014-09-23 | (재)한국나노기술원 | 글라스 기반 프로브 카드용 스페이스 트랜스포머의 제조방법 및 이에 의해 제조된 글라스 기반 프로브 카드용 스페이스 트랜스포머 |

| US8841751B2 (en) | 2013-01-23 | 2014-09-23 | Advanced Semiconductor Engineering, Inc. | Through silicon vias for semiconductor devices and manufacturing method thereof |

| US9978688B2 (en) | 2013-02-28 | 2018-05-22 | Advanced Semiconductor Engineering, Inc. | Semiconductor package having a waveguide antenna and manufacturing method thereof |

| US9089268B2 (en) | 2013-03-13 | 2015-07-28 | Advanced Semiconductor Engineering, Inc. | Neural sensing device and method for making the same |

| US9173583B2 (en) | 2013-03-15 | 2015-11-03 | Advanced Semiconductor Engineering, Inc. | Neural sensing device and method for making the same |

| US8987734B2 (en) | 2013-03-15 | 2015-03-24 | Advanced Semiconductor Engineering, Inc. | Semiconductor wafer, semiconductor process and semiconductor package |

| US11758666B2 (en) * | 2020-09-14 | 2023-09-12 | Innolux Corporation | Manufacturing method of metal structure |

| US20230096301A1 (en) * | 2021-09-29 | 2023-03-30 | Catlam, Llc. | Circuit Board Traces in Channels using Electroless and Electroplated Depositions |

Family Cites Families (44)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5071518A (en) | 1989-10-24 | 1991-12-10 | Microelectronics And Computer Technology Corporation | Method of making an electrical multilayer interconnect |

| EP0516866A1 (en) | 1991-05-03 | 1992-12-09 | International Business Machines Corporation | Modular multilayer interwiring structure |

| JP3313432B2 (ja) * | 1991-12-27 | 2002-08-12 | 株式会社東芝 | 半導体装置及びその製造方法 |

| US5603847A (en) | 1993-04-07 | 1997-02-18 | Zycon Corporation | Annular circuit components coupled with printed circuit board through-hole |

| US5587119A (en) | 1994-09-14 | 1996-12-24 | E-Systems, Inc. | Method for manufacturing a coaxial interconnect |

| US5814889A (en) | 1995-06-05 | 1998-09-29 | Harris Corporation | Intergrated circuit with coaxial isolation and method |

| US5872051A (en) | 1995-08-02 | 1999-02-16 | International Business Machines Corporation | Process for transferring material to semiconductor chip conductive pads using a transfer substrate |

| US6946716B2 (en) * | 1995-12-29 | 2005-09-20 | International Business Machines Corporation | Electroplated interconnection structures on integrated circuit chips |

| US6310484B1 (en) | 1996-04-01 | 2001-10-30 | Micron Technology, Inc. | Semiconductor test interconnect with variable flexure contacts |

| US7052941B2 (en) | 2003-06-24 | 2006-05-30 | Sang-Yun Lee | Method for making a three-dimensional integrated circuit structure |

| JP3176307B2 (ja) | 1997-03-03 | 2001-06-18 | 日本電気株式会社 | 集積回路装置の実装構造およびその製造方法 |

| US6620731B1 (en) | 1997-12-18 | 2003-09-16 | Micron Technology, Inc. | Method for fabricating semiconductor components and interconnects with contacts on opposing sides |

| US5962922A (en) | 1998-03-18 | 1999-10-05 | Wang; Bily | Cavity grid array integrated circuit package |

| US6222276B1 (en) | 1998-04-07 | 2001-04-24 | International Business Machines Corporation | Through-chip conductors for low inductance chip-to-chip integration and off-chip connections |

| US6122187A (en) | 1998-11-23 | 2000-09-19 | Micron Technology, Inc. | Stacked integrated circuits |

| US6316737B1 (en) | 1999-09-09 | 2001-11-13 | Vlt Corporation | Making a connection between a component and a circuit board |

| JP3386029B2 (ja) | 2000-02-09 | 2003-03-10 | 日本電気株式会社 | フリップチップ型半導体装置及びその製造方法 |

| JP2001338947A (ja) | 2000-05-26 | 2001-12-07 | Nec Corp | フリップチップ型半導体装置及びその製造方法 |

| US6577013B1 (en) | 2000-09-05 | 2003-06-10 | Amkor Technology, Inc. | Chip size semiconductor packages with stacked dies |

| US6740576B1 (en) | 2000-10-13 | 2004-05-25 | Bridge Semiconductor Corporation | Method of making a contact terminal with a plated metal peripheral sidewall portion for a semiconductor chip assembly |

| JP2002134545A (ja) | 2000-10-26 | 2002-05-10 | Oki Electric Ind Co Ltd | 半導体集積回路チップ及び基板、並びにその製造方法 |

| JP4608763B2 (ja) | 2000-11-09 | 2011-01-12 | 日本電気株式会社 | 半導体装置 |

| WO2002047139A2 (en) * | 2000-12-04 | 2002-06-13 | Ebara Corporation | Methode of forming a copper film on a substrate |

| US6512300B2 (en) | 2001-01-10 | 2003-01-28 | Raytheon Company | Water level interconnection |

| US6747347B2 (en) | 2001-08-30 | 2004-06-08 | Micron Technology, Inc. | Multi-chip electronic package and cooling system |

| US6599778B2 (en) | 2001-12-19 | 2003-07-29 | International Business Machines Corporation | Chip and wafer integration process using vertical connections |

| US7135777B2 (en) | 2002-05-03 | 2006-11-14 | Georgia Tech Research Corporation | Devices having compliant wafer-level input/output interconnections and packages using pillars and methods of fabrication thereof |

| US6939789B2 (en) | 2002-05-13 | 2005-09-06 | Taiwan Semiconductor Manufacturing Co., Ltd. | Method of wafer level chip scale packaging |

| SG111069A1 (en) | 2002-06-18 | 2005-05-30 | Micron Technology Inc | Semiconductor devices including peripherally located bond pads, assemblies, packages, and methods |

| JP2004103911A (ja) * | 2002-09-11 | 2004-04-02 | Shinko Electric Ind Co Ltd | 配線形成方法 |

| SG111972A1 (en) | 2002-10-17 | 2005-06-29 | Agency Science Tech & Res | Wafer-level package for micro-electro-mechanical systems |

| US20040108217A1 (en) * | 2002-12-05 | 2004-06-10 | Dubin Valery M. | Methods for forming copper interconnect structures by co-plating of noble metals and structures formed thereby |

| WO2004064159A1 (ja) * | 2003-01-15 | 2004-07-29 | Fujitsu Limited | 半導体装置及び三次元実装半導体装置、並びに半導体装置の製造方法 |

| TWI251313B (en) | 2003-09-26 | 2006-03-11 | Seiko Epson Corp | Intermediate chip module, semiconductor device, circuit board, and electronic device |

| US20050104027A1 (en) | 2003-10-17 | 2005-05-19 | Lazarev Pavel I. | Three-dimensional integrated circuit with integrated heat sinks |

| US7276787B2 (en) | 2003-12-05 | 2007-10-02 | International Business Machines Corporation | Silicon chip carrier with conductive through-vias and method for fabricating same |

| JP4114660B2 (ja) * | 2003-12-16 | 2008-07-09 | セイコーエプソン株式会社 | 半導体装置の製造方法、半導体装置、回路基板、電子機器 |

| US20050179120A1 (en) * | 2003-12-16 | 2005-08-18 | Koji Yamaguchi | Process for producing semiconductor device, semiconductor device, circuit board and electronic equipment |

| US7230318B2 (en) | 2003-12-24 | 2007-06-12 | Agency For Science, Technology And Research | RF and MMIC stackable micro-modules |

| US7157310B2 (en) | 2004-09-01 | 2007-01-02 | Micron Technology, Inc. | Methods for packaging microfeature devices and microfeature devices formed by such methods |

| JP4246132B2 (ja) | 2004-10-04 | 2009-04-02 | シャープ株式会社 | 半導体装置およびその製造方法 |

| US7348671B2 (en) | 2005-01-26 | 2008-03-25 | Micron Technology, Inc. | Vias having varying diameters and fills for use with a semiconductor device and methods of forming semiconductor device structures including same |

| US7838997B2 (en) * | 2005-06-14 | 2010-11-23 | John Trezza | Remote chip attachment |

| US7402515B2 (en) | 2005-06-28 | 2008-07-22 | Intel Corporation | Method of forming through-silicon vias with stress buffer collars and resulting devices |

-

2007

- 2007-02-15 US US11/675,268 patent/US7598163B2/en active Active

-

2008

- 2008-02-14 EP EP08729880A patent/EP2111635A1/en not_active Withdrawn

- 2008-02-14 KR KR1020097018804A patent/KR101118798B1/ko active IP Right Grant

- 2008-02-14 WO PCT/US2008/053982 patent/WO2008101093A1/en active Application Filing

- 2008-02-14 JP JP2009549722A patent/JP5476127B2/ja active Active

- 2008-02-14 CN CN200880004533XA patent/CN101632166B/zh active Active

Also Published As

| Publication number | Publication date |

|---|---|

| WO2008101093B1 (en) | 2008-10-30 |

| US20080200022A1 (en) | 2008-08-21 |

| CN101632166A (zh) | 2010-01-20 |

| WO2008101093A1 (en) | 2008-08-21 |

| EP2111635A1 (en) | 2009-10-28 |

| KR20090115203A (ko) | 2009-11-04 |

| CN101632166B (zh) | 2012-11-28 |

| KR101118798B1 (ko) | 2012-03-21 |

| JP2010519738A (ja) | 2010-06-03 |

| US7598163B2 (en) | 2009-10-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5476127B2 (ja) | ポスト−シード成層工程 | |

| KR101655331B1 (ko) | 비아 상호접속을 제조하는 방법 | |

| KR101178823B1 (ko) | 반도체 칩 및 그 제조 방법 | |

| JP4773307B2 (ja) | 半導体装置の製造方法 | |

| DE102010000417B4 (de) | Elektronisches Bauelement und Verfahren zu seiner Herstellung | |

| US8580687B2 (en) | Semiconductor structure and method for making same | |

| JP2006516824A5 (ja) | ||

| KR101452791B1 (ko) | 파인 피치 상호접속부 및 그 제조 방법 | |

| JP6528550B2 (ja) | 半導体装置およびその製造方法 | |

| JP5230061B2 (ja) | 半導体装置及びその製造方法 | |

| US20130130439A1 (en) | Formed metallic heat sink substrate, circuit system, and fabrication methods | |

| DE102017109670B4 (de) | Herstellungsverfahren für ein Chippackage mit Seitenwandmetallisierung | |

| CN108122833B (zh) | 制作半导体装置的方法 | |

| US9455239B2 (en) | Integrated circuit chip and fabrication method | |

| JP5834563B2 (ja) | 半導体装置の製造方法 | |

| DE102012109868B4 (de) | Verfahren zur Herstellung einer Halbleitervorrichtung | |

| TWI441291B (zh) | 半導體封裝件及其製造方法 | |

| DE102018112979A1 (de) | Monolithisch integrierter chip einschliesslich aktiver elektrischer komponenten und passiver elektrischer komponenten mit chipkantenstabilisierungsstrukturen | |

| KR100602093B1 (ko) | 반도체 소자 및 그 제조방법 | |

| KR100613344B1 (ko) | 반도체 소자의 제조 방법 | |

| JP5810693B2 (ja) | 電子デバイス及びその製造方法 | |

| DE102021105577A1 (de) | Mikroelektromechanisches system und verfahren zu dessen herstellung | |

| KR970003840A (ko) | 반도체 소자의 다층 금속 배선 형성방법 | |

| KR20000033687A (ko) | 반도체 장치의 금속배선 형성방법 | |

| JPS63287034A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20100407 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20100407 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100908 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100908 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130305 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130531 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130621 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130912 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131007 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140106 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140127 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140207 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5476127 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |