JP5466818B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP5466818B2 JP5466818B2 JP2007251130A JP2007251130A JP5466818B2 JP 5466818 B2 JP5466818 B2 JP 5466818B2 JP 2007251130 A JP2007251130 A JP 2007251130A JP 2007251130 A JP2007251130 A JP 2007251130A JP 5466818 B2 JP5466818 B2 JP 5466818B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor device

- gate electrode

- silicon

- transistor

- vertical mos

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 34

- 238000009792 diffusion process Methods 0.000 claims description 23

- 230000002093 peripheral effect Effects 0.000 claims 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 50

- 229910052710 silicon Inorganic materials 0.000 description 50

- 239000010703 silicon Substances 0.000 description 50

- 238000004519 manufacturing process Methods 0.000 description 26

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 15

- 229910052814 silicon oxide Inorganic materials 0.000 description 15

- 229910052581 Si3N4 Inorganic materials 0.000 description 14

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 14

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 9

- 239000000758 substrate Substances 0.000 description 7

- 229910052785 arsenic Inorganic materials 0.000 description 4

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 4

- 239000003990 capacitor Substances 0.000 description 4

- 238000005530 etching Methods 0.000 description 4

- 238000010438 heat treatment Methods 0.000 description 4

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 239000007772 electrode material Substances 0.000 description 2

- 239000012535 impurity Substances 0.000 description 2

- 238000000034 method Methods 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7827—Vertical transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66666—Vertical transistors

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Semiconductor Memories (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Electrodes Of Semiconductors (AREA)

Description

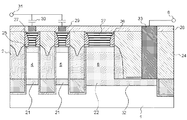

図1に示すように、シリコン基板1の主表面に形成された第1の導電型のゲート電極2を共有した複数の角柱縦型MOSトランジスタ3,4,5のゲート電極2の電位供給6が、角柱縦型MOSトランジスタの第1の角柱3,4,5と同時に形成され、かつ、一部分にゲート絶縁膜7を有しない、かつ、ゲート電極2の導電型と同じ第1の導電型である第2の柱8の拡散層22を介して行われていて、ゲート電極2への電位供給が、第2の柱8上にコンタクトされた電極・配線6により行なう構造とする。

第1の実施例の製法は、以下の通りである。

第1の実施例によれば、DRAMのセルトランジスタを縦型MOSトランジスタ3,4,5で構成し、シリコン柱8をワード線電位供給に利用できるので、以下のような効果がある。

図17に示すように、シリコン基板1の主表面に形成された第1の導電型のゲート電極2を共有した複数の角柱縦型MOSトランジスタ4,5のゲート電極2への電位供給6が、角柱縦型MOSトランジスタの第1の角柱4,5と同時に形成され、かつ、一部分にゲート絶縁膜7を有しない、かつ、ゲート電極2の導電型と同じ第1の導電型である第2の柱8の拡散層22を介して行われていて、ゲート電極の電位供給6が、第2の柱8下に形成された第1の導電型の拡散層32より行なわれ、ゲート電極の電位供給6用のコンタクト33が上記拡散層32に形成されている構造とする。なお、図17では、シリコン柱8上にサイドウオール26、エピタキシャル成長層27を同様に形成しているが、シリコン柱8上のマスク層12を除去せずに上部への不純物注入を行わず、サイドウオール26、エピタキシャル成長層27を形成しない構成や、上部への不純物注入を行った後、開口部を絶縁膜で埋め込み、サイドウオール26、エピタキシャル成長層27を形成しない構成としても問題はない。

第2の実施例の製法は、第1の実施例と同じであるが、上記図2で示した構造を図18に示した構造に置き換えることと、上記図4で示した構造を図19に示した構造に置き換えることと、上記図5で示した構造を図20に示した構造に置き換えることと、上記図6で示した構造を図21に示した構造に置き換えることにより実現できる。

第2の実施例によれば、第1の実施例と同様の効果を有する。なお、ゲート電極の電位供給6に必要な面積が増加するものの、コンタクト33の配置に自由度が増す。

次に第3の実施例は、図22に示すように、第1の導電型のゲート電極を共有した複数の角柱縦型MOSトランジスタ4,5のゲート電極2への電位供給が、角柱縦型MOSトランジスタ4,5の第1の角柱と同時に形成され、かつ、少なくとも一部分にゲート絶縁膜を有しない、かつ、ゲート電極の導電型と同じ第1の導電型である第2の柱8の拡散層22を介して行われていて、ゲート電極の電位供給が、第2の柱下に形成された第1の導電型の拡散層を共有した縦型MOSトランジスタ34を動作させることにより行なう構造とする。

第3の実施例の製法は、第1の実施例及び第2の実施例の製法を組み合わせたものであり、詳細は省略する。

第3の実施例によれば、第1の実施例と同様の効果を有する。なお、ゲート電極の電位供給6に必要な縦型MOSトランジスタ34分の面積が増加するものの、縦型MOSトランジスタ34の上部拡散層25からの電位供給が可能になるので配置に自由度が増す。

2・・・ゲート電極

3、4、5、34・・・縦型MOSトランジスタ

6・・・ワード線電位供給

7・・・ゲート酸化膜

8・・・第2の柱

11、13、15、24,28・・・シリコン酸化膜

12・・・シリコン窒化膜

16、19・・・レジスト膜

17・・・シリコン露出面

18・・・ゲート酸化膜

20、23・・・多結晶シリコン膜

21・・・下部拡散層

22・・・n型層

25・・・上部拡散層

26・・・サイドウォール

27・・・エピタキシャル成長層

29、33・・・電極

30・・・キャパシタ

31・・・プレート電位供給

32・・・下部拡散層と同じ導電型層

Claims (5)

- 第1の導電型のゲート電極を共有した複数の縦型MOSトランジスタを有する半導体装置であって、

該複数の縦型MOSトランジスタが、側面周囲に形成された第1のゲート絶縁膜を介して前記ゲート電極と側面周囲で対峙して成る第1の半導体柱を有し、

前記半導体装置は、第1の導電型であり、側面周囲に形成された第2のゲート絶縁膜を介して前記ゲート電極と側面周囲で対峙して成り、少なくとも一部分の前記第2のゲート絶縁膜を除去した部分で前記ゲート電極と接している第2の半導体柱を有し、

前記複数の縦型MOSトランジスタの共有されるゲート電極への電位供給が、前記第2の半導体柱を介して行われることを特徴とする半導体装置。 - 請求項1に記載の半導体装置において、前記複数の縦型MOSトランジスタの共有されるゲート電極への電位供給が、前記第2の半導体柱上にコンタクトされた電極・配線により行われていることを特徴とする半導体装置。

- 請求項1に記載の半導体装置において、前記複数の縦型MOSトランジスタの共有されるゲート電極への電位供給が、前記第2の半導体柱下に形成された第1の導電型の拡散層にコンタクトされた電極・配線により行われていることを特徴とする半導体装置。

- 請求項1に記載の半導体装置において、前記複数の縦型MOSトランジスタの共有されるゲート電極への電位供給が、前記第2の半導体柱下に形成された第1の導電型の拡散層を共有した縦型MOSトランジスタを動作させることにより行われていることを特徴とする半導体装置。

- 前記半導体装置は、第1の導電型のゲート電極を共有した複数の縦型MOSトランジスタからなるトランジスタ列が複数配置され、アレイ状に形成された半導体装置であって、各トランジスタ列と交差する行方向に、各トランジスタ列の一つのトランジスタ同士が、前記第1の半導体柱下に形成された第1の導電型の拡散層で接続され、各行方向でトランジスタ下にビットラインを構成していることを特徴する請求項1乃至4のいずれか1項に記載の半導体装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007251130A JP5466818B2 (ja) | 2007-09-27 | 2007-09-27 | 半導体装置 |

| US12/239,048 US7902573B2 (en) | 2007-09-27 | 2008-09-26 | Semiconductor device including vertical MOS transistors |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007251130A JP5466818B2 (ja) | 2007-09-27 | 2007-09-27 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009081377A JP2009081377A (ja) | 2009-04-16 |

| JP2009081377A5 JP2009081377A5 (ja) | 2013-05-23 |

| JP5466818B2 true JP5466818B2 (ja) | 2014-04-09 |

Family

ID=40507190

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007251130A Expired - Fee Related JP5466818B2 (ja) | 2007-09-27 | 2007-09-27 | 半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7902573B2 (ja) |

| JP (1) | JP5466818B2 (ja) |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5588123B2 (ja) * | 2009-05-22 | 2014-09-10 | ピーエスフォー ルクスコ エスエイアールエル | 半導体装置及びその製造方法 |

| JP2011086679A (ja) | 2009-10-13 | 2011-04-28 | Elpida Memory Inc | 半導体装置および半導体装置の製造方法 |

| JP2011171500A (ja) | 2010-02-18 | 2011-09-01 | Elpida Memory Inc | 半導体装置及びその製造方法 |

| JP5711481B2 (ja) | 2010-08-19 | 2015-04-30 | ピーエスフォー ルクスコ エスエイアールエルPS4 Luxco S.a.r.l. | 半導体装置 |

| JP2012094762A (ja) * | 2010-10-28 | 2012-05-17 | Elpida Memory Inc | 半導体装置および半導体装置の製造方法 |

| US9431400B2 (en) * | 2011-02-08 | 2016-08-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor memory device and method for manufacturing the same |

| JP2013135130A (ja) * | 2011-12-27 | 2013-07-08 | Elpida Memory Inc | 半導体装置及びその製造方法 |

| JP2013239568A (ja) | 2012-05-15 | 2013-11-28 | Ps4 Luxco S A R L | 半導体装置 |

| US8987796B2 (en) | 2012-08-17 | 2015-03-24 | Ps4 Luxco S.A.R.L. | Semiconductor device having semiconductor pillar |

| US20150270268A1 (en) * | 2012-11-06 | 2015-09-24 | Atsushi Fujikawa | Semiconductor device |

| WO2014203303A1 (ja) * | 2013-06-17 | 2014-12-24 | ユニサンティス エレクトロニクス シンガポール プライベート リミテッド | 半導体装置の製造方法、及び、半導体装置 |

| JP5759077B1 (ja) * | 2013-08-07 | 2015-08-05 | ユニサンティス エレクトロニクス シンガポール プライベート リミテッドUnisantis Electronics Singapore Pte Ltd. | 半導体装置の製造方法、及び、半導体装置 |

| JP5936653B2 (ja) * | 2014-08-06 | 2016-06-22 | ユニサンティス エレクトロニクス シンガポール プライベート リミテッドUnisantis Electronics Singapore Pte Ltd. | 半導体装置 |

| JP5986618B2 (ja) * | 2014-12-04 | 2016-09-06 | ユニサンティス エレクトロニクス シンガポール プライベート リミテッドUnisantis Electronics Singapore Pte Ltd. | 半導体装置 |

| JP6156883B2 (ja) * | 2015-02-06 | 2017-07-05 | ユニサンティス エレクトロニクス シンガポール プライベート リミテッドUnisantis Electronics Singapore Pte Ltd. | 半導体装置の製造方法及び半導体装置 |

| JP6285393B2 (ja) * | 2015-06-04 | 2018-02-28 | ユニサンティス エレクトロニクス シンガポール プライベート リミテッドUnisantis Electronics Singapore Pte Ltd. | 半導体装置の製造方法、及び、半導体装置 |

| JP6174174B2 (ja) * | 2016-02-05 | 2017-08-02 | ユニサンティス エレクトロニクス シンガポール プライベート リミテッドUnisantis Electronics Singapore Pte Ltd. | 半導体装置の製造方法、及び、半導体装置 |

| JP6114425B2 (ja) * | 2016-03-11 | 2017-04-12 | ユニサンティス エレクトロニクス シンガポール プライベート リミテッドUnisantis Electronics Singapore Pte Ltd. | 半導体装置の製造方法、及び、半導体装置 |

| JP6143913B2 (ja) * | 2016-04-06 | 2017-06-07 | ユニサンティス エレクトロニクス シンガポール プライベート リミテッドUnisantis Electronics Singapore Pte Ltd. | 半導体装置の製造方法及び半導体装置 |

| JP6284585B2 (ja) * | 2016-07-15 | 2018-02-28 | ユニサンティス エレクトロニクス シンガポール プライベート リミテッドUnisantis Electronics Singapore Pte Ltd. | 半導体装置の製造方法及び半導体装置 |

| JP6328832B2 (ja) * | 2017-07-05 | 2018-05-23 | ユニサンティス エレクトロニクス シンガポール プライベート リミテッドUnisantis Electronics Singapore Pte Ltd. | 半導体装置の製造方法、及び、半導体装置 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2703970B2 (ja) * | 1989-01-17 | 1998-01-26 | 株式会社東芝 | Mos型半導体装置 |

| JPH03231460A (ja) * | 1990-02-06 | 1991-10-15 | Nec Corp | 半導体記憶装置 |

| JP2877462B2 (ja) * | 1990-07-23 | 1999-03-31 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| JP3315429B2 (ja) * | 1991-04-23 | 2002-08-19 | キヤノン株式会社 | 半導体装置及びその製造方法 |

| JP2002094027A (ja) | 2000-09-11 | 2002-03-29 | Toshiba Corp | 半導体記憶装置とその製造方法 |

| JP2003218242A (ja) * | 2002-01-24 | 2003-07-31 | Hitachi Ltd | 不揮発性半導体記憶装置およびその製造方法 |

| DE10231966A1 (de) * | 2002-07-15 | 2004-02-12 | Infineon Technologies Ag | Feldeffekttransistor, zugehörige Verwendung und zugehöriges Herstellungsverfahren |

| JP4108537B2 (ja) | 2003-05-28 | 2008-06-25 | 富士雄 舛岡 | 半導体装置 |

-

2007

- 2007-09-27 JP JP2007251130A patent/JP5466818B2/ja not_active Expired - Fee Related

-

2008

- 2008-09-26 US US12/239,048 patent/US7902573B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20090085098A1 (en) | 2009-04-02 |

| JP2009081377A (ja) | 2009-04-16 |

| US7902573B2 (en) | 2011-03-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5466818B2 (ja) | 半導体装置 | |

| JP5383049B2 (ja) | 垂直方向のチャンネルを有するアクセス素子、これを含む半導体装置、及びアクセス素子の形成方法 | |

| US7723184B2 (en) | Semiconductor device and manufacture method therefor | |

| US8294205B2 (en) | Semiconductor device and method of forming semiconductor device | |

| US20170025424A1 (en) | Self-Aligned Source For Split-Gate Non-volatile Memory Cell | |

| TWI553778B (zh) | 具有埋入式位元線之半導體裝置 | |

| JP5522622B2 (ja) | 半導体記憶装置及びその製造方法 | |

| JP4658977B2 (ja) | 半導体装置の製造方法 | |

| US10535710B2 (en) | Methods of forming integrated circuitry | |

| JP2008511996A (ja) | 半導体の構造とトランジスタ、および半導体の構造とトランジスタとを形成する方法 | |

| SG183450A1 (en) | Floating body cell structures, devices including same, and methods for forming same | |

| JP2009065024A (ja) | 半導体装置及びその製造方法 | |

| US20160233218A1 (en) | Semiconductor device | |

| JP2009177080A (ja) | 半導体記憶装置 | |

| KR20120078917A (ko) | 반도체 소자 및 그 형성 방법 | |

| WO2014112496A1 (ja) | 半導体装置及びその製造方法 | |

| JP2009267208A (ja) | 半導体装置及びその製造方法 | |

| JP2012174790A (ja) | 半導体装置及びその製造方法 | |

| JP2010050133A (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP2010219325A (ja) | 半導体記憶装置及びその製造方法 | |

| JP2009182303A (ja) | 半導体装置及びその製造方法 | |

| US8530311B2 (en) | Method of manufacturing semiconductor device | |

| TW200534355A (en) | Semiconductor structure | |

| JP2013219179A (ja) | 半導体装置及びその製造方法 | |

| JP2011199084A (ja) | 半導体記憶装置及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100810 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130417 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20130730 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131220 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140107 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140127 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |