JP5448263B2 - 表示装置、半導体装置、モジュール及び電子機器 - Google Patents

表示装置、半導体装置、モジュール及び電子機器 Download PDFInfo

- Publication number

- JP5448263B2 JP5448263B2 JP2010251043A JP2010251043A JP5448263B2 JP 5448263 B2 JP5448263 B2 JP 5448263B2 JP 2010251043 A JP2010251043 A JP 2010251043A JP 2010251043 A JP2010251043 A JP 2010251043A JP 5448263 B2 JP5448263 B2 JP 5448263B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- pixel

- row

- video signal

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3266—Details of drivers for scan electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3275—Details of drivers for data electrodes

- G09G3/3291—Details of drivers for data electrodes in which the data driver supplies a variable data voltage for setting the current through, or the voltage across, the light-emitting elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0861—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor with additional control of the display period without amending the charge stored in a pixel memory, e.g. by means of additional select electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0243—Details of the generation of driving signals

- G09G2310/0251—Precharge or discharge of pixel before applying new pixel voltage

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/027—Details of drivers for data electrodes, the drivers handling digital grey scale data, e.g. use of D/A converters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/02—Details of power systems and of start or stop of display operation

- G09G2330/021—Power management, e.g. power saving

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2018—Display of intermediate tones by time modulation using two or more time intervals

- G09G3/2022—Display of intermediate tones by time modulation using two or more time intervals using sub-frames

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

- G09G3/3241—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element the current through the light-emitting element being set using a data current provided by the data driver, e.g. by using a two-transistor current mirror

- G09G3/325—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element the current through the light-emitting element being set using a data current provided by the data driver, e.g. by using a two-transistor current mirror the data current flowing through the driving transistor during a setting phase, e.g. by using a switch for connecting the driving transistor to the data driver

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3258—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the voltage across the light-emitting element

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal (AREA)

- Control Of El Displays (AREA)

- Electroluminescent Light Sources (AREA)

- Liquid Crystal Display Device Control (AREA)

Description

に関し、好適には信号によって輝度が変化する電流駆動型表示素子で形成された画素や電

圧によって輝度が変化する電圧駆動型表示素子で形成された画素や、液晶等の電圧によっ

て透過率が変化する表示素子で形成された画素や、信号線駆動回路や走査線駆動回路を含

む表示装置に関する。

表示装置が注目を浴びている。このような自発光型の表示装置に用いられる表示素子とし

て、例えば、有機発光ダイオード(OLED(Organic Light Emitt

ing Diode)、有機EL素子、エレクトロルミネッセンス素子ともいう)が注目

を集めており、ELディスプレイ等に用いられるようになってきている。OLED等の表

示素子は自発光型であるため、液晶ディスプレイに比べて視認性が高く、バックライトが

不要で応答速度が速いとの利点を有している。また、表示素子の輝度は、当該表示素子に

流れる電流値によって制御される。

003を有し、画素部7003には、複数の画素7004が設けられている(図61)。

また、複数の画素7004は、行方向に配置された走査線(G1〜Gm)と列方向に配置

された信号線(S1〜Sn)に対応するようにマトリクス状に配置されている。信号線駆

動回路7001はビデオ信号を信号線S1〜Snに出力し、走査線駆動回路7002は行

方向に配置された画素7004を選択するための信号を走査線G1〜Gmに出力する。そ

して、選択された行の各列に対応する画素に信号線駆動回路7001からのビデオ信号が

書き込まれる。各画素は書き込まれた信号を保存する。

3の全ての画素に信号の書き込みが行われると画素7004への書き込み期間が終了する

。画素の発光動作時には、画素7004は書き込まれた信号を一定期間保存しているため

、画素へ書き込まれた信号に応じた状態を維持する。そして、書き込み動作と発光動作を

繰り返し行うことにより、動画を表示している。

線駆動回路7001は、例えば、パルス出力回路7011、第1のラッチ回路7012お

よび第2のラッチ回路7013を有している。パルス出力回路7011は、入力されたス

タートパルス信号(S−SP)等のタイミングに従ってサンプリングパルスを順次第1の

ラッチ回路7012に出力する。第1のラッチ回路7012には、ビデオ信号(Vide

o Data)が入力される。そのタイミングは、パルス出力回路7011から出力され

たサンプリングパルスに従って制御される。そして、第1のラッチ回路7012の各段に

ビデオ信号が保持される。つまり、パルス出力回路7011から出力されたサンプリング

パルスによって、第1のラッチ回路7012の各段のラッチ回路が動作している。

に、第2のラッチ回路7013にラッチパルス(Latch Pulse)が入力され、

第1のラッチ回路7012に保持されていたビデオ信号は一斉に第2のラッチ回路701

3に転送され、第2のラッチ回路7013で保持されるようになる。そして、第2のラッ

チ回路7013からビデオ信号(一行分)が同時に信号線S1〜Snへ出力される。そし

て、第2のラッチ回路7013から信号線に信号が出力されている間に、次の行のデータ

がビデオ信号から第1のラッチ回路7012に入力される。そして、最終段まで入力され

た後、ラッチパルスによって第1のラッチ回路7012から第2のラッチ回路へ信号が転

送される。このような動作を繰り返し行うことにより、全ての画素に信号を入力し動画の

表示を行っている。

タル階調方式がある。アナログ方式には、表示素子の発光強度をアナログ制御する方式と

表示素子の発光時間をアナログ制御する方式がある。アナログ階調方式においては表示素

子の発光強度をアナログ制御する方式がよく用いられている。しかし、発光強度をアナロ

グ制御する方式は、画素毎の薄膜トランジスタ(以下、「TFT」ともいう)の特性のバ

ラツキの影響を受けやすく、画素毎の輝度にもバラツキが生じてしまう。一方、デジタル

階調方式はデジタル制御で表示素子をオンオフさせ、階調を表現している。デジタル階調

方式の場合、画素毎の輝度の均一性に優れているが、発光・非発光の2状態しかないため

、このままでは、2階調しか表現できない。そこで、別の手法を組み合わせて、多階調化

を図ることが行われている。多階調化のための手法としては、例えば、画素の発光面積に

重みをつけて(1画素を複数の領域に分割して領域毎に発光または非発光を制御する)そ

の選択により階調表示を行う面積階調方式がある。また、発光時間に重みをつけて(1フ

レームを複数のサブフレームに分割してサブフレーム毎に画素の発光または非発光を制御

する)その選択により階調表示を行う時間階調方式がある。一般的に、デジタル階調方式

の場合には、高精細化にも適している時間階調法が用いられることが多い。(例えば、特

許文献1)

かしながら、高精細化が進むにつれ、画素数が増えることにより信号の書き込みを行う画

素数も増加することになる。さらに、高階調表示を行うためにも、サブフレーム数を増加

しなければならない。その結果、画素への信号の書き込みの回数が増加する。

ングパルスを第1のラッチ回路へ入力するため、パルス出力回路では1行分の信号を最初

の列から最後の列まで転送させるという動作を行っており、画素数の増加に伴いますます

消費電力の増加が問題となってくる。

のビデオ信号の書き込み回数を減らし、消費電力の低減を図ることが可能な表示装置を提

供することを課題とする。

画素部と、ビデオ信号を信号線に入力する信号線駆動回路と、前記ビデオ信号を書き込む

画素の行を選択する走査線駆動回路とを有し、前記信号線駆動回路はシフトレジスタを備

え、前記走査線駆動回路に選択される行の画素に書き込むビデオ信号と前記選択される行

の一行後の画素に書き込もうとするビデオ信号とが等しいとき、前記シフトレジスタで信

号の転送を行わない手段を有することを特徴としている。

配置された画素部と、ビデオ信号を信号線に入力する信号線駆動回路と、前記ビデオ信号

を書き込む画素の行を選択する走査線駆動回路とを有し、前記信号線駆動回路はシフトレ

ジスタを備え、前記走査線駆動回路に選択される行の画素に書き込むビデオ信号と前記選

択される行の一行後の画素に書き込もうとするビデオ信号とが連続した複数の列において

等しいとき、前記連続した複数の列において前記シフトレジスタで信号の転送を行わない

手段を有することを特徴としている。

配置された画素部と、ビデオ信号を信号線に入力する信号線駆動回路と、前記ビデオ信号

を書き込む画素の行を選択する走査線駆動回路とを有し、前記信号線駆動回路はシフトレ

ジスタとラッチ回路とを備え、前記ラッチ回路は前記シフトレジスタから供給されるサン

プリングパルスに基づいて前記ビデオ信号を保持する手段を有し、前記ラッチ回路に保持

されたビデオ信号と前記ラッチ回路に書き込もうとするビデオ信号とが等しいとき、前記

ラッチ回路へサンプリングパルスの供給を行わない手段を有することを特徴としている。

配置された画素部と、ビデオ信号を信号線に入力する信号線駆動回路と、前記ビデオ信号

を書き込む画素の行を選択する走査線駆動回路とを有し、前記信号線駆動回路はシフトレ

ジスタとラッチ回路とを備え、前記ラッチ回路は前記シフトレジスタから供給されるサン

プリングパルスに基づいて前記ビデオ信号を保持する手段を有し、走査線駆動回路に選択

される行の画素に書き込むビデオ信号と前記選択される行の一行後の画素に書き込もうと

するビデオ信号とが等しい列を有するとき、前記等しい列において前記ラッチ回路へサン

プリングパルスの供給を行わない手段を有することを特徴としている。

配置された画素部と、ビデオ信号を信号線に入力する信号線駆動回路と、前記ビデオ信号

を書き込む画素の行を選択する走査線駆動回路とを有し、前記信号線駆動回路はシフトレ

ジスタとラッチ回路とを備え、前記ラッチ回路は前記シフトレジスタから供給されるサン

プリングパルスに基づいて前記ビデオ信号を保持する手段を有し、前記走査線駆動回路に

選択される行の画素に書き込むビデオ信号と前記選択される行の一行後の画素に書き込も

うとするビデオ信号とが連続した複数の列において等しいとき、前記連続した複数の列に

おいて前記シフトレジスタで信号の転送を行わない手段を有することを特徴としている。

配置された画素部と、ビデオ信号を信号線に入力する信号線駆動回路と、前記ビデオ信号

を書き込む画素の行を選択する走査線駆動回路とを有し、前記信号線駆動回路はシフトレ

ジスタと第1のラッチ回路と第2のラッチ回路とを備え、前記第1のラッチ回路は前記シ

フトレジスタから供給されるサンプリングパルスに基づいて前記ビデオ信号を保持する手

段を有し、前記第2のラッチ回路は前記第1のラッチ回路から供給される前記ビデオ信号

を保持する手段を有し、前記第2のラッチ回路に保持されたビデオ信号と前記第1のラッ

チ回路に書き込もうとするビデオ信号とが等しいとき、前記第1のラッチ回路にサンプリ

ングパルスの供給を行わない手段を有することを特徴としている。

配置された画素部と、ビデオ信号を信号線に入力する信号線駆動回路と、前記ビデオ信号

を書き込む画素の行を選択する走査線駆動回路とを有し、前記信号線駆動回路はシフトレ

ジスタと第1のラッチ回路と第2のラッチ回路とを備え、前記第1のラッチ回路は前記シ

フトレジスタから供給されるサンプリングパルスに基づいて前記ビデオ信号を保持する手

段を有し、前記第2のラッチ回路は前記第1のラッチ回路から供給される前記ビデオ信号

を保持する手段を有し、前記走査線駆動回路に選択される行の画素に書き込むビデオ信号

と前記選択される行の一行後の画素に書き込もうとするビデオ信号とが等しい列を有する

とき、前記等しい列において前記第1のラッチ回路へサンプリングパルスの供給を行わな

い手段を有することを特徴としている。

配置された画素部と、ビデオ信号を信号線に入力する信号線駆動回路と、前記ビデオ信号

を書き込む画素の行を選択する走査線駆動回路とを有し、前記信号線駆動回路はシフトレ

ジスタと第1のラッチ回路と第2のラッチ回路とを備え、前記第1のラッチ回路は前記シ

フトレジスタから供給されるサンプリングパルスに基づいて前記ビデオ信号を保持する手

段を有し、前記第2のラッチ回路は前記第1のラッチ回路から供給される前記ビデオ信号

を保持する手段を有し、前記走査線駆動回路に選択される行の画素に書き込むビデオ信号

と前記選択される行の一行後の画素に書き込もうとするビデオ信号とが連続した複数の列

において等しいとき、前記連続した複数の列において前記シフトレジスタで信号の転送を

行わない手段を有することを特徴としている。

配置された画素部と、ビデオ信号を信号線に入力する信号線駆動回路と、前記ビデオ信号

を書き込む画素の行を選択する走査線駆動回路とを有し、前記走査線駆動回路は、選択さ

れる行の画素に書き込もうとするビデオ信号と前記選択される行の画素に保存されたビデ

オ信号とが等しいとき、前記選択される行の画素へのビデオ信号の書き込みを行わない手

段を有し、前記信号線駆動回路はシフトレジスタを備え、前記走査線駆動回路に選択され

る行の画素に書き込むビデオ信号と前記選択される行の一行後の画素に書き込もうとする

ビデオ信号とが等しいとき、前記シフトレジスタで信号の転送を行わない手段を有するこ

とを特徴としている。

配置された画素部と、ビデオ信号を信号線に入力する信号線駆動回路と、前記ビデオ信号

を書き込む画素の行を選択する走査線駆動回路とを有し、前記走査線駆動回路は、選択さ

れる行の画素に書き込もうとするビデオ信号と前記選択される行の画素に保存されたビデ

オ信号とが等しいとき、前記選択される行の画素を選択しない手段を有し、前記信号線駆

動回路はシフトレジスタを備え、前記走査線駆動回路に選択される行の画素に書き込むビ

デオ信号と前記選択される行の一行後の画素に書き込もうとするビデオ信号とが等しいと

き、前記シフトレジスタで信号の転送を行わない手段を有することを特徴としている。

流の流れを制御できるものなら、どのような構成でもよい。トランジスタでもよいし、ダ

イオードでもよいし、それらを組み合わせた論理回路でもよい。よって、スイッチとして

トランジスタを用いる場合、そのトランジスタは、単なるスイッチとして動作するため、

トランジスタの極性(導電型)は特に限定されない。ただし、オフ電流が少ない方が望ま

しい場合、オフ電流が少ない方の極性のトランジスタを用いることが望ましい。オフ電流

が少ないトランジスタとしては、LDD領域を設けているものやマルチゲート構造にして

いるもの等がある。また、スイッチとして動作させるトランジスタのソース端子の電位が

、低電位側電源(Vss、GND、0Vなど)に近い状態で動作する場合はNチャネル型

を、反対に、ソース端子の電位が、高電位側電源(Vddなど)に近い状態で動作する場

合はPチャネル型を用いることが望ましい。なぜなら、ゲートとソース間電圧の絶対値を

大きくできるため、スイッチとして、動作させやすいからである。なお、Nチャネル型と

Pチャネル型の両方を用いて、CMOS型のスイッチにしてもよい。

。したがって、間に別の素子やスイッチなどが配置されていてもよい。

むEL素子)やフィールドエミッションディスプレイ(FED)で用いる素子、液晶ディ

スプレイ(LCD)、プラズマディスプレイ(PDP)、電子ペーパーディスプレイ、デ

ジタルマイクロミラーデバイス(DMD)、圧電セラミックディスプレイ、強誘電性LC

D、反強誘電性LCD、SED方式平面型ディスプレイ(SED:Surface−co

nduction Electron−emitter Disply)など、どのよう

な表示素子でもよい。なお、時間階調方式を用いているものや、メモリ性のある画素を有

しているもの(画素にSRAMやDRAMなどを有しているものや、メモリ性素子(信号

を記憶できるような素子)を有しているもの)などに好適である。

晶シリコンに代表される非単結晶半導体膜を用いた薄膜トランジスタ(TFT)、半導体

基板やSOI基板を用いて形成されるトランジスタ、MOS型トランジスタ、接合型トラ

ンジスタ、バイポーラトランジスタ、有機半導体やカーボンナノチューブを用いたトラン

ジスタ、その他のトランジスタを適用することができる。また、トランジスタが配置され

ている基板の種類に限定はなく、単結晶基板、SOI基板、ガラス基板、プラスチック基

板などに配置することが出来る。

ンジスタでもよいし、どのような基板上に形成されていてもよい。したがって、回路の全

てガラス基板上に形成されていてもよいし、プラスチック基板に形成されていてもよいし

、単結晶基板に形成されていてもよいし、SOI基板上に形成されていてもよいし、どの

ような基板上に形成されていてもよい。あるいは、回路の一部が、ある基板に形成されて

おり、回路の別の一部が、別の基板に形成されていてもよい。つまり、回路の全てが同じ

基板上に形成されていなくてもよい。例えば、回路の一部は、ガラス基板上にTFTを用

いて形成し、回路の別の一部は、単結晶基板上に形成し、そのICチップをCOG(Ch

ip On Glass)で接続してガラス基板上に配置してもよい。あるいは、そのI

CチップをTAB(Tape Auto Bonding)やプリント基板を用いてガラ

ス基板と接続してもよい。

B(青)の色要素からなるフルカラー表示装置の場合には、一画素とはRの色要素やGの

色要素やBの色要素のいずれか一をいうものとする。

合わせたいわゆる格子状に配置されている場合はもちろんのこと、三色の色要素(例えば

RGB)でフルカラー表示を行う場合に、1つの画像の最小要素を表す三つの色要素の画

素がいわゆるデルタ配置されている場合も含むものとする。

)を含む回路を有する装置をいう。また、液晶表示装置とは、液晶素子を含む表示装置を

いう。

することができる。また、画素への信号の書き込みの回数を減らすことができ、消費電力

の低減を図ることが可能な表示装置を提供することができる。

明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様

々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実

施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の

構成において、同じものを指す符号は異なる図面間で共通して用いる場合がある。

き込みを行うビデオ信号と1行前に書き込まれたビデオ信号との比較、またはある行に新

たに書き込みを行うビデオ信号と既にその行の画素に書き込まれたビデオ信号との比較を

行い、サンプリングパルスの出力や画素へのビデオ信号の書き込みを行うかどうか制御す

る。そのため、本発明の表示装置は大きく分けて2つの構成を適用する。

画素へビデオ信号の書き込みを行う際に、1行前(例えば、(i−1)行)に書き込まれ

たビデオ信号と次の行(i行)に書き込みを行おうとするビデオ信号とを比較し、同じで

ある場合に信号線駆動回路101でのサンプリングパルスの生成を行わない構成とする。

なお、ここで、1行前((i−1)行)に書き込まれたビデオ信号と書き込みを行おうと

するビデオ信号とを比較するとは、1行前の各列に対応する画素に書き込まれたビデオ信

号と新たに書き込みを行う行(i行)の各列に対応する画素に書き込むビデオ信号を、同

一の信号線に接続された列毎で比較することをいう。

その行の各列に対応する画素に書き込まれて保持されているビデオ信号と新たにその行に

書き込みを行おうとするビデオ信号とを比較し、同じである場合にその行に対応する画素

にビデオ信号の書き込みを行わない構成とする。なお、ここで、既にその行の各列に対応

する画素に書き込まれて保持されているビデオ信号と新たに書き込みを行おうとするビデ

オ信号とを比較するとは、既にその行に書き込まれているビデオ信号と新たにその行に書

き込みを行おうとするビデオ信号とを、同一の信号線に接続された列毎で比較することを

いう。

れているビデオ信号と新たにその行に書き込みを行おうとするビデオ信号とがその行に対

応する各列の画素同士を比較した場合に全て同じである場合に適用する。一方、第1の構

成では、1行前の各列に対応する画素に書き込まれたビデオ信号と新たに書き込みを行う

行(i行)の各列に対応する画素に書き込むビデオ信号とが全て同じである場合に限らず

適用することができる。

であり、第1の構成と第2の構成はそれぞれ適用してもよいし、組み合わせて適用するこ

ともできる。

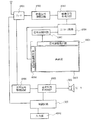

3とを有している(図1)。画素部103には、走査線G1〜Gmと信号線S1〜Snと

に対応してマトリクス状に配置された画素104が設けられており、各画素104は書き

込まれた信号を保存する手段を有している。

LKB)、スタートパルス信号(G_SP)等の信号が入力される。ただし、これに限定

されない。

w)信号を繰り返す信号であり、クロック反転信号(G_CLKB)は、クロック信号(

G_CLK)と極性の反転する信号である。そして、これらの信号により、走査線駆動回

路102の同期をとったり、処理の実行のタイミングの制御を行ったりする。よって、走

査線駆動回路102にスタートパルス信号(G_SP)が入力されると、クロック信号や

クロック反転信号に従って、各走査線G1〜Gmにそれぞれの画素の行を選択するタイミ

ングの走査信号(ゲート選択パルス)が生成される。この走査信号は、走査線駆動回路1

02に接続された走査線を介して、画素部103に設けられた複数の画素行を一つずつ順

に選択するタイミングの信号である。

信号を入力することにより、信号を書き込む画素の行を選択する。つまり、画素を選択す

る信号が入力された走査線Giに接続された画素の行が選択される。画素が選択されると

信号線を介してそこに信号が入力される。また、本発明では、走査線駆動回路102に転

送制御信号(G_ENABLEt)やサンプリング制御信号(G_ENABLEp)を入

力し、サンプリングパルスの生成の制御を行う。具体的には、既にその行に書き込まれて

保持されているビデオ信号と新たにその行に書き込みを行おうとするビデオ信号とを比較

し、同じである場合にその行に対応する走査線の選択を行わずビデオ信号の書き込みを行

わない。

LKB)、スタートパルス信号(S_SP)、ビデオ信号(Video Data)等の

信号が入力される。ただし、これに限定されない。

号を繰り返す信号であり、クロック反転信号(S_CLKB)は、クロック信号(S_C

LK)と極性の反転する信号である。そして、これらの信号により、信号線駆動回路10

1の同期をとったり、処理の実行のタイミングの制御を行ったりする。よって、信号線駆

動回路101にスタートパルス信号(S_SP)が入力されると、クロック信号やクロッ

ク反転信号に従って、画素の列に対応したサンプリングパルスが生成される。サンプリン

グパルスは、ある画素へ書き込まれるビデオ信号(Video Data)が信号線駆動

回路101に入力されているときに、当該ビデオ信号をその画素の列にデータとして変換

するためのタイミングを制御する信号である。従って、このサンプリングパルスにより、

シリアルのデータとして信号線駆動回路101に入力されるビデオ信号のデータをパラレ

ルのビデオ信号のデータにすることができる。なお、線順次方式の表示装置の場合には、

このパラレルのビデオ信号のデータは、信号線駆動回路101で保持され、一列分を同時

に信号線S1〜Snのそれぞれへ入力される。また、点順次方式の場合には、サンプリン

グパルスのタイミングに従ってシリアルのビデオ信号のデータをパラレルのビデオ信号の

データとして順々に信号線S1〜Snのそれぞれの列に入力する。このように、信号線駆

動回路101は、それぞれ各列の画素に応じたビデオ信号を信号線S1〜Snへ入力する

。

信号の書き込みを行う画素の行が選択される。そして、信号線駆動回路101から信号線

S1〜Snに入力されたビデオ信号は、選択された行に対応する各列の画素104に書き

込まれ、各画素104は書き込まれたビデオ信号のデータを一定期間保存する。また、本

発明では、信号線駆動回路101に転送制御信号(S_ENABLEt)やサンプリング

制御信号(S_ENABLEp)を入力し、サンプリングパルスの生成の制御を行う。具

体的には、1行前((i−1)行目)に書き込まれたビデオ信号と次の行(i行目)に新

たに書き込みを行うビデオ信号とを列毎に比較し、同じ列がある場合に信号線駆動回路1

01でのサンプリングパルスの生成を行わなかったり、途中で停止する構成とする。

オ信号が書き込まれると画素へのビデオ信号の書き込みが終了する。なお、各画素は、書

き込まれたビデオ信号のデータを一定期間保持することによって、点灯又は非点灯の状態

を維持することができる。また、各画素の点灯又は非点灯の状態を制御することによって

、表示装置における階調を表現することができる。例えば、画素104の発光時間の長さ

を制御することにより階調を表現することができる。

ができる。また、静止画表示の場合においても、画像が書き換えられる度に書き込み動作

と発光動作が行われる。

本実施の形態では、本発明の表示装置の一例に関して図面を参照して説明する。具体的

には、ある行を選択して当該選択された行にビデオ信号の書き込みを行う際に、ある行に

書き込みを行うビデオ信号と1行前に画素に書き込まれたビデオ信号とを比較する構成に

関して説明する。

2と、画素部103とを有している。画素部103には、走査線G1〜Gmと信号線S1

〜Snとに対応してマトリクス状に配置された画素104が設けられており、画素104

は書き込まれた信号を保存する手段を有している。また、信号線駆動回路101は、パル

ス出力回路201と、第1のラッチ回路202と、第2のラッチ回路203とを有してい

る。

(S−CLK)、クロック反転信号(S−CLKB)のタイミングに従ってサンプリング

パルスを順次第1のラッチ回路202に出力する。第1のラッチ回路202には、ビデオ

信号(Video Data)が入力され、パルス出力回路201から出力されたサンプ

リングパルスが入力されるタイミングに従って、各段にビデオ信号が入力されて保持され

る。つまり、パルス出力回路201から出力されたサンプリングパルスによって、第1の

ラッチ回路202の各段のラッチ回路が動作している。

、水平帰線期間中に、第2のラッチ回路203にラッチパルス(Latch Pulse

)が入力され、第1のラッチ回路202に保持されていたデジタルビデオ信号は、一斉に

第2のラッチ回路203に転送される。その後、第2のラッチ回路203に保持されたデ

ジタルビデオ信号は1行分が同時に信号線S1〜Snへ出力される。

)が入力されている。そして、転送制御信号のレベルによりパルス出力回路201から第

1のラッチ回路202へのサンプリングパルスの出力が制御される。つまり、転送制御信

号により、第1のラッチ回路202にビデオ信号を入力するかどうかの制御を行うことが

できる。第1のラッチ回路202へビデオ信号の入力を行うかどうかは、画素部103の

各行において1行前((i−1)行目)のビデオ信号と新たに書き込みを行う次の後(i

行目)のビデオ信号とを列毎に比較して、前の行で画素に書き込まれたビデオ信号と異な

る場合のみ第1のラッチ回路202へサンプリングパルスを出力して、当該第1のラッチ

回路202へ新たなビデオ信号の書き込みを行う。

サンプリングパルスを出力して当該第1のラッチ回路202にビデオ信号書き込むのでは

なく、サンプリングパルスの生成を選択的に制御することにより、消費電力を低減するこ

とができる。

3を用いてより詳しく説明する。図3では、選択された行のある列以降の画素において、

新たに書き込みを行うビデオ信号が一行前にその列以降の画素に書き込まれたビデオ信号

と同じであるときに、パルス出力回路201で信号の転送を停止する場合を示している。

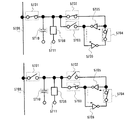

を複数段用いて構成されたシフトレジスタ207とANDゲート205とを有しており、

当該フリップフロップ回路204にクロック信号(S−CLK)、クロック反転信号(S

−CLKB)、スタートパルス信号(S−SP)が入力される。そして、これらの信号の

タイミングに従って順次サンプリングパルスが出力される。また、ANDゲート205の

2つの入力端子は、フリップフロップ回路204の入力端子と出力端子に接続されている

。なお、ここでは、ANDゲート205を用いた例を示しているが、これに限定されない

。同様な働きをする回路であればどのような構造を用いてもよく、例えば、ORゲート、

NANDゲート、NORゲート、XORゲート、NOTゲート等を用いたり組み合わせた

りしてもよい。

ルスが重ならないようにすることができる。そのような必要がない場合にはANDゲート

を設ける必要はない。例えば、図74に示すように、一つの信号線に出力されるサンプリ

ングパルスを複数のフリップフロップ回路204(ここでは2つ)により生成する構成と

してもよい。この場合、ANDゲートを設けなくても各列のサンプリングパルスが重なら

ないようにすることができる。

は、第1のラッチ回路202に出力され、その信号のタイミングに従ってビデオ信号が第

1のラッチ回路202に保持される。第1のラッチ回路202において、最終段までビデ

オ信号の保持が完了すると、水平帰線期間中に、第2のラッチ回路203にラッチパルス

が入力され、第1のラッチ回路202に保持されていたビデオ信号は、一斉に第2のラッ

チ回路203に転送される。

ッチ206を設け、転送制御信号(S_ENABLEt)によって、当該スイッチ206

のオン、オフを制御する。スイッチをオンすると、正論理の場合は強制的にL信号(負論

理の場合はH信号)が書き込まれる。具体的には、書き込みを行う行に関してある列以降

に書き込むビデオ信号が一行前に画素に書き込まれたビデオ信号と同じ場合に、転送制御

信号を用いてスイッチ206をオンして強制的にL信号を書き込むことによって、スター

トパルス信号から順に転送されてきた信号を初期化して当該列以降においてシフトレジス

タ207での信号の転送を停止する。その結果、当該列以降において、第1のラッチ回路

へのサンプリングパルスの出力が行われなくなり、当該列以降の第1のラッチ回路202

へのビデオ信号の書き込みも行われない。従って、ある列以降において、シフトレジスタ

での転送を停止することによりフリップフロップ回路204での充放電が無くなるため消

費電力を低減することができる。また、ビデオ信号線へのビデオ信号の入力も停止するこ

とによって、第1のラッチ回路202へのビデオ信号の充放電が無くなるため消費電力を

低減することができる。なお、ここでは、一列目のフリップフロップ回路の入力部にスイ

ッチ206を設けていないが、設けた構造としてもよい。

を制御できるものなら、どのような構成でもよい。トランジスタでもよいし、ダイオード

でもよいし、それらを組み合わせた論理回路でもよい。スイッチとしてトランジスタを用

いる場合を図73(A)に示す。トランジスタは、第1端子(ソース端子又はドレイン端

子)がフリップフロップ回路204の入力部分に接続され、第2端子(ソース端子又はド

レイン端子)が低電源電位に設定された電極と接続されている。低電源電位としては例え

ばGND、0Vなどが設定されていても良い。また、トランジスタは、単なるスイッチと

して動作するため、トランジスタの極性(導電型)は特に限定されない。ただし、オフ電

流が少ない方が望ましい場合、オフ電流が少ない方の極性のトランジスタを用いることが

望ましい。オフ電流が少ないトランジスタとしては、LDD領域を設けているものやマル

チゲート構造にしているもの等がある。また、スイッチとして動作させるトランジスタの

ソース端子の電位が、低電位側電源(Vss、GND、0Vなど)に近い状態で動作する

場合はNチャネル型を、反対に、ソース端子の電位が、高電位側電源(Vddなど)に近

い状態で動作する場合はPチャネル型を用いることが望ましい。なぜなら、ゲートとソー

ス間電圧の絶対値を大きくできるため、スイッチとして、動作させやすいからである。な

お、Nチャネル型とPチャネル型の両方を用いて、CMOS型のスイッチにしてもよい。

また、スイッチとして、ダイオードを用いてもよく、この場合を(図73(B))に示す

。スイッチとして、図73(B)に示すようにダイオードを設けた場合には、通常は転送

制御信号をHレベルに保ち、転送を停止する場合にLレベルにすることによりダイオード

がオンして信号を初期化することができる。また他にも、ダイオード接続したトランジス

タ、PN接合やPIN接合のダイオードやショットキー型のダイオードやカーボンナノチ

ューブで形成されたダイオードなどを用いてもよい。

は、画素部103において1行がn列(1列目〜n列目)の信号線から構成される場合に

おいて、(j+3)列目以降には第1のラッチ回路202へのビデオ信号の書き込みを行

わない例を示している。なお、図4(A)はスイッチ206として図73(A)に示した

トランジスタを用いた場合を示しており、図4(B)はスイッチ206として図73(B

)に示したダイオードを用いた場合を示している。

前のビデオ信号とが同じであるため、転送制御信号を用いてスイッチ206をオンするこ

とによって、(j+3)列目以降の列ではシフトレジスタ207での信号の転送を停止す

る。つまり、(j+3)列目以降の列において、第1のラッチ回路202へサンプリング

パルスを出力せず、当該第1のラッチ回路202へビデオ信号の書き込みを行わない。具

体的に、図4(A)では、(j+2)列目までは転送制御信号をLレベルに保ち、(j+

3)列目において転送制御信号をHレベルとしてスイッチ206として機能するトランジ

スタをオンして強制的にL信号を書き込むことによって、スタートパルスから順に転送さ

れてきた信号を初期化して(j+3)列目以降においてシフトレジスタ207での信号の

転送を停止する。また、図4(B)では、(j+2)列目までは転送制御信号をHレベル

に保ち、(j+3)列目において転送制御信号をLレベルとして((a)の場合)スイッ

チ206として機能するダイオードをオンして強制的にL信号を書き込むことによって、

スタートパルスから順に転送されてきた信号を初期化して(j+3)列目以降においてシ

フトレジスタ207での信号の転送を停止する。また、(j+3)列目以降において転送

制御信号をLレベルとして((b)の場合)スイッチ206として機能するダイオードを

オンして強制的にL信号を書き込むことによって、スタートパルスから順に転送されてき

た信号を初期化して(j+3)列目以降においてシフトレジスタ207での信号の転送を

停止することも可能である。

の場合、少なくとも(j+2)列目は一行前に書き込まれた(j+1)列目のビデオ信号

と異なっている)あるため、転送制御信号をオフの状態とし、フリップフロップ回路20

4からANDゲート205を介して第1のラッチ回路202へサンプリングパルスを出力

して当該第1のラッチ回路202に新たにビデオ信号の書き込みを行っている。一方、(

j+3)列目以降の列においては、一行前のビデオ信号と全て同じであるため、(j+3

)列目に転送制御信号を用いてスイッチ206をオンの状態とすることによって、(j+

3)列目以降はシフトレジスタ207での信号の転送を停止させ、第1のラッチ回路20

2へサンプリングパルスを出力せず、当該第1のラッチ回路202に新たなビデオ信号の

書き込みを行わない。新たな信号を書き込まなくても、既に第1のラッチ回路202に保

存されているビデオ信号と同じなので問題はない。

ビデオ信号が保持されており、(j+3)列目以降は一行前と同じビデオ信号が第1のラ

ッチ回路202に保持されている。そして、水平帰線期間中に、第2のラッチ回路203

にラッチパルスが入力され、第1のラッチ回路202に保持されていたビデオ信号が第2

のラッチ回路203に転送され、第2のラッチ回路203に保持されたデジタルビデオ信

号1行分が同時に信号線S1〜Snへ出力される。

、ある列以降のビデオ信号が一行前のビデオ信号と同じ場合にそれ以降の列においてはシ

フトレジスタ207の信号の転送を停止して、第1のラッチ回路202へサンプリングパ

ルスの出力を行わないことによって、消費電力を低減することができる。

た場合、その列以降の全ての列において、シフトレジスタ207での信号の転送が停止し

、第1のラッチ回路202へサンプリングパルスが出力されなくなる。従って、図3に示

した構成において、走査方向切り換えスイッチを設け、走査する方向を選択できるように

してもよい。つまり、シフトレジスタ207において、直列に接続された複数のフリップ

フロップ回路204のうち、両端に位置するフリップフロップ回路204のいずれか一方

からスタートパルス信号を入力するか選択することによって、第1のラッチ回路202へ

のサンプリングパルスの出力を低減することができる。

)に示す。ここでは、フリップフロップ回路204の入力部に信号の転送を制御する走査

方向切り換えスイッチ281、282を設ける。具体的には、隣接するフリップフロップ

回路(例えば、j列目と(j+1)列目に対応するフリップフロップ回路)において、j

列目に対応するフリップフロップ回路の出力部と(j+1)列目に対応するフリップフロ

ップ回路の入力部の間に走査方向切り換えスイッチ281を設ける。そして、j列目に対

応するフリップフロップ回路の入力部と(j+1)列目に対応するフリップフロップ回路

の出力部の間に走査方向切り換えスイッチ282を設ける。

オ信号の書き込みを行う場合において、(n−2)列目のビデオ信号のみが一行前に画素

に書き込まれたビデオ信号と異なる際に、1列目にスタートパルス信号を入力した場合と

、n列目にスタートパルス信号を入力してシフトレジスタ207の信号の転送を行った場

合のタイミングチャートを図5に示す。

タートパルス信号を入力した場合を示している。回路図は、図75(B)に相当し、走査

方向切り換えスイッチ281がオンしており走査方向切り換えスイッチ282はオフした

状態となっている。この場合には、シフトレジスタ207において、1列目〜(n−2)

列目までは信号の転送が行われ、(n−1)列目以降には信号の転送が行われない。つま

り、1列目〜(n−2)列目までのフリップフロップ回路204からANDゲート205

を介して第1のラッチ回路202へサンプリングパルスが出力され、当該第1のラッチ回

路202に新たにビデオ信号が書き込まれる。

4にスタートパルス信号を入力した場合を示している。回路図は、図75(C)に相当し

、走査方向切り換えスイッチ281がオフしており走査方向切り換えスイッチ282はオ

ンした状態となっている。この場合には、シフトレジスタ207において、n列目〜(n

−2)列目まで信号の転送が行われ、(n−3)列目〜1列目には信号の転送が行われな

い。つまり、n列目〜(n−2)列目までのフリップフロップ回路204からANDゲー

ト205を介して第1のラッチ回路202へサンプリングパルスが出力され、当該第1の

ラッチ回路202にビデオ信号が新たに書き込まれるが、1列目〜(n−3)列目までは

シフトレジスタ207の信号の転送が停止し、第1のラッチ回路202へサンプリングパ

ルスを出力しない構成とすることができる。

、シフトレジスタ207で信号を転送し、第1のラッチ回路202へサンプリングパルス

を出力して当該第1のラッチ回路202へビデオ信号の書き込みを行うが、図5(B)で

は、n列目〜(n−1)列目までの2列分において、シフトレジスタ207で信号を転送

し、第1のラッチ回路202へサンプリングパルスを出力して当該第1のラッチ回路20

2にビデオ信号の書き込みを行う。従って、走査方向切り換えスイッチを設けて走査する

方向を選択可能とすることによって、シフトレジスタ207において信号の転送を早めに

停止し、フリップフロップ回路204からANDゲート205を介して出力するサンプリ

ングパルスを停止し、当該第1のラッチ回路202へビデオ信号の書き込みを低減するこ

とができる。その結果、ビデオ信号の充放電や、シフトレジスタ207での充放電が無く

なるため、消費電力を低減することができる。これは、nの数(画素数)が大きくなれば

なるほど顕著な効果が得られる。

フリップフロップ回路は、基本的には、入力された信号を遅延させて出力させる構成であ

ればよい。図77に示すフリップフロップ回路3101では、クロックドインバータ31

02、クロックドインバータ3103及びインバータ3104を有し、一般的に、ディレ

イ型フリップフロップ回路(DFF)と呼ばれている。DFFを構成するクロックトイン

バータ3102及び3103は、そこに入力されるクロック信号やクロック反転信号に同

期して動作する。そのため、遅延回路としてDFFを一段配置すると、DFFに供給され

るクロック信号の1パルス分だけ(クロック信号の周期の半分の時間だけ)、信号が遅延

することになる。なお、図77ではDFFを用いた場合の構成を示したが、これに限定さ

れない。シフトレジスタで用いられるような回路であればどのような構成でも適用可能で

ある。

は、基本的には、入力された信号を保持して出力させる構成であればよい。図78に示す

ラッチ回路3201では、インバータ3202、クロックドインバータ3203、クロッ

クドインバータ3204及びインバータ3205を有している。ラッチ回路を構成するク

ロックトインバータ3203及び3204は、そこに入力されるタイミング信号やインバ

ータ3202を介して入力されるタイミング信号に同期して動作する。つまり、タイミン

グ信号に同期して入力された信号を保持して出力させる。なお、本発明に適用可能なラッ

チ回路は、図78の構成に限られず、入力された信号を保持して出力させる回路であれば

どのような構成でも適用可能である。

た構成にも適用することができる。この場合について図76を用いて説明する。

が複数個(ここでは3個ずつ)設けられ、第1のラッチ回路202の数に対応したビデオ

線が複数(ここでは3つ)設けられている。そして、第2のラッチ回路203から出力さ

れたビデオ信号がD/A変換回路を介して信号線に出力される構成となっている。なお、

ここでは第1のラッチ回路を3個(3ビット分)設けた例を示したが、これに限られない

。つまり、実施者が適宜必要な表示ビット数(例えば、6ビットなら第1のラッチ回路と

第2のラッチ回路を6個ずつ)を考慮して選択すればよい。

a〜202cに出力され、その信号のタイミングに従ってビデオ信号が第1のラッチ回路

に保持される。ここでは、ビデオ線が第1のラッチ回路202の数だけ設けられており、

第1のラッチ回路202a〜第1のラッチ回路202cにそれぞれビデオ信号1〜ビデオ

信号3が保持される。つまり、並列した3つの第1のラッチ回路202において、3ビッ

ト分のビデオ信号の取り込みが同時に行われる。そして、第1のラッチ回路202におい

て、最終段までビデオ信号の保持が完了すると、水平帰線期間中に、第2のラッチ回路2

03にラッチパルスが入力され、第1のラッチ回路202に保持されていたビデオ信号は

、一斉に第2のラッチ回路203に転送される。

1のラッチ回路202a〜第1のラッチ回路202cから出力されたビデオ信号がそれぞ

れ第2のラッチ回路203a〜第2のラッチ回路203cに保持される。そして、第2の

ラッチ回路203に保持されたビデオ信号はD/A変換回路283を介して画素へ出力さ

れる。

に、信号を初期化するスイッチ206を設け、転送制御信号(S_ENABLEt)によ

って、当該スイッチ206のオン、オフを制御する。スイッチをオンすると、正論理の場

合は強制的にL信号(負論理の場合はH信号)が書き込まれる。具体的には、書き込みを

行う行に関してある列以降に書き込むビデオ信号が一行前に画素に書き込まれたビデオ信

号と同じ場合に、転送制御信号を用いてスイッチ206をオンして強制的にL信号を書き

込むことによって、スタートパルス信号から順に転送されてきた信号を初期化して当該列

以降においてシフトレジスタ207での信号の転送を停止する。その結果、当該列以降に

おいて、第1のラッチ回路へのサンプリングパルスの出力が行われなくなり、当該列以降

の第1のラッチ回路202へのビデオ信号の書き込みも行われない。従って、ある列以降

において、シフトレジスタでの転送停止することによりフリップフロップ回路204での

充放電が無くなるため消費電力を低減することができる。また、ビデオ信号線へのビデオ

信号の入力も停止することによって、第1のラッチ回路202へのビデオ信号の充放電が

無くなるため消費電力を低減することができる。

一行前に画素に書き込まれたビデオ信号と同じ場合とは、当行に書き込みを行うビデオ信

号と一行前に画素に書き込まれたビデオ信号とを列毎に比較した際に、1列あたりの複数

のビット分のビデオ信号が全て一致した場合(ここでは、当行に書き込みを行うビデオ信

号1〜3と一行前に画素に書き込まれたビデオ信号1〜3がそれぞれ一致した場合)をい

う。

、図73、図74等に示した構成と組み合わせてもよい。また、図76に示した信号線駆

動回路は、デジタル信号を入力してアナログ信号で画素の階調を表示する表示装置に適用

することが好ましく、好適には液晶表示装置に適用することができる。

本実施の形態では、上記実施の形態1と異なる信号線駆動回路を有する表示装置の一例

に関して図面を参照して説明する。

に示す。

構成されたシフトレジスタ207とANDゲート205とを有し、ANDゲート205の

2つの入力端子は、フリップフロップ回路204の入力端子と出力端子に接続されている

。さらに、上記図3に示したパルス出力回路201において、複数のフリップフロップ回

路204から構成されるシフトレジスタ207を複数の領域に分割して設け、スタートパ

ルス信号を複数用意してシフトレジスタの複数の領域にそれぞれスタートパルス信号の入

力を行う構成となっている。なお、ここでは、ANDゲート205を用いた例を示してい

るが、これに限定されない。同様な働きをする回路であればどのような構造を用いてもよ

く、例えば、ORゲート、NANDゲート、NORゲート、XORゲート、NOTゲート

等を用いたり組み合わせたりしてもよい。また、図6に示す構成では、ANDゲート20

5を用いることにより、各列のサンプリングパルスが重ならないようにすることができる

。そのような必要がない場合にはANDゲートを設ける必要はない。

号(S−CLK)、クロック反転信号(S−CLKB)が入力されたタイミングに従って

サンプリングパルスを順次第1のラッチ回路202へ出力する。第1のラッチ回路202

には、ビデオ信号が入力され、パルス出力回路201から出力された複数のサンプリング

パルスが入力されるタイミングに従って、各段にビデオ信号が入力され保持される。つま

り、パルス出力回路201から出力されたサンプリングパルスによって、第1のラッチ回

路202の各段のラッチ回路が動作している。

了すると、水平帰線期間中に、第2のラッチ回路203にラッチパルス(Latch P

ulse)が入力され、第1のラッチ回路202に保持されていたデジタルビデオ信号は

、一斉に第2のラッチ回路203に転送される。その後、第2のラッチ回路203に保持

されたデジタルビデオ信号は1行分が同時に信号線S1〜Snへ出力される。

るスイッチ206を設け、転送制御信号(S_ENABLEt)によって、当該スイッチ

206のオン、オフを制御する。具体的には、新たに書き込みをおこなう行のある列以降

に書き込むビデオ信号が一行前に画素に書き込まれたビデオ信号と同じ場合に、転送制御

信号を用いてスイッチ206をオンして、当該列以降においてシフトレジスタ207での

信号の転送を停止させ、当該第1のラッチ回路202にサンプリングパルスの出力を行わ

ない。さらに、本実施の形態では、フリップフロップ回路204から構成されるシフトレ

ジスタ207を複数の領域に分けて設け、領域毎にスタートパルス信号の入力を行ってい

る。従って、一旦、転送制御信号を用いてスイッチ206をオンにして、シフトレジスタ

207での信号の転送を止めてしまっても、新しい領域では別個にスタートパルス信号を

入力することによりシフトレジスタ207での信号の転送を復活させることができる。な

お、図6では、スイッチ206をトランジスタで設けた例を示したが、これに限られず上

記実施の形態で示したスイッチのいずれかを用いることができる。

用いて詳細に説明する。

トレジスタ207が、1列目〜j列目までのフリップフロップ回路から構成される領域2

07aと、(j+1)列目〜n列目までのフリップフロップ回路から構成される領域20

7bとに分けて設けられている例を示している。この場合、シフトレジスタ207におい

て、領域207aでは第1のスタートパルス信号が入力されることにより信号の転送が開

始し、領域207bでは第2のスタートパルス信号が入力されることにより信号の転送が

開始する構成となっている。つまり、シフトレジスタ207において、領域207aでは

、入力された第1のスタートパルス信号、クロック信号、クロック反転信号のタイミング

に従ってサンプリングパルスが順次第1のラッチ回路202に出力される。一方、領域2

07bでは、入力された第2のスタートパルス信号、クロック信号、クロック反転信号の

タイミングに従ってサンプリングパルスが順次第1のラッチ回路202に出力される。第

2のスタートパルス信号は、207aでのサンプリングパルスの出力が終わると、直ぐに

、207bでのサンプリングパルスの出力が始まるように入力することが望ましい。

7aと領域207bの各々において別々に制御する。ここでは、例えば、図6において、

一行前のビデオ信号と比較した際に、2列目と(j+2)列目においてのみビデオ信号が

異なる場合を考える。

04に入力することによって、1列目と2列目の信号線S1、S2に電気的に接続された

各々の第1のラッチ回路202へサンプリングパルスを出力して、当該第1のラッチ回路

202にビデオ信号の書き込みを行う。そして、転送制御信号を用いてスイッチ206を

オンすることによって、3列目以降(ここでは、3列目〜j列目まで)のシフトレジスタ

207での信号の転送を停止し、3列目〜j列目の信号線S3〜Sjに電気的に接続され

た第1のラッチ回路202へはサンプリングパルスを出力せずビデオ信号をビデオ信号線

へ出力することも行わずビデオ信号の書き込みを行わない。

04に入力することによって、(j+1)列目と(j+2)列目の信号線Sj+1、Sj

+2に電気的に接続された第1のラッチ回路202へサンプリングパルスを出力して、当

該第1のラッチ回路202にビデオ信号の書き込みを行う。そして、転送制御信号を用い

てスイッチ206をオンすることによって、(j+3)列目以降(ここでは、(j+3)

列目〜n列目)のシフトレジスタ207での信号の転送を停止し、(j+3)列目〜n列

目の信号線S(j+3)〜Snに電気的に接続された第1のラッチ回路202へはサンプ

リングパルスを出力せずビデオ信号の書き込みを行わない。

される領域207aにおいて、3列目以降のビデオ信号は一行前のビデオ信号と同じであ

るため、転送制御信号を用いてスイッチ206をオンすることによって、3列目以降の列

(3列目〜j列目)では、シフトレジスタ207での信号の転送を停止して、第1のラッ

チ回路202へサンプリングパルスの出力を行わない。そして、第2のスタートパルス信

号の入力によってシフトレジスタ207の信号の転送が制御される領域207bにおいて

、(j+3)列目以降のビデオ信号は一行前のビデオ信号と同じであるため、転送制御信

号を用いてスイッチ206をオンして、(j+3)列目以降の列((j+3)列目〜n列

目)では、シフトレジスタ207での信号の転送を停止して、第1のラッチ回路202へ

サンプリングパルスの出力を行わない。

回路202に書き込まれたビデオ信号が第2のラッチ回路203を介して信号線へ出力さ

れ、3列目〜j列目、(j+3)列目〜n列目では前の行で既に第1のラッチ回路202

に保持されているビデオ信号がラッチパルスの入力と共に第2のラッチ回路203を介し

て信号線へ出力される。

列目〜n列目では、シフトレジスタ207において信号の転送を停止し、第1のラッチ回

路へサンプリングパルスを出力せず、当該第1のラッチ回路202にビデオ信号を書き込

まないため、ビデオ信号の充放電や、シフトレジスタ207での充放電を無くし消費電力

を低減することができる。

合にその行におけるある列以降の全ての列のシフトレジスタ207において信号の転送が

止まり、第1のラッチ回路202へサンプリングパルスの出力が行われなくなる。そのた

め、その行においてある列以降のビデオ信号が全て1行前の信号と同じとなる必要がある

。従って、上記実施の形態で示した場合には、1列目〜(j+2)列目まではシフトレジ

スタ207において信号を転送し、第1のラッチ回路202へサンプリングパルスを出力

する必要がある。しかし、本実施の形態で示す構成では、分割した複数の領域毎に転送制

御信号を制御してスイッチ206のオンまたはオフを行うことができるため、シフトレジ

スタ207での信号の転送の有無をより詳細に制御し、第1のラッチ回路へのサンプリン

グパルスの出力の有無をより詳細に制御することができる。その結果、消費電力をより効

果的に低減することが可能となる。

それぞれスタートパルス信号を入力する構成を示したが、もちろん本発明はこの構成に限

定されず、シフトレジスタ207を3つ以上の複数の領域に分けて設け、複数のスタート

パルス信号を入力することによって、各領域のサンプリングパルスの出力等を制御するこ

とができる。

けることも可能である。つまり、上述したようにシフトレジスタ207が複数の領域に分

けて設けられた構成において、各領域(図6では、領域207aと207b)に走査方向

切り換えスイッチを設け、領域毎に走査する方向を選択できるようにすることができる。

つまり、複数の領域において、直列に接続された複数のフリップフロップ回路のうち、各

々の領域の両端に位置するフリップフロップ回路のいずれか一方から第1のスタートパル

ス信号、第2のスタートパルス信号を入力するかを選択できるようにする。

ップフロップ回路のどちら側から第1のスタートパルス信号を入力するか選択できるよう

にし、領域207bにおいては(j+1)列目とn列目に相当するフリップフロップ回路

のどちら側から第2のスタートパルス信号を入力するか選択できるようする。

のみビデオ信号が異なる場合を考える。この場合のタイミングチャートを図8に示す。

スタートパルス信号を入力し、1列目と2列目のフリップフロップ回路204からサンプ

リングパルスを出力して第1のラッチ回路202にビデオ信号の書き込みを行う。そして

、転送制御信号を用いてスイッチ206をオンすることにより3列目以降(ここでは、3

列目〜j列目まで)は、シフトレジスタ207での信号の転送を停止し、第1のラッチ回

路202へのサンプリングパルスの出力を行わず、当該第1のラッチ回路202へビデオ

信号の書き込みを行わない。

ートパルス信号を入力し、n列目のフリップフロップ回路204からサンプリングパルス

を出力して第1のラッチ回路202にビデオ信号の書き込みを行う。そして、転送制御信

号をオンすることにより(n−1)列目以降(ここでは、(n−1)目〜(j+1)列目

まで)は、シフトレジスタ207での信号の転送を停止させ、第1のラッチ回路202へ

のサンプリングパルスの出力を行わず、当該第1のラッチ回路202へビデオ信号の書き

込みを行わない。

3列目〜(n−1)列目において、シフトレジスタ207における信号の転送を停止し、

第1のラッチ回路202へのサンプリングパルスの出力を行わず、当該第1のラッチ回路

202へビデオ信号の書き込みを行わない構成とすることができる。つまり、画素の行に

おいて両端に位置する列にのみ一行前のビデオ信号と異なる場合であっても、シフトレジ

スタ207を複数の領域に分け、当該領域毎に走査方向を制御することによって、シフト

レジスタ207において信号の転送を早めに停止して、第1のラッチ回路202へのサン

プリングパルスの出力をより効果的に低減することが可能となるため、消費電力を効果的

に低減することができる。

示した一つの信号線に対して複数のラッチ回路を設けた構成と組み合わせて適用すること

ができる。つまり、本発明は、本実施の形態で示した構成と上記実施の形態で示した構成

とを組み合わせた全ての構成を適用することができる。

本実施の形態では、上記実施の形態と異なる信号線駆動回路を有する表示装置の一例に

関して図面を参照して説明する。具体的には、上記実施の形態と異なるパルス出力回路を

有する表示装置に関して具体的に説明する。

構成されたシフトレジスタ207と3入力のANDゲート235とを有し、ANDゲート

235の入力端子は、フリップフロップ回路204の入力端子と出力端子とサンプリング

制御信号が出力される配線に接続された構成となっている。なお、ここでは、ANDゲー

ト205を用いた例を示しているが、これに限定されない。同様な働きをする回路であれ

ばどのような構造を用いてもよく、例えば、ORゲート、NANDゲート、NORゲート

、XORゲート、NOTゲート等を用いたり組み合わせたりしてもよい。

号(S−CLK)、クロック反転信号(S−CLKB)が入力されたタイミングに従って

サンプリングパルスを順次第1のラッチ回路202へ出力する。第1のラッチ回路202

には、ビデオ信号が入力され、パルス出力回路201から出力された複数のサンプリング

パルスが入力されるタイミングに従って、各段にビデオ信号が入力され保持される。つま

り、パルス出力回路201から出力されたサンプリングパルスによって、第1のラッチ回

路202の各段のラッチ回路が動作している。そして、第1のラッチ回路202において

、最終段までデジタルビデオ信号の保持が完了すると、水平帰線期間中に、第2のラッチ

回路203にラッチパルス(Latch Pulse)が入力され、第1のラッチ回路2

02に保持されていたデジタルビデオ信号は、一斉に第2のラッチ回路203に転送され

る。その後、第2のラッチ回路203に保持されたデジタルビデオ信号は1行分が同時に

信号線S1〜Snへ出力される。

LEp)が入力されており、サンプリング制御信号のレベルによりANDゲート235か

ら第1のラッチ回路202へのサンプリングパルスの出力を制御する。つまり、シフトレ

ジスタ207において全ての列で信号の転送を行い、サンプリング制御信号のレベルを制

御してANDゲート235に入力することによって、第1のラッチ回路202へのサンプ

リングパルスの出力を制御する。

よい。図20では、図9における3入力のANDゲート235の代わりに2入力のAND

ゲート235a、235bを設けた構成となっている。ANDゲート235aの入力端子

は、フリップフロップ回路204の入力端子と出力端子に接続されており、ANDゲート

235bの入力端子は、ANDゲート235aの出力端子とサンプリング制御信号が出力

される配線に接続された構成となっている。なお、ここでは、ANDゲート205を用い

た例を示しているが、これに限定されない。同様な働きをする回路であればどのような構

造を用いてもよく、例えば、ORゲート、NANDゲート、NORゲート、XORゲート

、NOTゲート等を用いたり組み合わせたりしてもよい。

サンプリングパルスが重ならないようにすることができる。そのような必要がない場合に

はANDゲート235を3入力として設ける必要はない。例えば、図21に示すように、

一つの信号線に出力されるサンプリングパルスを複数のフリップフロップ回路204(こ

こでは2つ)により生成する構成としてもよい。この場合、ANDゲート235cを3入

力としなくてよく、ANDゲート235cの入力端子はフリップフロップ回路の出力部と

サンプリング制御信号が出力される配線に接続された構成となっている。

j+4)列目、(j+6)列目〜(j+8)列目に新たに書き込みを行うビデオ信号が一

行前に画素に書き込まれたビデオ信号と同じである場合を示している。

に新たに書き込みを行うビデオ信号が一行前のビデオ信号と同じであるため、サンプリン

グ制御信号をオフして、ANDゲート235から第1のラッチ回路202へサンプリング

パルスの出力を行わない。このとき、ビデオ信号線に、ビデオ信号は入力されない。一方

、j列目〜(j+2)列目、(j+5)列目、(j+9)列目、(j+10)列目に新た

に書き込みを行うビデオ信号が一行前のビデオ信号と異なるため、サンプリング制御信号

をオンして、ANDゲート235から第1のラッチ回路202へサンプリングパルスを出

力し、当該第1のラッチ回路202へビデオ信号の書き込みを行う。なお、図9に示す構

成では、シフトレジスタ207において、全ての列で信号の転送が行われているため、A

NDゲート205にサンプリング制御信号を入力して第1のラッチ回路202へのサンプ

リングパルスの出力の制御を行っている。

目では新たに第1のラッチ回路202に書き込まれたビデオ信号が第2のラッチ回路20

3を介して信号線へ出力され、(j+3)列目、(j+4)列目、(j+6)列目〜(j

+8)列目では前の行で既に第1のラッチ回路202に保持されているビデオ信号が第2

のラッチ回路を介して信号線へ出力される。

チ回路202へのサンプリングパルスの出力を必要な列でだけ停止させることができる。

つまり、必要な列(ここでは、一行前とビデオ信号が異なる列)に対してのみ選択的にビ

デオ信号の書き込みを行うことによって、消費電力を低減することができる。また、一行

前とビデオ信号が同じときには、ビデオ信号線にビデオ信号を入力しないことにより低消

費電力を図ることができる。

。

るスイッチ236を設け、転送制御信号(S_ENABLEt)を用いて当該スイッチ2

36を制御する構成としてもよい。この場合、第1のラッチ回路202へのサンプリング

パルスの出力を転送制御信号とサンプリング制御信号を用いて制御することができる。ま

た、上記図20、図21に示した構成に転送制御信号を設けた構成としてもよい。なお、

図11では、スイッチ236をトランジスタで設けた例を示したが、これに限られず上記

実施の形態で示したスイッチのいずれかを用いることができる。

列目〜(j+8)列目、(j+11)列目〜n列目に新たに書き込みを行うビデオ信号が

一行前のビデオ信号と同じである場合を示している。

、(j+11)列目〜n列目に新たに書き込みを行うビデオ信号は一行前のビデオ信号と

同じであるため、サンプリング制御信号をオフして、ANDゲート235から第1のラッ

チ回路202へサンプリングパルスの出力を行わない。一方、j列目〜(j+2)列目、

(j+5)列目、(j+9)列目、(j+10)列目に書き込みを行うビデオ信号は一行

前のビデオ信号と異なるため、サンプリング制御信号をオンして、ANDゲート235か

ら第1のラッチ回路202へサンプリングパルスを出力し、当該第1のラッチ回路202

へビデオ信号の書き込みを行う。なお、ここでは、(j+11)列目以降において、書き

込みを行うビデオ信号が全て1行前のビデオ信号と同じであるため、転送制御信号を用い

てスイッチ236をオンして(j+11)列目以降においてシフトレジスタ207での信

号の転送を中止する。

スタでの信号の転送や第1のラッチ回路へのサンプリングパルスの出力を制御し、必要な

列に対してのみ選択的にビデオ信号の書き込みを行うことができるため、消費電力を低減

することができる。

以降において新たに書き込みを行うビデオ信号と一行前に画素に書き込まれたビデオ信号

とが全て同じである必要があり、サンプリング制御信号を用いてサンプリングパルスの出

力を制御する場合には、列毎にサンプリングパルスの出力を制御することができるが、全

ての列に対してシフトレジスタで信号の転送を行う必要がある。そのため、転送制御信号

とサンプリング制御信号の両方を用いてサンプリングパルスの出力を制御することにより

、様々な画素の表示に柔軟に対応できるため、より効果的に消費電力を低減することが可

能となる。

スイッチを設けてもよいし、シフトレジスタを複数の領域に分け、スタートパルス信号を

複数用意して当該複数のシフトレジスタの領域にそれぞれスタートパルス信号の入力を行

う構成としてもよい。さらに、シフトレジスタ207を複数の領域に分けて設け、当該領

域毎に走査方向を制御する構成としてもよい。

発明は、本実施の形態で示した構成と上記実施の形態で示した構成とを組み合わせた全て

の構成を適用することができる。

本実施の形態では、上記実施の形態と異なる表示装置の一例に関して図面を参照して説

明する。具体的には、ある期間の複数の行における動作方法に関して、特に一行前のビデ

オ信号と新たに次の行に書き込みを行うビデオ信号が全ての列において同一である場合を

含む場合の動作方法に関して説明する。

2のラッチ回路243を有している。パルス出力回路241は、フリップフロップ回路2

44を複数段用いて形成されたシフトレジスタ247とANDゲート245とを有してお

り、ANDゲート245の2つの入力端子は、隣り合うフリップフロップ回路244との

出力端子と接続されている。つまり、各段のフリップフロップ回路244はANDゲート

245より1つ冗長に設けられ、隣り合うフリップフロップ回路244の出力が信号線S

1〜Snに対応して設けられた各段のANDゲート245に入力される構成となっている

。

初期化するスイッチ246を設け、転送制御信号(S_ENABLEt)により当該スイ

ッチ246を制御する。そして、スタートパルス信号が入力され、フリップフロップ回路

244から第1のラッチ回路242へ信号が順次転送されていっても、ある列以降のビデ

オ信号が1行前のビデオ信号と同じ場合には転送制御信号をオンして、シフトレジスタ2

47において信号の転送を停止させ、ある列以降において第1のラッチ回路へのサンプリ

ングパルスの出力を行わない構成となっている。なお、図13では、スイッチ246をト

ランジスタで設けた例を示したが、これに限られず上記実施の形態で示したスイッチのい

ずれかを用いることができる。

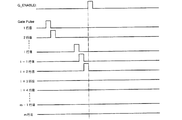

画素へ入力するビデオ信号を信号線駆動回路の第1のラッチ回路242に保持する期間(

ここでは、TGi−1、TGi、TGi+1)を示している。つまり、TGi−1、TG

i、TGi+1は、それぞれ1ゲート選択期間に相当する。

、クロック反転信号(S−CLKB)が入力され、フリップフロップ回路244の第1段

目にスタートパルス信号(S−SP)が入力される。図14においては、パルス2101

がTGi−1のスタートパルスに相当する。

ク信号の1パルス分遅れる。よって、冗長に設けられた第1段目のフリップフロップ回路

244と次の段のフリップフロップ回路244の出力が入力される一列目のANDゲート

245の出力は、図14に示すパルス2301のようにクロック信号のパルス分となる。

パルス2301は、サンプリングパルスSamp.1として1列目の画素に対応した第1

のラッチ回路242に入力される。同様にn列目のANDゲート245の出力は、図14

に示すパルス2302のようにサンプリングパルスSamp.nとしてn列目の画素に対

応した第1のラッチ回路242に入力される。

1が入力されており、サンプリングパルスが入力されるタイミングに従って、画素の各列

に対応した各段の第1のラッチ回路にビデオ信号を保持する。なお、図14において、サ

ンプリングパルスが入力されるタイミングとは、サンプリングパルスがHレベルからLレ

ベルに立ち下がるときのことである。このときに、第1のラッチ回路242に入力されて

いるビデオ信号が、当該第1のラッチ回路242の各々の段に保持される。

線期間中に、第2のラッチ回路243にラッチパルス(Latch Pulse)240

1が入力され、第1のラッチ回路242に保持されていたビデオ信号は、一斉に第2のラ

ッチ回路243に転送される。その後、第2のラッチ回路243に保持されたビデオ信号

は1行分が同時に信号線へ出力される。

設けられており、当該スイッチ246は転送制御信号により制御されている。従って、転

送制御信号のレベルによりシフトレジスタ247における信号の転送が制御され、第1の

ラッチ回路242に出力されるサンプリングパルスが制御される。

においてHレベルとなり、それ以外の場合においてLレベルとなる。つまり、転送制御信

号がLレベルのときには、フリップフロップ回路244の入力部分に設けられた信号を初

期化するスイッチ246がオフするため、シフトレジスタ247において信号は転送され

、第1のラッチ回路242にサンプリングパルスが出力されビデオ信号が書き込まれる。

転送制御信号がHレベルのときには、フリップフロップ回路244の入力部分に設けられ

た信号を初期化するスイッチ246がオンするため、シフトレジスタ247において信号

の転送が停止し、第1のラッチ回路242にサンプリングパルスが出力されず、当該第1

のラッチ回路242にビデオ信号の書き込みが行われない。ビデオ信号の書き込みを行わ

ないため、ビデオ信号をビデオ信号線(Video Line)に入力する必要がない。

よって、ビデオ信号の供給を止めてもよい。その結果、より消費電力を低減することがで

きる。

号と異なっているか、または少なくとも1列目とn列目において一行前のビデオ信号と異

なっている例を示している。そのため、全ての列においてシフトレジスタ247で信号の

転送を行い第1のラッチ回路242へサンプリングパルスを出力して、当該第1のラッチ

回路242へ新たにビデオ信号の書き込みを行っている例を示しているため、転送制御信

号はLレベルとなっている。

画素行の全ての列において一行前((i−1)行目)に画素に書き込まれたビデオ信号と

同じ場合について示している。

LK)、クロック反転信号(S−CLKB)が入力され、フリップフロップ回路244の

第1段目にスタートパルス信号(S−SP)が入力される。図14においては、パルス2

111がTGiのスタートパルスに相当する。

れると同時に、転送制御信号がHレベルとなり、フリップフロップ回路244の入力部分

に設けられた信号を初期化するスイッチがオンするため、次の段のフリップフロップ回路

への信号が転送されなくなる。その結果、シフトレジスタ247において信号の転送が停

止するため、全ての列において第1のラッチ回路242へサンプリングパルスが出力され

ずビデオ信号の書き込みが行われない。ビデオ信号の書き込みを行わないため、ビデオ信

号をビデオ信号線(Video Line)に入力する必要がない。よって、ビデオ信号

の供給を止めてもよい。その結果、より消費電力を低減することができる。

オ信号が、一斉に第2のラッチ回路243に転送され、第2のラッチ回路243に保持さ

れたビデオ信号の1行分が同時に信号線へ出力される。つまり、一行前と同じビデオ信号

が出力される。

列において一行前(i行目)のビデオ信号と同じ場合について示している。

LK)、クロック反転信号(S−CLKB)が入力され、フリップフロップ回路244の

第1段目にスタートパルス信号(S−SP)が入力される。図14においては、パルス2

121がTGi+1のスタートパルスに相当する。

フロップ回路244の出力が入力された一列目のANDゲート245から、図14に示す

パルス2321のようにクロック信号の1パルス分が出力される。パルス2321は、サ

ンプリングパルスSamp.1として1列目の画素に対応した第1のラッチ回路242に

入力され、サンプリングパルスSamp.1が入力されるタイミングに従って、1列目の

画素に対応した第1のラッチ回路242にビデオ信号が書き込まれる。

れの画素に対応した第1のラッチ回路242にサンプリングパルスが入力されビデオ信号

が書き込まれる。

Hレベルとなり、フリップフロップ回路244の入力部分に設けられた信号を初期化する

スイッチがオンするため、次の段のフリップフロップ回路への信号が転送されなくなる。

その結果、(j−1)列目以降において、シフトレジスタ247の信号の転送が停止する

ため、j列目以降の列において第1のラッチ回路242へサンプリングパルスが出力され

ずビデオ信号の書き込みが行われない。また、j列目以降の列においてビデオ信号の書き

込みを行わないため、ビデオ信号をビデオ信号線(Video Line)に入力する必

要がない。よって、j列目以降の列においてビデオ信号の供給を止めてもよい。その結果

、より消費電力を低減することができる。

たビデオ信号が、ラッチパルスの入力と共に一斉に第2のラッチ回路243に転送され、

第2のラッチ回路243に保持されたビデオ信号の1行分が同時に信号線へ出力される。

つまり、一行前と同じビデオ信号が出力される。

前のビデオ信号と同じ場合は、第1段目のフリップフロップ回路244からパルスが出力

されると同時に、転送制御信号がHレベルとなり、シフトレジスタ247において信号の

転送が停止し、第1のラッチ回路へサンプリングパルスが出力されず当該第1のラッチ回

路へビデオ信号の書き込みが行われない。従って、書き込みを行う画素行の全ての列にお

いて一行前に画素に書き込んだビデオ信号と同じ場合には、スタートパルス信号の入力を

行わないようにしてもよい。

ス信号の入力を行わないようにする。なぜなら、このときTGiでは、シフトレジスタで

信号の転送が行われず第1のラッチ回路へサンプリングパルスが出力されないため、そも

そもスタートパルス信号を入力する必要がないからである。そして、スタートパルス信号

のパルス2111を入力しない場合には、第1のラッチ回路242へサンプリングパルス

が出力されないため、第1のラッチ回路へビデオ信号2211の書き込みが行われない。

従って、第1のラッチ回路242への電荷の充放電を省略することにより、消費電力を低

減することができる。なお、この場合、転送制御信号のパルス2511は出力してもよい

し、出力しなくともよい。ビデオ信号の書き込みを行わないため、ビデオ信号をビデオ信

号線(Video Line)に入力する必要がない。よって、ビデオ信号の供給を止め

てもよい。その結果、より消費電力を低減することができる。

信号線駆動回路へビデオ信号の入力を行わないようにしてもよい。

わないようにする。なぜなら、このときTGiで入力されるビデオ信号は、第1のラッチ

回路242に書き込まれないため、そもそもビデオ信号を入力する必要がないからである

。そして、ビデオ信号の入力を停止することにより、ビデオ線への電荷の充放電が省略で

きるため消費電力を低減することができる。従って、TGiにおいては、ビデオ線への消

費電力が小さくなる電位(例えば、L信号のみ)を入力するか、第1のラッチ回路をフロ

ーティングにすればよい。なお、これは外部から信号が入力される接続端子と信号線駆動

回路とが画素部を挟んで設けられている場合には特に有効となる。この場合の、構成の一

例を図16に示す。

部8003及び接続端子部8005を有している。画素部8003上には、画素部800

3を覆うように対向電極8004が形成され、対向電極8004は、接続端子部に形成さ

れた対向電極の低電源電位が入力される複数の接続端子8007から伸張した接続端子8

007のパッドより幅広の配線とコンタクトホール8008を介して接続されている。そ

して、ビデオ信号が入力される接続端子8006はビデオ線8009により信号線駆動回

路8001と接続されている。本構成の場合には、対向電極8004への電源供給ライン

の抵抗(接続端子8007とFPC端子との接触抵抗や、対向電極8004と接続端子8

007との間の配線抵抗など)や容量(平行配線間容量や配線交差間容量等)を小さくす

ることができる。よって、電源供給ラインでの電圧降下や波形のなまりや変動を低減し、

対向電極の電位を正常にすることができる。そして、ビデオ線8009のように引き回し

配線が長くなって配線に寄生している抵抗や容量が大きくなっても、ビデオ線8009の

充放電を減らすことができるので消費電力の低減を図ることができる。

スタートパルス信号のパルス2111の入力を行わなくてもよいし、転送制御信号のパル

ス2511を入力しなくてもよい。

信号線駆動回路へクロック信号やクロック反転信号等の入力を行わないようにしてもよい

。

号を信号線駆動回路へ入力しないようにする。例えば、クロック信号とクロック反転信号

とで互いに反転している一定の電位(一方がHレベル、他方がLレベル)を入力するよう

にしてもよい。なぜなら、このときTGiでは、シフトレジスタの信号の転送が行われず

第1のラッチ回路へサンプリングパルスが出力されないため、そもそもクロック信号やク

ロック反転信号を信号線駆動回路へ入力する必要がないからである。従って、クロック信

号やクロック反転信号を一定の電位にしておくことにより電荷の充放電が行われないため

、消費電力を低減することができる。また、図17(A)のTGiにおいて、図15(A

)に示したように信号線駆動回路へスタートパルス信号のパルス2111の入力を行わな

くてもよいし、転送制御信号のパルス2511を入力しなくてもよいし、図15(B)に

示したようにビデオ信号2211の入力を行わないようにしてもよい。その結果、大幅に

消費電力を低減することができる。

信号線駆動回路へラッチパルスの入力を行わないようにしてもよい。

へ入力しないようにする。なぜなら、このときTGiでは、シフトレジスタの信号の転送

が行われず第1のラッチ回路へサンプリングパルスが出力されないため、そもそもラッチ

パルスを信号線駆動回路へ入力する必要がないからである。従って、ラッチパルスを信号

線駆動回路へ入力しないことによって、第1のラッチ回路から第2のラッチ回路への信号

の転送が行われないため、電荷の充放電を省略し消費電力を低減することができる。また

、図17(B)のTGiにおいて、図15(A)に示したように信号線駆動回路へスター

トパルス信号のパルス2111の入力を行わなくてもよいし、転送制御信号のパルス25

11を入力しなくてもよいし、図15(B)に示したようにビデオ信号2211の入力を

行わないようにしてもよいし、図17(A)に示したようにクロック信号やクロック反転

信号の入力を行わないようにしてもよい。その結果、大幅に消費電力を低減することがで

きる。

説明する。

2のラッチ回路243を有している。パルス出力回路241は、フリップフロップ回路2

44を複数段用いて形成されたシフトレジスタ247とANDゲート245とを有してお

り、ANDゲート245の2つの入力端子は、隣り合うフリップフロップ回路244との

出力端子と接続されている。さらに、図18では、上記図13に示したパルス出力回路2

01において、複数のフリップフロップ回路204から構成されるシフトレジスタ207

を複数の領域に分割して設け、スタートパルス信号を複数用意してシフトレジスタの当該

複数の領域にそれぞれスタートパルス信号の入力を行う構成となっている。

るスイッチ246を設け、転送制御信号(S_ENABLEt)により当該スイッチ24

6を制御する。そして、スタートパルス信号が入力され、フリップフロップ回路244か

ら第1のラッチ回路242へ信号が順次転送されていっても、ある列以降のビデオ信号が

1行前のビデオ信号と同じ場合には転送制御信号をオンして、シフトレジスタ247にお

いて信号の転送を停止させ、ある列以降において第1のラッチ回路へのサンプリングパル

スの出力を行わない構成となっている。

トレジスタ247が、1列目〜j列目までのフリップフロップ回路から構成される第1の

領域247aと、(j+1)列目〜n列目までのフリップフロップ回路から構成される第

2の領域247bとに分けて設けられている例を示している。この場合、シフトレジスタ

247において、第1の領域247aでは第1のスタートパルス信号が入力されることに

より信号の転送が開始し、領域247bでは第2のスタートパルス信号が入力されること

により信号の転送が開始する構成となっている。

る。なお、図14と同じ部分については説明を省略する。

画素へ入力するビデオ信号を信号線駆動回路の第1のラッチ回路242に保持する期間(

ここでは、TGi−1、TGi、TGi+1)を示している。つまり、TGi−1、TG

i、TGi+1は、それぞれ1ゲート選択期間に相当する。

ク反転信号(S−CLKB)が入力され、第1の領域247aのフリップフロップ回路2

44の第1段目に第1のスタートパルス信号(S−SP1)が入力される。図19(A)

においては、パルス2101がTGi−1の第1のスタートパルス信号に相当する。

ク信号のパルス分遅れる。よって、冗長に設けられた第1段目のフリップフロップ回路2

44と次の段のフリップフロップ回路244の出力が入力される一列目のANDゲート2

45の出力は、図19(A)に示すパルス2301のようにクロック信号のパルス分とな

る。パルス2301は、サンプリングパルスSamp.1として1列目の画素に対応した

第1のラッチ回路242に入力される。同様にj列目のANDゲート245の出力は、図

14に示すパルス2303のようにサンプリングパルスSamp.jとしてj列目の画素

に対応した第1のラッチ回路242に入力される。

7の第2の領域247bに、クロック信号(S−CLK)、クロック反転信号(S−CL

KB)が入力され、第2の領域247bのフリップフロップ回路244の第1段目に第2

のスタートパルス信号(S−SP2)が入力される。図19(A)においては、パルス2

102がTGi−1の第1のスタートパルス信号に相当する。

ク信号のパルス分遅れる。よって、冗長に設けられた第1段目のフリップフロップ回路2

44と次の段のフリップフロップ回路244の出力が入力される(j+1)列目のAND

ゲート245の出力は、図19(A)に示すパルス2304のようにクロック信号のパル

ス分となる。パルス2304は、サンプリングパルスSamp.j+1として(j+1)

列目の画素に対応した第1のラッチ回路242に入力される。同様にn列目のANDゲー

ト245の出力は、図19(A)に示すパルス2302のようにサンプリングパルスSa

mp.nとしてn列目の画素に対応した第1のラッチ回路242に入力される。

1が入力されており、サンプリングパルスが入力されるタイミングに従って、画素の各列

に対応した各段の第1のラッチ回路にビデオ信号を保持する。

線期間中に、第2のラッチ回路243にラッチパルス(Latch Pulse)240

1が入力され、第1のラッチ回路242に保持されていたビデオ信号は、一斉に第2のラ

ッチ回路243に転送される。その後、第2のラッチ回路243に保持されたビデオ信号

は1行分が同時に信号線へ出力される。

設けられており、当該スイッチ246は転送制御信号により制御されている。従って、転

送制御信号のレベルによりシフトレジスタ247の第1の領域247aおよび第2の領域

247bにおける信号の転送が制御され、第1のラッチ回路242に出力されるサンプリ

ングパルスが制御される。

号と異なっているか、または少なくとも1列目とn列目において一行前のビデオ信号と異

なっている例を示している。そのため、全ての列においてシフトレジスタ247の第1の

領域247aおよび第2の領域247bで信号の転送を行い第1のラッチ回路242へサ

ンプリングパルスを出力して、当該第1のラッチ回路242へ新たにビデオ信号の書き込

みを行っている例を示しているため、転送制御信号はLレベルとなっている。

画素行の全ての列において一行前((i−1)行目)に画素に書き込まれたビデオ信号と

同じ場合について示している。

クロック反転信号(S−CLKB)が入力され、第1の領域247aのフリップフロップ

回路244の第1段目に第1のスタートパルス信号(S−SP)が入力される。図19(

A)においては、パルス2111がTGiの第1のスタートパルスに相当する。

力されると同時に、転送制御信号がHレベル(パルス2511)となり、フリップフロッ

プ回路244の入力部分に設けられた信号を初期化するスイッチがオンするため、次の段

のフリップフロップ回路への信号が転送されなくなる。その結果、シフトレジスタ247

において信号の転送が停止するため、全ての列において第1のラッチ回路242へサンプ

リングパルスが出力されずビデオ信号の書き込みが行われない。

、クロック反転信号(S−CLKB)が入力され、第2の領域247bのフリップフロッ

プ回路244の第1段目に第2のスタートパルス信号(S−SP)が入力される。図19

(A)においては、パルス2112がTGiの第2のスタートパルスに相当する。

ップ回路244からパルスが出力されると同時に、転送制御信号がHレベル(パルス25

12)となり、シフトレジスタ247の第2の領域247bにおいても信号の転送が停止

する。

オ信号が、一斉に第2のラッチ回路243に転送され、第2のラッチ回路243に保持さ

れたビデオ信号の1行分が同時に信号線へ出力される。つまり、一行前と同じビデオ信号

が出力される。

いて同一である場合には、図19(B)に示すように第1のスタートパルス(パルス21

11)と第2のスタートパルス(パルス2112)をそれぞれ同時にシフトレジスタ24

7の第1の領域247aと第2の領域247bに入力することも可能である。TGiでは

、全ての列において、第1のラッチ回路242にビデオ信号が書き込まれないからである

。この場合、第1の領域247aと第2の領域247bの第1段目のフリップフロップ回

路244からパルスが出力されると同時に、転送制御信号がHレベル(パルス2511)

とすることによって、フリップフロップ回路244の入力部分に設けられた信号を初期化

するスイッチをオンすればよい。

まれたビデオ信号とが同一であり、(j+2)列目〜n列目に新たに書き込みを行うビデ

オ信号と一行前に書き込まれたビデオ信号とが同一である場合を示している。

いて、それぞれ、上記図14のTGi+1で説明した方法を用いて同様に行うことができ

る。

て一行前のビデオ信号と同じ場合は、第1段目のフリップフロップ回路244からパルス

が出力されると同時に、転送制御信号がHレベルとなり、シフトレジスタ247において

信号の転送が停止し、第1のラッチ回路へサンプリングパルスが出力されず、当該第1の

ラッチ回路へビデオ信号の書き込みが行われない。従って、書き込みを行う画素行の全て

の列において一行前に画素に書き込んだビデオ信号と同じ場合には、上記図15、17に

示したように、スタートパルス信号、ビデオ信号、クロック信号、クロック反転信号、ラ

ッチパルス等の入力を行わないようにしてもよい。

発明は、本実施の形態で示した構成と上記実施の形態で示した構成とを組み合わせた構成

を全て含んでいる。

本実施の形態では、画素に書き込みを行おうとするビデオ信号が、既にその画素へ書き

込まれているビデオ信号(つまり、画素に保存されているビデオ信号)と等しい場合に関

して図面を参照して説明を行う。具体的には、ある行以降において、既にその行の画素へ

書き込まれているビデオ信号と新たにその行に書き込みを行おうとするビデオ信号とが同

じである場合に関して説明する。

を書き込む場合に、書き込みを行おうとするビデオ信号が既にその画素へ書き込まれてい

るビデオ信号と一致している場合、その画素の行へはビデオ信号の書き込みを行わないよ

うにする。つまり、その行の画素(以下、「画素行」とも記す。)にビデオ信号を書き込

む動作時において、その画素行が選択されない信号を入力し続けるか、またはその画素行

の走査線をフローティングにする。

オ信号が、それらの画素へ書き込みを行おうとするビデオ信号と全て一致しているときだ

け、その行の画素に信号の書き込みを行わない。よって、その行の各列の画素に書き込み

を行おうとするビデオ信号のうち一つでも既に書き込まれているビデオ信号と異なる場合

には、その走査線につながっている画素の全てに信号の書き込みを行う。なぜなら、走査

線に画素を選択する信号を入力すると、信号線の電位が否応なしに画素に入力され、画素

のデータが書き換わってしまうためである。従って、一行における全てのビデオ信号が一

致する場合のみ、その走査線を選択しないようにする。

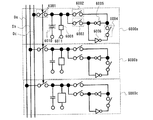

とを有している。パルス出力回路251には、クロック信号(G_CLK)、クロック反

転信号(G_CLKB)、スタートパルス信号(G_SP)等が入力されている。そして

、それらの信号のタイミングに従って、バッファ253にゲート選択パルスが入力される

。そして、パルス出力回路251から出力されたゲート選択パルス(SC.1〜SC.m

)はバッファ253によって、電流供給能力の高いゲート選択パルス(G.1〜G.m)

に変換され、走査線G1〜Gmに出力される。なお、パルス出力回路251とバッファ2

53との間に信号のレベルをシフトさせる回路(レベルシフタ)を設けた構成としてもよ

い。

されている。そして、転送制御信号により、ビデオ信号の書き込みを行わない画素行を選

択し、当該画素行にゲート選択パルスの出力を行わない構成となっている。

されたシフトレジスタ257とANDゲート255とを有しており、当該フリップフロッ

プ回路254にクロック信号(S−CLK)、クロック反転信号(S−CLKB)、スタ

ートパルス信号(S−SP)が入力される。そして、シフトレジスタ257で信号が転送

され、これらの信号のタイミングに従ってバッファ253へ順次ゲート選択パルスが出力

される。また、ANDゲート255の2つの入力端子は、フリップフロップ回路254の

入力端子と出力端子に接続されている。

るスイッチ256を設け、転送制御信号を用いて当該スイッチ256のオン、オフを制御

する。例えば、ある行以降の全ての行おいて画素にビデオ信号の書き込みを行わない場合

には、転送制御信号を用いてスイッチ256をオンすることにより、ある行以降において

シフトレジスタ257での信号の転送を停止させ、バッファ253へゲート選択パルスの

出力を行わないようにする。この場合、ある行以降においては走査線の選択を行わないた

め、ある行以降の画素に新たにビデオ信号の書き込みを行わず、既に書き込まれているビ

デオ信号を保持させ続ける。なお、図22では、スイッチ256をトランジスタで設けた

例を示したが、これに限られず上記実施の形態で示したスイッチのいずれかを用いること

ができる。

続されたトランジスタのゲート容量に代表される負荷容量に電荷を充放電することになる

。そこで、このように、ある行以降において、既に画素に書き込まれているビデオ信号と

その画素に新たに書き込みを行おうとするビデオ信号が等しいとき、ある行以降において

シフトレジスタ257での信号の転送を停止し、走査線にその画素行を選択するゲート選

択パルスを入力しないようにすることによって、充放電の回数を減らし消費電力を低減す

ることができる。

(1行目〜m行目)の走査線から構成される場合において、(i+3)行目以降の画素に

はビデオ信号の書き込みを行わない例を示している。

(i+3)行目以降の各列に書き込まれているビデオ信号と同じであるため、転送制御信

号を用いてスイッチ256をオンすることにより、(i+3)行目以降の行においてシフ

トレジスタ257での信号の転送を停止し、(i+3)行目以降の画素行にゲート選択パ

ルスの出力を行わない。

たにその行の画素に書き込みを行おうとするビデオ信号とを比較した場合に異なる行が少

なくとも一つ(この場合、少なくとも(i+2)行目に既に書き込まれているビデオ信号

が書き込みを行おうとするビデオ信号と異なっている)あるため、転送制御信号を用いて

スイッチ256をオフの状態とし、バッファ253を介して走査線にゲート選択パルスを

出力して画素にビデオ信号の書き込みを行っている。一方、(i+3)行目以降の行にお

いては、既にその行の画素に書き込まれているビデオ信号と書き込みを行おうとするビデ

オ信号とが全て同じであるため、(i+3)行目に転送制御信号を用いてスイッチ256

をオンすることにより、(i+3)行目以降の画素にはビデオ信号の書き込みを行わず、

既に画素に書き込まれているビデオ信号を保持する。

線に接続されたトランジスタのゲート容量に代表される負荷容量に電荷を充放電すること

になる。そこで、図23に示すように、ビデオ信号の書き込みを行う場合に、既にその画

素へ書き込まれているビデオ信号と新たにその画素へ書き込みを行おうとするビデオ信号

がある行以降全て同じ場合には転送制御信号を用いて、その画素行以降においてシフトレ

ジスタ257での信号の転送を停止し、走査線にゲート選択パルスを入力しないようにす

ると、充放電の回数を減らすことができ、消費電力を低減することができる。

した場合、その行以降の全ての行において、シフトレジスタ257の信号の転送が停止し

、走査線へゲート選択パルスの出力が行われなくなる。従って、図22に示した構成にお

いて、走査方向切り換えスイッチを設け、走査する方向を選択できるようにしてもよい。

つまり、シフトレジスタ257において、直列に接続された複数のフリップフロップ回路

254のうち、両端に位置するフリップフロップ回路254のいずれか一方からスタート

パルス信号を入力するか選択することによって、より多くの行で走査線へのゲート選択パ

ルスの出力を低減することが可能となる。

つまり、ある行以降において、既にその画素へ書き込まれているビデオ信号と新たにその

画素へ書き込みを行おうとするビデオ信号が同じ場合に、転送制御信号によりシフトレジ

スタ257での信号の転送を停止する構成であればどのような構成としてもよい。また、

図23の場合には、(i+3)行目以降において、信号線駆動回路を全て停止させてもよ

い。その結果、大幅に消費電力を低減することができる。

れたシフトレジスタ267とANDゲート265とを有し、ANDゲート265の2つの

入力端子は、フリップフロップ回路264の入力端子と出力端子に接続されている。さら

に、パルス出力回路261において、シフトレジスタ267を複数の領域に分割して設け

、スタートパルス信号を複数用意して当該複数のシフトレジスタの領域にそれぞれスター

トパルス信号の入力を行う構成となっている。

設け、転送制御信号(G_ENABLEt)を用いて当該スイッチ266のオン、オフを

制御する。例えば、ある行以降の全ての行おいて画素にビデオ信号の書き込みを行わない

場合には、転送制御信号を用いてスイッチ256をオンすることにより、ある行以降にお

いてシフトレジスタ257での信号の転送を停止させ、バッファ253へゲート選択パル

スの出力を行わないようにする。この場合、ある行以降においては、画素に新たにビデオ

信号の書き込みを行わず、既に書き込まれているビデオ信号を保持させ続ける。

7を複数の領域に分けて設け、当該領域毎にスタートパルス信号の入力を行う構成を示し

ている。従って、一旦、転送制御信号を用いてスイッチ256をオンすることによって、

ある行以降におけるシフトレジスタ257の信号の転送を止めてしまっても、別の領域で

は別個にスタートパルス信号が入力されるためシフトレジスタ267での信号の転送を復

活させることができる。

シフトレジスタ267が、1行目〜i行目までフリップフロップ回路264から構成され

る領域267aと、(i+1)行目〜m行目までのフリップフロップ回路264から構成

される領域267bとに分けて設けられている例を示している。

号が入力されることにより信号の転送が開始し、領域267bでは第2のスタートパルス

信号が入力されることにより信号の転送が開始する構成となっている。つまり、シフトレ

ジスタ267において、領域267aでは、入力された第1のスタートパルス信号、クロ

ック信号、クロック反転信号のタイミングに従ってゲート選択パルスが順次バッファ25

3を介して走査線に出力される。一方、領域267bでは、入力された第2のスタートパ

ルス信号、クロック信号、クロック反転信号のタイミングに従ってゲート選択パルスが順

次バッファ253を介して走査線に出力される。

いて、領域267aと領域267bの各々において別々に制御する。例えば、図24にお

いて、既に画素に書き込まれているビデオ信号と書き込みを行おうとするビデオ信号とを

比較した際に、2行目と(i+2)行目においてのみ既に書き込まれているビデオ信号と

書き込みを行おうとするビデオ信号が異なる場合を考える。

順々にゲート選択パルスを出力して画素行を選択し、当該画素行にビデオ信号の書き込み

を行う。続いて、転送制御信号を用いてスイッチ266をオンすることによって、3行目

以降(ここでは、3行目〜i行目まで)は、シフトレジスタ267での信号の転送を停止

し、フリップフロップ回路264から走査線へゲート選択パルスの出力を行わず、画素へ

ビデオ信号の書き込みを行わない。

)行目走査線にゲート選択パルスを出力して当該画素行にデータの書き込みを行う。続い

て、転送制御信号を用いてスイッチ266をオンすることによって、(i+3)行目以降

(ここでは、(i+3)行目〜m行目)はシフトレジスタ267での信号の転送を停止し

、フリップフロップ回路204から走査線へのゲート選択パルスの出力を行わず、画素へ

のデータの書き込みを行わない。

れる領域263aにおいて、3行目以降(ここでは、3行目〜i行目まで)では既に画素

に保持されたビデオ信号と書き込みを行おうとするビデオ信号とが同じであるため、転送

制御信号を用いてスイッチ266をオンすることによって3行目〜i行目の走査線にゲー

ト選択パルスの出力を行わない。

れる領域263bにおいて、(i+3)行目以降(ここでは、(i+3)行目〜i行目ま

で)では既に画素に保持されたビデオ信号と書き込みを行おうとするビデオ信号とが同じ

であるため、転送制御信号を用いてスイッチ266をオンすることによって(i+3)行

目以降の走査線にゲート選択パルスの出力を行わない。

信号が書き込まれ、3行目〜i行目、(i+3)行目〜m行目では既にその行に書き込ま

れているビデオ信号を保持し続ける。

)行目〜m行目では、シフトレジスタ267において信号の転送を停止し、走査線にその

画素行を選択するゲート選択パルスの入力を行わないため、充放電の回数を減らすことが

でき、消費電力を低減することができる。また、走査線にゲート選択パルスの入力を行わ

ない場合には、信号線駆動回路を全て停止させてもよい。その結果、大幅に消費電力を低

減することができる。

た場合に、その行以降の全ての行においてシフトレジスタ257で信号の転送が止まり、

その行以降全ての走査線にゲート選択パルスの出力が行われなくなる。そのため、ある行

以降において、既に画素に書き込まれたビデオ信号と新たに書き込みを行おうとするビデ

オ信号とが全て同じとなる必要がある。従って、この場合図22に示した構成では、1行

目〜(i+2)行目までシフトレジスタ267での信号の転送を行い、走査線にゲート選

択パルスを出力する必要がある。一方、図24に示す構成では、分割した複数の領域毎に

転送制御信号を用いてスイッチ266のオンまたはオフを行うことができるため、シフト

レジスタ267での信号の転送を詳細に制御し、走査線へのゲート選択パルスの出力の有

無を詳細に制御することによって、消費電力を低減することが可能となる。

れスタートパルス信号を入力する構成を示したが、もちろん本発明はこの構成に限定され

ず、シフトレジスタ267を3つ以上の複数の領域に分けて設け、それぞれの領域に対応

した複数のスタートパルス信号を入力することによって、各領域においてゲート選択パル

スの出力を制御することができる。

、シフトレジスタ267が複数の領域に分けて設けられた構成において、各領域(図24

では、領域267aと267b)に走査方向切り換えスイッチを設け、領域毎に走査する

方向を選択できるようにすることができる。つまり、複数の領域において、直列に接続さ

れた複数のフリップフロップ回路のうち、各々の領域の両端に位置するフリップフロップ

回路のいずれか一方から第1のスタートパルス信号、第2のスタートパルス信号を入力す

るかを選択できるようにすることができる。

リップフロップ回路のどちら側から第1のスタートパルス信号を入力するか選択できるよ

うにし、領域267bにおいては(i+1)行目とm行目に相当するフリップフロップ回

路のどちら側から第2のスタートパルス信号を入力するか選択できるようする。

書き込みを行おうとするビデオ信号が等しいとき、ある行以降においてシフトレジスタ2

57での信号の転送を停止し、走査線にその画素行を選択するゲート選択パルスを入力し

ないようにすることによって、充放電の回数を減らし消費電力を低減することができる。

ビデオ信号と書き込みを行おうとするビデオ信号とが等しい場合、その画素行への信号の

書き込み動作時において、その画素行の信号線をフローティングにすることにより、さら

に消費電力の低減を図ることが可能となる。なぜなら、一つの走査線に接続されている画

素と同数の信号線の配線交差要領への充放電を省略することができるためである。また、

フローティングにしなくとも信号線に入力した直前の信号をそのまま出力するようにして

もよい。なぜなら、その信号線にはすでに配線交差容量への充放電が完了しているため、

それほど消費電力はかからないからである。例えば、上記実施の形態で上述した、一行前

のビデオ信号と新たに次の行に書き込みを行うビデオ信号が全ての列において同一である

場合の駆動方法(例えば、図14、図15、図17)を適用することができる。

、画素にビデオ信号の書き込みを行う場合において、一行前のビデオ信号と書き込みを行

うビデオ信号との比較、および既に画素に書き込まれたビデオ信号と書き込みを行うビデ

オ信号との比較を行い、画素へのビデオ信号の書き込みを制御することができる。

る行以降の画素に既に書き込まれたビデオ信号と新たに書き込みを行おうとするビデオ信

号との比較を行い、全ての画素において同じである場合には、本実施の形態で示した構成

を用いて走査線にゲート選択パルスの出力を行わず、走査線の選択を行わないようにする

。一方、既に画素に書き込まれたビデオ信号と新たにその画素へ書き込みを行おうとする

ビデオ信号とが異なる行がある場合には、一行前に画素に書き込まれたビデオ信号と新た

に書き込みを行うビデオ信号との比較を行い、異なる列がある場合には、上記実施の形態

1乃至4に示した構成を用いて一行前に書き込まれたビデオ信号と異なる列にのみビデオ

信号を書き込むようにする。

うとするビデオ信号との比較と、一行前に画素に書き込まれたビデオ信号と新たに書き込

みを行うビデオ信号との比較とを行うことによって、最も消費電力が小さくなるように動

作させることによって、より効果的に消費電力を低減することができる。

わせた構成を全て含んでいる。

本実施の形態では、画素に書き込みを行うビデオ信号が、既にその画素へ書き込まれて

いるビデオ信号(つまり、画素に保存されているビデオ信号)と等しい場合に関して、上

記実施の形態5と異なる構成に関して図面を参照して説明を行う。具体的には、既にその

画素へ書き込まれているビデオ信号と書き込みを行うビデオ信号が同じである行が複数あ

る場合に、行毎に選択的にゲート選択パルスの出力を行わない構成に関して説明する。

用いて構成されたシフトレジスタ277とANDゲート275とを有し、ANDゲート2

75の入力端子は、フリップフロップ回路274の入力端子と出力端子とサンプリング制

御信号が出力される配線に接続された構成となっている。

−CLK)、クロック反転信号(S−CLKB)が入力されたタイミングに従ってゲート

選択パルスを順次バッファ回路273へ出力する。そして、バッファ253により電流供

給能力の高い画素選択信号に変換され、走査線に出力される。

)が入力されており、サンプリング制御信号のレベルによりバッファ253へのゲート選

択パルスの出力を制御する。つまり、シフトレジスタ277の全ての行において信号の転

送を行い、サンプリング制御信号をANDゲート275に入力することによって、バッフ

ァ253へのゲート選択パルスの出力の制御を行う。

(i+6)行目〜(i+8)行目の画素に新たに書き込みを行おうとするビデオ信号が既

にその画素行の画素に書き込まれたビデオ信号と同じである場合を示している。

の画素に新たに書き込みを行おうとするビデオ信号は既に当該画素行に保存されているビ

デオ信号と同じであるため、サンプリング制御信号をオフして、ANDゲート275から

バッファ253へゲート選択パルスの出力を行わない。一方、i行目〜(i+2)行目、

(i+5)行目、(i+9)行目、(i+10)行目に新たに書き込みを行おうとするビ

デオ信号は、既に当該画素行に保持されているビデオ信号と異なるため、サンプリング制

御信号をオンして、ANDゲート275からバッファ253へゲート選択パルスを出力し

、走査線を選択することにより画素へビデオ信号の書き込みを行う。なお、ここでは、シ

フトレジスタ277において、全ての行で信号の転送が行われているため、ANDゲート

275にサンプリング制御信号を入力してゲート選択パルスの出力の制御を行っている。

目では画素に新たなビデオ信号が書き込まれ、(i+3)行目、(i+4)行目、(i+

6)行目〜(i+8)行目では既にその画素に保存されているビデオ信号が保持され続け

る。

パルスの出力を必要な行でだけ停止させることができる。つまり、必要な行(ここでは、

既にその行の画素に書き込まれているビデオ信号と新たにその行の画素に書き込みを行お

うとするビデオ信号とが異なる行)に対してのみ選択的に走査線を選択して、画素にビデ

オ信号の書き込みを行うことによって、消費電力を低減することができる。また、走査線

にゲート選択パルスの入力を行わない場合には、信号線駆動回路を全て停止させてもよい

。その結果、大幅に消費電力を低減することができる。

路284の入力部に信号を初期化するスイッチ286を設け、転送制御信号を用いて当該

スイッチを制御する構成としてもよい。この場合、ゲート選択パルスの出力を転送制御信

号とサンプリング制御信号を用いて制御することができる。なお、図28では、スイッチ

286をトランジスタで設けた例を示したが、これに限られず上記実施の形態で示したス

イッチのいずれかを用いることができる。

i+11)行目〜m行目において、新たに画素に書き込もうとするビデオ信号が既にその

画素に書き込まれたデータと同じである場合を示している。

、(i+11)行目〜m行目の画素に書き込みを行うビデオ信号は既にその画素行に書き

込まれているビデオ信号と同じであるため、サンプリング制御信号をオフして、ANDゲ

ート285からバッファ253へゲート選択パルスの出力を行わない。一方、i行目〜(

i+2)行目、(i+5)行目、(i+9)行目、(i+10)行目の画素においては既

にその画素に書き込まれているビデオ信号と書き込みを行うビデオ信号とが異なるため、

サンプリング制御信号をオンして、ANDゲート285からバッファ253へゲート選択

パルスを出力し、ビデオ信号の書き込みを行う。なお、ここでは、(i+11)行目以降

の行では全て既にその行に書き込まれているビデオ信号と書き込みを行うビデオ信号とが

同じであるため、転送制御信号をオンして(i+11)行目以降においてシフトレジスタ

287の信号の転送を中止する。

スタでの信号の転送や走査線へのゲート選択パルスの出力を制御し、必要な行の画素に対

してのみ選択的にビデオ信号の書き込みを行うことができるため、消費電力を低減するこ

とができる。

降において新たに書き込みを行おうとするビデオ信号と既にある行以降に書き込まれたビ

デオとが全て同じである必要があり、サンプリング制御信号を用いてゲート選択パルスの

出力を制御する場合には、行毎にゲート選択パルスの出力を制御することができるが、全

ての行に対してシフトレジスタで信号の転送を行う必要がある。そのため、転送制御信号

とサンプリング制御信号の両方を用いてゲート選択パルスの出力を制御することにより、

様々な画素の表示に柔軟に対応できるため、より効果的に消費電力を低減することが可能

となる。また、走査線にゲート選択パルスの入力を行わない場合には、信号線駆動回路を

全て停止させてもよい。その結果、大幅に消費電力を低減することができる。

スイッチを設けてもよいし、シフトレジスタ287を複数の領域に分け、スタートパルス

信号を複数用意して当該複数のシフトレジスタの領域にそれぞれスタートパルス信号の入

力を行う構成としてもよい。さらに、シフトレジスタ287を複数の領域に分けて設け、

当該領域毎に走査方向を制御する構成としてもよい。

ビデオ信号と書き込みを行おうとするビデオ信号とが等しい場合、その画素行への信号の

書き込み動作時において、その画素行の信号線をフローティングにすることにより、さら

に消費電力の低減を図ることが可能となる。なぜなら、一つの走査線に接続されている画

素と同数の信号線の配線交差要領への充放電を省略することができるためである。また、

フローティングにしなくとも信号線に入力した直前の信号をそのまま出力するようにして

もよい。なぜなら、その信号線にはすでに配線交差容量への充放電が完了しているため、

それほど消費電力はかからないからである。例えば、上記実施の形態で上述した、一行前

のビデオ信号と新たに次の行に書き込みを行うビデオ信号が全ての列において同一である

場合の駆動方法(例えば、図14、図15、図17)を適用することができる。

、画素にビデオ信号の書き込みを行う場合において、一行前のビデオ信号と書き込みを行

うビデオ信号との比較、および既に画素に書き込まれたビデオ信号と新たにその画素へ書

き込みを行おうとするビデオ信号との比較を行い、画素へのビデオ信号の書き込みを制御

することができる。

(i行)の画素に既に書き込まれたビデオ信号と新たにその行(i行)の画素に書き込み

を行おうとするビデオ信号との比較を行い、全ての画素において同じである場合には、本

実施の形態で示した構成を用いて走査線にゲート選択パルスの出力を行わず、走査線の選

択を行わないようにする。一方、既に画素に書き込まれたビデオ信号と新たに書き込みを

行おうとするビデオ信号とが異なる場合には、一行前((i−1)行)に画素に書き込ま

れたビデオ信号と新たに次の行(i行)の画素に書き込みを行うビデオ信号との比較を行

い、異なる列がある場合には、上記実施の形態1乃至4に示した構成を用いて一行前に書

き込まれたビデオ信号と異なる列にのみビデオ信号を書き込むようにする。

するビデオ信号と、一行前に画素に書き込まれたビデオ信号と新たに書き込みを行うビデ

オ信号との比較とを行うことによって、最も消費電力が小さくなるように動作させること

によって、より効果的に消費電力を低減することができる。

わせた構成を全て含んでいる。

本実施の形態では、ある行の画素に新たに書き込みを行おうとするビデオ信号が、既に

その行の画素へ書き込まれているビデオ信号(つまり、画素に保存されているビデオ信号

)と等しい場合に適用する信号線駆動回路の構成例に関して図面を参照して説明を行う。

具体的には、ある行の画素に新たに書き込みを行おうとするビデオ信号が、既にその行の

画素へ書き込まれているビデオ信号と等しい場合に画素へビデオ信号の書き込みを行わな

い構成を有する信号線駆動回路に関して説明する。

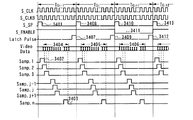

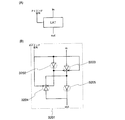

、第2のラッチ回路803、出力制御回路804を有する。パルス出力回路801には、

クロック信号(S_CLK)、クロック反転信号(S_CLKB)、スタートパルス信号

(S_SP)が入力される。これらの信号にしたがって順次サンプリングパルスが出力さ

れる。

入力され、その信号のタイミングにしたがってビデオ信号(Video Data)が第

1のラッチ回路802に保持される。

線期間中に、第2のラッチ回路803にラッチパルス(Latch Pulse)が入力

され、第1のラッチ回路802に保持されていたビデオ信号は、一斉に第2のラッチ回路

803に転送される。

。さらに、出力制御回路804には出力制御信号(S_ENABLE)が入力されており

、この信号によりビデオ信号を信号線S1〜Snに出力するかしないかが制御される。な

お、出力制御回路804では、ビデオ信号を出力しないときに、信号線S1〜Snをフロ

ーティングにしてもいいし、固定電位を設定してもよい。固定電位としては、消費電力を

低減するような電位を設定しておけばよい。

期間において、画素への信号の書き込みを行う画素行における一行分のビデオ信号のビデ

オ信号が、前回のサブフレーム期間における一行分のビデオ信号のビデオ信号と同じ場合

に、出力制御信号はLレベルとなり、一行分のデータが一つでも異なる場合に出力制御信

号がHレベルとなる。つまり、出力制御信号がLレベルのときには、出力制御回路804

からビデオ信号が出力されず、Hレベルのとき出力制御回路804からビデオ信号が出力

される。

ングチャートを用いてこの信号線駆動回路の動作について説明する。

ック信号(S_CLK)、クロック反転信号(S_CLKB)、スタートパルス信号(S

_SP)が入力される。

ーム期間におけるそれぞれj−1行目の画素、j行目の画素、j+1行目の画素、j+2

行目の画素へ入力するビデオ信号を信号線駆動回路の第1のラッチ回路812にラッチす

る期間を示している。つまり、1ゲート選択期間に相当する。そして、TGi−1にはビ

デオ信号3404、TGiにはビデオ信号3405、TGi+1にはビデオ信号3406

のデータが第1のラッチ回路812に入力される。

5にはクロック信号(S_CLK)、クロック反転信号(S_CLKB)が入力され、フ

リップフロップ回路815の第1段目にスタートパルス信号(S_SP)が入力される。

図31において、パルス3401がTGi−1のスタートパルス信号である。

ク信号のパルス分遅れる。このパルス3402はサンプリングパルスSamp.1として

第1のラッチ回路812の一列目の画素に対応したLAT1に入力される。同様にn段目

のフリップフロップ回路815の出力はパルス3403のようにサンプリングパルスSa

mp.nとして第1のラッチ回路812のn列目の画素に対応したLAT1に入力される

。

されており、サンプリングパルスが入力されるタイミングに従って、画素の各列に対応し

た各段のラッチ回路にビデオ信号を保持する。なお、ここでのサンプリングパルスが入力

されるタイミングとは、サンプリングパルスがHレベルからLレベルに立ち下がるときの

ことである。このときに、第1のラッチ回路812に入力されているビデオ信号が、第1

のラッチ回路812のそれぞれの段に保持される。

線期間中に、第2のラッチ回路813にラッチパルス(Latch Pulse)340

7が入力され、第1のラッチ回路812に保持されていたビデオ信号は、一斉に第2のラ

ッチ回路813に転送される。その後、第2のラッチ回路813に保持されたビデオ信号

は1行分が同時に出力制御回路814へ入力される。

、この信号のレベルによりビデオ信号を信号線S1〜Snに出力するかしないかが制御さ

れる。出力制御信号(S_ENABLE)は、1フレーム期間中のあるサブフレーム期間

において、画素への信号の書き込みを行う画素行における一行分のビデオ信号が、前回の

サブフレーム期間における一行分のビデオ信号と同じ場合に、出力制御信号はLレベルと

なり、一行分のデータが一つでも異なる場合に出力制御信号がHレベルとなる。

14の各段に設けられたアナログスイッチがオフするため出力制御回路814からビデオ

信号が出力されず、Hレベルのときには、各段に設けられたアナログスイッチがオンする

ため出力制御回路814からビデオ信号が出力される。

るため第2のラッチ回路813に保持されたビデオ信号3404が出力制御回路814を

介して信号線S1〜Snに出力される。そして、再び、フリップフロップ回路815の第

1段目にスタートパルス信号(S_SP)が入力される。パルス3408がTGiのスタ

ートパルス信号である。すると、再びサンプリングパルスが出力される。そして、このサ

ンプリングパルスのタイミングに従ってビデオ信号3405が第1のラッチ回路812の

各段に保持される。そして、ラッチパルス3409が入力されると、このビデオ信号34

05が第2のラッチ回路813に一斉に転送される。そして、このビデオ信号3405は

1行分が同時に出力制御回路814へ入力される。

であるため第2のラッチ回路813に保持されたビデオ信号3405は出力制御回路81

4から出力されない。つまり、信号線S1〜Snはフローティングとなっている。そして

、再び、フリップフロップ回路815の第1段目にスタートパルス信号(S_SP)が入

力される。パルス3410がTGi+1のスタートパルス信号である。すると、再びサン

プリングパルスが出力される。そして、このサンプリングパルスのタイミングに従ってビ

デオ信号3406が第1のラッチ回路812の各段に保持される。そして、ラッチパルス

3412が入力されると、このビデオ信号3406が第2のラッチ回路813に一斉に転

送される。そして、このビデオ信号3406は1行分が同時に出力制御回路814へ入力

される。

であるため第2のラッチ回路813に保持されたビデオ信号3406が出力制御回路81

4を介して信号線S1〜Snに出力される。また、再び、フリップフロップ回路815の

第1段目にスタートパルス信号(S_SP)が入力される。パルス3413がTGi+2

のスタートパルス信号である。

信号の処理を行う。さらに、サブフレーム分の処理を繰り返すことで1フレームの画像を

表示することができる。

ている信号のデータと等しいため、i行目の画素への信号書き込み時間、つまり、TGi

+1の間は信号線S1〜Snをフローティングにしている。よって、信号線への充放電を

省略することができ、消費電力の低減を図ることができる。

に変換する期間においては、信号のデータ保持の開始のきっかけとなるスタートパルス信

号(S_SP)のパルスを入力しないようにしてもよい。つまり、図32(A)に示すよ