JP5314964B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP5314964B2 JP5314964B2 JP2008208472A JP2008208472A JP5314964B2 JP 5314964 B2 JP5314964 B2 JP 5314964B2 JP 2008208472 A JP2008208472 A JP 2008208472A JP 2008208472 A JP2008208472 A JP 2008208472A JP 5314964 B2 JP5314964 B2 JP 5314964B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- forming

- mixed

- silicon oxide

- substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B10/00—Static random access memory [SRAM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B10/00—Static random access memory [SRAM] devices

- H10B10/12—Static random access memory [SRAM] devices comprising a MOSFET load element

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

- H10D84/0172—Manufacturing their gate conductors

- H10D84/0177—Manufacturing their gate conductors the gate conductors having different materials or different implants

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

- H10D84/0181—Manufacturing their gate insulating layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/038—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon technology, e.g. SiGe

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/60—Formation of materials, e.g. in the shape of layers or pillars of insulating materials

- H10P14/65—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by treatments performed before or after the formation of the materials

- H10P14/6516—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by treatments performed before or after the formation of the materials of treatments performed after formation of the materials

- H10P14/6518—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by treatments performed before or after the formation of the materials of treatments performed after formation of the materials by introduction of substances into an already-existing insulating layer

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/60—Formation of materials, e.g. in the shape of layers or pillars of insulating materials

- H10P14/66—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by the type of materials

- H10P14/662—Laminate layers, e.g. stacks of alternating high-k metal oxides

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/60—Formation of materials, e.g. in the shape of layers or pillars of insulating materials

- H10P14/69—Inorganic materials

- H10P14/692—Inorganic materials composed of oxides, glassy oxides or oxide-based glasses

- H10P14/6921—Inorganic materials composed of oxides, glassy oxides or oxide-based glasses containing silicon

- H10P14/69215—Inorganic materials composed of oxides, glassy oxides or oxide-based glasses containing silicon the material being a silicon oxide, e.g. SiO2

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/60—Formation of materials, e.g. in the shape of layers or pillars of insulating materials

- H10P14/69—Inorganic materials

- H10P14/692—Inorganic materials composed of oxides, glassy oxides or oxide-based glasses

- H10P14/6938—Inorganic materials composed of oxides, glassy oxides or oxide-based glasses the material containing at least one metal element, e.g. metal oxides, metal oxynitrides or metal oxycarbides

- H10P14/6939—Inorganic materials composed of oxides, glassy oxides or oxide-based glasses the material containing at least one metal element, e.g. metal oxides, metal oxynitrides or metal oxycarbides characterised by the metal

- H10P14/69391—Inorganic materials composed of oxides, glassy oxides or oxide-based glasses the material containing at least one metal element, e.g. metal oxides, metal oxynitrides or metal oxycarbides characterised by the metal the material containing aluminium, e.g. Al2O3

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/60—Formation of materials, e.g. in the shape of layers or pillars of insulating materials

- H10P14/69—Inorganic materials

- H10P14/692—Inorganic materials composed of oxides, glassy oxides or oxide-based glasses

- H10P14/6938—Inorganic materials composed of oxides, glassy oxides or oxide-based glasses the material containing at least one metal element, e.g. metal oxides, metal oxynitrides or metal oxycarbides

- H10P14/6939—Inorganic materials composed of oxides, glassy oxides or oxide-based glasses the material containing at least one metal element, e.g. metal oxides, metal oxynitrides or metal oxycarbides characterised by the metal

- H10P14/69397—Inorganic materials composed of oxides, glassy oxides or oxide-based glasses the material containing at least one metal element, e.g. metal oxides, metal oxynitrides or metal oxycarbides characterised by the metal the material containing two or more metal elements

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/60—Formation of materials, e.g. in the shape of layers or pillars of insulating materials

- H10P14/69—Inorganic materials

- H10P14/692—Inorganic materials composed of oxides, glassy oxides or oxide-based glasses

- H10P14/6938—Inorganic materials composed of oxides, glassy oxides or oxide-based glasses the material containing at least one metal element, e.g. metal oxides, metal oxynitrides or metal oxycarbides

- H10P14/6939—Inorganic materials composed of oxides, glassy oxides or oxide-based glasses the material containing at least one metal element, e.g. metal oxides, metal oxynitrides or metal oxycarbides characterised by the metal

- H10P14/69392—Inorganic materials composed of oxides, glassy oxides or oxide-based glasses the material containing at least one metal element, e.g. metal oxides, metal oxynitrides or metal oxycarbides characterised by the metal the material containing hafnium, e.g. HfO2

Landscapes

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Electrodes Of Semiconductors (AREA)

- Formation Of Insulating Films (AREA)

- Semiconductor Memories (AREA)

- Thin Film Transistor (AREA)

Description

H.N. Alshareef et al., Symp. VLSI Tech., Dig., p.10, 2006 H-S. Jung, et al., Symp. VLSI Tech. Dig., p.204, 2006 T. Schram, et al., Symp. VLSI Tech. Dig., p.44, 2008

本実施の形態では、SRAM(static random access memory)を備えた半導体装置に本発明を適用した場合について説明する。

前記実施の形態1では、pMISトランジスタQpのHfAlO膜6pと、nMISトランジスタQnのHfMgO膜6nの2種類の混合膜(高誘電率膜)を形成するために、それぞれに対応するAl膜7およびMg膜11の金属薄膜の切り分けに際し、レジスト膜10、14を用いたマスク合わせを2回行う場合について説明した。本実施の形態では、そのレジスト膜を用いたマスク合わせを1回省略する場合について説明する。それに伴う製造工程は前記実施の形態1と異なるが、最終構造は前記実施の形態1と同様となる。以下に、前記実施の形態1と相違する点を中心に説明する。図22〜図24は本実施の形態における製造工程中の半導体装置の要部を模式的に示す断面図である。

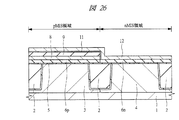

前記実施の形態2では、ハードマスクとして用いたSiN膜9を除去し、pMIS領域で保護膜のTiN膜8を露出した後、nMIS領域に金属薄膜のMg膜11、保護膜のTiN膜12を形成する場合について説明した。本実施の形態では、ハードマスクとして用いたSiN膜9を除去せずに以降の工程を行う場合について説明する。それに伴う製造工程は前記実施の形態2と異なるが、最終構造は前記実施の形態2と同様となる。以下に、前記実施の形態2と相違する点を中心に説明する。図25〜図26は本実施の形態における製造工程中の半導体装置の要部を模式的に示す断面図である。

前記実施の形態1では、例えば図19を参照して、大気暴露により金属薄膜の変質を抑制するために、金属薄膜(例えばMg膜)上に保護膜(例えばTiN膜)を設ける場合について、例えば図19を参照して説明した。本実施の形態では、この保護膜を設けずに、ベース絶縁膜に金属薄膜の金属元素を拡散させる場合について説明する。図27は、本実施の形態における高誘電率膜の形成を説明するための図であり、nMISトランジスタの場合が示されている。なお、前記実施の形態1とは相違する点を中心に説明し、pMISトランジスタの場合も同様の工程で形成することができるのでその説明は省略する。

前記実施の形態1では、例えば図19を参照して、大気暴露などにより金属薄膜の変質を抑制するために、金属薄膜(例えばMg膜)上のみに保護膜(例えばTiN膜)を設けた場合について説明した。本実施の形態では金属薄膜を保護膜で挟んで金属薄膜を保護する場合について説明する。図28は、本実施の形態における高誘電率膜の形成を説明するための図であり、nMISトランジスタの場合が示されている。なお、前記実施の形態1とは相違する点を中心に説明し、pMISトランジスタの場合も同様の工程で形成することができるのでその説明は省略する。

前記実施の形態1では、例えば図19を参照して、大気暴露により金属薄膜の変質を抑制するために、金属薄膜(例えばMg膜)上に保護膜(例えばTiN膜)を設ける場合について、例えば図19を参照して説明した。本実施の形態では、ベース絶縁膜(例えばHfO2膜)上に保護膜(例えばTiN膜)を設け、基板界面絶縁膜(SiO2膜)とベース絶縁膜(HfO2膜)との間に金属薄膜(例えばMg膜)を設ける場合について説明する。図29は、本実施の形態における高誘電率膜の形成を説明するための図であり、nMISトランジスタの場合が示されている。なお、前記実施の形態1とは相違する点を中心に説明し、pMISトランジスタの場合も同様の工程で形成することができるのでその説明は省略する。

2 素子分離領域

3 nウェル

4 pウェル

5 SiO2膜

6 HfO2膜

6n HfMgO膜

6p HfAlO膜

7 Al膜

8 TiN膜

9 SiN膜

10 レジスト膜

11 Mg膜

12 TiN膜

13 SiN膜

14 レジスト膜

15 TiN膜

16 ポリシリコン膜

17 p型半導体領域(ソース/ドレイン)

18 n型半導体領域(ソース/ドレイン)

19 サイドウォール

20 シリサイド膜

21 層間絶縁膜

22 コンタクトホール

23 配線

101 基板

102 高誘電率膜

103 金属酸化膜

104 ゲート絶縁膜

105 ゲート電極

CNT コンタクト

G ゲート電極

Qn nMISトランジスタ

Qp pMISトランジスタ

Claims (13)

- 以下の工程を含むMISトランジスタを備えた半導体装置の製造方法:

(a)半導体基板の主面上に、酸化シリコン膜を形成する工程;

(b)前記酸化シリコン膜上に、ハフニウムおよび酸素を含む膜状の基材を形成する工程;

(c)前記基材上に、前記基材より薄く、かつ、金属元素のみからなる膜状の混合材を形成する工程;

(d)前記混合材の表面を窒化した後にアニール処理を施し、前記基材に前記混合材を拡散することによって、前記酸化シリコン膜上に、酸化シリコンより誘電率が高く、前記基材のハフニウムおよび酸素と、前記混合材の金属元素とを含む混合膜を形成する工程;

(e)前記混合膜上に、導電性膜を形成する工程;

(f)前記導電性膜から構成されるゲート電極、前記混合膜および前記酸化シリコン膜から構成されるゲート絶縁膜を形成する工程。 - 以下の工程を含むMISトランジスタを備えた半導体装置の製造方法:

(a)半導体基板の主面上に、酸化シリコン膜を形成する工程;

(b)前記酸化シリコン膜上に、ハフニウムおよび酸素を含む膜状の基材を形成する工程;

(c)前記基材上に、前記基材より薄く、かつ、金属元素のみからなる膜状の混合材を形成する工程;

(d)前記混合材の表面を酸化した後にアニール処理を施し、前記基材に前記混合材を拡散することによって、前記酸化シリコン膜上に、酸化シリコンより誘電率が高く、前記基材のハフニウムおよび酸素と、前記混合材の金属元素とを含む混合膜を形成する工程;

(e)前記混合膜上に、導電性膜を形成する工程;

(f)前記導電性膜から構成されるゲート電極、前記混合膜および前記酸化シリコン膜から構成されるゲート絶縁膜を形成する工程。 - 以下の工程を含むMISトランジスタを備えた半導体装置の製造方法:

(a)半導体基板の主面上に、酸化シリコン膜を形成する工程;

(b)前記酸化シリコン膜上に、ハフニウムおよび酸素を含む膜状の基材を形成する工程;

(c)前記基材上に、前記基材より薄く、かつ、金属元素のみからなる膜状の混合材を形成する工程;

(d)前記混合材の表面を酸化し、さらに窒化した後にアニール処理を施し、前記基材に前記混合材を拡散することによって、前記酸化シリコン膜上に、酸化シリコンより誘電率が高く、前記基材のハフニウムおよび酸素と、前記混合材の金属元素とを含む混合膜を形成する工程;

(e)前記混合膜上に、導電性膜を形成する工程;

(f)前記導電性膜から構成されるゲート電極、前記混合膜および前記酸化シリコン膜から構成されるゲート絶縁膜を形成する工程。 - 以下の工程を含むMISトランジスタを備えた半導体装置の製造方法:

(a)半導体基板の主面上に、酸化シリコン膜を形成する工程;

(b)前記酸化シリコン膜上に、ハフニウムおよび酸素を含む膜状の基材を形成する工程;

(c)前記基材上に、前記基材より薄く、かつ、金属元素のみからなる膜状の混合材を形成する工程;

(d)前記混合材上に、保護膜を形成する工程;

(e)前記保護膜を有する状態で、前記基材に前記混合材を拡散することによって、前記酸化シリコン膜上に、酸化シリコンより誘電率が高く、前記基材のハフニウムおよび酸素と、前記混合材の金属元素とを含む混合膜を形成する工程;

(f)前記工程(e)の後、前記保護膜を除去する工程;

(g)前記混合膜上に、導電性膜を形成する工程;

(h)前記導電性膜から構成されるゲート電極、前記混合膜および前記酸化シリコン膜から構成されるゲート絶縁膜を形成する工程。 - 前記MISトランジスタはnチャネル型であり、

前記工程(c)において、酸化ハフニウムより電気陰性度が小さい酸化金属物を構成する金属元素からなる前記混合材を形成することを特徴とする請求項4記載の半導体装置の製造方法。 - 前記MISトランジスタはpチャネル型であり、

前記工程(c)において、酸化ハフニウムより電気陰性度が大きい酸化金属物を構成する金属元素からなる前記混合材を形成することを特徴とする請求項4記載の半導体装置の製造方法。 - 前記工程(e)において、アニール処理によって前記基材に前記混合材を拡散することを特徴とする請求項4記載の半導体装置の製造方法。

- 前記工程(c)で真空状態において前記混合材を形成し、その真空状態を保ったまま前記工程(d)で前記保護膜を形成することを特徴とする請求項4記載の半導体装置の製造方法。

- 前記工程(d)では、保護膜として窒化チタン膜を形成することを特徴とする請求項4記載の半導体装置の製造方法。

- 以下の工程を含むMISトランジスタを備えた半導体装置の製造方法:

(a)半導体基板の主面上に、酸化シリコン膜を形成する工程;

(b)前記酸化シリコン膜上に、ハフニウムおよび酸素を含む膜状の基材を形成する工程;

(c)前記基材上に、保護膜を形成する工程;

(d)前記保護膜上に、前記基材より薄く、かつ、金属元素のみからなる膜状の混合材を形成する工程;

(e)前記保護膜を有する状態で、前記基材に前記混合材を拡散することによって、前記酸化シリコン膜上に、酸化シリコンより誘電率が高く、前記基材のハフニウムおよび酸素と、前記混合材の金属元素とを含む混合膜を形成する工程;

(f)前記工程(e)の後、前記保護膜を除去する工程;

(g)前記混合膜上に、導電性膜を形成する工程;

(h)前記導電性膜から構成されるゲート電極、前記混合膜および前記酸化シリコン膜から構成されるゲート絶縁膜を形成する工程。 - 以下の工程を含むMISトランジスタを備えた半導体装置の製造方法:

(a)半導体基板の主面上に、酸化シリコン膜を形成する工程;

(b)前記酸化シリコン膜上に、ハフニウムおよび酸素を含む膜状の基材を形成する工程;

(c)前記基材上に、第1保護膜を形成する工程;

(d)前記第1保護膜上に、前記基材より薄く、かつ、金属元素のみからなる膜状の混合材を形成する工程;

(e)前記混合材上に、第2保護膜を形成する工程;

(f)前記第1保護膜および前記第2保護膜を有する状態で、前記基材に前記混合材を拡散することによって、前記酸化シリコン膜上に、酸化シリコンより誘電率が高く、前記基材のハフニウムおよび酸素と、前記混合材の金属元素とを含む混合膜を形成する工程;

(g)前記工程(f)の後、前記第2保護膜および前記第1保護膜を除去する工程;

(h)前記混合膜上に、導電性膜を形成する工程;

(i)前記導電性膜から構成されるゲート電極、前記混合膜および前記酸化シリコン膜から構成されるゲート絶縁膜を形成する工程。 - 以下の工程を含むCMISを備えた半導体装置の製造方法:

(a)前記CMISの一方を構成する第1MISトランジスタが形成される第1領域と、前記CMISの他方を構成する第2MISトランジスタが形成される第2領域とを有する半導体基板を準備する工程;

(b)前記半導体基板の主面上に、酸化シリコン膜を形成する工程;

(c)前記酸化シリコン膜上に、ハフニウムおよび酸素を含む膜状の基材を形成する工程;

(d)前記基材上に、金属元素のみからなる膜状の第1混合材を形成する工程;

(e)前記第1混合材上に、第1保護膜を形成する工程;

(f)前記第2領域の前記第1保護膜および前記第1混合材を除去する工程;

(g)前記第2領域の前記基材上に、前記基材より薄く、かつ、前記第1混合材の金属元素とは異なる金属元素のみからなる膜状の第2混合材を形成する工程;

(h)前記第2混合材上に、第2保護膜を形成する工程;

(i)前記第1保護膜および前記第2保護膜を有する状態で、前記第1領域の前記基材に前記第1混合材を拡散すると共に、前記第2領域の前記基材に前記第2混合材を拡散することによって、

前記第1領域では、前記酸化シリコン膜上に、酸化シリコンより誘電率が高く、前記基材のハフニウムおよび酸素と、前記第1混合材の金属元素とを含む第1混合膜を形成し、

前記第2領域では、前記酸化シリコン膜上に、酸化シリコンより誘電率が高く、前記基材のハフニウムおよび酸素と、前記第2混合材の金属元素とを含む第2混合膜を形成する工程;

(j)前記工程(i)の後、前記第1保護膜および前記第2保護膜を除去する工程;

(k)前記第1混合膜および前記第2混合膜上に、導電性膜を形成する工程;

(l)前記導電性膜から構成される前記第1MISトランジスタのゲート電極、前記第1混合膜および前記酸化シリコン膜から構成される前記第1MISトランジスタのゲート絶縁膜を形成し、

前記導電性膜から構成される前記第2MISトランジスタのゲート電極、前記第2混合膜および前記酸化シリコン膜から構成される前記第2MISトランジスタのゲート絶縁膜を形成する工程。 - 前記工程(d)において、酸化ハフニウムより電気陰性度が大きい酸化金属物を構成する金属元素からなる前記第1混合材を形成し、

前記工程(g)において、酸化ハフニウムより電気陰性度が小さい酸化金属物を構成する金属元素からなる前記第2混合材を形成することを特徴とする請求項12記載の半導体装置の製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008208472A JP5314964B2 (ja) | 2008-08-13 | 2008-08-13 | 半導体装置の製造方法 |

| TW098117118A TWI456697B (zh) | 2008-08-13 | 2009-05-22 | 半導體裝置之製造方法及半導體裝置 |

| CN2009101584767A CN101651120B (zh) | 2008-08-13 | 2009-07-08 | 半导体器件的制造方法和半导体器件 |

| US12/537,875 US8288221B2 (en) | 2008-08-13 | 2009-08-07 | Method of manufacturing semiconductor device and semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008208472A JP5314964B2 (ja) | 2008-08-13 | 2008-08-13 | 半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010045210A JP2010045210A (ja) | 2010-02-25 |

| JP2010045210A5 JP2010045210A5 (ja) | 2011-09-15 |

| JP5314964B2 true JP5314964B2 (ja) | 2013-10-16 |

Family

ID=41673309

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008208472A Expired - Fee Related JP5314964B2 (ja) | 2008-08-13 | 2008-08-13 | 半導体装置の製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US8288221B2 (ja) |

| JP (1) | JP5314964B2 (ja) |

| CN (1) | CN101651120B (ja) |

| TW (1) | TWI456697B (ja) |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5329294B2 (ja) * | 2009-04-30 | 2013-10-30 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| US8399344B2 (en) * | 2009-10-07 | 2013-03-19 | Asm International N.V. | Method for adjusting the threshold voltage of a gate stack of a PMOS device |

| US8659155B2 (en) | 2009-11-05 | 2014-02-25 | Taiwan Semiconductor Manufacturing Company, Ltd. | Mechanisms for forming copper pillar bumps |

| US8343865B2 (en) * | 2010-01-21 | 2013-01-01 | Renesas Electronics Corporation | Semiconductor device having dual work function metal |

| JP2011176173A (ja) * | 2010-02-25 | 2011-09-08 | Renesas Electronics Corp | 半導体装置及びその製造方法 |

| JP5548550B2 (ja) * | 2010-07-30 | 2014-07-16 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| JP2012044013A (ja) * | 2010-08-20 | 2012-03-01 | Renesas Electronics Corp | 半導体装置の製造方法 |

| JP2013098214A (ja) * | 2011-10-28 | 2013-05-20 | Elpida Memory Inc | 半導体装置及びその製造方法 |

| JP5638559B2 (ja) * | 2012-03-26 | 2014-12-10 | 株式会社東芝 | 半導体装置 |

| JP5823353B2 (ja) * | 2012-06-20 | 2015-11-25 | 株式会社東芝 | 不揮発性半導体記憶装置の製造方法 |

| EP2717308A1 (en) | 2012-10-08 | 2014-04-09 | Imec | A method for manufacturing a dual work function semiconductor device |

| KR20140122585A (ko) * | 2013-04-10 | 2014-10-20 | 삼성전자주식회사 | 반도체 소자 및 이의 제조 방법 |

| US9263270B2 (en) * | 2013-06-06 | 2016-02-16 | Globalfoundries Inc. | Method of forming a semiconductor device structure employing fluorine doping and according semiconductor device structure |

| JP6581446B2 (ja) * | 2015-09-09 | 2019-09-25 | 東芝メモリ株式会社 | 絶縁膜及び記憶装置 |

| JP2017092191A (ja) * | 2015-11-06 | 2017-05-25 | 株式会社デンソー | 炭化珪素半導体装置 |

| CN106952917A (zh) * | 2016-01-07 | 2017-07-14 | 中国科学院上海微系统与信息技术研究所 | 一种soi六晶体管sram单元及其制作方法 |

| CN113809012B (zh) * | 2020-06-12 | 2024-02-09 | 长鑫存储技术有限公司 | 半导体器件及其制造方法 |

Family Cites Families (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR19990014155A (ko) * | 1997-07-24 | 1999-02-25 | 윌리엄 비. 켐플러 | 고 유전율 실리케이트 게이트 유전체 |

| JP3944367B2 (ja) * | 2001-02-06 | 2007-07-11 | 松下電器産業株式会社 | 絶縁膜の形成方法及び半導体装置の製造方法 |

| JP4895430B2 (ja) | 2001-03-22 | 2012-03-14 | ルネサスエレクトロニクス株式会社 | 半導体装置及び半導体装置の製造方法 |

| US7326988B2 (en) * | 2002-07-02 | 2008-02-05 | Matsushita Electric Industrial Co., Ltd. | Semiconductor device and method for fabricating the same |

| WO2004008544A1 (ja) * | 2002-07-16 | 2004-01-22 | Nec Corporation | 半導体装置、その製造方法およびその製造装置 |

| JPWO2005038929A1 (ja) * | 2003-10-15 | 2007-02-08 | 日本電気株式会社 | 半導体装置の製造方法 |

| US6897095B1 (en) * | 2004-05-12 | 2005-05-24 | Freescale Semiconductor, Inc. | Semiconductor process and integrated circuit having dual metal oxide gate dielectric with single metal gate electrode |

| JP4005055B2 (ja) * | 2004-05-25 | 2007-11-07 | Necエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| US7060568B2 (en) * | 2004-06-30 | 2006-06-13 | Intel Corporation | Using different gate dielectrics with NMOS and PMOS transistors of a complementary metal oxide semiconductor integrated circuit |

| JP4792716B2 (ja) | 2004-07-06 | 2011-10-12 | 日本電気株式会社 | 半導体装置およびその製造方法 |

| US7087476B2 (en) | 2004-07-28 | 2006-08-08 | Intel Corporation | Using different gate dielectrics with NMOS and PMOS transistors of a complementary metal oxide semiconductor integrated circuit |

| JP4372024B2 (ja) * | 2005-02-14 | 2009-11-25 | 株式会社東芝 | Cmos半導体装置 |

| JP2006295131A (ja) * | 2005-03-17 | 2006-10-26 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| JP4850458B2 (ja) | 2005-09-12 | 2012-01-11 | 富士通セミコンダクター株式会社 | 半導体装置およびその製造方法 |

| JP2007080995A (ja) * | 2005-09-13 | 2007-03-29 | Toshiba Corp | 半導体装置 |

| JP2007243009A (ja) * | 2006-03-10 | 2007-09-20 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| JPWO2007116470A1 (ja) * | 2006-03-31 | 2009-08-20 | 富士通株式会社 | 半導体装置及びその製造方法 |

| JPWO2007138693A1 (ja) * | 2006-05-31 | 2009-10-01 | 富士通株式会社 | 半導体デバイスおよびその作製方法 |

| JP4282691B2 (ja) * | 2006-06-07 | 2009-06-24 | 株式会社東芝 | 半導体装置 |

| JP2008311464A (ja) * | 2007-06-15 | 2008-12-25 | National Institute Of Advanced Industrial & Technology | 半導体装置とその製造方法 |

| TWI492367B (zh) * | 2007-12-03 | 2015-07-11 | 瑞薩電子股份有限公司 | Cmos半導體裝置之製造方法 |

-

2008

- 2008-08-13 JP JP2008208472A patent/JP5314964B2/ja not_active Expired - Fee Related

-

2009

- 2009-05-22 TW TW098117118A patent/TWI456697B/zh not_active IP Right Cessation

- 2009-07-08 CN CN2009101584767A patent/CN101651120B/zh active Active

- 2009-08-07 US US12/537,875 patent/US8288221B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| TWI456697B (zh) | 2014-10-11 |

| JP2010045210A (ja) | 2010-02-25 |

| TW201013847A (en) | 2010-04-01 |

| CN101651120A (zh) | 2010-02-17 |

| US8288221B2 (en) | 2012-10-16 |

| CN101651120B (zh) | 2013-10-02 |

| US20100038729A1 (en) | 2010-02-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5314964B2 (ja) | 半導体装置の製造方法 | |

| US7732872B2 (en) | Integration scheme for multiple metal gate work function structures | |

| JP5128121B2 (ja) | 高性能cmos回路及びその製造方法 | |

| CN103426928B (zh) | 半导体器件和该器件的制造方法 | |

| US9349742B2 (en) | Embedded memory and methods of forming the same | |

| CN101421839B (zh) | 使用金属/金属氮化物双层结构作为自对准强按比例缩放cmos器件中的栅电极 | |

| JP5550286B2 (ja) | 半導体装置の製造方法 | |

| US7863127B2 (en) | Manufacturing method of semiconductor device | |

| CN102822959B (zh) | 半导体器件及其制造方法 | |

| TW202234595A (zh) | 半導體結構 | |

| US20080036008A1 (en) | Semiconductor device and method for manufacturing the same | |

| TWI469262B (zh) | 半導體裝置之製造方法及半導體裝置 | |

| KR102434987B1 (ko) | 박막 형성 방법 및 반도체 소자의 제조 방법 | |

| US8018004B2 (en) | Semiconductor device and manufacturing method thereof | |

| WO2011057492A1 (zh) | 一种半导体器件及其制造方法 | |

| US20100252888A1 (en) | Semiconductor device | |

| US20110284971A1 (en) | Semiconductor device and manufacturing method thereof | |

| JP2009267180A (ja) | 半導体装置 | |

| JP2007005721A (ja) | 半導体装置およびその製造方法 | |

| JP2008124393A (ja) | 半導体装置の製造方法 | |

| WO2010146641A1 (ja) | 半導体装置及びその製造方法 | |

| JP4163164B2 (ja) | 半導体装置およびその製造方法 | |

| JP5291992B2 (ja) | 半導体装置の製造方法 | |

| JP2010062499A (ja) | 半導体装置および半導体装置の製造方法 | |

| US20120068275A1 (en) | Semiconductor device and method for fabricating the same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100528 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110801 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110801 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130222 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130305 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130422 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130611 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130708 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5314964 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |