JP5135683B2 - 振動型ジャイロセンサ及び振動素子の製造方法 - Google Patents

振動型ジャイロセンサ及び振動素子の製造方法 Download PDFInfo

- Publication number

- JP5135683B2 JP5135683B2 JP2005374324A JP2005374324A JP5135683B2 JP 5135683 B2 JP5135683 B2 JP 5135683B2 JP 2005374324 A JP2005374324 A JP 2005374324A JP 2005374324 A JP2005374324 A JP 2005374324A JP 5135683 B2 JP5135683 B2 JP 5135683B2

- Authority

- JP

- Japan

- Prior art keywords

- vibration

- vibrator

- layer

- gyro sensor

- vibration element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title description 208

- 238000004519 manufacturing process Methods 0.000 title description 42

- 239000010410 layer Substances 0.000 claims description 468

- 239000000758 substrate Substances 0.000 claims description 256

- 238000001514 detection method Methods 0.000 claims description 152

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 89

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 89

- 230000003014 reinforcing effect Effects 0.000 claims description 54

- 239000011241 protective layer Substances 0.000 claims description 52

- 230000002093 peripheral effect Effects 0.000 claims description 44

- 230000010355 oscillation Effects 0.000 claims description 30

- 239000000463 material Substances 0.000 claims description 22

- 229910021421 monocrystalline silicon Inorganic materials 0.000 claims description 17

- 238000007789 sealing Methods 0.000 claims description 3

- 230000008569 process Effects 0.000 description 149

- 238000005530 etching Methods 0.000 description 144

- 239000010408 film Substances 0.000 description 130

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 115

- 229910052710 silicon Inorganic materials 0.000 description 115

- 239000010703 silicon Substances 0.000 description 115

- 239000010409 thin film Substances 0.000 description 56

- 230000015572 biosynthetic process Effects 0.000 description 43

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 41

- 239000010931 gold Substances 0.000 description 41

- 229910052737 gold Inorganic materials 0.000 description 41

- 238000000059 patterning Methods 0.000 description 36

- 229920002120 photoresistant polymer Polymers 0.000 description 32

- 238000012545 processing Methods 0.000 description 28

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 25

- 238000005520 cutting process Methods 0.000 description 24

- 238000004544 sputter deposition Methods 0.000 description 23

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 21

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 20

- 230000003139 buffering effect Effects 0.000 description 20

- 239000007789 gas Substances 0.000 description 18

- 230000008859 change Effects 0.000 description 17

- 230000010287 polarization Effects 0.000 description 16

- 238000010586 diagram Methods 0.000 description 14

- 230000000694 effects Effects 0.000 description 14

- 230000006870 function Effects 0.000 description 13

- 230000001965 increasing effect Effects 0.000 description 13

- 238000006243 chemical reaction Methods 0.000 description 12

- 238000007747 plating Methods 0.000 description 12

- 239000004065 semiconductor Substances 0.000 description 12

- 239000010936 titanium Substances 0.000 description 12

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 11

- 239000010949 copper Substances 0.000 description 11

- 238000009413 insulation Methods 0.000 description 11

- 238000001020 plasma etching Methods 0.000 description 11

- 229910052719 titanium Inorganic materials 0.000 description 11

- 230000009471 action Effects 0.000 description 10

- 229910052786 argon Inorganic materials 0.000 description 10

- 230000007547 defect Effects 0.000 description 10

- 238000001039 wet etching Methods 0.000 description 10

- 230000007423 decrease Effects 0.000 description 9

- 229910052697 platinum Inorganic materials 0.000 description 9

- 230000002787 reinforcement Effects 0.000 description 9

- 238000002844 melting Methods 0.000 description 8

- 230000008018 melting Effects 0.000 description 8

- 230000001681 protective effect Effects 0.000 description 8

- 230000000052 comparative effect Effects 0.000 description 7

- 239000013078 crystal Substances 0.000 description 7

- 229910052751 metal Inorganic materials 0.000 description 7

- 239000002184 metal Substances 0.000 description 7

- 230000035945 sensitivity Effects 0.000 description 7

- 230000001360 synchronised effect Effects 0.000 description 7

- KWYUFKZDYYNOTN-UHFFFAOYSA-M Potassium hydroxide Chemical compound [OH-].[K+] KWYUFKZDYYNOTN-UHFFFAOYSA-M 0.000 description 6

- 239000004020 conductor Substances 0.000 description 6

- 239000000428 dust Substances 0.000 description 6

- 238000000206 photolithography Methods 0.000 description 6

- 238000000992 sputter etching Methods 0.000 description 6

- WGTYBPLFGIVFAS-UHFFFAOYSA-M tetramethylammonium hydroxide Chemical compound [OH-].C[N+](C)(C)C WGTYBPLFGIVFAS-UHFFFAOYSA-M 0.000 description 6

- 238000007667 floating Methods 0.000 description 5

- 238000003754 machining Methods 0.000 description 5

- 230000007246 mechanism Effects 0.000 description 5

- 230000003647 oxidation Effects 0.000 description 5

- 238000007254 oxidation reaction Methods 0.000 description 5

- 230000003321 amplification Effects 0.000 description 4

- 238000013016 damping Methods 0.000 description 4

- 238000009616 inductively coupled plasma Methods 0.000 description 4

- 230000001678 irradiating effect Effects 0.000 description 4

- 238000003199 nucleic acid amplification method Methods 0.000 description 4

- 238000012360 testing method Methods 0.000 description 4

- 235000012431 wafers Nutrition 0.000 description 4

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- 239000012790 adhesive layer Substances 0.000 description 3

- 238000004458 analytical method Methods 0.000 description 3

- 239000012298 atmosphere Substances 0.000 description 3

- 239000003795 chemical substances by application Substances 0.000 description 3

- 230000006835 compression Effects 0.000 description 3

- 238000007906 compression Methods 0.000 description 3

- 239000000470 constituent Substances 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 238000006073 displacement reaction Methods 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- 238000002474 experimental method Methods 0.000 description 3

- 238000000227 grinding Methods 0.000 description 3

- 238000010438 heat treatment Methods 0.000 description 3

- 229910052451 lead zirconate titanate Inorganic materials 0.000 description 3

- DDFHBQSCUXNBSA-UHFFFAOYSA-N 5-(5-carboxythiophen-2-yl)thiophene-2-carboxylic acid Chemical compound S1C(C(=O)O)=CC=C1C1=CC=C(C(O)=O)S1 DDFHBQSCUXNBSA-UHFFFAOYSA-N 0.000 description 2

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- 229910004298 SiO 2 Inorganic materials 0.000 description 2

- 239000000853 adhesive Substances 0.000 description 2

- 230000001070 adhesive effect Effects 0.000 description 2

- 230000000903 blocking effect Effects 0.000 description 2

- 238000012937 correction Methods 0.000 description 2

- 230000002950 deficient Effects 0.000 description 2

- 229910003460 diamond Inorganic materials 0.000 description 2

- 239000010432 diamond Substances 0.000 description 2

- 238000009826 distribution Methods 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 230000005484 gravity Effects 0.000 description 2

- 230000001771 impaired effect Effects 0.000 description 2

- 239000011229 interlayer Substances 0.000 description 2

- 238000010030 laminating Methods 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 239000000155 melt Substances 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 238000004904 shortening Methods 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- 238000009825 accumulation Methods 0.000 description 1

- 238000007743 anodising Methods 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 239000010953 base metal Substances 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 239000003985 ceramic capacitor Substances 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 238000013329 compounding Methods 0.000 description 1

- 238000005094 computer simulation Methods 0.000 description 1

- 239000012141 concentrate Substances 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000007598 dipping method Methods 0.000 description 1

- 238000004043 dyeing Methods 0.000 description 1

- 239000007772 electrode material Substances 0.000 description 1

- 230000002708 enhancing effect Effects 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 238000005304 joining Methods 0.000 description 1

- HFGPZNIAWCZYJU-UHFFFAOYSA-N lead zirconate titanate Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ti+4].[Zr+4].[Pb+2] HFGPZNIAWCZYJU-UHFFFAOYSA-N 0.000 description 1

- 238000001755 magnetron sputter deposition Methods 0.000 description 1

- 239000003550 marker Substances 0.000 description 1

- 230000000873 masking effect Effects 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000003973 paint Substances 0.000 description 1

- 230000000149 penetrating effect Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 230000036470 plasma concentration Effects 0.000 description 1

- UPIXZLGONUBZLK-UHFFFAOYSA-N platinum Chemical compound [Pt].[Pt] UPIXZLGONUBZLK-UHFFFAOYSA-N 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 238000003825 pressing Methods 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 230000035939 shock Effects 0.000 description 1

- 229910000679 solder Inorganic materials 0.000 description 1

- 238000005476 soldering Methods 0.000 description 1

- 230000000087 stabilizing effect Effects 0.000 description 1

- 238000003756 stirring Methods 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- 230000009466 transformation Effects 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- 238000011179 visual inspection Methods 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

- 238000003466 welding Methods 0.000 description 1

Images

Classifications

-

- F—MECHANICAL ENGINEERING; LIGHTING; HEATING; WEAPONS; BLASTING

- F21—LIGHTING

- F21V—FUNCTIONAL FEATURES OR DETAILS OF LIGHTING DEVICES OR SYSTEMS THEREOF; STRUCTURAL COMBINATIONS OF LIGHTING DEVICES WITH OTHER ARTICLES, NOT OTHERWISE PROVIDED FOR

- F21V15/00—Protecting lighting devices from damage

- F21V15/01—Housings, e.g. material or assembling of housing parts

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B81—MICROSTRUCTURAL TECHNOLOGY

- B81B—MICROSTRUCTURAL DEVICES OR SYSTEMS, e.g. MICROMECHANICAL DEVICES

- B81B3/00—Devices comprising flexible or deformable elements, e.g. comprising elastic tongues or membranes

- B81B3/0064—Constitution or structural means for improving or controlling the physical properties of a device

- B81B3/0067—Mechanical properties

-

- F—MECHANICAL ENGINEERING; LIGHTING; HEATING; WEAPONS; BLASTING

- F21—LIGHTING

- F21V—FUNCTIONAL FEATURES OR DETAILS OF LIGHTING DEVICES OR SYSTEMS THEREOF; STRUCTURAL COMBINATIONS OF LIGHTING DEVICES WITH OTHER ARTICLES, NOT OTHERWISE PROVIDED FOR

- F21V1/00—Shades for light sources, i.e. lampshades for table, floor, wall or ceiling lamps

- F21V1/14—Covers for frames; Frameless shades

- F21V1/16—Covers for frames; Frameless shades characterised by the material

- F21V1/22—Covers for frames; Frameless shades characterised by the material the material being plastics

-

- F—MECHANICAL ENGINEERING; LIGHTING; HEATING; WEAPONS; BLASTING

- F21—LIGHTING

- F21V—FUNCTIONAL FEATURES OR DETAILS OF LIGHTING DEVICES OR SYSTEMS THEREOF; STRUCTURAL COMBINATIONS OF LIGHTING DEVICES WITH OTHER ARTICLES, NOT OTHERWISE PROVIDED FOR

- F21V1/00—Shades for light sources, i.e. lampshades for table, floor, wall or ceiling lamps

- F21V1/14—Covers for frames; Frameless shades

- F21V1/16—Covers for frames; Frameless shades characterised by the material

- F21V1/24—Covers for frames; Frameless shades characterised by the material the material being metal

-

- F—MECHANICAL ENGINEERING; LIGHTING; HEATING; WEAPONS; BLASTING

- F21—LIGHTING

- F21V—FUNCTIONAL FEATURES OR DETAILS OF LIGHTING DEVICES OR SYSTEMS THEREOF; STRUCTURAL COMBINATIONS OF LIGHTING DEVICES WITH OTHER ARTICLES, NOT OTHERWISE PROVIDED FOR

- F21V17/00—Fastening of component parts of lighting devices, e.g. shades, globes, refractors, reflectors, filters, screens, grids or protective cages

- F21V17/10—Fastening of component parts of lighting devices, e.g. shades, globes, refractors, reflectors, filters, screens, grids or protective cages characterised by specific fastening means or way of fastening

-

- F—MECHANICAL ENGINEERING; LIGHTING; HEATING; WEAPONS; BLASTING

- F21—LIGHTING

- F21V—FUNCTIONAL FEATURES OR DETAILS OF LIGHTING DEVICES OR SYSTEMS THEREOF; STRUCTURAL COMBINATIONS OF LIGHTING DEVICES WITH OTHER ARTICLES, NOT OTHERWISE PROVIDED FOR

- F21V19/00—Fastening of light sources or lamp holders

- F21V19/0075—Fastening of light sources or lamp holders of tubular light sources, e.g. ring-shaped fluorescent light sources

- F21V19/008—Fastening of light sources or lamp holders of tubular light sources, e.g. ring-shaped fluorescent light sources of straight tubular light sources, e.g. straight fluorescent tubes, soffit lamps

- F21V19/0085—Fastening of light sources or lamp holders of tubular light sources, e.g. ring-shaped fluorescent light sources of straight tubular light sources, e.g. straight fluorescent tubes, soffit lamps at least one conductive element acting as a support means, e.g. resilient contact blades, piston-like contact

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01C—MEASURING DISTANCES, LEVELS OR BEARINGS; SURVEYING; NAVIGATION; GYROSCOPIC INSTRUMENTS; PHOTOGRAMMETRY OR VIDEOGRAMMETRY

- G01C19/00—Gyroscopes; Turn-sensitive devices using vibrating masses; Turn-sensitive devices without moving masses; Measuring angular rate using gyroscopic effects

- G01C19/56—Turn-sensitive devices using vibrating masses, e.g. vibratory angular rate sensors based on Coriolis forces

- G01C19/5642—Turn-sensitive devices using vibrating masses, e.g. vibratory angular rate sensors based on Coriolis forces using vibrating bars or beams

- G01C19/5663—Manufacturing; Trimming; Mounting; Housings

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01P—MEASURING LINEAR OR ANGULAR SPEED, ACCELERATION, DECELERATION, OR SHOCK; INDICATING PRESENCE, ABSENCE, OR DIRECTION, OF MOVEMENT

- G01P15/00—Measuring acceleration; Measuring deceleration; Measuring shock, i.e. sudden change of acceleration

- G01P15/02—Measuring acceleration; Measuring deceleration; Measuring shock, i.e. sudden change of acceleration by making use of inertia forces using solid seismic masses

- G01P15/08—Measuring acceleration; Measuring deceleration; Measuring shock, i.e. sudden change of acceleration by making use of inertia forces using solid seismic masses with conversion into electric or magnetic values

- G01P15/0802—Details

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B81—MICROSTRUCTURAL TECHNOLOGY

- B81B—MICROSTRUCTURAL DEVICES OR SYSTEMS, e.g. MICROMECHANICAL DEVICES

- B81B2201/00—Specific applications of microelectromechanical systems

- B81B2201/02—Sensors

- B81B2201/0285—Vibration sensors

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B81—MICROSTRUCTURAL TECHNOLOGY

- B81B—MICROSTRUCTURAL DEVICES OR SYSTEMS, e.g. MICROMECHANICAL DEVICES

- B81B2203/00—Basic microelectromechanical structures

- B81B2203/01—Suspended structures, i.e. structures allowing a movement

- B81B2203/0118—Cantilevers

Landscapes

- Engineering & Computer Science (AREA)

- General Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Radar, Positioning & Navigation (AREA)

- Remote Sensing (AREA)

- Mechanical Engineering (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Gyroscopes (AREA)

Description

上記振動素子は、上記ランドに接続される複数の端子部が形成された実装面を有する基部と、この基部の側周部から片持ち梁状に一体に突設され上記基部の実装面と同一面を構成する基板対向面を有する振動子部とを有し、

上記振動子部の基板対向面には、第1電極層と、この第1電極層の上に積層された圧電層と、この圧電層の上に積層された第2電極層とがそれぞれ形成され、

上記振動子部の基端部位には、上記基部に向かって当該振動子部の断面積が次第に大きくなる補強部が形成されている。

シリコン基板の第1主面側にエッチング処理を施して、所定の傾斜角で傾斜するエッチング傾斜面を有するとともに上記第1主面からの厚みが当該振動素子の振動子部の厚みに対応する深さのエッチング凹部を形成するエッチング凹部形成工程と、

上記シリコン基板の前記エッチング凹部と対向する第2主面上に、前記圧電膜層及び第1,第2電極層を形成する電極形成工程と、

上記エッチング凹部内において前記振動子部の外形を形成する貫通溝からなるコ字状の外形溝をパターン形成する外形溝形成工程と、

上記外形溝の両端部にそれぞれ達するように上記シリコン基板を切断して当該振動素子の基部を切り分ける切断工程とを有し、

上記外形溝形成工程では、上記外形溝の両端部を上記エッチング凹部の途中箇所に形成することによって、上記振動子部の基端部位に、上記基部に向かって当該振動子部の断面積が次第に大きくなる補強部を形成する。

なお、本発明はこれに限定されることなく、本発明の技術的思想に基づいて種々の変形が可能である。また、本明細書においては、以下に説明するように構成部材の各部位について具体的な寸法値を挙げて説明しているが、各寸法値は中心基準値である。各部位は、この中心基準値に限定された寸法値で形成されることに限定されず、一般的な公差範囲の寸法値をもって形成されることは勿論である。また、振動型ジャイロセンサは、かかる寸法値の形状に限定されず、特性仕様に応じて各部が適宜形成される。

[振動型ジャイロセンサの概略構成]

振動型ジャイロセンサ1は、図1に示すように支持基板2と、この支持基板2の第1主面2−1上に組み付けられて部品実装空間部3を構成するカバー部材15とにより外観部材を構成し、例えばビデオカメラに搭載されて手振れ補正機構を構成する。また、振動型ジャイロセンサ1は、例えばバーチャルリアリティ装置に用いられて動作検知器を構成し、或いはカーナビゲーション装置に用いられて方向検知器を構成する。

振動型ジャイロセンサ1は、支持基板2を薄厚とすることによって小型、薄型化が図られていることから、外部から加えられる振動や衝撃等の外部負荷によって支持基板2に歪みや応力が発生することがある。そこで、本実施の形態では、支持基板2に外部負荷の緩衝構造が設けられることによって、歪みや応力が生じた場合でも支持基板2に搭載した振動素子20への影響が低減されるように構成されている。

次に、支持基板2には、振動素子20X,20Yに対応して部品実装領域6に、振動子部23をその厚さ方向に自由振動させる空間部を構成する凹部11A,11B(以下、個別に説明する場合を除いて間隔構成凹部11と総称する。)が形成されている。間隔構成凹部11は、支持基板2の第1主面2−1に対して例えばエッチング加工や溝切り加工を施すことで所定の深さと開口寸法を有する矩形の有底溝状に形成される。

振動素子20は、後述するようにシリコン基板21の第2主面21−2によって構成される基部22の第2主面(22−2)が支持基板2に対する固定面(実装面)を構成して上述した振動素子実装領域13上に実装される。図4に示すように基部22の実装面22−2には、第1端子部25A〜第4端子部25D(以下、個別に説明する場合を除いて端子部25と総称する。)が形成されるとともに、これら端子部25上にそれぞれ金属凸部として第1金バンプ26A〜第4金バンプ26D(以下、個別に説明する場合を除いて金バンプ26と総称する。)が形成されている。

また、各金バンプ26を基部22から突出される振動子部23の基端部(根元部位43(図35参照))から振動子部23の幅寸法t6の2倍を半径とする領域の外側領域に位置して形成することにより、金バンプ26による振動子部23の振動動作を吸収する作用を低減して高Q値を保持することが可能となる。

さらに、少なくとも1個の金バンプ26が、振動子部23の基端部から基部22の厚み寸法t1(図7参照)の2倍の範囲の領域内に形成されることで、振動子部23の振動動作が基部22に伝達されて共振周波数のズレを生じさせることが防止されるようになる。

さて、本実施の形態の振動素子20は、図7に示すように、振動子部23が、基部22の第2主面(実装面)22−2と同一面を構成する第2主面(基板対向面)23−2を有し、一端部を基部22に一体化されて片持ち梁状に突設されている。振動子部23は、その上面23−1が図8に示すように基部22の第1主面(上面)22−1から段落ちされることによって所定の厚みとされる。振動子部23は、所定の長さと断面積を有して基部22の一側周部22−3と一体に形成された断面矩形の片持ち梁によって構成される。

本実施の形態の振動素子20は、振動子部23に補強部129を形成することで基端部位或いはその近傍部位の機械的強度を向上させている。これにより、大きな外部負荷が加えられた場合でも振動子部23の破損発生を抑制できる。補強部129は、図8に示すように、振動子部23が突設される基部22の側周部22−3の部位において断面寸法を最大とするとともに、上述した長さ寸法t29の領域で厚みと幅が次第に小さくなる断面形状に形成される。

一方、シリコン基板21には、その表面に極めて微細な凹凸やマイクロクラック等が存在している。また、シリコン基板21には、第2主面21−2側からダイヤフラム部38に反応性イオンエッチング処理を施して上述した振動子部23の外形を切り抜く外形溝形成処理が施される。その際に、振動子部23の側面と第1主面23−1に跨る稜線部位にプラズマの流れにより微細な筋状の凹凸も生じる。これらの微細な凹凸やクラックについては、図9Aに示すように微細凹凸部127と総称する。なお、図では凹凸部127をやや誇張して示している。

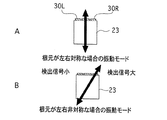

振動素子20には、後述する振動素子製造工程により、図4に示すように振動子部23の第2主面(基板対向面)23−2上に長さ方向の略全長に亘って、基準電極層(第1電極層)27と、圧電薄膜層28と、駆動電極層(第2電極層)29とが積層形成されている。振動子部23の第2主面(基板対向面)23−2上には、駆動電極層29を挟んで一対の検出電極30R、30L(以下、個別に説明する場合を除いて検出電極30と総称する。)が形成されており、これら駆動電極層29と検出電極30とにより第2電極層が構成されている。

振動素子20には、図4に示すように基部22の第2主面(実装面)22−2上に、基準電極層27と第1端子部25Aとを接続する第1リード31Aが形成されるとともに、駆動電極層29と第3端子部25Cとを接続する第3リード31Cが形成されている。同様に、基部22の実装面22−2上には、第1検出電極30Rと第2端子部25Bとを接続する第2リード31Bが形成されるとともに、第2検出電極30Lと第4端子部25Dとを接続する第4リード31Dが形成されている。なお、各リード31A〜31Dについては、以下、個別に説明する場合を除いてリード31と総称する。

振動素子20には、図2及び図4に示すように、第2主面21−2側において基部22と振動子部23を被覆する絶縁保護層45が形成されている。絶縁保護層45は、第1層の第1アルミナ(酸化アルミニウム:Al2O3)層46と、第2層の酸化シリコン(SiO2)層47と、第3層の第2アルミナ層48とからなる3層構造によって構成される。

振動型ジャイロセンサ1においては、同一形状の第1振動素子20Xと第2振動素子20Yとを支持基板2に対して精密に位置決めして実装するために、支持基板2が各ランド4の位置を実装機側に認識される。振動素子20には、実装機によって認識された各ランド4に対して位置決めされて実装されるようにするために、基部22の第1主面(上面)22−1に位置合わせ用マーク32A,32B(以下、位置合わせ用マーク32と総称する。)が設けられている。

続いて、支持基板2の第1主面2−1を外部から遮蔽するカバー15の詳細について説明する。

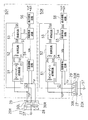

次に、振動型ジャイロセンサ1を駆動する回路構成について図6を参照して説明する。

以下、本実施の形態の振動型ジャイロセンサ1の製造方法について説明する。図10は振動型ジャイロセンサ1の製造方法を説明する主要工程フローである。

シリコン基板21は、外形寸法が、工程に用いられる設備仕様に応じて切り出し寸法が適宜決定され、例えば300×300(mm)とされる。シリコン基板21は図11に示すように平面視矩形状の基板に限らず、平面視円形のウェーハ形状でもよい。シリコン基板21は、作業性やコスト等によって厚み寸法を決定されるが、少なくとも振動素子20の基部22の厚み寸法よりも大きな厚みであればよい。シリコン基板21は、上述したように基部22の厚みが300μmであるとともに振動子部23の厚みが100μmであることから、300μm以上の基板が用いられる。

振動素子製造工程は、半導体プロセスの薄膜工程と同様の工程からなり、シリコン基板21の第1主面21−1側から各振動素子20の振動子部23を形成する部位を所定の厚み寸法とする上述したエッチング凹部37を形成するエッチング凹部形成工程を有する。

上述したエッチング凹部形成工程により、シリコン基板21にエッチング凹部37の底面と第2主面21−2との間に、所定の厚みを有する矩形のダイヤフラム部38が構成される。ダイヤフラム部38は、振動素子20の振動子部23を構成する。エッチング凹部形成工程の後、ダイヤフラム部38の第2主面21−2側を加工面として電極形成工程が施される。

次に、最上層に形成された第2電極層42に対してパターニング処理を施す第2電極層パターニング工程が行われる。第2電極層パターニング工程では図21及び図22に示すように所定形状の駆動電極層29と一対の検出電極30R,30Lとを形成する。

振動素子製造工程においては、上述した各工程を経て基部22の形成部位に対応して、駆動電極層29と検出電極30のリード接続部29−1,30R−1,30L−1及び端子部25B〜25Dを形成するとともに、これら各端子部25と一体化されるリード31B〜31Dを形成する。この際、リード31B〜31Dをリード接続部29−1,30R−1,30L−1と円滑に接続するために、図27及び図28に示す平坦化層24を形成する。

次に、基部22の形成部位に上述した第2端子部25B〜第4端子部25D及び第2リード31B〜第4リード31Dを形成する配線層形成工程が施される。配線層形成工程は、基部22の形成部位に全面に亘って感光性のフォトレジスト層を形成するとともに、このフォトレジスト層に対してフォトリソグラフ処理を施して第2端子部25B〜第4端子部25Dや第2リード31B〜第4リード31Dに対応する開口パターンを形成し、さらにスパッタリングによって各開口部内に導体層を形成して配線層を形成する。配線層形成工程は、所定の導体部を形成した後に、フォトレジスト層を除去して図29及び図30に示す第2端子部25B〜第4端子部25D及び第2リード31B〜第4リード31Dをパターン形成する。

続いて、上述した工程を経て主面上に端子部25とリード31とを形成した基部22と、各電極層と圧電薄膜層28とを形成した振動子部23の主面上に3層構成の絶縁保護層45を形成する絶縁保護層形成工程が施される。絶縁保護層形成工程は、レジスト層形成工程と、レジスト層パターニング形成工程と、第1アルミナ層形成工程と、酸化シリコン層形成工程と、第2アルミナ層形成工程と、レジスト層除去工程とを有する。

次に、シリコン基板21の第1主面21−1上に、図34に示すようにエッチングストップ層70を形成する工程が施される。エッチングストップ層70は、後述する外形溝形成工程をシリコン基板21に対して施す際に、第1主面21−1側にプラズマ集中が生じて所定のエッジ形状が形成されない形状不良の発生を抑制する機能を奏する。エッチングストップ層形成工程は、例えばシリコン基板21の第1主面21−1上に、スパッタ法によって全面に亘って厚みが500nm程度の酸化シリコンを形成する。

続いて、シリコン基板21上に形成される各振動素子20の圧電薄膜層28を一括して分極処理する分極処理工程が行われる。分極処理ための分極用配線にはCu配線が用いられる。Cu配線は、後述する分極処理を行った後に湿式エッチング処理によって容易に溶解することで、各振動素子20にダメージを与えることなく除去することが可能である。なお、分極用配線については、Cu配線に限定されず、上述した機能を奏する適宜の導電体によって形成してもよいことは勿論である。

次に、金バンプ形成工程が行われる。振動素子20は、上述したように支持基板2に表面実装されることから、各端子部25上に金バンプ26が形成される。金バンプ形成工程は、各端子部25に金ワイヤのボンディングツールを押し当てて所定形状のスタッドバンプを形成する。金バンプ形成工程においては、必要に応じて基部22上にいわゆるダミーバンプも形成される。なお、金バンプ26の他の形成方法としては、後述するめっきバンプ法がある。

続いて、シリコン基板21から各振動素子20を切り分ける切断工程が実施される。切断工程においては、例えばダイヤモンドカッタ等によって基部22の対応部位を切り分けることによって、各振動素子20の切り分けが行われる。切断工程では、ダイヤモンドカッタによって切断溝を形成した後に、シリコン基板21を折って切り分けが行われる。なお、切断工程は、砥石や研削によりシリコン基板21の面方位を利用して切断を行うようにしてもよい。

ここで、振動子部23の基端部位に構成される補強部129は、上述した振動素子製造工程を経て形成される。補強部129の形成に際しては、外形溝形成工程において、振動子部23の外形を切り抜く外形溝39の両端部39A,39B(図35)をエッチング凹部37の内周壁に形成されたエッチング傾斜面133の途中位置に形成される。そして、切断工程では、上述したように基部22の外形寸法に対応してシリコン基板21が切断されるが、基部22の側周部22−3の対応部位を外形溝39の両端部39A,39Bと接続するようにエッチング傾斜面133の途中で切断する。以上のようにして、図8に示したように振動子部23の基端部位がエッチング傾斜面133の傾斜によって外側面22−3に向かって次第に厚みを大きくする形状となる。これにより補強部129の縦補強部129Vが構成されるようにする。

以上の工程を経て製造された振動素子20は、シリコン基板21の第2主面21−2側を実装面として、支持基板2の第1主面2−1上に表面実装法によって実装される。振動素子20は、各端子部25に設けられた金バンプ26を支持基板2側の相対するランド4に位置合わせされる。この際、振動素子20は、上述したように位置合わせ用マーク32が読み取られて、実装機により位置と向きを高精度に位置決めされる。

振動素子製造工程においては、後述する調整工程に用いるレーザ装置を利用して、振動子部23に面取り部130或いは溶融面134が形成される。面取り部130或いは溶融面134の形成工程は、調整工程を行った後に振動子部23にレーザ加工を施すとバランスが崩れてしまうことがあることから、その前工程で行われる。

振動素子製造工程においては、上述したように誘導結合型プラズマを用いたエッチング処理を施してシリコン基板21から各振動素子20の振動子部23をそれぞれ高精度に切り抜くようにするが、材料取りの歩留まり等の条件によって各振動子部23がプラズマの出射中心線上に対して全て左右対称に位置して形成されることが困難である。このため、各振動素子20の位置ずれやその他種々の工程条件等によって各振動子部23の形状にバラツキが生じることがある。振動素子20は、例えば振動子部23の断面形状が台形状又は平行四辺形状に形成された場合に、正規の矩形形状の振動子部23との比較で垂直な上下振動からずれて中心軸線に対して質量が小さな側に傾いた状態で振動動作を行うようになる(図48参照)。

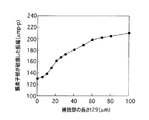

以上説明したように本実施の形態の振動型ジャイロセンサ1においては、振動素子20が、振動子部23の基端部位に基部22側に向かって次第に断面形状を大きくする補強部129(129V,129H)を形成することで、誤って本体機器を落下させる等によって大きな負荷が加えられた場合でも振動子部23の破損が防止される。補強部129は、以下の解析実験によって振動子部23の機械的強度を向上させることが確認される。

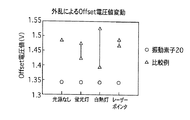

振動型ジャイロセンサ1においては、上述したように各電極層等を封止する絶縁保護層45を形成した振動素子20が備えられる。振動型ジャイロセンサ1においては、上述した絶縁保護層45の酸化シリコン層47の形成工程において、スパッタ槽のアルゴンガス圧仕様によって特性を異にした振動素子20を得る。図42は、アルゴンガス圧を0.4Pa〜0.6Paに変化させ、厚み寸法t27が500nmと固定した酸化シリコン層47をそれぞれ形成して絶縁保護層45を構成した各振動素子20を備えた振動型ジャイロセンサ1の出力電圧におけるノイズの発生率の特性図である。

また、上述した振動素子製造工程においては、半導体プロセスによって、単結晶シリコン基板21の第2主面21−2上に第1電極層40と圧電膜層41と第2電極層42とを薄膜形成した後に、これら各層に対して所定のパターニング処理を施して振動素子20を製造する。ところで、一般的な半導体プロセスにおいては、ボロンやリン等の不純物添加元素のドープ処理を施したNタイプ或いはPタイプのシリコン基板が用いられている。一般的なシリコン基板は、このために体積抵抗率が数十Ω・cmであり、ある程度の導電性を有し、グランド機能や薄膜形成時等に際しての下電極機能等を奏するようにしている。

上述の第1の実施の形態において、シリコン基板21に対して振動子部23の外形を切り抜く外形溝39の形成工程では、ICP−RIE(誘導結合型プラズマ反応性イオンエッチング)法が用いられている。この方法は、シリコン基板21に対して垂直かつ高アスペクト比で溝加工を行える点で非常に優れている。

上述の第1の実施の形態において、シリコン基板21に対して振動子部23の外形を切り抜く外形溝39の形成工程では、ICP−RIE法が用いられている。この方法は、シリコン基板21に対して垂直かつ高アスペクト比で溝加工を行える点で非常に優れている。

上述の第1の実施の形態において説明したように、振動素子20の振動子部23の表面(基板対向面23−2)には、基準電極層27、圧電薄膜層28および駆動電極層29が積層形成され、更にこれらの圧電層及び電極層は、外気中の水分や塵埃の付着から保護するための絶縁保護層45で被覆されている。これら圧電薄膜層28、電極層および保護層は、100μm程度の薄い振動子部23の表面に形成されるため、これらの形成膜の材料選択によっては材料のもつ応力により振動子部23自体が反ってしまう可能性が高い。

1.複数個のランドを有する配線パターンが形成された支持基板と、この支持基板の表面に実装された振動素子とを備えた振動型ジャイロセンサにおいて、

上記振動素子は、上記ランドに接続される複数の端子部が形成された実装面を有する基部と、この基部の側周部から片持ち梁状に一体に突設され上記基部の実装面と同一面を構成する基板対向面を有する振動子部とを有し、

上記振動子部の基板対向面には、第1電極層と、この第1電極層の上に積層された圧電層と、この圧電層の上に積層された第2電極層と、これら第1電極層、圧電層及び第2電極層を封止する絶縁保護層とがそれぞれ形成されていることを特徴とする振動型ジャイロセンサ。

2.上記絶縁保護層は、少なくとも酸化シリコン層を含んでなる上記1に記載の振動型ジャイロセンサ。

3.上記酸化シリコン層の上層及び下層のうち少なくとも下層側に密着層が形成されている上記2に記載の振動型ジャイロセンサ。

4.上記密着層はアルミナ層である上記3に記載の振動型ジャイロセンサ。

5.上記絶縁保護層は、上記第2電極層の少なくとも2倍の厚みを有する上記1に記載の振動型ジャイロセンサ。

6.上記絶縁保護層は、上記第1電極層よりも幅広で、かつ上記振動子部の外周縁に沿って前記振動子部の基板対向面を露出させて形成されている上記1に記載の振動型ジャイロセンサ。

7.上記振動子部の上面側には、当該振動子部の反り量を制御する反り制御膜が形成されている上記1に記載の振動型ジャイロセンサ。

8.上記振動子部の反り量が±5μm以内である上記7に記載の振動型ジャイロセンサ。

9.上記振動素子は、非ドープ単結晶シリコン基板を基材として形成されている上記1に記載の振動型ジャイロセンサ。

10.上記非ドープ単結晶シリコン基板の体積抵抗率は、100Ω・cm以上である上記9に記載の振動型ジャイロセンサ。

11.上記支持基板の表面は、遮光性のカバー部材で被覆されている上記1に記載の振動型ジャイロセンサ。

12.複数の端子部が形成された実装面を有する基部と、この基部の側周部から片持ち梁状に一体に突設され上記基部の実装面と同一面を構成する基板対向面を有する振動子部とを備えた振動型ジャイロセンサの製造方法において、

上記振動子部の基板対向面に第1電極層を形成する工程と、この第1電極層の上に圧電層を形成する工程と、この圧電層の上に第2電極層を形成する工程と、上記圧電層及び第1,第2電極層を被覆する絶縁保護層を形成する工程とを有することを特徴とする振動型ジャイロセンサの製造方法。

13.上記絶縁保護層は、上記振動子部の基板対向面上に密着層を形成する工程と、この密着層の上に酸化シリコン層を形成する工程とを有する上記12に記載の振動型ジャイロセンサの製造方法。

14.上記酸化シリコン層は、0.4Pa以下でかつ放電限界の下限値以上のアルゴンガス雰囲気中でスパッタ法により成膜される上記13に記載の振動型ジャイロセンサの製造方法。

15.上記絶縁保護層を形成する工程では、上記酸化シリコン層の上にレジスト密着層を形成する工程を更に有する上記13に記載の振動型ジャイロセンサの製造方法。

Claims (11)

- 複数個のランドを有する配線パターンが形成された支持基板と、この支持基板の表面に実装された振動素子と、前記振動素子を駆動する駆動検出回路とを備え、

前記振動素子は、前記ランドに接続される複数の端子部が形成された第1の面を有する基部と、この基部の側周部から片持ち梁状に一体に突設され前記基部の前記第1の面と同一面を構成する第2の面を有する振動子部とを有し、

前記振動子部の前記第2の面には、第1電極層と、この第1電極層の上に積層された圧電層と、この圧電層の上に積層された駆動電極と一対の検出電極とを含む第2電極層とがそれぞれ形成され、

前記振動子部の上面は、前記基部の上面から傾斜部を介して段落ち形成されており、

前記駆動検出回路は、前記駆動電極に所定周波数の発振出力を印加して前記振動子部を振動させ、コリオリ力による前記一対の検出電極の出力から角速度を検出し、

前記振動子部の基端部位には、前記基部に向かって当該振動子部の断面積が次第に大きくなる補強部が形成され、

前記補強部は、前記振動子部の基端部位上面側に前記傾斜部に沿って形成された縦補強部である

振動型ジャイロセンサ。 - 請求項1に記載の振動型ジャイロセンサであって、

前記第1の面は実装面であり、前記第2の面は基板対向面である

振動型ジャイロセンサ。 - 請求項2に記載の振動型ジャイロセンサであって、

前記振動子部の基板対向面とは反対側の面と両側面との間の稜線部に面取り部が形成されている

振動型ジャイロセンサ。 - 請求項2に記載の振動型ジャイロセンサであって、

前記振動子部の基板対向面以外の領域は、当該振動子部の振動特性調整用のレーザが照射される被加工領域とされる

振動型ジャイロセンサ。 - 請求項2に記載の振動型ジャイロセンサであって、

前記振動子部には、その基板対向面を除く面の少なくとも一部が溶融されて平滑面とされている

振動型ジャイロセンサ。 - 請求項1に記載の振動型ジャイロセンサであって、

前記支持基板の表面は、遮光性のカバー部材で被覆されている

振動型ジャイロセンサ。 - 請求項1に記載の振動型ジャイロセンサであって、

前記振動子部に、前記第1電極層、前記圧電層及び前記第2電極層を封止する絶縁保護層がさらに形成された

振動型ジャイロセンサ。 - 請求項7に記載の振動型ジャイロセンサであって、

前記絶縁保護層は、少なくとも酸化シリコン層を含んでなる

振動型ジャイロセンサ。 - 請求項7に記載の振動型ジャイロセンサであって、

前記絶縁保護層は、前記第2電極層の少なくとも2倍の厚みを有する

振動型ジャイロセンサ。 - 請求項7に記載の振動型ジャイロセンサであって、

前記振動子部の上面側には、当該振動子部の反り量を制御する反り制御膜が形成されている

振動型ジャイロセンサ。 - 請求項1に記載の振動型ジャイロセンサであって、

前記振動素子は、非ドープ単結晶シリコン基板を基材として形成されている

振動型ジャイロセンサ。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005374324A JP5135683B2 (ja) | 2005-02-28 | 2005-12-27 | 振動型ジャイロセンサ及び振動素子の製造方法 |

| EP20060003942 EP1696206B1 (en) | 2005-02-28 | 2006-02-27 | Method for manufacturing vibrating gyrosensor |

| US11/363,395 US7723901B2 (en) | 2005-02-28 | 2006-02-27 | Vibrating gyrosensor and vibrating element |

| KR20060019298A KR20060095517A (ko) | 2005-02-28 | 2006-02-28 | 진동형 자이로센서 및 진동 소자의 제조 방법 |

| CN2006100747373A CN1831478B (zh) | 2005-02-28 | 2006-02-28 | 用于制造振动陀螺传感器和振动元件的方法 |

Applications Claiming Priority (9)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005054844 | 2005-02-28 | ||

| JP2005054844 | 2005-02-28 | ||

| JP2005080473 | 2005-03-18 | ||

| JP2005080473 | 2005-03-18 | ||

| JP2005176870 | 2005-06-16 | ||

| JP2005176870 | 2005-06-16 | ||

| JP2005176869 | 2005-06-16 | ||

| JP2005176869 | 2005-06-16 | ||

| JP2005374324A JP5135683B2 (ja) | 2005-02-28 | 2005-12-27 | 振動型ジャイロセンサ及び振動素子の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007024861A JP2007024861A (ja) | 2007-02-01 |

| JP2007024861A5 JP2007024861A5 (ja) | 2009-02-19 |

| JP5135683B2 true JP5135683B2 (ja) | 2013-02-06 |

Family

ID=36581200

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005374324A Expired - Fee Related JP5135683B2 (ja) | 2005-02-28 | 2005-12-27 | 振動型ジャイロセンサ及び振動素子の製造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7723901B2 (ja) |

| EP (1) | EP1696206B1 (ja) |

| JP (1) | JP5135683B2 (ja) |

| KR (1) | KR20060095517A (ja) |

| CN (1) | CN1831478B (ja) |

Families Citing this family (32)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006284551A (ja) * | 2005-02-23 | 2006-10-19 | Sony Corp | 振動型ジャイロセンサ |

| JP2006250583A (ja) * | 2005-03-08 | 2006-09-21 | Sony Corp | 振動型ジャイロセンサ |

| GB2439606B (en) * | 2006-06-29 | 2011-08-17 | C Mac Quartz Crystals Ltd | An oscillator |

| JP2008224628A (ja) * | 2007-03-15 | 2008-09-25 | Sony Corp | 角速度センサ及び電子機器 |

| JP5328007B2 (ja) * | 2007-03-30 | 2013-10-30 | パナソニック株式会社 | 圧電体素子及びその製造方法 |

| JP4640459B2 (ja) * | 2008-07-04 | 2011-03-02 | ソニー株式会社 | 角速度センサ |

| US20100100083A1 (en) * | 2008-10-22 | 2010-04-22 | Scott Lundahl | Method of treatment for dermatologic disorders |

| JP4778548B2 (ja) * | 2008-12-17 | 2011-09-21 | 日本電波工業株式会社 | 圧電フレーム、圧電デバイス及び圧電フレームの製造方法 |

| JP5206709B2 (ja) * | 2009-03-18 | 2013-06-12 | 株式会社豊田中央研究所 | 可動体を備えている装置 |

| US20110001394A1 (en) * | 2009-07-02 | 2011-01-06 | Eta Sa | Piezoelectric thin-film tuning fork resonator |

| CN102668726B (zh) * | 2009-12-24 | 2015-07-01 | 古河电气工业株式会社 | 注塑成型基板与实装零件的安装结构 |

| JP5506035B2 (ja) * | 2010-02-23 | 2014-05-28 | 富士フイルム株式会社 | アクチュエータの製造方法 |

| JP4905574B2 (ja) * | 2010-03-25 | 2012-03-28 | 株式会社豊田中央研究所 | 可動部分を備えている積層構造体 |

| EP2582886B1 (en) | 2010-06-16 | 2019-11-27 | Mueller International, LLC | Infrastructure monitoring devices, systems, and methods |

| JP5765087B2 (ja) * | 2011-06-27 | 2015-08-19 | セイコーエプソン株式会社 | 屈曲振動片、その製造方法及び電子機器 |

| US9772250B2 (en) | 2011-08-12 | 2017-09-26 | Mueller International, Llc | Leak detector and sensor |

| JP5982896B2 (ja) * | 2012-03-13 | 2016-08-31 | セイコーエプソン株式会社 | センサー素子、センサーデバイスおよび電子機器 |

| CN103369423A (zh) * | 2013-07-25 | 2013-10-23 | 瑞声科技(南京)有限公司 | 入耳式耳机 |

| DE102014101372B4 (de) * | 2014-02-04 | 2015-10-08 | Vega Grieshaber Kg | Vibrationssensor mit geklebtem Antrieb |

| JP6519995B2 (ja) * | 2014-06-30 | 2019-05-29 | セイコーエプソン株式会社 | 振動素子、振動素子の製造方法、振動子、ジャイロセンサー、電子機器および移動体 |

| JP6507565B2 (ja) * | 2014-10-28 | 2019-05-08 | セイコーエプソン株式会社 | 電子デバイス、電子機器および移動体 |

| US10305178B2 (en) | 2016-02-12 | 2019-05-28 | Mueller International, Llc | Nozzle cap multi-band antenna assembly |

| US10283857B2 (en) | 2016-02-12 | 2019-05-07 | Mueller International, Llc | Nozzle cap multi-band antenna assembly |

| JP6759696B2 (ja) * | 2016-05-13 | 2020-09-23 | Tdk株式会社 | レンズ駆動装置 |

| JP6819216B2 (ja) * | 2016-10-26 | 2021-01-27 | セイコーエプソン株式会社 | ジャイロセンサー、ジャイロセンサーの製造方法、電子機器および移動体 |

| DE102017206388A1 (de) * | 2017-04-13 | 2018-10-18 | Robert Bosch Gmbh | Verfahren zum Schutz einer MEMS-Einheit vor Infrarot-Untersuchungen sowie MEMS-Einheit |

| US10859462B2 (en) | 2018-09-04 | 2020-12-08 | Mueller International, Llc | Hydrant cap leak detector with oriented sensor |

| US11342656B2 (en) | 2018-12-28 | 2022-05-24 | Mueller International, Llc | Nozzle cap encapsulated antenna system |

| US11473993B2 (en) | 2019-05-31 | 2022-10-18 | Mueller International, Llc | Hydrant nozzle cap |

| US11542690B2 (en) | 2020-05-14 | 2023-01-03 | Mueller International, Llc | Hydrant nozzle cap adapter |

| CN114743935B (zh) * | 2022-04-11 | 2024-08-30 | 中国工程物理研究院电子工程研究所 | 一种改善大功率器件封装互连层缺陷的方法 |

| DE102023202097A1 (de) | 2023-03-09 | 2024-09-12 | Robert Bosch Gesellschaft mit beschränkter Haftung | Verfahren und Vorrichtung zum Herstellen eines MEMS-Bauelementes |

Family Cites Families (30)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4494409A (en) * | 1981-05-29 | 1985-01-22 | Kabushiki Kaisha Toyota Chuo Kenkyusho | Engine vibration sensor |

| JPS638565A (ja) * | 1986-06-27 | 1988-01-14 | Mitsubishi Electric Corp | 半導体加速度検出装置 |

| JPH0623782B2 (ja) | 1988-11-15 | 1994-03-30 | 株式会社日立製作所 | 静電容量式加速度センサ及び半導体圧力センサ |

| JPH04315056A (ja) * | 1991-04-12 | 1992-11-06 | Tokai Rika Co Ltd | 加速度センサ |

| JP3218813B2 (ja) * | 1993-02-03 | 2001-10-15 | 松下電器産業株式会社 | 角速度センサおよびその製造方法 |

| US5802684A (en) * | 1993-09-14 | 1998-09-08 | Nikon Corporation | Process for producing a vibration angular-velocity sensor |

| JPH07113643A (ja) | 1993-10-15 | 1995-05-02 | Nikon Corp | 圧電振動角速度計 |

| US5539270A (en) * | 1993-11-19 | 1996-07-23 | Matsushita Electric Works, Ltd. | Acceleration detector |

| JPH07299905A (ja) * | 1994-05-09 | 1995-11-14 | Fujitsu Ltd | インクジェットヘッド及びその製造方法 |

| US5765046A (en) * | 1994-08-31 | 1998-06-09 | Nikon Corporation | Piezoelectric vibration angular velocity meter and camera using the same |

| SE9500729L (sv) * | 1995-02-27 | 1996-08-28 | Gert Andersson | Anordning för mätning av vinkelhastighet i enkristallint material samt förfarande för framställning av sådan |

| JP3682664B2 (ja) * | 1995-10-27 | 2005-08-10 | Necトーキン株式会社 | 圧電振動ジャイロ |

| JP3599880B2 (ja) * | 1996-03-12 | 2004-12-08 | オリンパス株式会社 | カンチレバーチップ |

| JPH1019574A (ja) * | 1996-06-27 | 1998-01-23 | Nikon Corp | 圧電振動角速度計の製造方法 |

| JPH10339638A (ja) * | 1997-06-06 | 1998-12-22 | Murata Mfg Co Ltd | 角速度センサ |

| JP2000055666A (ja) * | 1998-08-03 | 2000-02-25 | Nippon Soken Inc | 角速度センサ及びその製造方法 |

| JP3796991B2 (ja) * | 1998-12-10 | 2006-07-12 | 株式会社デンソー | 角速度センサ |

| JP3119255B2 (ja) | 1998-12-22 | 2000-12-18 | 日本電気株式会社 | マイクロマシンスイッチおよびその製造方法 |

| JP2000292175A (ja) * | 1999-04-12 | 2000-10-20 | Denso Corp | 角速度センサおよびその製造方法 |

| DE60037928T2 (de) * | 1999-09-08 | 2009-01-22 | Alps Electric Co., Ltd. | Kreiselgerät und Eingabegerät dafür |

| JP3771100B2 (ja) | 2000-01-19 | 2006-04-26 | アルプス電気株式会社 | 静電容量検出型センサおよびジャイロスコープならびに入力装置 |

| JP2003028649A (ja) * | 2001-05-11 | 2003-01-29 | Murata Mfg Co Ltd | センサ回路モジュールおよびそれを用いた電子装置 |

| JP2003207338A (ja) * | 2002-01-15 | 2003-07-25 | Ngk Insulators Ltd | 振動型ジャイロスコープ用振動子および振動型ジャイロスコープ |

| JP3687619B2 (ja) * | 2002-03-25 | 2005-08-24 | 株式会社村田製作所 | 振動ジャイロおよびそれを用いた電子装置 |

| JP2004132792A (ja) * | 2002-10-09 | 2004-04-30 | Toyota Motor Corp | センサユニットの構造 |

| JP2004361115A (ja) * | 2003-06-02 | 2004-12-24 | Denso Corp | 半導体力学量センサ |

| JP4281451B2 (ja) * | 2003-07-17 | 2009-06-17 | 株式会社大真空 | 圧電振動片および圧電振動子 |

| JP4478495B2 (ja) * | 2004-03-31 | 2010-06-09 | ソニー株式会社 | 振動型ジャイロセンサ素子及びその製造方法 |

| EP1626283B1 (en) * | 2004-08-13 | 2011-03-23 | STMicroelectronics Srl | Micro-electromechanical structure, in particular accelerometer, with improved insensitivity to thermomechanical stresses |

| JP5037819B2 (ja) * | 2005-03-04 | 2012-10-03 | ソニー株式会社 | 電子機器 |

-

2005

- 2005-12-27 JP JP2005374324A patent/JP5135683B2/ja not_active Expired - Fee Related

-

2006

- 2006-02-27 EP EP20060003942 patent/EP1696206B1/en not_active Expired - Fee Related

- 2006-02-27 US US11/363,395 patent/US7723901B2/en not_active Expired - Fee Related

- 2006-02-28 KR KR20060019298A patent/KR20060095517A/ko not_active Application Discontinuation

- 2006-02-28 CN CN2006100747373A patent/CN1831478B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN1831478B (zh) | 2013-06-12 |

| CN1831478A (zh) | 2006-09-13 |

| US20060202591A1 (en) | 2006-09-14 |

| KR20060095517A (ko) | 2006-08-31 |

| JP2007024861A (ja) | 2007-02-01 |

| EP1696206A1 (en) | 2006-08-30 |

| US7723901B2 (en) | 2010-05-25 |

| EP1696206B1 (en) | 2011-10-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5135683B2 (ja) | 振動型ジャイロセンサ及び振動素子の製造方法 | |

| JP5037819B2 (ja) | 電子機器 | |

| CN1969168B (zh) | 振动型陀螺传感器 | |

| JP5107399B2 (ja) | 振動型ジャイロセンサ | |

| CN1828224B (zh) | 振动陀螺传感器和调节振动陀螺传感器的方法 | |

| JP2007258917A (ja) | 圧電デバイス | |

| JP4640459B2 (ja) | 角速度センサ | |

| US7126262B2 (en) | Piezoelectric vibration gyro element, method for manufacturing the same, and piezoelectric vibration gyro sensor | |

| JP7528566B2 (ja) | 振動素子の製造方法、振動素子および振動デバイス | |

| JP2006250583A (ja) | 振動型ジャイロセンサ | |

| JP5146578B2 (ja) | 振動型ジャイロセンサ | |

| JP2006242590A (ja) | 振動型ジャイロセンサ | |

| JP2009065521A (ja) | 圧電デバイスの製造方法および圧電振動板 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20071028 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081225 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20081225 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110531 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110607 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110808 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120313 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120514 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120626 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120921 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20120928 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121016 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121029 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5135683 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151122 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |