JP5043333B2 - 親水性Si表面と界面接合酸化物の溶解とを用いるSi間擬似疎水性ウェハ接合 - Google Patents

親水性Si表面と界面接合酸化物の溶解とを用いるSi間擬似疎水性ウェハ接合 Download PDFInfo

- Publication number

- JP5043333B2 JP5043333B2 JP2005363874A JP2005363874A JP5043333B2 JP 5043333 B2 JP5043333 B2 JP 5043333B2 JP 2005363874 A JP2005363874 A JP 2005363874A JP 2005363874 A JP2005363874 A JP 2005363874A JP 5043333 B2 JP5043333 B2 JP 5043333B2

- Authority

- JP

- Japan

- Prior art keywords

- oxide

- annealing

- layer

- bonding

- wafer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000004090 dissolution Methods 0.000 title description 33

- 238000000034 method Methods 0.000 claims description 72

- 235000012431 wafers Nutrition 0.000 claims description 70

- 238000000137 annealing Methods 0.000 claims description 56

- 229910052710 silicon Inorganic materials 0.000 claims description 34

- 239000010703 silicon Substances 0.000 claims description 33

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 32

- 230000001681 protective effect Effects 0.000 claims description 25

- 239000004065 semiconductor Substances 0.000 claims description 20

- 239000013078 crystal Substances 0.000 claims description 17

- 229910052760 oxygen Inorganic materials 0.000 claims description 17

- 239000007789 gas Substances 0.000 claims description 16

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 11

- 239000001301 oxygen Substances 0.000 claims description 11

- 230000001590 oxidative effect Effects 0.000 claims description 9

- 238000000151 deposition Methods 0.000 claims description 7

- 238000005304 joining Methods 0.000 claims description 7

- 239000000203 mixture Substances 0.000 claims description 5

- 238000004381 surface treatment Methods 0.000 claims description 5

- 238000004140 cleaning Methods 0.000 claims description 4

- 238000004519 manufacturing process Methods 0.000 claims description 4

- 229910008045 Si-Si Inorganic materials 0.000 claims description 3

- 229910006411 Si—Si Inorganic materials 0.000 claims description 3

- 229910052786 argon Inorganic materials 0.000 claims description 2

- 229910052736 halogen Inorganic materials 0.000 claims description 2

- 150000002367 halogens Chemical class 0.000 claims description 2

- 229910052734 helium Inorganic materials 0.000 claims description 2

- 229910052743 krypton Inorganic materials 0.000 claims description 2

- 229910052754 neon Inorganic materials 0.000 claims description 2

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 claims 3

- QPJSUIGXIBEQAC-UHFFFAOYSA-N n-(2,4-dichloro-5-propan-2-yloxyphenyl)acetamide Chemical compound CC(C)OC1=CC(NC(C)=O)=C(Cl)C=C1Cl QPJSUIGXIBEQAC-UHFFFAOYSA-N 0.000 claims 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 27

- 230000008569 process Effects 0.000 description 27

- 239000000758 substrate Substances 0.000 description 26

- 239000000463 material Substances 0.000 description 22

- 230000002209 hydrophobic effect Effects 0.000 description 12

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 11

- 230000015572 biosynthetic process Effects 0.000 description 7

- 230000008021 deposition Effects 0.000 description 6

- 230000003647 oxidation Effects 0.000 description 5

- 238000007254 oxidation reaction Methods 0.000 description 5

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 4

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- 230000005540 biological transmission Effects 0.000 description 4

- 238000006243 chemical reaction Methods 0.000 description 4

- 238000005530 etching Methods 0.000 description 4

- 238000009832 plasma treatment Methods 0.000 description 4

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 4

- 229910052814 silicon oxide Inorganic materials 0.000 description 4

- 239000000126 substance Substances 0.000 description 4

- WGTYBPLFGIVFAS-UHFFFAOYSA-M tetramethylammonium hydroxide Chemical compound [OH-].C[N+](C)(C)C WGTYBPLFGIVFAS-UHFFFAOYSA-M 0.000 description 4

- 238000011282 treatment Methods 0.000 description 4

- LYCAIKOWRPUZTN-UHFFFAOYSA-N Ethylene glycol Chemical compound OCCO LYCAIKOWRPUZTN-UHFFFAOYSA-N 0.000 description 3

- 238000003795 desorption Methods 0.000 description 3

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 2

- 238000003917 TEM image Methods 0.000 description 2

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 229910052799 carbon Inorganic materials 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 238000002310 reflectometry Methods 0.000 description 2

- 229910003811 SiGeC Inorganic materials 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 238000005280 amorphization Methods 0.000 description 1

- 229910052787 antimony Inorganic materials 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 229910052801 chlorine Inorganic materials 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 238000011982 device technology Methods 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 238000005553 drilling Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 230000004807 localization Effects 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 230000010355 oscillation Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 229920001296 polysiloxane Polymers 0.000 description 1

- 238000001953 recrystallisation Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000001179 sorption measurement Methods 0.000 description 1

- 229910052717 sulfur Inorganic materials 0.000 description 1

- 238000010301 surface-oxidation reaction Methods 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/185—Joining of semiconductor bodies for junction formation

- H01L21/187—Joining of semiconductor bodies for junction formation by direct bonding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76251—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Element Separation (AREA)

- Crystals, And After-Treatments Of Crystals (AREA)

Description

接合されることになるSi表面を有するハンドル・ウェハを選択するステップと、

接合されることになるSi表面を有し、好ましくは、ドナー・ウェハ表面から所定の深さの切断面又はエッチング停止領域を含むドナー・ウェハを選択するステップと、

2つのウェハの接合面に当該技術分野に周知の洗浄及び表面処理を施し、いずれの接合面上にも約3nmから5nmまでより多い酸化物をもたらすことなく、該接合面を親水性のままにするステップと、

当該技術分野に周知の方法によってウェハを接合するステップと、

ドナー・ウェハの望ましくない部分を除去し、移送されたドナー・ウェハを残すステップと、

必要に応じて移送されたドナー・ウェハ層上に表面処理を行い、所定の表面仕上げ及び厚さを有する接合されたドナー・ウェハを残すステップと、

本発明の新規な酸化物溶解プロセスを実行し、接合面に残っている界面材料を除去するステップと、

を含む。

250℃−950℃、5℃/分、Ar+1.2%O2、

950℃−1200℃、3℃/分、Ar+0.13%O2、

1200℃−1325℃、1℃/分、Ar+0.063%O2、

1325℃/5時間、Ar+0.063%O2、

1325℃−1200℃、−3℃/分、Ar+0%O2、

1200℃−400℃、−5℃/分、N2、

を含むアニールが施された。

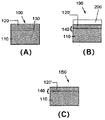

112、320:ハンドル・ウェハ

114、186:ドナー・ウェハ

300、340:基板構造体

182、330:界面酸化物層

Claims (15)

- 半導体構造体を製造する方法であって、

2つのシリコン表面の各々に存在する3nmから5nmまでの厚さより薄い酸化物層を介して当該2つのシリコン表面を接合することにより接合構造体を形成するステップと、

250℃から1325℃までの温度範囲においてO 2 が0.02%から2%の濃度範囲で存在する雰囲気内で、前記2つのシリコン表面の各々に存在する前記酸化物層を含む前記接合構造体をアニールするステップを含み、

前記アニールするステップにより前記接合構造体から前記酸化物層が完全に除去され、前記2つのシリコン表面が互いに直接接合されることを特徴とする方法。 - 前記2つのシリコン表面が、第1の単結晶表面配向を有する第1のシリコン表面と、第2の単結晶表面配向を有する第2のシリコン表面とを含み、前記第2の単結晶表面配向が、前記第1の単結晶表面配向と異なる、請求項1に記載の方法。

- 前記アニールするステップが、0.1時間から24時間までの時間、前記温度範囲で行われる、請求項1に記載の方法。

- 酸化物のないSi間界面が存在する、接合されたSiオンSiウェハ対を形成する方法であって、

接合されることになる第1のSi表面を有するハンドル・ウェハを選択するステップと、

接合されることになる第2のSi表面を有するドナー・ウェハを選択するステップと、

前記2つのウェハの接合面に洗浄及び表面処理を施して、いずれの接合面上にも3nmから5nmまでより多い酸化物をもたらすことなく、親水性接合のための表面を形成するステップと、

前記ウェハを接合するステップと、

前記ドナー・ウェハの望ましくない部分を除去し、転写されたドナー・ウェハを残すステップと、

250℃から1325℃までの温度範囲においてO 2 が0.02%から2%の濃度範囲で存在する雰囲気内で、前記第1のSi表面と前記第2のSi表面とに形成された酸化物層を含む接合されたウェハ対をアニールするステップと、を含み、

前記アニールするステップにより前記ウェハ対から前記酸化物層が完全に除去され、前記第1のSi表面と前記第2のSi表面とが互いに直接接合されることを特徴とする方法。 - 前記ドナー・ウェハは、前記Si表面から所定の深さの切断面又はエッチング停止領域を含む、請求項4に記載の方法。

- 前記残すステップと前記アニールするステップとの間に、所定の表面仕上げと厚さを有する前記接合されたドナー・ウェハを残すように表面処理を施すステップをさらに含む、請求項4に記載の方法。

- 前記第1のSi表面が第1の単結晶表面配向を有し、前記第2のSi表面が第2の単結晶表面配向を有し、前記第2の単結晶表面配向が、前記第1の単結晶表面配向と異なる、請求項4に記載の方法。

- 前記第1及び第2の単結晶表面配向が、(100)、(110)、又は(111)表面配向を含む、請求項2または7に記載の方法。

- 前記酸化物がシリコン及び酸素を含む、請求項1または4に記載の方法。

- 前記アニールするステップが、0.5時間から24時間までの時間、前記温度範囲で行われる、請求項4に記載の方法。

- 前記アニールするステップが、Ar、He、Kr、Ne、Xe、N2 、H2、H含有ガス、C含有ガス、F含有ガス、Cl含有ガス、Si含有ガス、ハロゲン含有ガス、及びこれらの混合物からなる群から選択される少なくとも1つのガスを含む前記雰囲気において行われる、請求項1または4に記載の方法。

- 前記雰囲気が酸化性である、請求項11に記載の方法。

- 前記アニールするステップの前に処分可能な保護キャップ層を堆積させるステップと、該アニールするステップ後に前記処分可能な保護キャップ層を除去するステップとをさらに含む、請求項1または4に記載の方法。

- 前記アニールするステップ中に生成される何らかの表面酸化物層を除去するステップをさらに含む、請求項1または4に記載の方法。

- 前記除去するステップが、フッ化水素酸(HF)を含有する湿式エッチングを含む、請求項14に記載の方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/031,165 | 2005-01-07 | ||

| US11/031,165 US8138061B2 (en) | 2005-01-07 | 2005-01-07 | Quasi-hydrophobic Si-Si wafer bonding using hydrophilic Si surfaces and dissolution of interfacial bonding oxide |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006191029A JP2006191029A (ja) | 2006-07-20 |

| JP2006191029A5 JP2006191029A5 (ja) | 2008-11-13 |

| JP5043333B2 true JP5043333B2 (ja) | 2012-10-10 |

Family

ID=36653805

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005363874A Expired - Fee Related JP5043333B2 (ja) | 2005-01-07 | 2005-12-16 | 親水性Si表面と界面接合酸化物の溶解とを用いるSi間擬似疎水性ウェハ接合 |

Country Status (4)

| Country | Link |

|---|---|

| US (3) | US8138061B2 (ja) |

| JP (1) | JP5043333B2 (ja) |

| CN (1) | CN1818154A (ja) |

| TW (1) | TW200632992A (ja) |

Families Citing this family (51)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP1719179B1 (en) * | 2004-02-25 | 2018-10-03 | Sony Semiconductor Solutions Corporation | Photodetecting device |

| US8138061B2 (en) | 2005-01-07 | 2012-03-20 | International Business Machines Corporation | Quasi-hydrophobic Si-Si wafer bonding using hydrophilic Si surfaces and dissolution of interfacial bonding oxide |

| US7285473B2 (en) * | 2005-01-07 | 2007-10-23 | International Business Machines Corporation | Method for fabricating low-defect-density changed orientation Si |

| US7670928B2 (en) * | 2006-06-14 | 2010-03-02 | Intel Corporation | Ultra-thin oxide bonding for S1 to S1 dual orientation bonding |

| JP2008060355A (ja) * | 2006-08-31 | 2008-03-13 | Sumco Corp | 貼り合わせウェーハの製造方法および貼り合わせウェーハ |

| FR2910177B1 (fr) * | 2006-12-18 | 2009-04-03 | Soitec Silicon On Insulator | Couche tres fine enterree |

| SG144092A1 (en) * | 2006-12-26 | 2008-07-29 | Sumco Corp | Method of manufacturing bonded wafer |

| JP5368996B2 (ja) * | 2006-12-26 | 2013-12-18 | ソイテック | 半導体オンインシュレータ構造体を製造する方法 |

| WO2008078133A1 (en) * | 2006-12-26 | 2008-07-03 | S.O.I.Tec Silicon On Insulator Technologies | Method for producing a semiconductor-on-insulator structure |

| JP5009124B2 (ja) * | 2007-01-04 | 2012-08-22 | コバレントマテリアル株式会社 | 半導体基板の製造方法 |

| JP5038723B2 (ja) * | 2007-01-04 | 2012-10-03 | コバレントマテリアル株式会社 | 半導体基板およびその製造方法 |

| FR2911430B1 (fr) * | 2007-01-15 | 2009-04-17 | Soitec Silicon On Insulator | "procede de fabrication d'un substrat hybride" |

| EP2109883A1 (en) | 2007-02-08 | 2009-10-21 | S.O.I.T.E.C. Silicon on Insulator Technologies | Method of fabrication of highly heat dissipative substrates |

| JP5256625B2 (ja) * | 2007-03-05 | 2013-08-07 | 株式会社Sumco | 貼り合わせウェーハの評価方法 |

| JP5433927B2 (ja) * | 2007-03-14 | 2014-03-05 | 株式会社Sumco | 貼り合わせウェーハの製造方法 |

| WO2008114099A1 (en) | 2007-03-19 | 2008-09-25 | S.O.I.Tec Silicon On Insulator Technologies | Patterned thin soi |

| FR2918792B1 (fr) * | 2007-07-10 | 2010-04-23 | Soitec Silicon On Insulator | Procede de traitement de defauts d'interface dans un substrat. |

| JP2011504655A (ja) * | 2007-11-23 | 2011-02-10 | エス. オー. アイ. テック シリコン オン インシュレーター テクノロジーズ | 精密な酸化物の溶解 |

| EP2065921A1 (en) * | 2007-11-29 | 2009-06-03 | S.O.I.T.E.C. Silicon on Insulator Technologies | Method for fabricating a semiconductor substrate with areas with different crystal orienation |

| US7858495B2 (en) * | 2008-02-04 | 2010-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing SOI substrate |

| WO2009104060A1 (en) * | 2008-02-20 | 2009-08-27 | S.O.I.Tec Silicon On Insulator Technologies | Oxidation after oxide dissolution |

| WO2009128776A1 (en) * | 2008-04-15 | 2009-10-22 | Vallin Oerjan | Hybrid wafers with hybrid-oriented layer |

| FR2933234B1 (fr) * | 2008-06-30 | 2016-09-23 | S O I Tec Silicon On Insulator Tech | Substrat bon marche a structure double et procede de fabrication associe |

| FR2933235B1 (fr) * | 2008-06-30 | 2010-11-26 | Soitec Silicon On Insulator | Substrat bon marche et procede de fabrication associe |

| FR2933233B1 (fr) * | 2008-06-30 | 2010-11-26 | Soitec Silicon On Insulator | Substrat de haute resistivite bon marche et procede de fabrication associe |

| US20100178750A1 (en) * | 2008-07-17 | 2010-07-15 | Sumco Corporation | Method for producing bonded wafer |

| JP2010072209A (ja) * | 2008-09-17 | 2010-04-02 | Fuji Xerox Co Ltd | 静電荷像現像用トナー、静電荷像現像用トナーの製造方法、静電荷像現像用現像剤および画像形成装置 |

| FR2936356B1 (fr) * | 2008-09-23 | 2010-10-22 | Soitec Silicon On Insulator | Procede de dissolution locale de la couche d'oxyde dans une structure de type semi-conducteur sur isolant |

| FR2938120B1 (fr) * | 2008-10-31 | 2011-04-08 | Commissariat Energie Atomique | Procede de formation d'une couche monocristalline dans le domaine micro-electronique |

| JP5493345B2 (ja) * | 2008-12-11 | 2014-05-14 | 信越半導体株式会社 | Soiウェーハの製造方法 |

| FR2941324B1 (fr) * | 2009-01-22 | 2011-04-29 | Soitec Silicon On Insulator | Procede de dissolution de la couche d'oxyde dans la couronne d'une structure de type semi-conducteur sur isolant. |

| US7927975B2 (en) | 2009-02-04 | 2011-04-19 | Micron Technology, Inc. | Semiconductor material manufacture |

| FR2964495A1 (fr) * | 2010-09-02 | 2012-03-09 | Soitec Silicon On Insulator | Procede de fabrication d'une structure seoi multiple comportant une couche isolante ultrafine |

| FR2968450A1 (fr) * | 2010-12-07 | 2012-06-08 | Soitec Silicon On Insulator | Procede de traitement d'une structure de type semi-conducteur sur isolant |

| KR101810310B1 (ko) * | 2011-01-25 | 2017-12-18 | 에베 그룹 에. 탈너 게엠베하 | 웨이퍼들의 영구적 결합을 위한 방법 |

| FR2972564B1 (fr) | 2011-03-08 | 2016-11-04 | S O I Tec Silicon On Insulator Tech | Procédé de traitement d'une structure de type semi-conducteur sur isolant |

| US9312133B2 (en) | 2011-08-25 | 2016-04-12 | Aeroflex Colorado Springs Inc. | Wafer structure for electronic integrated circuit manufacturing |

| US9378955B2 (en) | 2011-08-25 | 2016-06-28 | Aeroflex Colorado Springs Inc. | Wafer structure for electronic integrated circuit manufacturing |

| US20130049175A1 (en) * | 2011-08-25 | 2013-02-28 | Aeroflex Colorado Springs Inc. | Wafer structure for electronic integrated circuit manufacturing |

| US9378956B2 (en) | 2011-08-25 | 2016-06-28 | Aeroflex Colorado Springs Inc. | Wafer structure for electronic integrated circuit manufacturing |

| US9396947B2 (en) | 2011-08-25 | 2016-07-19 | Aeroflex Colorado Springs Inc. | Wafer structure for electronic integrated circuit manufacturing |

| US20130049178A1 (en) * | 2011-08-25 | 2013-02-28 | Aeroflex Colorado Springs Inc. | Wafer structure for electronic integrated circuit manufacturing |

| US9589801B2 (en) | 2011-10-31 | 2017-03-07 | Arizona Board Of Regents, A Body Corporated Of The State Of Arizona, Acting For And On Behalf Of Arizona State University | Methods for wafer bonding and for nucleating bonding nanophases using wet and steam pressurization |

| CN102586886A (zh) * | 2012-03-10 | 2012-07-18 | 天津市环欧半导体材料技术有限公司 | 一种用于去除硅晶片表面氧沉积物的硅晶片退火方法 |

| US9418963B2 (en) | 2012-09-25 | 2016-08-16 | Arizona Board Of Regents, A Body Corporate Of The State Of Arizona Acting For And On Behalf Of Arizona State University | Methods for wafer bonding, and for nucleating bonding nanophases |

| FR3007891B1 (fr) * | 2013-06-28 | 2016-11-25 | Soitec Silicon On Insulator | Procede de fabrication d'une structure composite |

| JP6061251B2 (ja) * | 2013-07-05 | 2017-01-18 | 株式会社豊田自動織機 | 半導体基板の製造方法 |

| US9601368B2 (en) * | 2015-07-16 | 2017-03-21 | Infineon Technologies Ag | Semiconductor device comprising an oxygen diffusion barrier and manufacturing method |

| US9741685B2 (en) * | 2015-08-07 | 2017-08-22 | Lam Research Corporation | Methods for directly bonding silicon to silicon or silicon carbide to silicon carbide |

| FR3057705B1 (fr) * | 2016-10-13 | 2019-04-12 | Soitec | Procede de dissolution d'un oxyde enterre dans une plaquette de silicium sur isolant |

| EP3586356B1 (de) * | 2017-02-21 | 2023-11-08 | EV Group E. Thallner GmbH | Verfahren zum bonden von substraten |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3175323B2 (ja) * | 1991-08-26 | 2001-06-11 | 株式会社デンソー | 半導体基板の製造方法 |

| JP2820120B2 (ja) * | 1996-06-03 | 1998-11-05 | 日本電気株式会社 | 半導体基板の製造方法 |

| JP4273540B2 (ja) * | 1998-07-21 | 2009-06-03 | 株式会社Sumco | 貼り合わせ半導体基板及びその製造方法 |

| JP2004031715A (ja) * | 2002-06-27 | 2004-01-29 | Shin Etsu Handotai Co Ltd | Soiウエーハの製造方法及びsoiウエーハ |

| US7153757B2 (en) | 2002-08-29 | 2006-12-26 | Analog Devices, Inc. | Method for direct bonding two silicon wafers for minimising interfacial oxide and stresses at the bond interface, and an SOI structure |

| US7329923B2 (en) | 2003-06-17 | 2008-02-12 | International Business Machines Corporation | High-performance CMOS devices on hybrid crystal oriented substrates |

| US7023055B2 (en) | 2003-10-29 | 2006-04-04 | International Business Machines Corporation | CMOS on hybrid substrate with different crystal orientations using silicon-to-silicon direct wafer bonding |

| US20050116290A1 (en) | 2003-12-02 | 2005-06-02 | De Souza Joel P. | Planar substrate with selected semiconductor crystal orientations formed by localized amorphization and recrystallization of stacked template layers |

| US7285473B2 (en) | 2005-01-07 | 2007-10-23 | International Business Machines Corporation | Method for fabricating low-defect-density changed orientation Si |

| US8138061B2 (en) | 2005-01-07 | 2012-03-20 | International Business Machines Corporation | Quasi-hydrophobic Si-Si wafer bonding using hydrophilic Si surfaces and dissolution of interfacial bonding oxide |

-

2005

- 2005-01-07 US US11/031,165 patent/US8138061B2/en not_active Expired - Fee Related

- 2005-12-16 JP JP2005363874A patent/JP5043333B2/ja not_active Expired - Fee Related

-

2006

- 2006-01-04 TW TW095100286A patent/TW200632992A/zh unknown

- 2006-01-05 CN CNA2006100004455A patent/CN1818154A/zh active Pending

-

2009

- 2009-08-08 US US12/538,115 patent/US8053330B2/en not_active Expired - Fee Related

-

2012

- 2012-02-27 US US13/405,760 patent/US20120156861A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| CN1818154A (zh) | 2006-08-16 |

| US20120156861A1 (en) | 2012-06-21 |

| US20090298258A1 (en) | 2009-12-03 |

| JP2006191029A (ja) | 2006-07-20 |

| TW200632992A (en) | 2006-09-16 |

| US20060154442A1 (en) | 2006-07-13 |

| US8053330B2 (en) | 2011-11-08 |

| US8138061B2 (en) | 2012-03-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5043333B2 (ja) | 親水性Si表面と界面接合酸化物の溶解とを用いるSi間擬似疎水性ウェハ接合 | |

| US7087965B2 (en) | Strained silicon CMOS on hybrid crystal orientations | |

| JP4959690B2 (ja) | ハイブリッド配向基板のための改善されたアモルファス化/テンプレート再結晶化の方法 | |

| TWI297171B (en) | Method for fabricating a germanium on insulator (geoi) type wafer | |

| US7060585B1 (en) | Hybrid orientation substrates by in-place bonding and amorphization/templated recrystallization | |

| EP2333824B1 (en) | Manufacture of thin SOI devices | |

| US20040137698A1 (en) | Fabrication system and method for monocrystaline semiconductor on a substrate | |

| US20050275024A1 (en) | SOI chip with recess-resistant buried insulator and method of manufacturing the same | |

| US9779982B2 (en) | Fabrication method of a stack of electronic devices | |

| JP2008547219A (ja) | 転位の無い歪んだ結晶を作成するための方法 | |

| US20070017438A1 (en) | Method of forming dislocation-free strained thin films | |

| TWI711118B (zh) | 用於製作應變式絕緣體上半導體底材之方法 | |

| US20180130656A1 (en) | FORMING DEFECT-FREE RELAXED SiGe FINS | |

| JP4328708B2 (ja) | Cmosデバイスの製造方法及びcmosデバイスを備える構造 | |

| EP1597758A1 (en) | Relaxation of a thin layer after its transfer | |

| JP2003078118A (ja) | 半導体部材の製造方法及び半導体装置の製造方法 | |

| JP2008130726A (ja) | 半導体装置の製造方法 | |

| JP2005191458A (ja) | 半導体部材とその製造方法、及び半導体装置 | |

| JP2008244106A (ja) | 半導体装置の製造方法 | |

| FR2987936A1 (fr) | Procedes de fabrication de fines couches de materiau semi-conducteur cristallin, et structures et dispositifs connexes |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080930 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080930 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090206 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120308 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120313 |

|

| RD12 | Notification of acceptance of power of sub attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7432 Effective date: 20120404 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20120404 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120605 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120626 |

|

| RD14 | Notification of resignation of power of sub attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7434 Effective date: 20120626 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120712 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150720 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |