JP4853028B2 - アクティブマトリクス表示装置、およびそのタイミング制御用半導体装置 - Google Patents

アクティブマトリクス表示装置、およびそのタイミング制御用半導体装置 Download PDFInfo

- Publication number

- JP4853028B2 JP4853028B2 JP2006009709A JP2006009709A JP4853028B2 JP 4853028 B2 JP4853028 B2 JP 4853028B2 JP 2006009709 A JP2006009709 A JP 2006009709A JP 2006009709 A JP2006009709 A JP 2006009709A JP 4853028 B2 JP4853028 B2 JP 4853028B2

- Authority

- JP

- Japan

- Prior art keywords

- period

- signal

- image signal

- signal line

- vertical blanking

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000011159 matrix material Substances 0.000 title claims description 18

- 239000004065 semiconductor Substances 0.000 title claims description 8

- 230000005764 inhibitory process Effects 0.000 claims description 3

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 40

- 239000004973 liquid crystal related substance Substances 0.000 description 27

- 230000000630 rising effect Effects 0.000 description 14

- 238000010586 diagram Methods 0.000 description 13

- 230000007257 malfunction Effects 0.000 description 8

- 238000000034 method Methods 0.000 description 6

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 5

- 229910052710 silicon Inorganic materials 0.000 description 5

- 239000010703 silicon Substances 0.000 description 5

- 230000003111 delayed effect Effects 0.000 description 4

- 238000006243 chemical reaction Methods 0.000 description 3

- 230000002159 abnormal effect Effects 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- 239000000758 substrate Substances 0.000 description 2

- 230000001360 synchronised effect Effects 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000010348 incorporation Methods 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G5/00—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators

- G09G5/36—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators characterised by the display of a graphic pattern, e.g. using an all-points-addressable [APA] memory

- G09G5/39—Control of the bit-mapped memory

- G09G5/395—Arrangements specially adapted for transferring the contents of the bit-mapped memory to the screen

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/06—Details of flat display driving waveforms

- G09G2310/061—Details of flat display driving waveforms for resetting or blanking

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/08—Details of timing specific for flat panels, other than clock recovery

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal Display Device Control (AREA)

- Liquid Crystal (AREA)

Description

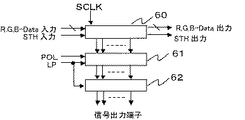

図1は,本実施の形態における液晶表示装置1の回路構成を示しており、前記アクティブマトリクス表示デバイスの一例として液晶パネル2を駆動するための周辺回路の構成を示したブロック図である.同図において液晶表示装置1は、液晶パネル2、画像信号線駆動手段であるソースドライバIC(6〜13)、走査信号線駆動手段であるゲートドライバIC(3〜5)およびタイミング制御回路18、(以後タイミング制御回路をTCONと称す)から構成されている。

本実施の形態における液晶表示装置の構成は前述の実施の形態1における図1の構成と同様であり、詳しい説明は省略し異なる部分について主に説明する。タイミング制御回路(TCON)18の構成を図9に示す。本実施の形態におけるTCON18の入出力信号は前述の実施の形態1と同一であり、ここでは詳細な説明を省略する。図9において符号84はソースドライバ制御信号生成回路であり、前述の実施の形態1におけるソースドライバ制御信号生成回路34に相当し、その内部構成は異なるが同様の機能を奏する。

2 液晶パネル

3、4、5 ゲートドライバIC

6、7、8、9、10、11、12、13 ソースドライバIC

14 画像信号線

15 走査信号線

16 画素部

18 タイミング制御回路

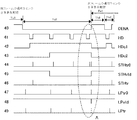

23 POL出力波形

24、50、100 STH出力波形

25、51、101 LP出力波形

30、35 AND回路

31 スタートパルス生成回路

32、33 マスク信号生成回路

34 ラッチパルス生成回路

36、84 ソースドライバ制御信号生成回路

44、94 水平スタートパルストリガ源信号波形

45、95 水平スタートパルストリガ有効信号波形

46、96 水平スタートパルストリガ信号波形

47、97 ラッチパルストリガ源信号波形

48、98 ラッチパルストリガ有効信号波形

49、99 ラッチパルストリガ信号波形

80 ブランキングカウンタ

81 記憶回路

82、83 比較回路

M 第一の時点

N 第二の時点

Tv1 垂直走査期間

Tv2 垂直ブランキング期間

Th 水平周期

RGB−Data 画像表示データ

Claims (5)

- マトリクス状に配置された複数の画素と、該画素の各列に配置された複数の画像信号線と、前記画素の各行に配置された複数の走査信号線と、該走査信号線を駆動する走査信号線駆動手段と、前記画像信号線に前記画素を駆動するための画像信号を供給する画像信号線駆動手段と、前記走査信号線駆動手段と前記画像信号線駆動手段とを駆動制御するタイミング制御回路と、を具備するアクティブマトリクス表示装置であって、

前記タイミング制御回路は、該タイミング制御回路から前記画像信号線駆動手段に出力される画像表示制御信号が、前記画素の表示輝度に対応する画像表示データと、該画像表示データの入出力タイミングを制御する駆動制御信号とに分別され、垂直ブランキング期間中においても所定の周期で前記駆動制御信号を前記画像信号線駆動手段に出力するよう構成され、

前記タイミング制御回路は、前記垂直ブランキング期間内の少なくとも後半の第一の期間に対応して前記画像信号線駆動手段に対して、前記画像表示データの読み込みを休止するよう前記駆動制御信号を出力し、

前記タイミング制御回路は、前記第一の期間中の所定の第一の時点と、前記垂直ブランキング期間が終了した後の最初の水平表示期間に対応する前記画像表示データの読み込み開始時点を第二の時点とし、前記第一の時点と前記第二の時点期間は、前記画像信号線駆動手段の前記画像信号の更新を停止するよう前記駆動制御信号を前記画像信号線駆動手段に出力し、

前記第一の時点と前記第二の時点期間は、垂直走査期間中の一水平周期より短いことを特徴とするアクティブマトリクス表示装置。 - 前記タイミング制御回路は、前記第一の期間に対応して前記画像信号線駆動手段への水平スタートパルスを消去することを特徴とする請求項1に記載のアクティブマトリクス表示装置。

- 前記タイミング制御回路は、前記画像信号線駆動手段へのラッチパルスを消去することにより、前記第一の時点と前記第二の時点期間は、前記画像信号線駆動手段の前記画像信号の更新を停止するよう制御することを特徴とする請求項1または2に記載のアクティブマトリクス表示装置。

- 前記タイミング制御回路は、前記第一の時点と前記第二の時点期間が、前記画像信号線駆動手段の構成に基づいて予め定められたラッチパルスの入力禁止期間を包含するよう前記画像信号線駆動手段を制御することを特徴とする請求項1乃至3のいずれか一項に記載のアクティブマトリクス表示装置。

- 請求項1乃至4のいずれか一項に記載の前記タイミング制御回路を内蔵したアクティブマトリクス表示装置のタイミング制御用半導体装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006009709A JP4853028B2 (ja) | 2006-01-18 | 2006-01-18 | アクティブマトリクス表示装置、およびそのタイミング制御用半導体装置 |

| TW096101228A TW200737112A (en) | 2006-01-18 | 2007-01-12 | Active matrix display device and semiconductor device for controlling its timing |

| KR1020070004107A KR100832513B1 (ko) | 2006-01-18 | 2007-01-15 | 액티브 매트릭스 표시장치 및 그것의 타이밍 제어용반도체장치 |

| US11/623,990 US7773083B2 (en) | 2006-01-18 | 2007-01-17 | Active matrix display device and semiconductor device for timing control thereof |

| CNB2007100020467A CN100504525C (zh) | 2006-01-18 | 2007-01-18 | 有源矩阵显示装置及其定时控制用半导体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006009709A JP4853028B2 (ja) | 2006-01-18 | 2006-01-18 | アクティブマトリクス表示装置、およびそのタイミング制御用半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007192982A JP2007192982A (ja) | 2007-08-02 |

| JP2007192982A5 JP2007192982A5 (ja) | 2008-12-25 |

| JP4853028B2 true JP4853028B2 (ja) | 2012-01-11 |

Family

ID=38262800

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006009709A Active JP4853028B2 (ja) | 2006-01-18 | 2006-01-18 | アクティブマトリクス表示装置、およびそのタイミング制御用半導体装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7773083B2 (ja) |

| JP (1) | JP4853028B2 (ja) |

| KR (1) | KR100832513B1 (ja) |

| CN (1) | CN100504525C (ja) |

| TW (1) | TW200737112A (ja) |

Families Citing this family (29)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101329706B1 (ko) * | 2007-10-10 | 2013-11-14 | 엘지디스플레이 주식회사 | 액정표시장치 및 이의 구동방법 |

| JP5576587B2 (ja) * | 2007-10-12 | 2014-08-20 | 船井電機株式会社 | 液晶表示装置 |

| KR101508542B1 (ko) * | 2007-11-21 | 2015-04-03 | 엘지디스플레이 주식회사 | 액정표시장치의 제어신호 전송회로 및 그 제어신호의전송방법 |

| JP5268389B2 (ja) * | 2008-02-28 | 2013-08-21 | キヤノン株式会社 | 固体撮像装置、その駆動方法及び撮像システム |

| TWI413071B (zh) | 2008-06-11 | 2013-10-21 | Novatek Microelectronics Corp | 用於液晶顯示器降低消耗功率之驅動方法及相關裝置 |

| CN103680440B (zh) * | 2008-06-23 | 2017-02-01 | 联咏科技股份有限公司 | 用于液晶显示器降低消耗功率的驱动方法及相关装置 |

| JP5522375B2 (ja) | 2009-03-11 | 2014-06-18 | Nltテクノロジー株式会社 | 液晶表示装置、該装置に用いられるタイミングコントローラ及び信号処理方法 |

| CN102034444B (zh) * | 2009-09-30 | 2013-01-23 | 北京京东方光电科技有限公司 | 液晶显示器源驱动方法及驱动装置 |

| KR101688599B1 (ko) * | 2010-06-01 | 2016-12-23 | 삼성전자 주식회사 | 모드전환방법, 상기 모드전환방법이 적용되는 디스플레이구동ic 및 영상신호처리시스템 |

| JP5251926B2 (ja) * | 2010-06-16 | 2013-07-31 | セイコーエプソン株式会社 | 撮影装置およびタイミング制御回路 |

| JP5617542B2 (ja) | 2010-11-04 | 2014-11-05 | 三菱電機株式会社 | マトリクス表示装置、およびマトリクス表示装置の駆動方法 |

| JP2012191304A (ja) * | 2011-03-09 | 2012-10-04 | Jvc Kenwood Corp | 同期信号処理装置及び同期信号処理方法 |

| KR20120133432A (ko) * | 2011-05-31 | 2012-12-11 | 삼성디스플레이 주식회사 | 유기전계발광 표시장치 및 그의 구동방법 |

| CN102855838B (zh) * | 2011-06-30 | 2015-07-08 | 上海天马微电子有限公司 | 用于显示器的时序控制器 |

| KR101872430B1 (ko) | 2011-08-25 | 2018-07-31 | 엘지디스플레이 주식회사 | 액정표시장치 및 그 구동 방법 |

| KR102005872B1 (ko) * | 2011-10-26 | 2019-08-01 | 삼성디스플레이 주식회사 | 표시 장치 및 그 구동 방법 |

| KR102050432B1 (ko) * | 2011-11-17 | 2020-01-09 | 엘지디스플레이 주식회사 | 액정 표시장치 및 그 구동방법 |

| CN102708817B (zh) * | 2012-04-10 | 2014-09-10 | 京东方科技集团股份有限公司 | 一种显示装置的驱动方法及显示装置 |

| CN102708834B (zh) * | 2012-06-28 | 2015-03-25 | 天马微电子股份有限公司 | 液晶显示器源驱动方法、源驱动装置及液晶显示面板 |

| JP5961125B2 (ja) | 2013-02-26 | 2016-08-02 | 株式会社ジャパンディスプレイ | 表示装置及び電子機器 |

| JP6462207B2 (ja) * | 2013-11-21 | 2019-01-30 | ラピスセミコンダクタ株式会社 | 表示デバイスの駆動装置 |

| KR102211692B1 (ko) * | 2014-09-03 | 2021-02-04 | 삼성디스플레이 주식회사 | 유기 발광 다이오드 표시 장치 |

| CN108463918B (zh) * | 2015-10-30 | 2021-09-03 | 株式会社东芝 | 电池控制装置以及电池系统 |

| TWI581245B (zh) * | 2016-07-06 | 2017-05-01 | 奇景光電股份有限公司 | 液晶顯示器的極性反轉驅動方法及源極驅動器 |

| CN109036299B (zh) * | 2017-06-09 | 2022-01-04 | 京东方科技集团股份有限公司 | 数据传输方法、装置、系统和存储介质 |

| CN111653236B (zh) * | 2020-06-16 | 2021-09-17 | 厦门天马微电子有限公司 | 一种显示装置 |

| CN112951150B (zh) * | 2021-01-29 | 2022-06-28 | 深圳市明微电子股份有限公司 | Led显示屏节能方法、装置、设备及存储介质 |

| KR20230142330A (ko) | 2022-03-31 | 2023-10-11 | 주식회사 에스알이엔지 | 일체형 수배전반 열화 방지 시스템 및 이를 이용한 열화 방지 방법 |

| CN115240584B (zh) * | 2022-05-30 | 2023-11-28 | 北京奕斯伟计算技术股份有限公司 | 时序控制器、源极驱动芯片、驱动电路及驱动控制方法 |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07175454A (ja) * | 1993-10-25 | 1995-07-14 | Toshiba Corp | 表示制御装置および表示制御方法 |

| JP3318667B2 (ja) * | 1996-02-06 | 2002-08-26 | シャープ株式会社 | 液晶表示装置 |

| KR100477139B1 (ko) | 1997-07-23 | 2005-07-07 | 삼성전자주식회사 | 구동제어회로를갖는액정표시장치 |

| JPH11231843A (ja) | 1998-02-16 | 1999-08-27 | Sony Corp | 液晶表示装置 |

| US6538648B1 (en) * | 1998-04-28 | 2003-03-25 | Sanyo Electric Co., Ltd. | Display device |

| JP3336408B2 (ja) * | 1998-07-17 | 2002-10-21 | 株式会社アドバンスト・ディスプレイ | 液晶表示装置 |

| JP2000338936A (ja) * | 1999-05-28 | 2000-12-08 | Matsushita Electric Ind Co Ltd | 液晶表示装置 |

| JP2001202066A (ja) | 1999-11-09 | 2001-07-27 | Sharp Corp | 画像表示装置及びその駆動方法 |

| KR20010065766A (ko) * | 1999-12-30 | 2001-07-11 | 박종섭 | 구동 주파수를 감소시키기 위한 액정 표시 장치 및 이를이용한 주파수 변조 방법 |

| JP2001282163A (ja) * | 2000-03-30 | 2001-10-12 | Sanyo Electric Co Ltd | 表示装置 |

| JP2002297110A (ja) * | 2001-03-30 | 2002-10-11 | Sanyo Electric Co Ltd | アクティブマトリクス型液晶表示装置の駆動方法 |

| JP3911141B2 (ja) * | 2001-09-18 | 2007-05-09 | 株式会社日立製作所 | 液晶表示装置およびその駆動方法 |

| JP3719974B2 (ja) * | 2001-11-26 | 2005-11-24 | 株式会社アドバンスト・ディスプレイ | 液晶駆動装置 |

| JP2007041258A (ja) * | 2005-08-03 | 2007-02-15 | Mitsubishi Electric Corp | 画像表示装置およびタイミングコントローラ |

-

2006

- 2006-01-18 JP JP2006009709A patent/JP4853028B2/ja active Active

-

2007

- 2007-01-12 TW TW096101228A patent/TW200737112A/zh unknown

- 2007-01-15 KR KR1020070004107A patent/KR100832513B1/ko not_active IP Right Cessation

- 2007-01-17 US US11/623,990 patent/US7773083B2/en active Active

- 2007-01-18 CN CNB2007100020467A patent/CN100504525C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN100504525C (zh) | 2009-06-24 |

| TWI361420B (ja) | 2012-04-01 |

| US20070165127A1 (en) | 2007-07-19 |

| CN101004499A (zh) | 2007-07-25 |

| KR100832513B1 (ko) | 2008-05-26 |

| JP2007192982A (ja) | 2007-08-02 |

| KR20070076475A (ko) | 2007-07-24 |

| TW200737112A (en) | 2007-10-01 |

| US7773083B2 (en) | 2010-08-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4853028B2 (ja) | アクティブマトリクス表示装置、およびそのタイミング制御用半導体装置 | |

| JP4904641B2 (ja) | 液晶表示制御回路 | |

| JP5403879B2 (ja) | 液晶表示装置及びその駆動方法 | |

| JP5122396B2 (ja) | ドライバ及び表示装置 | |

| KR101325982B1 (ko) | 액정표시장치 및 이의 구동방법 | |

| KR100821016B1 (ko) | 액정 표시 장치 | |

| US20140340383A1 (en) | Display device and electrical apparatus | |

| WO2008029546A1 (en) | Display controller, display device, display system and method for controlling display device | |

| JP5522375B2 (ja) | 液晶表示装置、該装置に用いられるタイミングコントローラ及び信号処理方法 | |

| EP2065878A1 (en) | Displaying device, its driving circuit and its driving method | |

| US9412317B2 (en) | Display device and method of driving the same | |

| JP5617542B2 (ja) | マトリクス表示装置、およびマトリクス表示装置の駆動方法 | |

| JP7114875B2 (ja) | 電気光学装置、電気光学装置の制御方法および電子機器 | |

| CN101025899A (zh) | 源极驱动装置及其驱动方法、显示器件及其驱动方法 | |

| JP2009109955A (ja) | マトリクス表示装置用タイミングコントローラ、及びこれを採用した液晶表示装置 | |

| JP2005345603A (ja) | 液晶表示装置およびその駆動方法 | |

| JP3726910B2 (ja) | 表示ドライバ及び電気光学装置 | |

| WO2007135793A1 (ja) | カウンタ回路およびそれを備える制御信号生成回路ならびに表示装置 | |

| CN100356431C (zh) | 驱动液晶显示装置的装置 | |

| CN101174377B (zh) | 消除显示器系统的断电残影的方法与显示器系统 | |

| KR20080036283A (ko) | 표시 장치 및 이의 구동방법 | |

| JP2009015103A (ja) | 表示制御装置及びその制御方法 | |

| KR102465513B1 (ko) | 표시 장치 | |

| KR100521255B1 (ko) | 액정 표시 장치 및 그 구동 방법 | |

| JP2009265334A (ja) | 表示装置および表示装置の駆動方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081105 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20081105 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110712 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110905 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110927 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111010 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141104 Year of fee payment: 3 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 4853028 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141104 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |