JP4759944B2 - 不揮発性半導体記憶装置の製造方法 - Google Patents

不揮発性半導体記憶装置の製造方法 Download PDFInfo

- Publication number

- JP4759944B2 JP4759944B2 JP2004200913A JP2004200913A JP4759944B2 JP 4759944 B2 JP4759944 B2 JP 4759944B2 JP 2004200913 A JP2004200913 A JP 2004200913A JP 2004200913 A JP2004200913 A JP 2004200913A JP 4759944 B2 JP4759944 B2 JP 4759944B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- substrate

- memory cell

- peripheral circuit

- forming

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 34

- 238000004519 manufacturing process Methods 0.000 title claims description 32

- 238000000034 method Methods 0.000 title claims description 23

- 238000002955 isolation Methods 0.000 claims description 70

- 230000002093 peripheral effect Effects 0.000 claims description 65

- 239000000758 substrate Substances 0.000 claims description 61

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 36

- 229920005591 polysilicon Polymers 0.000 claims description 36

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 28

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 28

- 238000005530 etching Methods 0.000 claims description 16

- 238000000059 patterning Methods 0.000 claims description 7

- 229910052581 Si3N4 Inorganic materials 0.000 description 31

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 31

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 12

- 239000005380 borophosphosilicate glass Substances 0.000 description 11

- 238000000206 photolithography Methods 0.000 description 10

- 230000008878 coupling Effects 0.000 description 6

- 238000010168 coupling process Methods 0.000 description 6

- 238000005859 coupling reaction Methods 0.000 description 6

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 5

- 230000000052 comparative effect Effects 0.000 description 5

- 239000010410 layer Substances 0.000 description 5

- 229910052710 silicon Inorganic materials 0.000 description 5

- 239000010703 silicon Substances 0.000 description 5

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 5

- 229910052721 tungsten Inorganic materials 0.000 description 5

- 239000010937 tungsten Substances 0.000 description 5

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 4

- 239000011229 interlayer Substances 0.000 description 4

- 230000003647 oxidation Effects 0.000 description 3

- 238000007254 oxidation reaction Methods 0.000 description 3

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 230000000873 masking effect Effects 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- UAJUXJSXCLUTNU-UHFFFAOYSA-N pranlukast Chemical compound C=1C=C(OCCCCC=2C=CC=CC=2)C=CC=1C(=O)NC(C=1)=CC=C(C(C=2)=O)C=1OC=2C=1N=NNN=1 UAJUXJSXCLUTNU-UHFFFAOYSA-N 0.000 description 1

- 229960004583 pranlukast Drugs 0.000 description 1

- 230000002265 prevention Effects 0.000 description 1

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 1

- 229910021342 tungsten silicide Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/40—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the peripheral circuit region

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/76224—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using trench refilling with dielectric materials

- H01L21/76229—Concurrent filling of a plurality of trenches having a different trench shape or dimension, e.g. rectangular and V-shaped trenches, wide and narrow trenches, shallow and deep trenches

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/40—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the peripheral circuit region

- H10B41/42—Simultaneous manufacture of periphery and memory cells

- H10B41/43—Simultaneous manufacture of periphery and memory cells comprising only one type of peripheral transistor

- H10B41/44—Simultaneous manufacture of periphery and memory cells comprising only one type of peripheral transistor with a control gate layer also being used as part of the peripheral transistor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/30—EEPROM devices comprising charge-trapping gate insulators characterised by the memory core region

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

- Electrodes Of Semiconductors (AREA)

- Element Separation (AREA)

Description

先ず、図17(a)に示すように、シリコン基板1上に熱酸化膜2を形成し、熱酸化膜2上にシリコン窒化膜3を形成する。さらに、シリコン窒化膜3上に、素子分離領域に対応する部分が開口するレジストパターン4を写真製版により形成する。

その後、図21(b)に示すように、基板1全面にONO膜10を形成する。

そして、図22(b)に示すように、レジストパターン11をマスクとして、周辺回路のONO膜10及びポリシリコン膜8を順次ドライエッチングする。さらに、周辺回路の熱酸化膜7をフッ酸により除去する。その後、レジストパターン11を除去すると、図23(a)に示す構造が得られる。ここで、図23(a)に示すように、周辺回路において、分離酸化膜6表面が基板1表面よりも落ち込むことにより段差Bが生じ、この段差Bに起因して後述する問題が発生する。

基板の活性領域を分離する素子分離であって、その上面が該基板の表面よりも高い素子分離を該基板に形成する工程と、

前記基板上にシリコン酸化膜を形成する工程と、

前記素子分離の間の前記シリコン酸化膜上にポリシリコン膜を自己整合的に形成する工程と、

前記周辺回路を覆う第1レジストパターンを形成した後、前記メモリセルにおける前記素子分離を所定の膜厚だけエッチングする工程と、

前記基板全面に多層絶縁膜を形成する工程と、

前記メモリセルを覆う第2レジストパターンを形成した後、前記周辺回路における前記多層絶縁膜と前記ポリシリコン膜と前記シリコン酸化膜とを除去する工程と、

前記周辺回路の前記基板上にゲート絶縁膜を形成する工程と、

前記基板の全面に導電膜を形成する工程と、

前記周辺回路及び前記メモリセルにおける前記導電膜をパターニングする工程と、

前記メモリセルにおいて、パターニングされた前記導電膜をマスクとして前記多層絶縁膜及び前記ポリシリコン膜をパターニングする工程とを含むことを特徴とするものである。

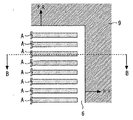

図1〜図11は、本実施の形態による不揮発性半導体記憶装置の製造方法を説明するための工程断面図である。

各図において、周辺回路の活性領域の断面と、メモリセルのゲート幅方向及びゲート長方向の断面を示している。また、必要に応じて、周辺回路の素子分離領域の断面を示している。

次に、図2(b)に示すように、シリコン窒化膜3をストッパ膜としてシリコン酸化膜6をCMP法により平坦化する。これにより、シリコン窒化膜3の表面と、シリコン酸化膜6の表面とが同じ高さになる。

次に、シリコン窒化膜3を熱リン酸により除去すると、図3(a)に示す構造が得られる。さらに、熱酸化膜2をフッ酸により除去すると、図3(b)に示す構造が得られる。これにより、上面が基板1表面よりも高い分離酸化膜6、すなわち基板1表面から上面が突き出た分離酸化膜6が形成される。図12は、メモリセルアレイにおける活性領域を示す上面図である。図12に示すように、短冊状の活性領域Aがその短手方向に複数並んで形成されており、活性領域Aを分離するように素子分離としての分離酸化膜6が形成されている。図25に示す従来のメモリセルアレイと異なり、本実施の形態ではメモリセルアレイの端部に活性領域A’が形成されたことにより、メモリセルアレイが活性領域A’により取り囲まれている。すなわち、メモリセルと周辺回路との境界部分に活性領域A’が形成されている。活性領域A’の周囲には周辺回路との素子分離が形成されている。このメモリセルアレイ端部に形成された活性領域A’は、短冊状の活性領域Aの端部を相互に接続する。活性領域A’の幅W1は、少なくとも短冊状の活性領域Aの幅W2よりも広い幅にする。なお、活性領域Aの端部には、ダミーゲート等を形成することができる。

次に、図4(b)に示すように、分離酸化膜6をストッパ膜としてポリシリコン膜8をCMP法により平坦化する。これにより、分離酸化膜6の表面と、ポリシリコン膜8の表面とが同じ高さになる。ここで、ポリシリコン膜8の位置は、分離酸化膜6に対して自己整合的に決められる。よって、フローティングゲート電極8が分離酸化膜6に対して自己整合的に形成されたことになり、写真製版を用いる場合に必要な分離酸化膜とフローティングゲート電極との高精度な位置合わせが不要になる。

そして、メモリセル領域を覆い、かつ、周辺回路領域に対応する部分が開口するレジストパターン11を写真製版により形成する。

その後、レジストパターン11を除去する。

次に、BPSG膜22及びプラグ27上に層間絶縁膜としてのBPSG膜28を形成する。そして、BPSG膜28上にヴィアホール形成部分が開口するレジストパターンを写真製版により形成する。さらに、このレジストパターンをマスクとしてBPSG膜28をドライエッチングすることにより、所望のプラグ27に達するヴィアホールが形成される。その後、レジストパターンを除去する。続いて、基板1全面にタングステン膜を堆積し、BPSG膜28をストッパ膜としてCMP法による平坦化又はエッチバックを行うことにより、ヴィアホール内にタングステンプラグ29が形成される。最後に、タングステンプラグ29に接続されたアルミニウム配線30を形成する。これにより、図11(b)に示すような構造が得られる。

図15は、本比較例において、メモリセルの活性領域と、周辺回路を覆うレジストパターンとの位置関係を示す上面図である。

上記実施の形態では、図13及び図14に示すように、メモリセルアレイ端部を取り囲む活性領域A’上にレジストパターン9端部を配置した。これにより、メモリセルと周辺回路の境界部分の分離酸化膜6がエッチングされず、段差の発生を防止することができる。すなわち、上記実施の形態による方法を用いて製造された不揮発性半導体記憶装置において、メモリセルと周辺回路の境界部分の分離酸化膜6上面が、基板1の表面と同等の高さであるか若しくは該表面よりも高い。

これに対して、本比較例では、図15に示すように、短冊状活性領域Aの端部を接続する活性領域A’を形成せず、メモリセルと周辺回路の境界部分の分離酸化膜6上にレジストパターン9端部を配置した。この場合、図16に示すように、レジストパターン9で覆われていない部分の分離酸化膜6がエッチングされてしまい、その結果として段差Cが生じる。この段差Cに起因して、その後にメモリセルをマスクして行う周辺回路のONO膜9,ポリシリコン膜8,熱酸化膜7の除去によって、メモリセルと周辺回路の境界部分において従来周辺回路で発生したような分離酸化膜6上の段差が発生してしまう。

本実施の形態では、活性領域A’上にレジストパターン9端部を配置することにより、かかる段差Cの発生を防止することができる。このため、メモリセルと周辺回路の境界部分において分離酸化膜6上の段差の発生を防止することができ、さらにエッチング残渣の発生を防止することができる。

Claims (2)

- メモリセルと、該メモリセルに隣接する周辺回路とを有する不揮発性半導体記憶装置の製造方法であって、

基板の活性領域を分離する素子分離であって、その上面が該基板の表面よりも高い素子分離を該基板に形成する工程と、

前記素子分離の間の前記基板上にシリコン酸化膜を形成する工程と、

前記素子分離の間の前記シリコン酸化膜上にポリシリコン膜を自己整合的に形成する工程と、

前記周辺回路を覆う第1レジストパターンを形成した後、前記メモリセルにおける前記素子分離を所定の膜厚だけエッチングする工程と、

前記基板全面に多層絶縁膜を形成する工程と、

前記メモリセルを覆う第2レジストパターンを形成した後、前記素子分離の表面を前記基板の表面よりも落ち込ませることなく、前記周辺回路における前記素子分離の上面を前記基板の表面と同等の高さとなるように若しくは前記基板の表面よりも高くなるように、前記周辺回路における前記多層絶縁膜と前記ポリシリコン膜と前記シリコン酸化膜とを除去する工程と、

前記周辺回路の前記基板上にゲート絶縁膜を形成する工程と、

前記基板の全面に導電膜を形成する工程と、

前記周辺回路及び前記メモリセルにおける前記導電膜をパターニングする工程と、

前記メモリセルにおいて、パターニングされた前記導電膜をマスクとして前記多層絶縁膜及び前記ポリシリコン膜をパターニングする工程とを含み、

前記メモリセルにおける活性領域は、短手方向に複数並んで配置された短冊状の第1活性領域と、該第1活性領域の端部を相互に接続すると共に前記メモリセルを取り囲むように配置された第2活性領域とを有し、

前記第1レジストパターンの端部が前記第2活性領域に位置するように前記第1レジストパターンを形成することを特徴とする不揮発性半導体記憶装置の製造方法。 - メモリセルと、該メモリセルに隣接する周辺回路とを有する不揮発性半導体記憶装置の製造方法であって、

基板の活性領域を分離する素子分離であって、その上面が該基板の表面よりも高い素子分離を該基板に形成する工程と、

前記素子分離の間の前記基板上にトンネル酸化膜となるシリコン酸化膜を形成する工程と、

前記素子分離の間の前記シリコン酸化膜上にフローティングゲート電極となるポリシリコン膜を自己整合的に形成する工程と、

前記周辺回路を覆う第1レジストパターンを形成した後、前記メモリセルにおける前記素子分離を所定の膜厚だけエッチングすることにより、前記メモリセルにおける前記ポリシリコン膜の側面上部を露出させる工程と、

前記第1レジストパターンを除去した後、前記基板全面に多層絶縁膜を形成する工程と、

前記メモリセルを覆う第2レジストパターンを形成した後、前記素子分離の表面を前記基板の表面よりも落ち込ませることなく、前記周辺回路における前記素子分離の上面を前記基板の表面と同等の高さとなるように若しくは前記基板の表面よりも高くなるように、前記周辺回路における前記多層絶縁膜と前記ポリシリコン膜と前記シリコン酸化膜とを除去する工程と、

前記周辺回路における前記シリコン酸化膜を除去した後、周辺回路の前記基板上にゲート絶縁膜を形成する工程と、

前記基板の全面にゲート電極又はコントロールゲート電極となる導電膜を形成する工程と、

前記周辺回路及び前記メモリセルにおける前記導電膜をパターニングすることにより、前記周辺回路の前記ゲート絶縁膜上にゲート電極を形成すると共に、前記メモリセルの前記多層絶縁膜上にコントロールゲート電極を形成する工程と、

前記コントロールゲート電極をマスクとして前記メモリセルの前記多層絶縁膜及び前記ポリシリコン膜をパターニングすることにより、フローティングゲート電極を形成する工程とを含み、

前記メモリセルにおける活性領域は、短手方向に複数並んで配置された短冊状の第1活性領域と、該第1活性領域の端部を相互に接続すると共に前記メモリセルを取り囲むように配置された第2活性領域とを有し、

前記第1レジストパターンの端部が前記第2活性領域に位置するように前記第1レジストパターンを形成することを特徴とする不揮発性半導体記憶装置の製造方法。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004200913A JP4759944B2 (ja) | 2004-07-07 | 2004-07-07 | 不揮発性半導体記憶装置の製造方法 |

| KR1020050059704A KR101148177B1 (ko) | 2004-07-07 | 2005-07-04 | 불휘발성 반도체 기억장치의 제조방법 및 불휘발성 반도체기억장치 |

| US11/172,886 US7592226B2 (en) | 2004-07-07 | 2005-07-05 | Method for manufacturing non-volatile semiconductor memory device, and non-volatile semiconductor memory device |

| US12/537,652 US7829414B2 (en) | 2004-07-07 | 2009-08-07 | Method for manufacturing non-volatile semiconductor memory device, and non-volatile semiconductor memory device |

| US12/906,521 US8344473B2 (en) | 2004-07-07 | 2010-10-18 | Method for manufacturing non-volatile semiconductor memory device, and non-volatile semiconductor memory device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004200913A JP4759944B2 (ja) | 2004-07-07 | 2004-07-07 | 不揮発性半導体記憶装置の製造方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010079205A Division JP2010183098A (ja) | 2010-03-30 | 2010-03-30 | 不揮発性半導体記憶装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006024705A JP2006024705A (ja) | 2006-01-26 |

| JP2006024705A5 JP2006024705A5 (ja) | 2007-08-02 |

| JP4759944B2 true JP4759944B2 (ja) | 2011-08-31 |

Family

ID=35540423

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004200913A Expired - Fee Related JP4759944B2 (ja) | 2004-07-07 | 2004-07-07 | 不揮発性半導体記憶装置の製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (3) | US7592226B2 (ja) |

| JP (1) | JP4759944B2 (ja) |

| KR (1) | KR101148177B1 (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4759944B2 (ja) * | 2004-07-07 | 2011-08-31 | ルネサスエレクトロニクス株式会社 | 不揮発性半導体記憶装置の製造方法 |

| KR100594326B1 (ko) * | 2005-03-22 | 2006-06-30 | 삼성전자주식회사 | 2-비트 동작을 위한 비휘발성 메모리 소자 및 그 제조 방법 |

| US8183595B2 (en) * | 2005-07-29 | 2012-05-22 | International Rectifier Corporation | Normally off III-nitride semiconductor device having a programmable gate |

| WO2012071100A1 (en) * | 2010-09-08 | 2012-05-31 | William Marsh Rice University | Siox-based nonvolatile memory architecture |

| US8735863B2 (en) | 2011-01-28 | 2014-05-27 | Privatran | Integrated nonvolatile resistive memory elements |

| US9385163B2 (en) | 2011-08-26 | 2016-07-05 | William Marsh Rice University | Addressable SiOX memory array with incorporated diodes |

| JP2013135029A (ja) * | 2011-12-26 | 2013-07-08 | Elpida Memory Inc | 半導体装置の製造方法 |

| US9059094B2 (en) * | 2012-08-24 | 2015-06-16 | Macronix International Co., Ltd. | Semiconductor gate structure and method of fabricating thereof |

| US10071801B2 (en) * | 2013-08-13 | 2018-09-11 | The United States Of America As Represented By The Administrator Of Nasa | Tri-rotor aircraft capable of vertical takeoff and landing and transitioning to forward flight |

| US9425206B2 (en) * | 2014-12-23 | 2016-08-23 | Taiwan Semiconductor Manufacturing Co., Ltd. | Boundary scheme for embedded poly-SiON CMOS or NVM in HKMG CMOS technology |

| JP7117223B2 (ja) * | 2018-11-08 | 2022-08-12 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3710880B2 (ja) | 1996-06-28 | 2005-10-26 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| JP3540633B2 (ja) * | 1998-11-11 | 2004-07-07 | 株式会社東芝 | 半導体装置の製造方法 |

| JP2001036048A (ja) * | 1999-07-16 | 2001-02-09 | Denso Corp | 半導体メモリ及びその製造方法 |

| KR20010036048A (ko) | 1999-10-05 | 2001-05-07 | 천경호 | 숙취해소용 음료조성물 |

| JP4911826B2 (ja) | 2001-02-27 | 2012-04-04 | ルネサスエレクトロニクス株式会社 | 不揮発性半導体記憶装置およびその製造方法 |

| JP2003023115A (ja) | 2001-07-06 | 2003-01-24 | Mitsubishi Electric Corp | 不揮発性半導体記憶装置の製造方法及び不揮発性半導体記憶装置 |

| JP4160283B2 (ja) * | 2001-09-04 | 2008-10-01 | 株式会社東芝 | 半導体装置の製造方法 |

| JP2003289114A (ja) * | 2002-03-28 | 2003-10-10 | Toshiba Corp | 半導体記憶装置及びその製造方法 |

| JP4759944B2 (ja) * | 2004-07-07 | 2011-08-31 | ルネサスエレクトロニクス株式会社 | 不揮発性半導体記憶装置の製造方法 |

-

2004

- 2004-07-07 JP JP2004200913A patent/JP4759944B2/ja not_active Expired - Fee Related

-

2005

- 2005-07-04 KR KR1020050059704A patent/KR101148177B1/ko not_active IP Right Cessation

- 2005-07-05 US US11/172,886 patent/US7592226B2/en active Active

-

2009

- 2009-08-07 US US12/537,652 patent/US7829414B2/en active Active

-

2010

- 2010-10-18 US US12/906,521 patent/US8344473B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US8344473B2 (en) | 2013-01-01 |

| US20060006492A1 (en) | 2006-01-12 |

| JP2006024705A (ja) | 2006-01-26 |

| US7592226B2 (en) | 2009-09-22 |

| KR101148177B1 (ko) | 2012-05-24 |

| US7829414B2 (en) | 2010-11-09 |

| US20100219498A1 (en) | 2010-09-02 |

| US20110031580A1 (en) | 2011-02-10 |

| KR20060049817A (ko) | 2006-05-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4947931B2 (ja) | 半導体装置 | |

| KR101148177B1 (ko) | 불휘발성 반도체 기억장치의 제조방법 및 불휘발성 반도체기억장치 | |

| JP2008078298A (ja) | 半導体装置及びその製造方法 | |

| JP4822792B2 (ja) | 半導体装置およびその製造方法 | |

| JP2008205379A (ja) | 不揮発性半導体メモリ及びその製造方法 | |

| JP2008047630A (ja) | 半導体装置およびその製造方法 | |

| US20080081463A1 (en) | Method for fabricating storage node contact in semiconductor device | |

| JP2008091368A (ja) | 半導体装置及びその製造方法 | |

| JP2004055826A (ja) | 半導体装置の製造方法 | |

| JP2010183098A (ja) | 不揮発性半導体記憶装置 | |

| JP2008192891A (ja) | 半導体装置及びその製造方法 | |

| KR100660548B1 (ko) | 비휘발성 메모리 장치 및 그 형성 방법 | |

| JP2005294518A (ja) | 半導体装置およびその製造方法 | |

| KR101002519B1 (ko) | 플래쉬 메모리 소자의 제조 방법 | |

| JP2006196895A (ja) | 自己整列コンタクトの形成方法 | |

| JP2005311166A (ja) | 半導体記憶装置およびその製造方法 | |

| KR100506050B1 (ko) | 반도체소자의 콘택 형성방법 | |

| KR101061171B1 (ko) | 반도체 소자의 제조방법 | |

| KR100605102B1 (ko) | 반도체소자의 콘택 플러그 구조체 및 그 형성 방법 | |

| JP2010034291A (ja) | 不揮発性半導体記憶装置の製造方法 | |

| KR20090009392A (ko) | 반도체 소자의 제조 방법 | |

| JP2008118025A (ja) | 半導体装置およびその製造方法 | |

| JP2008192890A (ja) | 半導体装置およびその製造方法 | |

| JP2010080602A (ja) | 半導体装置およびその製造方法 | |

| JP2010080603A (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070618 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070618 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100127 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100202 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100330 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100521 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101124 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110119 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110208 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110331 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20110408 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110510 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110523 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140617 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 4759944 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |