JP2008205379A - 不揮発性半導体メモリ及びその製造方法 - Google Patents

不揮発性半導体メモリ及びその製造方法 Download PDFInfo

- Publication number

- JP2008205379A JP2008205379A JP2007042408A JP2007042408A JP2008205379A JP 2008205379 A JP2008205379 A JP 2008205379A JP 2007042408 A JP2007042408 A JP 2007042408A JP 2007042408 A JP2007042408 A JP 2007042408A JP 2008205379 A JP2008205379 A JP 2008205379A

- Authority

- JP

- Japan

- Prior art keywords

- gate electrode

- contact portion

- source

- insulating film

- source line

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B69/00—Erasable-and-programmable ROM [EPROM] devices not provided for in groups H10B41/00 - H10B63/00, e.g. ultraviolet erasable-and-programmable ROM [UVEPROM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/0411—Manufacture or treatment of FETs having insulated gates [IGFET] of FETs having floating gates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/68—Floating-gate IGFETs

- H10D30/681—Floating-gate IGFETs having only two programming levels

- H10D30/683—Floating-gate IGFETs having only two programming levels programmed by tunnelling of carriers, e.g. Fowler-Nordheim tunnelling

Landscapes

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Abstract

【課題】メモリセルトランジスタを微細化でき、且つ、メモリセルアレイ部のサイズを縮小できる。

【解決手段】本発明の例に関わる不揮発性半導体メモリは、半導体基板1表面に形成されるソース及びドレイン拡散層5,6と、ソース及びドレイン拡散層5,6間のチャネル領域上に形成されるゲート絶縁膜2と、ゲート絶縁膜2上に形成されるフローティングゲート電極3と、フローティングゲート電極3上に、電極間絶縁膜10を介して形成されるコントロールゲート電極11と、ソース拡散層5に接触するソース線コンタクト部SC1とを具備し、ソース線コンタクト部SC1の上端は、コントロールゲート電極11の下端より低い位置にあることを備える。

【選択図】図2

【解決手段】本発明の例に関わる不揮発性半導体メモリは、半導体基板1表面に形成されるソース及びドレイン拡散層5,6と、ソース及びドレイン拡散層5,6間のチャネル領域上に形成されるゲート絶縁膜2と、ゲート絶縁膜2上に形成されるフローティングゲート電極3と、フローティングゲート電極3上に、電極間絶縁膜10を介して形成されるコントロールゲート電極11と、ソース拡散層5に接触するソース線コンタクト部SC1とを具備し、ソース線コンタクト部SC1の上端は、コントロールゲート電極11の下端より低い位置にあることを備える。

【選択図】図2

Description

本発明は、不揮発性半導体メモリに係り、特に、積層ゲート構造を有するメモリセルトランジスタに関する。

不揮発性半導体メモリとして、例えば、NAND型或いはNOR型フラッシュメモリが、電子機器に用いられている。

NOR型フラッシュメモリにおいて、メモリセルトランジスタは、例えば、コントロールゲート電極とフローティングゲート電極からなる積層ゲート構造のMOS(Metal Oxide Semiconductor)トランジスタである。

その積層ゲート構造は、メモリセルアレイ部内にライン&スペースで形成されるため、メモリセルトランジスタのチャネル領域及びソース及びドレイン拡散層は、容易に微細化できる(例えば、特許文献1参照)。

一方、それらのソース及びドレイン拡散層とビット線及びソース線を接続するために設けられるコンタクト部の微細化は容易ではない。

コンタクト部は、積層ゲート電極及びソース/ドレイン拡散層が形成された後に形成される。そのため、コンタクト部が埋め込まれるコンタクトホールは、積層ゲート電極の高さに基づいたアスペクト比で形成される。

それゆえ、ソース/ドレイン拡散層は、コンタクト材のコンタクトホールへの埋め込み性や、コンタクト部とゲート電極とのショートマージンの確保などにより、サイズが大きくなってしまう。

この問題は、積層ゲート構造のメモリセルトランジスタでは顕著であり、コンタクト部の微細化が、メモリセルアレイ部全体の微細化に追随できていない。そのため、メモリセルアレイ内に占めるコンタクト部の面積が、徐々に増大する傾向にある。

また、上記の問題を解決するため、ソース線コンタクト部を設けず、ソース拡散層がワード線の延びる方向に共有されるように形成し、その拡散層をコンタクト部の代替とする方法(SAS:Self Aligned Source)が、よく用いられる。

しかし、SASは、タングステン(W)などのプラグ材を用いたコンタクト部と比較すると、抵抗値が大きくなってしまう。

それゆえ、メモリセルアレイ部内にシャント領域が一定間隔で設けられる。シャント領域内では、SASの上部にそれよりも低抵抗率のソース線が配置され、両者は、コンタクト部を介して、互いに接続される。

特開2004−152878号公報

本発明の例は、メモリセルトランジスタを微細化できる技術について提案する。

本発明の例に関わる不揮発性半導体メモリは、半導体基板表面に形成されるソース及びドレイン拡散層と、前記ソース及びドレイン拡散層間のチャネル領域上に形成されるゲート絶縁膜と、前記ゲート絶縁膜上に形成されるフローティングゲート電極と、前記フローティングゲート電極上に、電極間絶縁膜を介して形成されるコントロールゲート電極と、前記ソース拡散層に接触するソース線コンタクト部とを具備し、前記ソース線コンタクト部の上端は、前記コントロールゲート電極の下端より低い位置にあることを備える。

本発明の例に関わる不揮発性半導体メモリは、半導体基板表面に形成されるソース及びドレイン拡散層と、前記ソース及びドレイン拡散層間のチャネル領域上に形成されるゲート絶縁膜と、前記ゲート絶縁膜上に形成されるフローティングゲート電極と、前記ソース拡散層に接触するソース線コンタクト部と、前記フローティングゲート電極上面及び前記ソース線コンタクト部上面を覆う電極間絶縁膜と、前記電極間絶縁膜を介して、前記フローティングゲート電極上に形成されるコントロールゲート電極とを具備し、前記コントロールゲート電極の上面は、前記ソース線コンタクト部上面を覆う電極間絶縁膜上面以下の位置にあることを備える。

本発明の例に関わる不揮発性半導体メモリの製造方法は、半導体基板表面上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上にフローティングゲート電極を形成する工程と、前記フローティングゲート電極をマスクとして、ソース及びドレイン拡散層を形成する工程と、前記フローティングゲート電極の上端と一致するように、前記拡散層上に絶縁層を形成する工程と、前記絶縁層内に前記拡散層の表面が露出するようにコンタクトホールを形成する工程と、前記拡散層と接触するようにソース線コンタクト部を前記コンタクトホールに埋め込む工程と、前記フローティングゲート電極上に、電極間絶縁膜を形成する工程と、前記電極間絶縁膜上に、コントロールゲート電極を形成する工程とを備える。

本発明の例によれば、メモリセルトランジスタを微細化できる。

以下、図面を参照しながら、本発明の例を実施するための最良の形態について詳細に説明する。

1. 概要

本発明の実施形態の不揮発性半導体メモリは、積層ゲート構造を有するメモリセルトランジスタに関する。

本発明の実施形態の不揮発性半導体メモリは、積層ゲート構造を有するメモリセルトランジスタに関する。

例えば、NOR型フラッシュメモリにおいて、メモリセルトランジスタの拡散層とソース線或いはビット線を接続するために、コンタクト部が設けられる。そのコンタクト部は、1つ或いは2つ以上のコンタクト層からなる。

本発明の実施形態は、コンタクト部が2つ以上のコンタクト層から構成される場合において、ソース拡散層に接触するソース線コンタクト部の上端が、コントロールゲート電極の下端より低い位置にあることを特徴とする。ここで、下端方向は基板方向、上端方向は基板と反対方向と定義する。そして、低い位置にあるとは、比較対象の部材・部位よりも基板方向にあることと定義する。

本発明の実施形態では、ソース拡散層に接触するコンタクト部が埋め込まれるコンタクトホールは、フローティングゲート電極の高さに基づいたアスペクト比で形成される。

それゆえ、積層ゲート電極の高さでコンタクトホールを形成する場合のアスペクト比に比べ、そのアスペクト比を低減でき、拡散層のサイズを縮小できる。

したがって、本発明の実施形態は、メモリセルトランジスタを微細化でき、メモリセルアレイ部のサイズを縮小できる。

また、本発明の実施形態の構造においては、上記のソース拡散層に接触するコンタクト部が、コントロールゲート電極が形成される工程より、前の工程で形成される。即ち、本発明の実施形態では、積層される2つのゲート電極が、それぞれ異なる工程で形成される製造方法となる。

それゆえ、本発明の実施形態では、上記の構造を得るための製造方法についても説明する。

尚、本発明の実施形態で述べるソース線及びビット線コンタクト部とは、ソース線及びビット線より下層に位置するコンタクト部と定義する。

2. 実施の形態

次に、最良と思われるいくつかの実施の形態について説明する。

次に、最良と思われるいくつかの実施の形態について説明する。

尚、本発明の実施形態は、NOR型フラッシュメモリを例として、詳細な説明を行う。

また、コンタクト部の定義は、概要で説明した通りとする。

(1) 第1の実施形態

(a) 実施例

(i) 構造

図1乃至図4を用いて、本実施形態の構造について説明する。

(a) 実施例

(i) 構造

図1乃至図4を用いて、本実施形態の構造について説明する。

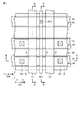

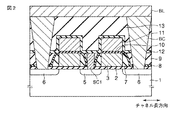

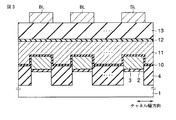

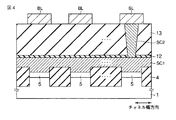

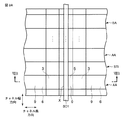

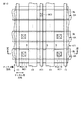

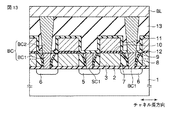

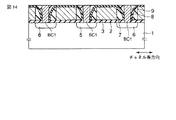

図1は、NOR型フラッシュメモリのメモリセルアレイ部の平面図を示す。図2は、図1のII−II線に沿う断面を示す。また、図3は、図1のIII−III線に沿う断面を示し、図4は、図1のIV−IV線に沿う断面図を示す。

図1に示すように、メモリセルアレイ部は、アクティブ領域AAと、アクティブ領域AAを電気的に分離する素子分離領域STIを有している。

メモリセルトランジスタは、素子分離領域STIに囲まれたアクティブ領域AA上に、マトリクス状に配置されている。

NOR型フラッシュメモリにおいて、1つのメモリセルトランジスタのドレイン拡散層6には、ビット線コンタクト部BCが接続される。また、そのソース拡散層5には、第1のソース線コンタクト部SC1が接続される。

ソース線コンタクト部SC1は、アクティブ領域AAを横切る方向(チャネル幅方向)に延びる。

ビット線BLは、アクティブ領域AA上層を、チャネル長方向に延びる。

ソース線SLは、例えば、メモリセルアレイ部内に設けられたシャント領域SA上層に設けられ、ビット線BLと同様に、チャネル長方向に延びる。ソース線SLは、シャント領域SA内に設けられた第2のソース線コンタクト部SC2を介して、第1のソース線コンタクト部SC1と接続される。シャント領域SAは、例えば、64個のアクティブ領域AA毎に、設けられる。

また、ワード線を兼ねるコントロールゲート電極11は、ビット線BLが延びる方向と直交する方向に延びる。

図2乃至図4に示すように、メモリセルトランジスタは、フローティングゲート電極3及びコントロールゲート電極11から構成される積層ゲート構造を有している。この積層ゲートの高さは、例えば、300nm程度である。

フローティングゲート電極3は、半導体基板1表面に形成されたゲート絶縁膜2上に配置される。チャネル幅方向に隣接するフローティングゲート電極3は、例えば、STI(Shallow Trench Isoration)構造の素子分離絶縁層4により、電気的に分離される。フローティングゲート電極3は、例えば、ポリシリコンから構成される。

また、フローティングゲート電極3のチャネル長方向の側壁には、例えば、スペーサ絶縁層7が形成される。

また、フローティングゲート電極3のチャネル長方向の側壁には、例えば、スペーサ絶縁層7が形成される。

コントロールゲート電極11は、電極間絶縁膜10を介して、フローティングゲート電極3上に配置される。そして、このコントロールゲート電極11は、ワード線として機能するため、チャネル幅方向に延び、チャネル幅方向に隣接するメモリセルトランジスタ間で共有される。コントロールゲート電極11は、例えば、ポリシリコンから構成される。尚、本実施例においては、一層構造のコントロールゲート電極を示すが、例えば、ポリシリコン膜とその上層に形成されるシリサイド膜からなる2層構造のコントロールゲート電極でもよい。

また、図3に示すように、コントロールゲート電極11は、例えば、電極間絶縁膜10を介して、フローティングゲート電極3のチャネル幅方向の側部を覆うように形成されても良い。このような構造とすることで、フローティングゲート電極3とコントロールゲート電極11間のカップリング比を向上できる。

ソース拡散層5及びドレイン拡散層6は、メモリセルトランジスタのソース/ドレイン領域として、半導体基板1表面に形成される。ソース及びドレイン拡散層5,6は、チャネル長方向に隣接するメモリセルトランジスタ間で、それぞれ共有されている。

ドレイン拡散層6は、ビット線コンタクト部BCを介して、ビット線BLに電気的に接続される。また、ビット線コンタクト部は、テーパ状に形成されたコンタクトホールに埋め込まれている。

ビット線BLは、チャネル長方向に隣接するメモリセルトランジスタ間で共有される。

ビット線BLは、チャネル長方向に隣接するメモリセルトランジスタ間で共有される。

ソース拡散層5は、第1及び第2のソース線コンタクト部SC1,SC2の2つのコンタクト層を介して、ソース線SLに電気的に接続される。ソース線コンタクト部SC1,SC2は、例えば、タングステン(W)から構成される。また、ソース線SLは、例えば、アルミ(Al)或いは銅(Cu)などの低抵抗率のメタル材から構成される。

尚、ソース線SL及びビット線BLと、コンタクト部BC,SC1,SC2との間には、中間金属膜及びその中間金属膜とソース線SL及びビット線とを接続するためのコンタクト部が設けられてもよい。

尚、本実施形態で述べるソース線及びビット線コンタクト部とは、ソース線及びビット線より下層(基板方向)に位置するコンタクト部と定義する。

第1のソース線コンタクト部SC1は、第1の絶縁層9内に形成されたスリット状のコンタクトホールに埋め込まれ、ソース拡散層5と接触している。そして、図4に示すように、第1のソース線コンタクト部SC1は、チャネル幅方向に隣接するメモリセルトランジスタのソース拡散層5間で、それぞれ共有接続される。即ち、第1のソース線コンタクト部SC1は、素子分離領域STI上及びアクティブ領域AA上を、チャネル幅方向に延びている。

第2のソース線コンタクト部SC2は、シャント領域SA内に設けられる。そして、第1のソース線コンタクト部SC1は、第2のソース線コンタクト部SC2により、シャント領域SA内で、ソース線SLと接続される。

第2のソース線コンタクト部SC2は、シャント領域SA内に設けられる。そして、第1のソース線コンタクト部SC1は、第2のソース線コンタクト部SC2により、シャント領域SA内で、ソース線SLと接続される。

尚、上述のように、第1のソース線コンタクト部SC1は、チャネル幅方向に隣接するメモリセルトランジスタ間で共有されている。そのため、第1のソース線コンタクト部SC1を、ワード線の延びる方向に延びるソース線として用いることもでき、そのソース線コンタクト部SC1からメモリセルトランジスタにソース電圧を供給することもできる。その場合には、図1乃至4に示すようなソース線SL及び第2のコンタクト部SC2を設けずともよい。

また、本実施の形態において、ソース線SLが、ビット線BLと同じ層内に設けられた例を示すが、中間金属膜を用いて、ビット線BLとソース線SLとを、異なる層内に設けても良い。

本実施形態では、ソース拡散層5と接触している第1のソース線コンタクト部SC1の上端は、コントロールゲート電極11の下端よりも低い位置にある。ここで、下端方向は基板方向、上端方向は基板と反対方向と定義する。そして、低い位置にあるとは、比較対象の部材・部位よりも基板方向にあることと定義する。

コンタクトホールを形成する際のアスペクト比は、開口幅Wに対する深さ(高さ)Dのサイズ比D/Wによって決定される。

第1のソース線コンタクト部SC1が埋め込まれるコンタクトホールのアスペクト比は、フローティングゲート電極3の膜厚(高さ)とソース拡散層5のチャネル長方向のサイズで決定される。

よって、そのコンタクトホールの高さ方向のサイズが小さくなるので、アスペクト比を低減できる。そして、コンタクトホールの幅方向のサイズを小さくしても、コンタクトホールの形成に必要なアスペクト比を確保できる。

第1のソース線コンタクト部SC1が埋め込まれるコンタクトホールのアスペクト比は、フローティングゲート電極3の膜厚(高さ)とソース拡散層5のチャネル長方向のサイズで決定される。

よって、そのコンタクトホールの高さ方向のサイズが小さくなるので、アスペクト比を低減できる。そして、コンタクトホールの幅方向のサイズを小さくしても、コンタクトホールの形成に必要なアスペクト比を確保できる。

それゆえ、第1のソース線コンタクト部SC1が埋め込まれるコンタクトホールのアスペクト比を確保するために、ソース拡散層5のチャネル長方向のサイズを大きくする必要がない。

したがって、ソース拡散層5のチャネル長方向のサイズを縮小できる。

以上のように、本発明の第1の実施形態では、メモリセルトランジスタを微細化でき、メモリセルアレイ部のサイズを縮小できる。

以下には、上記の構造の製造方法について、説明する。

(ii) 製造方法

上記の構造を得るためには、第1のソース線コンタクト部SC1が、コントロールゲート電極11が形成される前に、形成される。

即ち、上記のメモリセルトランジスタ及びソース線コンタクト部の構造は、コントロールゲート電極とフローティングゲート電極を同時にゲート加工する自己整合的な手法を用いず、それらの電極を別途形成することで得られる。

上記の構造を得るためには、第1のソース線コンタクト部SC1が、コントロールゲート電極11が形成される前に、形成される。

即ち、上記のメモリセルトランジスタ及びソース線コンタクト部の構造は、コントロールゲート電極とフローティングゲート電極を同時にゲート加工する自己整合的な手法を用いず、それらの電極を別途形成することで得られる。

以下には、その製造方法について、詳細に説明する。

図5A乃至図10を用いて、第1の実施形態の製造方法について説明する。

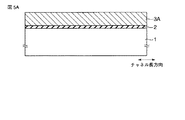

はじめに、図5A及び図5Bに示すように、例えば、シリコン酸化膜からなる、ゲート絶縁膜2が、例えば、熱酸化法により、半導体基板1表面に形成される。次に、ポリシリコン膜3Aが、例えば、CVD(Chemical Vapor Deposition)法により、ゲート絶縁膜2上に堆積される。

そして、ポリシリコン膜3Aは、所望のゲート幅となるようなライン&スペースのパターニングが施される。その後、ポリシリコン膜3A、半導体基板1が、例えば、RIE(Reactive Ion Etching)により、順次エッチングされる。それにより、所望のゲート幅となるポリシリコン膜3Aと、例えば、STI(Shallow Trench Isolation)構造の素子分離溝が形成される。

続いて、シリコン酸化物が、素子分離溝が埋め込まれるように、例えば、HDP−CVD(High Density Plasma CVD)法により、半導体基板1の全面に堆積される。その後、シリコン酸化物が、例えば、CMP(Chemical Mechanical Polising)法により、ポリシリコン膜3Aの上端と一致するように、平坦化される。すると、STI構造の素子分離絶縁層4が、半導体基板1内に形成される。

そして、ポリシリコン膜3Aは、所望のゲート幅となるようなライン&スペースのパターニングが施される。その後、ポリシリコン膜3A、半導体基板1が、例えば、RIE(Reactive Ion Etching)により、順次エッチングされる。それにより、所望のゲート幅となるポリシリコン膜3Aと、例えば、STI(Shallow Trench Isolation)構造の素子分離溝が形成される。

続いて、シリコン酸化物が、素子分離溝が埋め込まれるように、例えば、HDP−CVD(High Density Plasma CVD)法により、半導体基板1の全面に堆積される。その後、シリコン酸化物が、例えば、CMP(Chemical Mechanical Polising)法により、ポリシリコン膜3Aの上端と一致するように、平坦化される。すると、STI構造の素子分離絶縁層4が、半導体基板1内に形成される。

そして、ポリシリコン膜3Aが、所望のゲート長となるようなライン&スペースのパターニングが施される。このとき、そのパターニングは、例えば、後の工程でビット線コンタクト部が形成される領域のゲート間隔が、ソース線コンタクト部が形成される領域のゲート間隔よりも広くなるように形成される。そして、ポリシリコン膜3Aが、そのパターンに基づいて、例えば、RIEによりエッチングされる。

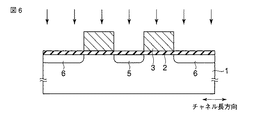

すると、図6に示すように、フローティングゲート電極3が形成される。そして、ソース拡散層5及びドレイン拡散層6が、例えば、イオン注入法により、半導体基板1表面に、フローティングゲート電極3をマスクとして、自己整合的に形成される。

すると、図6に示すように、フローティングゲート電極3が形成される。そして、ソース拡散層5及びドレイン拡散層6が、例えば、イオン注入法により、半導体基板1表面に、フローティングゲート電極3をマスクとして、自己整合的に形成される。

その後、例えば、SiNが、半導体基板1の全面を覆うように、例えば、CVD法により堆積された後、SiNに対して、エッチバックが施される。

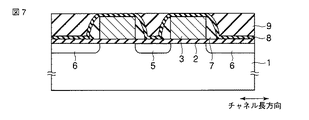

すると、図7に示すように、フローティングゲート電極3の側壁に、スペーサ絶縁層7が、形成される。このとき、ソース拡散層5上には、スペーサ絶縁層7からなる凹部が形成される。尚、このスペーサ絶縁層7は、後に形成するソース線コンタクト部とゲート電極とのショートマージンが確保できる場合には、形成せずとも良い。

その後、後の工程でCMPのストッパ膜となる、例えば、SiN膜8が、半導体基板1上の全面を覆うように形成される。さらに、例えば、BPSG(Boron Phosphorous Silicate Glass)又はTEOSなどから構成される第1の絶縁層9が、例えば、HDP−CVD法及びCMP法を用いて、その上端が、ストッパ膜であるSIN膜8の上端と一致するように形成される。

すると、図7に示すように、フローティングゲート電極3の側壁に、スペーサ絶縁層7が、形成される。このとき、ソース拡散層5上には、スペーサ絶縁層7からなる凹部が形成される。尚、このスペーサ絶縁層7は、後に形成するソース線コンタクト部とゲート電極とのショートマージンが確保できる場合には、形成せずとも良い。

その後、後の工程でCMPのストッパ膜となる、例えば、SiN膜8が、半導体基板1上の全面を覆うように形成される。さらに、例えば、BPSG(Boron Phosphorous Silicate Glass)又はTEOSなどから構成される第1の絶縁層9が、例えば、HDP−CVD法及びCMP法を用いて、その上端が、ストッパ膜であるSIN膜8の上端と一致するように形成される。

次に、図8A及び図8Bに示すように、ソース拡散層5表面が露出するように、コンタクトホールXが、例えば、RIEにより、絶縁層9内に形成される。このコンタクトホールXを形成するためのアスペクト比は、フローティングゲート電極3の膜厚(高さ)に比例して、決定される。よって、積層ゲートの高さでアスペクト比を決定するよりも、アスクペクト比を低減でき、それゆえ、ソース拡散層5のサイズを小さくできる。また、そのコンタクトホールXは、チャネル幅方向に延びるスリット状の構造となっている。

続いて、例えば、タングステン(W)などからなる、第1のソース線コンタクト部SC1が、ストッパ膜であるSiN膜8の上端と一致するように、コンタクトホールXに埋め込まれる。

続いて、例えば、タングステン(W)などからなる、第1のソース線コンタクト部SC1が、ストッパ膜であるSiN膜8の上端と一致するように、コンタクトホールXに埋め込まれる。

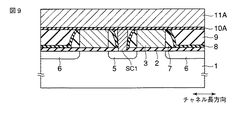

SiN膜8が、例えば、RIEにより除去された後、図9に示すように、電極間絶縁膜となる、例えば、ONO膜10A及びコントロールゲート電極となる、例えば、ポリシリコン膜11Aが、半導体基板1上の全面に、順次堆積される。

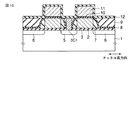

その後、図10に示すように、所望のゲート幅となるように、ポリシリコン膜及びONO膜が、RIE法に順次エッチングされ、電極間絶縁膜10及びコントロールゲート電極11が、形成される。

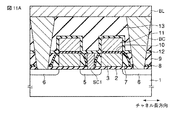

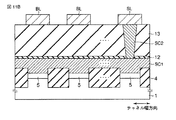

そして、図11A及び図11Bに示すように、バリア膜12が、コントロールゲート電極11の表面を覆うように形成され、その後、第2の絶縁層13が、半導体基板1上の全面に堆積される。さらに、第1のソース線コンタクトSC1と接触するように、第2のソース線コンタクトSC2が、絶縁層13内に形成された、例えば、テーパ状のコンタクトホールに埋め込まれる。

また、ビット線コンタクト部BCが、ドレイン拡散層6に接触するように、絶縁層9,13内に形成された開口部に埋め込まれる。

その後、例えば、Al或いはCuなどのメタル材からなる、ビット線BL及びソース線SLが、絶縁層13上面に、形成される。

また、ビット線コンタクト部BCが、ドレイン拡散層6に接触するように、絶縁層9,13内に形成された開口部に埋め込まれる。

その後、例えば、Al或いはCuなどのメタル材からなる、ビット線BL及びソース線SLが、絶縁層13上面に、形成される。

以上の製造工程により、本実施の形態のNOR型フラッシュメモリが完成する。

以上の製造工程で作製されたメモリセルトランジスタは、フローティングゲート電極の高さに基づいたアスペクト比で、ソース拡散層に接触する第1のソース線コンタクト部を形成できる。

よって、ソース拡散層のサイズを縮小でき、メモリセルトランジスタの微細化及びメモリセルアレイ部のサイズを縮小できる。

(b) 応用例

本実施形態において、リソグラフィ及びプラグ材の埋め込み性の観点から、スリット状のコンタクトホールに埋め込まれるソース線コンタクト部のほうが、ビット線コンタクト部に比べ、微細化の効果が大きい。

本実施形態において、リソグラフィ及びプラグ材の埋め込み性の観点から、スリット状のコンタクトホールに埋め込まれるソース線コンタクト部のほうが、ビット線コンタクト部に比べ、微細化の効果が大きい。

それゆえ、実施例においては、ソース線コンタクト部の上端が、コントロールゲート電極の下端より低い位置となるように形成され、ソース拡散層のチャネル長方向のサイズを縮小できる例について、説明した。

しかし、本発明の実施形態は、ソース線コンタクト部のみならず、ビット線コンタクト部にも適用でき、それにより、メモリセルトランジスタのサイズをさらに縮小することもできる。

以下には、本発明の実施形態を、ソース線コンタクト部及びビット線コンタクト部に適用した例について、説明する。

(i) 構造

図12は、本応用例の平面図を示し、図13は、図11のXIII−XIII線に沿う断面図を示す。

図12は、本応用例の平面図を示し、図13は、図11のXIII−XIII線に沿う断面図を示す。

図13に示すように、ビット線コンタクト部BCは、第1のソース線コンタクト部SC1と同時に形成される第1のビット線コンタクト部BC1と、第1のビット線コンタクト部BC1とビット線BLとを接続する第2のビット線コンタクト部BC2とから構成される。

本応用例において、第1のビット線コンタクト部BC1は、第1のソース線コンタクト部SC1と同時に形成される。

即ち、第1のビット線コンタクト部BC1を埋め込むためのコンタクトホールも、フローティングゲート電極3の高さ(膜厚)に基づいたアスペクト比で形成される。

即ち、第1のビット線コンタクト部BC1を埋め込むためのコンタクトホールも、フローティングゲート電極3の高さ(膜厚)に基づいたアスペクト比で形成される。

それゆえ、そのコンタクトホールのアスペクト比を低減でき、また、ドレイン拡散層6のチャネル長方向のサイズを縮小できる。

よって、ソース及びドレイン拡散層のサイズを縮小できる。それにより、メモリセルトランジスタを微細化でき、メモリセルアレイ部のサイズを縮小できる。

(ii) 製造方法

以下、本応用例の構造の製造方法について、説明を行う。

以下、本応用例の構造の製造方法について、説明を行う。

はじめに、図5A及び図7と同様の工程で、フローティングデート電極3が、半導体基板1表面のゲート絶縁膜2上に形成される。この際、後の工程でドレイン拡散層が形成される領域のサイズは、実施例に示すサイズよりも狭くなるよう形成される。

次に、そのフローティングゲート電極3をマスクとして、ソース及びドレイン拡散層5,6が、自己整合的に半導体基板1表面に形成される。その後、スペーサ絶縁層7、ストッパ膜8、第1の絶縁層9が、順次形成される。

そして、図14に示すように、第1のソース線コンタクト部SC1及び第1のビット線コンタクト部BC1が、拡散層5,6にそれぞれ接触するように、絶縁層9内に形成されたコンタクトホールに埋め込まれる。

続いて、図9乃至図11A,11Bと同様の工程で、電極間絶縁膜10、コントロールゲート電極11が、順次形成される。さらに、バリア膜12、第2の絶縁層13が形成される。

そして、第2のソース線コンタクト部SC2、第2のビット線コンタクト部BC2が、例えば、同時工程で、絶縁層13内に形成される。その後、ソース線SL及びビット線BLが、絶縁層13上に形成され、本応用例のNOR型フラッシュメモリが完成する。

そして、第2のソース線コンタクト部SC2、第2のビット線コンタクト部BC2が、例えば、同時工程で、絶縁層13内に形成される。その後、ソース線SL及びビット線BLが、絶縁層13上に形成され、本応用例のNOR型フラッシュメモリが完成する。

以上の製造工程で作製されたメモリセルトランジスタは、フローティングゲート電極3の高さに基づいたアスペクト比で、拡散層に接触するコンタクト部を形成できる。

よって、ソース及びドレイン拡散層のサイズを縮小でき、メモリセルトランジスタを微細でき、メモリセルアレイ部のサイズを縮小できる。

(c) 変形例

上述のスペーサ絶縁層7は、コンタクト部とゲート電極間のショートマージンが確保できる場合には、形成せずとも良い。

上述のスペーサ絶縁層7は、コンタクト部とゲート電極間のショートマージンが確保できる場合には、形成せずとも良い。

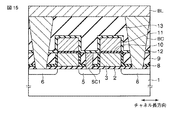

それゆえ、本発明の実施形態のメモリセルは、図15に示す構造でもよい。

この場合、チャネル長方向に隣接する2つのフローティングゲート電極3間は、第1の絶縁層9のみで埋め込まれる。そして、その絶縁層9内に、第1のソース線コンタクト部SC1が、ソース拡散層5に接触するように埋め込まれる。

よって、図15に示す構造においても、ソース拡散層5のサイズを縮小でき、メモリセルトランジスタを微細化できる。

また、スペーサ絶縁層を形成しないことにより、製造工程を削減でき、製造コストを低減できる。

尚、本変形例は、応用例に示す構造にも適用できる。

(2) 第2の実施形態

上述のように、第1の実施形態のNOR型フラッシュメモリは、ソース線コンタクトを形成するためのアスペクト比を低減させるため、フローティングゲート電極とコントロールゲート電極とが、それぞれ異なる工程で形成される。

上述のように、第1の実施形態のNOR型フラッシュメモリは、ソース線コンタクトを形成するためのアスペクト比を低減させるため、フローティングゲート電極とコントロールゲート電極とが、それぞれ異なる工程で形成される。

それゆえ、フローティングゲート電極とコントロールゲート電極が、同時にゲート加工されて形成される場合とは異なり、それらのゲート電極間のアライメントがずれる可能性がある。

本実施の形態においては、第1の実施形態の効果に加え、コントロールゲート電極とフローティングゲート電極間のアライメントのずれを許容できるメモリセルトランジスタの構造及び製造方法について説明する。

尚、第1の実施形態と同一部材には、同一の符号を付し、詳細な説明は省略する。

(a) 構造

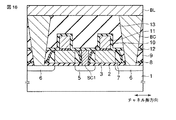

図16は、本実施形態のチャネル長方向の構造を示す断面図である。

図16は、本実施形態のチャネル長方向の構造を示す断面図である。

本実施形態において、コントロールゲート電極11のチャネル長方向の幅が、フローティングゲート電極3のチャネル長方向の幅よりも狭いことを特徴とする。

それにより、コントロールゲート電極11とフローティングゲート電極3間のアライメントのずれを許容できる。

また、そのような積層ゲート電極の構造とした場合においても、第1のソース線コンタクト部SC1の構造に対して、影響を及ぼすことはない。よって、ソース拡散層5のサイズを縮小することができる。

さらに、ビット線コンタクト部BCとコントロールゲート電極11とのショートを防止することもできる。

よって、本実施形態において、メモリセルトランジスタを微細化でき、メモリセルアレイ部のサイズを縮小できる。また、積層されたゲート電極間のアライメントのずれを許容でき、NOR型フラッシュメモリの製造歩留りを向上できる。

(b) 製造方法

以下、本実施形態の製造方法について説明を行う。

以下、本実施形態の製造方法について説明を行う。

はじめに、第1の実施形態の図5A乃至図9と同様の工程を用いて、フローティングゲート電極3、ドレイン及びソース拡散層5,6が、順次形成される。続いて、スペーサ絶縁層7、ストッパ膜8及び第1の絶縁層9が、順次形成される。

その後、第1のソース線コンタクト部SC1が、ソース拡散層5に接触するように、絶縁層9内に埋め込まれる。さらに、電極間絶縁膜となる、例えば、ONO膜10A及びコントロールゲート電極となるポリシリコン膜11Aが、堆積される。

その後、第1のソース線コンタクト部SC1が、ソース拡散層5に接触するように、絶縁層9内に埋め込まれる。さらに、電極間絶縁膜となる、例えば、ONO膜10A及びコントロールゲート電極となるポリシリコン膜11Aが、堆積される。

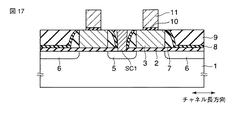

次に、コントロールゲート電極を形成するためのパターニングが、ポリシリコン膜11Aに施される。そのパターンは、コントロールゲート電極のチャネル長方向のサイズが、フローティングゲート電極3のチャネル長方向のサイズよりも狭くなるようなパターンである。

そのパターンに基づいて、例えば、RIE法によりエッチングを施すと、図17に示すように、コントロールゲート電極11のチャネル長方向のサイズが、フローティングゲート電極3のチャネル長方向のサイズよりも狭くなるように、形成される。

そのパターンに基づいて、例えば、RIE法によりエッチングを施すと、図17に示すように、コントロールゲート電極11のチャネル長方向のサイズが、フローティングゲート電極3のチャネル長方向のサイズよりも狭くなるように、形成される。

続いて、図16に示すように、図10、図11A及び図11Bに示す工程と同様の工程で、バリア膜12及び第2の絶縁層13が、形成される。さらに、ビット線コンタクト部BCが、絶縁層9,13内に形成される。また、第2のソース線コンタクト部SC2が、第1のソース線コンタクト部SC1に接触するように、絶縁層13内に埋め込まれる。その後、ソース線SL及びビット線BLが、絶縁層13上に形成され、本実施の形態のNOR型フラッシュメモリが完成する。

以上の製造工程で作製されたメモリセルトランジスタは、フローティングゲート電極の高さに基づいたアスペクト比で、拡散層に接触するコンタクト部を形成できる。

よって、拡散層のサイズを縮小でき、メモリセルトランジスタの微細化、並びに、メモリセルアレイ部のサイズを縮小できる。

また、コントロールゲート電極のチャネル長方向のサイズを、フローティングゲート電極のチャネル長方向のサイズより狭くすることで、積層された2つのゲート電極間のアライメントのずれを許容できる。

尚、本実施形態の積層ゲート電極の構造及びその製造方法は、第1の実施形態の応用例及び変形例にも適用できる。

(3) 第3の実施形態

第2の実施形態でも述べたように、本発明の実施形態においては、フローティングゲート電極3と、コントロールゲート電極が、それぞれ異なる工程でゲート加工されるため、それらの間でアライメントのずれが生じる。

第2の実施形態でも述べたように、本発明の実施形態においては、フローティングゲート電極3と、コントロールゲート電極が、それぞれ異なる工程でゲート加工されるため、それらの間でアライメントのずれが生じる。

第2の実施形態においては、コントロールゲート電極をゲート加工する際に、コントロールゲート電極のチャネル長方向のサイズが、フローティングゲート電極のチャネル長方向のサイズより狭くなるように加工を行い、アライメントのずれを許容する構造及び製造方法について述べた。

本実施形態においては、上記のアライメントのずれを自己整合的に防止できる構造及び製造方法について説明する。

尚、第1及び第2実施形態と同一部材に関しては、同一符号を付し、詳細な説明は、省略する。

(a) 構造

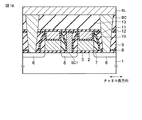

図18は、本実施形態のNOR型フラッシュメモリのチャネル長方向の断面を示す図である。

図18は、本実施形態のNOR型フラッシュメモリのチャネル長方向の断面を示す図である。

図18に示すように、コントロールゲート電極11は、スペーサ絶縁層7側面とフローティングゲート電極3上面からなる凹部に、自己整合的に埋め込まれた構造となっている。

それゆえ、フローティングゲート電極3とコントロールゲート電極11との間に、あわせずれが生じることはない。

そして、第1のソース線コンタクト部SC1の上端は、電極間絶縁膜10により覆われる。即ち、ソース拡散層5領域上に電極間絶縁膜が配置される構造となっている。また、第1のソース線コンタクト部SC1の上端は、ビット線コンタクト部BCの上端よりも低い位置にある。

コントロールゲート電極11は、CMPにより、凹部に自己整合的に埋め込まれる。この際、コントロールゲート電極11の上端とソース線コンタクト部SC1上の電極間絶縁膜10の上端は、完全に一致することが望ましい。しかし、通常、CMPによる表面研磨においては、ディッシング現象が生じ、それにより、コントロールゲート電極11の上端は、ソース線コンタクト部SC1上の電極間絶縁膜10の上端以下となる場合も生じる。

尚、図18は、コントロールゲート電極11の上端とソース線コンタクト部SC1上の電極間絶縁膜10の上端が一致した場合を図示している。

尚、図18は、コントロールゲート電極11の上端とソース線コンタクト部SC1上の電極間絶縁膜10の上端が一致した場合を図示している。

また、本実施形態においては、図18に示すように、コントロールゲート電極11が埋め込まれる凹部は、スペーサ絶縁層7側面とフローティングゲート電極3上面により形成されるが、その構造に限定されない。例えば、図15に示したように、スペーサ絶縁層が形成されない場合には、第1の絶縁層9側面とフローティングゲート電極3上面からなる凹部でも良い。

以上により、本実施の形態において、ソース拡散層のサイズを縮小できる。それゆえ、メモリセルトランジスタを微細化でき、メモリセルアレイ部のサイズを縮小できる。

また、積層される2つのゲート電極のアライメントのずれを、自己整合的な手法により防止でき、NOR型フラッシュメモリの製造歩留りを向上できる。

尚、本実施形態の構造は、第1の実施形態の応用例及び変形例に関しても、適用できる。

(b) 製造方法

以下、本実施形態の製造方法について説明を行う。

以下、本実施形態の製造方法について説明を行う。

はじめに、図5A乃至図6と同一の工程により、ゲート絶縁膜2、フローティングゲート電極3、ソース及びドレイン拡散層5,6が、順次形成される。この際、フローティングゲート電極3は、所望の膜厚より厚く形成される。

次に、図7及び図8と同様の工程により、スペーサ絶縁層7、ストッパ膜8、第1の絶縁層9が、順次形成される。そして、第1のソース線コンタクト部SC1が、ソース拡散層5に接触するように、第1の絶縁層9内に形成されたコンタクトホールに埋め込まれる。

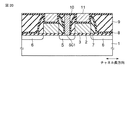

その後、図19に示すように、フローティングゲート電極3が、例えば、RIEにより、選択的にエッチングされる。それにより、フローティングゲート電極3上面とスペーサ絶縁層7側面からなる凹部Yが、チャネル領域上に形成される。尚、このエッチング工程において、フローティングゲート電極3は、例えば、所望の膜厚にされる。

その後、図19に示すように、フローティングゲート電極3が、例えば、RIEにより、選択的にエッチングされる。それにより、フローティングゲート電極3上面とスペーサ絶縁層7側面からなる凹部Yが、チャネル領域上に形成される。尚、このエッチング工程において、フローティングゲート電極3は、例えば、所望の膜厚にされる。

続いて、図20に示すように、電極間絶縁膜10が、フローティングゲート電極3上及び第1のソース線コンタクト部SC1上に形成される。そして、例えば、ポリシリコンが、例えば、CVD及びCMPにより、電極間絶縁膜の上端と一致するように、凹部に埋め込まれる。それにより、コントロールゲート電極11が、電極間絶縁膜10を介して、フローティングゲート電極3上に、自己整合的に形成される。

その後、図10、図11A及び図11Bと同様の工程により、バリア膜12、第2の絶縁層13が順次形成される。さらに、第2のソース線コンタクト部SC2、ビット線コンタクト部BC、ソース線SL、ビット線BLが形成される。それにより、図18に示す、本実施形態のNOR型フラッシュメモリが完成する。

尚、本実施形態においては、バリア膜12は形成せずともよい。

以上の製造工程で作製されたメモリセルトランジスタは、フローティングゲート電極の高さに基づいたアスペクト比で、拡散層に接触するコンタクト部を形成できる。

よって、ソース拡散層のサイズを縮小でき、メモリセルトランジスタの微細化、並びに、メモリセルアレイ部のサイズを縮小できる。

また、上記の製造方法は、コントロールゲート電極とフローティングゲート電極のアライメントのずれを、自己整合的な手法により防止できる。それゆえ、NOR型フラッシュメモリの製造歩留りを向上できる。

尚、本実施形態の製造方法は、第1の実施形態の応用例及び変形例に関しても、適用できる。

3. その他

本発明の例は、メモリセルトランジスタの微細化及びメモリセルアレイ部のサイズの縮小ができる。

本発明の例は、メモリセルトランジスタの微細化及びメモリセルアレイ部のサイズの縮小ができる。

本発明の例は、上述の実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で、各構成要素を変形して具体化できる。また、上述の実施の形態に開示されている複数の構成要素の適宜な組み合せにより種々の発明を構成できる。例えば、上述の実施の形態に開示される全構成要素から幾つかの構成要素を削除してもよいし、異なる実施の形態の構成要素を適宜組み合わせてもよい。

1:半導体基板、2:ゲート絶縁膜、3:フローティングゲート電極、4:素子分離絶縁層、5:ソース拡散層、6:ドレイン拡散層、7:スペーサ絶縁層、8:ストッパ膜(SiN膜)、9:第1の絶縁層、10:電極間絶縁膜、11:コントロールゲート電極、12:バリア膜、13:第2の絶縁層、SC1:第1のソース線コンタクト部、SC2:第2のソース線コンタクト部、BC:ビット線コンタクト部、BC1:第1のビット線コンタクト部、BC2:第2のビット線コンタクト部、SL:ソース線、BL:ビット線、X:コンタクトホール、Y:凹部、AA:アクティブ領域、STI:素子分離領域、SA:シャント領域。

Claims (5)

- 半導体基板表面に形成されるソース及びドレイン拡散層と、前記ソース及びドレイン拡散層間のチャネル領域上に形成されるゲート絶縁膜と、前記ゲート絶縁膜上に形成されるフローティングゲート電極と、前記フローティングゲート電極上に、電極間絶縁膜を介して形成されるコントロールゲート電極と、前記ソース拡散層に接触するソース線コンタクト部とを具備し、前記ソース線コンタクト部の上端は、前記コントロールゲート電極の下端より低い位置にあることを特徴とする不揮発性半導体メモリ。

- 半導体基板表面に形成されるソース及びドレイン拡散層と、前記ソース及びドレイン拡散層間のチャネル領域上に形成されるゲート絶縁膜と、前記ゲート絶縁膜上に形成されるフローティングゲート電極と、前記ソース拡散層に接触するソース線コンタクト部と、前記フローティングゲート電極上面及び前記ソース線コンタクト部上面を覆う電極間絶縁膜と、前記電極間絶縁膜を介して、前記フローティングゲート電極上に形成されるコントロールゲート電極とを具備し、前記コントロールゲート電極の上端は、前記ソース線コンタクト部上面を覆う電極間絶縁膜上端以下の位置にあることを特徴とする不揮発性半導体メモリ。

- 半導体基板表面上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上にフローティングゲート電極を形成する工程と、前記フローティングゲート電極をマスクとして、ソース及びドレイン拡散層を形成する工程と、前記フローティングゲート電極の上端と一致するように、前記拡散層上に絶縁層を形成する工程と、前記絶縁層内に前記拡散層の表面が露出するようにコンタクトホールを形成する工程と、前記拡散層と接触するようにソース線コンタクト部を前記コンタクトホールに埋め込む工程と、前記フローティングゲート電極上に、電極間絶縁膜を形成する工程と、前記電極間絶縁膜上に、コントロールゲート電極を形成する工程とを具備する不揮発性半導体メモリの製造方法。

- 前記コントロールゲート電極は、前記電極間絶縁膜上に、コントロールゲート電極材を形成する工程と、前記コントロールゲート電極材を、前記フローティングゲート電極のチャネル長方向のサイズよりも狭くなるように、コントロールゲート電極のゲート加工を行う工程とにより形成されることを特徴とする請求項3に記載の不揮発性半導体メモリの製造方法。

- 前記コントロールゲート電極は、前記ソース線コンタクト部を形成した後に、前記フローティングゲート電極の上端が、前記絶縁層の上端より低い位置になるように、前記フローティングゲート電極の上部をエッチングして、凹部を形成する工程と、前記凹部内及び前記ソース線コンタクト部上面を覆うように前記電極間絶縁膜を形成する工程と、前記凹部内にコントロールゲート電極材を自己整合的に埋め込む工程とにより形成されることを特徴とする請求項3に記載の不揮発性半導体メモリの製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007042408A JP2008205379A (ja) | 2007-02-22 | 2007-02-22 | 不揮発性半導体メモリ及びその製造方法 |

| US12/035,829 US20090035907A1 (en) | 2007-02-22 | 2008-02-22 | Method of forming stacked gate structure for semiconductor memory |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007042408A JP2008205379A (ja) | 2007-02-22 | 2007-02-22 | 不揮発性半導体メモリ及びその製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2008205379A true JP2008205379A (ja) | 2008-09-04 |

Family

ID=39782518

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007042408A Pending JP2008205379A (ja) | 2007-02-22 | 2007-02-22 | 不揮発性半導体メモリ及びその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US20090035907A1 (ja) |

| JP (1) | JP2008205379A (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012514346A (ja) * | 2008-12-31 | 2012-06-21 | インテル コーポレイション | 集積されたhigh−k誘電体と金属ベースの制御ゲートを有するフラッシュセル |

| JP2018526821A (ja) * | 2015-08-05 | 2018-09-13 | 日本テキサス・インスツルメンツ株式会社 | 金属ゲートプロセスに基づく低コストのフラッシュメモリ製造フロー |

| JP2020141131A (ja) * | 2019-02-26 | 2020-09-03 | 華邦電子股▲ふん▼有限公司Winbond Electronics Corp. | 半導体装置及びその製造方法 |

| CN111696989A (zh) * | 2019-03-15 | 2020-09-22 | 华邦电子股份有限公司 | 存储元件及其制造方法 |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7951704B2 (en) * | 2008-05-06 | 2011-05-31 | Spansion Llc | Memory device peripheral interconnects and method of manufacturing |

| US8669597B2 (en) | 2008-05-06 | 2014-03-11 | Spansion Llc | Memory device interconnects and method of manufacturing |

| JP5175889B2 (ja) * | 2010-03-26 | 2013-04-03 | 株式会社東芝 | 不揮発性半導体記憶装置およびその製造方法 |

| CN114256337B (zh) * | 2021-12-14 | 2025-08-01 | 北京超弦存储器研究院 | 一种半导体器件及其制造方法 |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100356773B1 (ko) * | 2000-02-11 | 2002-10-18 | 삼성전자 주식회사 | 플래쉬 메모리 장치 및 그 형성 방법 |

-

2007

- 2007-02-22 JP JP2007042408A patent/JP2008205379A/ja active Pending

-

2008

- 2008-02-22 US US12/035,829 patent/US20090035907A1/en not_active Abandoned

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012514346A (ja) * | 2008-12-31 | 2012-06-21 | インテル コーポレイション | 集積されたhigh−k誘電体と金属ベースの制御ゲートを有するフラッシュセル |

| EP2382665A4 (en) * | 2008-12-31 | 2014-12-31 | Intel Corp | FLASH MEMORY CELL WITH INTEGRATED HIGH CONSTANT K DIELECTRIC AND METAL BASED CONTROL GRID |

| JP2018526821A (ja) * | 2015-08-05 | 2018-09-13 | 日本テキサス・インスツルメンツ株式会社 | 金属ゲートプロセスに基づく低コストのフラッシュメモリ製造フロー |

| JP7021821B2 (ja) | 2015-08-05 | 2022-02-17 | テキサス インスツルメンツ インコーポレイテッド | 金属ゲートプロセスに基づく低コストのフラッシュメモリ製造フロー |

| JP2020141131A (ja) * | 2019-02-26 | 2020-09-03 | 華邦電子股▲ふん▼有限公司Winbond Electronics Corp. | 半導体装置及びその製造方法 |

| US11257833B2 (en) | 2019-02-26 | 2022-02-22 | Winbond Electronics Corp. | Memory device and manufacturing method thereof |

| CN111696989A (zh) * | 2019-03-15 | 2020-09-22 | 华邦电子股份有限公司 | 存储元件及其制造方法 |

| CN111696989B (zh) * | 2019-03-15 | 2023-04-18 | 华邦电子股份有限公司 | 存储元件及其制造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20090035907A1 (en) | 2009-02-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100681378B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| US8895400B2 (en) | Methods of fabricating semiconductor devices having buried word line interconnects | |

| CN101471379B (zh) | 半导体器件及其制造工艺 | |

| US11251188B2 (en) | Semiconductor memory device and a method of fabricating the same | |

| KR20080026509A (ko) | 반도체 장치 및 그 제조 방법 | |

| JP2008205379A (ja) | 不揮発性半導体メモリ及びその製造方法 | |

| US7511328B2 (en) | Semiconductor device having raised cell landing pad and method of fabricating the same | |

| JP2006286720A (ja) | 半導体装置およびその製造方法 | |

| US7928494B2 (en) | Semiconductor device | |

| US7557401B2 (en) | Semiconductor device and method of manufacturing the same | |

| KR101386434B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| JP2010040538A (ja) | 半導体装置の製造方法 | |

| JP2004152878A (ja) | 半導体記憶装置及びその製造方法 | |

| JP4155587B2 (ja) | 半導体装置の製造方法 | |

| JP2007227900A (ja) | 非揮発性メモリ素子の製造方法 | |

| JP2008192891A (ja) | 半導体装置及びその製造方法 | |

| JP2009049138A (ja) | 半導体装置の製造方法 | |

| JP2010080602A (ja) | 半導体装置およびその製造方法 | |

| KR100660552B1 (ko) | 반도체 장치의 배선 구조체 및 그 형성 방법 | |

| US7897457B2 (en) | Method for manufacturing a nonvolatile semiconductor memory device | |

| JP2005294518A (ja) | 半導体装置およびその製造方法 | |

| US20060081909A1 (en) | Semiconductor device and manufacturing method therefor | |

| JP2008192890A (ja) | 半導体装置およびその製造方法 | |

| JP2010034291A (ja) | 不揮発性半導体記憶装置の製造方法 | |

| JP2008103561A (ja) | 半導体装置及びその製造方法 |