JP4663094B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4663094B2 JP4663094B2 JP2000314369A JP2000314369A JP4663094B2 JP 4663094 B2 JP4663094 B2 JP 4663094B2 JP 2000314369 A JP2000314369 A JP 2000314369A JP 2000314369 A JP2000314369 A JP 2000314369A JP 4663094 B2 JP4663094 B2 JP 4663094B2

- Authority

- JP

- Japan

- Prior art keywords

- switch

- transistor

- electrically connected

- potential

- operational amplifier

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5628—Programming or writing circuits; Data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5642—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5671—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge trapping in an insulator

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0408—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors

- G11C16/0433—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing a single floating gate transistor and one or more separate select transistors

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

- G11C16/14—Circuits for erasing electrically, e.g. erase voltage switching circuits

- G11C16/16—Circuits for erasing electrically, e.g. erase voltage switching circuits for erasing blocks, e.g. arrays, words, groups

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/32—Timing circuits

Description

【発明が属する技術分野】

本発明は半導体不揮発性メモリに関する。特に、電気的書き込み及び消去可能な半導体不揮発性メモリ(EEPROMまたはElectrically Erasable and Programmable Read Only Memoryともいう)に関する。なお、本発明は、特に多値技術を用いた半導体不揮発性メモリに対して有効である。また、本発明は半導体不揮発性メモリを具備する半導体装置に関する。

【0002】

本明細書において、電気的書き込み及び消去可能な半導体不揮発性メモリ(EEPROM)とは、文字通り、電気的な書き込みおよび電気的な消去が可能な半導体不揮発性メモリの全体を指し、例えばフル機能EEPROM、或はフラッシュメモリをその範疇に含む。また、特に断りのない場合、不揮発性メモリおよび半導体不揮発性メモリはEEPROMと同義で用いる。また、半導体装置とは、半導体特性を利用することで機能する装置全般を指し、例えば、マイクロプロセッサ、液晶表示装置および発光装置に代表される電気光学装置、ならびにマイクロプロセッサあるいは電気光学装置を搭載した電子機器をその範疇に含む。

【0003】

【従来の技術】

近年、電気的書き込み及び消去可能な半導体不揮発性メモリ(EEPROM)、特にフラッシュメモリが磁気ディスクあるいはDRAMに置き代わる有力なメモリの候補として注目を浴びている。なかでも、個々のメモリ素子が3値以上データを記憶する、いわゆる多値の不揮発性メモリが大容量メモリとして注目されている。

【0004】

不揮発性メモリは、その回路構成や動作方法の違いによって、NOR型、NAND型、AND型、或はDINOR型といった種類に分けられる。また、不揮発性メモリを構成するメモリ素子としては、フローティングゲートを有するメモリトランジスタ、クラスタ層を有するメモリトランジスタ、MNOS(Metal-Nitride-Oxide-Semiconductor)構造あるいはMONOS(Metal-Oxide-Nitride-Oxide-Semiconductor)構造のメモリトランジスタ等が知られている。

【0005】

従来の不揮発性メモリは、代表的な書き込み動作として、ホットエレクトロン注入の方法(HE注入方式と呼ぶ)と、FNトンネル電流による電荷注入の方法(FN電流方式と呼ぶ)とが挙げられる。HE注入方式では、メモリトランジスタに高いコントロールゲート電圧と高いドレイン電圧を印加して、インパクトイオン化を起こし、発生したホットエレクトロンをゲート電極側に引き込むことによってメモリトランジスタに電荷を注入する。一方、FN電流方式では、コントロールゲート電極と基板との間に高電圧を印加しFNトンネル電流を流すことによって、メモリトランジスタに電荷を注入する。

【0006】

いずれの場合においても、書き込み後のしきい値電圧が所定の範囲内にあることを確かめるために、通常はベリファイ書き込みが行われる。特に、多値の不揮発性メモリにおいては、書き込み後のしきい値電圧を高精度に制御する必要が有るためにベリファイ書き込みが不可欠である。ベリファイ書き込みは、少量の電荷注入としきい値電圧を確認するための読み出しとを交互に行う方法である。そして、書き込み後のしきい値電圧が所定の範囲内に納まるまでこの動作が繰り返される。

【0007】

【発明が解決しようとする課題】

上述した電荷注入の方法は、電荷注入量を精度よく制御することが難しいという問題があった。これは、メモリトランジスタに同じ動作電圧を印加した場合でも、メモリトランジスタの電荷蓄積量、つまりしきい値電圧が異なると、電荷注入速度が異なるためである。

【0008】

そのため、しきい値電圧の異なるメモリトランジスタはもちろん、同一のメモリトランジスタであっても時間と共に電荷注入速度が変化する。例えば、電子を注入する場合、しきい値電圧は増加し、チャネル領域からみた実行的なゲート電圧が減少するので、電荷注入速度は減少する。

【0009】

さらに、トンネル酸化膜の膜質のばらつきなどの要因によって電荷注入速度がばらつくと、書き込み前のメモリトランジスタのしきい値電圧が等しかったとしても、徐々に電荷蓄積量に差が生じることになる。そして、しきい値電圧に差が生じると、さらに電荷注入量がばらつくという悪循環が生じる。

【0010】

ベリファイ書き込みは、このような問題を解決する方法の一つである。ベリファイ書き込みでは、少量の電荷を注入する毎にしきい値電圧の確認を行うので、電荷注入量を高精度に制御する必要がない。しかしながら、ベリファイ書き込みは、電荷注入の動作を分割し、その間に読み出し動作を行うために、本質的に時間がかかるという問題点がある。

【0011】

なお、ベリファイ書き込みにおいても、電荷注入量を精度よく制御することは重要である。電荷注入量を高精度に制御することによって、電荷注入の動作の分割を少なくすることができ、ベリファイ書き込み時間を短縮することができる。

【0012】

本発明は、上記問題点を鑑みてなされたものである。本発明では、電荷注入量を高精度に制御することができるな書き込み動作を行う不揮発性メモリを提供することを課題とする。そして、ベリファイ書き込み時間の短縮、さらにはベリファイ方式を用いない書き込み方式によって、書き込み時間の大幅な短縮を実現する不揮発性メモリを提供することを課題とする。またこのような不揮発性メモリを具備する半導体装置を提供することを課題とする。

【0013】

【課題を解決するための手段】

既に述べたように、従来の書き込み方法では、電荷注入速度がメモリトランジスタの電荷蓄積量、従ってしきい値電圧に依存してしまう。その結果、異なる状態のメモリトランジスタはもちろん、同一のメモリトランジスタであっても時間と共に電荷注入速度は変化し、電荷注入量の制御が難しくなっていた。

【0014】

このことは逆に、電荷注入量を高精度に制御するためには、メモリトランジスタの電荷蓄積量、つまりしきい値電圧に依存しない電荷注入速度を有する書き込み方法が有効であることを意味する。本発明者は、電荷注入速度がメモリトランジスタのしきい値電圧に依存するのは、書き込み時にメモリトランジスタのコントロールゲート電圧を直接制御するためであると考え、新たな書き込み方法として、メモリトランジスタのドレイン電圧とドレイン電流を制御する方法を考案した。

【0015】

つまり、本発明の不揮発性メモリは、メモリトランジスタのドレイン電圧とドレイン電流とを制御することによってホットエレクトロン注入方式の書き込み動作を行うことを特徴とする。この書き込み方法は、コントロールゲート電圧を直接制御するのではなく、ドレイン電流が一定となるように間接的にコントロールゲート電圧を制御することを特徴とし、電荷注入速度がしきい値電圧に依存しないことを特徴とする。

【0016】

本発明の不揮発性メモリにおける書き込み動作を理解するために、一つのメモリ素子に書き込みを行う簡単な回路を例にとって、その動作方法を説明する。説明には図1(a)若しくは(b)を用いる。

【0017】

メモリ素子としては、図26に示すような様々な素子を用いることができる(詳細は実施例3を参照)。図26(a)は、活性領域2601上に第1の絶縁膜2602と、半導体または導体のクラスタ2604によって構成されるクラスタ層2603と、第2の絶縁膜2605と、コントロールゲート電極2606とが順に積層されてなるメモリトランジスタであり、以下ではクラスタ層を有するメモリトランジスタと呼ぶ。また、図26(d)は、活性領域2616上に第1の絶縁膜2617と、半導体膜または導体膜によって構成されるフローティングゲート電極2618と、第2の絶縁膜2619と、コントロールゲート電極2620とが順に積層されてなるメモリトランジスタであり、以下、フローティングゲートを有するメモリトランジスタと呼ぶ。また、図26(b)、(c)はそれぞれMNOS構造のメモリトランジスタ及びMONOS構造のトランジスタである。

【0018】

ここでは、メモリ素子として、クラスタ層を有するメモリトランジスタ、MNOS構造のメモリトランジスタ、あるいはMONOS構造のメモリトランジスタを用いた回路図の例を図1(a)に、またフローティングゲートを有するメモリトランジスタを用いた回路図の例を図1(b)に示してある。それぞれのメモリ素子の記号が象徴するように、図1(a)に示したメモリトランジスタは電荷を蓄積する領域が空間的に離散的であることを特徴とし、図1(b)に示したメモリトランジスタは電荷を蓄積する領域が連続的であることを特徴とする。いずれの場合も、動作方法は全く同じであり、ここでは図1(a)を例にとって説明を行う。

【0019】

図1(a)に示した回路図は、メモリトランジスタ101(a)、電流量Iを供給する定電流源102、およびオペアンプ103によって構成されている。メモリトランジスタ101(a)のコントロールゲート電極にはオペアンプ103の出力が、ドレイン電極には定電流源102が接続されており、ソース電極は接地されている。また、オペアンプ103の2つの入力端子には、定電流源102と電圧Vpgmとがそれぞれ接続されている。

【0020】

図1に示した回路は負帰還の特性を有しており、オペアンプ103に入力される2つの電位は常に等しい状態で動作する。その結果、図1に示した回路図においてメモリトランジスタ101(a)は、ドレイン電圧がVpgmに等しく、またドレイン電流がIに等しい状態で動作する。

【0021】

実際に、メモリトランジスタ101(a)のドレイン電圧がVpgmより高い場合には、オペアンプ103からは正の電流が出力され、メモリトランジスタ101(a)のコントロールゲート電圧が上昇する。その結果、メモリトランジスタ101(a)のコンダクタンスが増加し、ドレイン電圧は引き下げられる。また逆に、メモリトランジスタ101(a)のドレイン電圧がVpgmより低い場合には、オペアンプ103からは負の電流が出力され、メモリトランジスタ101(a)のコントロールゲート電圧が低下する。その結果、メモリトランジスタ101(a)のコンダクタンスが減少し、ドレイン電圧は引き上げられることがわかる。

【0022】

本発明では、以上のようにメモリトランジスタのドレイン電圧とドレイン電流とを制御することによって、HE注入方式の書き込み動作を行う。なお、Vpgmを書き込み電圧、Iを書き込み電流と呼ぶ。

【0023】

上述した書き込み方法を用い、ドレイン電圧とドレイン電流とを一定とすると、メモリトランジスタのチャネル領域はフローティングゲートの電荷蓄積量に依らずに同じ状態をとる。つまり、コントロールゲート電圧はしきい値電圧のシフトと同じ量だけシフトし、チャネル領域からみた実行的なゲート電圧は常に一定に保たれた状態となる。さらに、ドレイン電圧とドレイン電流が一定であれば、一定量のホットエレクトロンが発生するため、フローティングゲートへの電荷注入速度は一定となる。

【0024】

このことは、書き込み電圧Vpgmと書き込み電流Iが一定の場合、メモリトランジスタのしきい値電圧のシフトΔVthと書き込み時間twとが、図2の曲線201に示すような直線で表されることを意味する。その結果、本発明の不揮発性メモリは、書き込み時間を制御することによって、しきい値電圧を高精度に制御することが可能となる。

【0025】

なお、図2には、従来の書き込み方法におけるしきい値電圧のシフトと書き込み時間の関係も示されている(図2の曲線202)。従来の書き込み方法において、コントロールゲート電圧を一定とした場合には、チャネル領域からみた実行的なゲート電圧が時間と共に減少するために、しきい値電圧のシフト量は減少する。このため、書き込み時間を制御することによってしきい値電圧のシフトを高精度で制御することが難しいことがわかる。

【0026】

本発明において、書き込み時の電荷注入速度は、メモリトランジスタのドレイン電圧とドレイン電流とを適切な値に設定することにより最適化することができる。本発明における書き込み方法はホットエレクトロン注入であるから、ドレイン電圧としてはホットエレクトロンが発生する程度の大きさが必要である。一方で、多量のホットエレクトロンが発生してしまうと電荷注入量の制御性が低下してしまうため、ドレイン電圧が大きすぎても好ましくない。メモリトランジスタのドレイン電圧は、メモリトランジスタのサイズにも依るが、3V以上であることが好ましく、また、線形領域に比較的近い飽和領域で動作することが好ましい。さらに、そのような領域において、書き込み電圧Vpgmと書き込み電流Iとを大きな値に設定することによって書き込み速度は向上し、逆に小さな値に設定することによって消費電流を抑えることが可能となる。書き込み電圧Vpgmと書き込み電流Iは、不揮発性メモリの用途に応じてそれぞれ最適な動作点の設定を行えば良い。

【0027】

また、上述した書き込み方法はホットエレクトロン注入の方法であるから、トンネル酸化膜によるエネルギー障壁よりも遥かに高いエネルギーを有する電子が主に関与する。そのため、トンネル酸化膜の膜質のばらつきはホットエレクトロンの注入量にほとんど影響を与えず、FNトンネル電流による電荷注入の方法と比較して、ばらつきの少ないしきい値制御が可能となる。

【0028】

本発明の不揮発性メモリは、上述した書き込み動作を用いることによって、以下のように書き込み時間の大幅な短縮が可能となる。

【0029】

まず、図3を参照する。図3は、しきい値電圧の揃ったメモリトランジスタに対して、従来の書き込みと、本発明における書き込みとをベリファイ動作無しで行った後のしきい値分布を定性的に表したものである。分布302は従来の書き込み後のしきい値電圧の分布を、分布301は本発明における書き込み後のしきい値電圧の分布を表す。また、Vtarは設定した書き込み後のしきい値電圧である。図3において、本発明における書き込み後の分布302を従来の書き込み後の分布301と比較すると、分布の中心とVtarとのずれ、および分布幅がいずれも小さくなっている(ΔV<ΔV'かつδv<δv')。

【0030】

一般に、異なる状態を表すしきい値電圧の差が、書き込み後の分布幅および中心のずれと比較して小さい場合には、一度の書き込みで全てのメモリセルを所定の状態にすることができないため、ベリファイ書き込みが必要となる。また、逆にしきい値電圧の差が書き込み後の分布幅および中心のずれより大きい場合には、一度の書き込み動作で書き込みを行うことができる。なお、ベリファイ書き込みとは、書き込みを一度で行うのではなく、少量の書き込みとしきい値を確認するための読み出しとを交互に行う方法を言う。そして、所定のしきい値に達するまでこの動作を繰り返す。

【0031】

従来の書き込み方法は、図3に示したように書き込み後の分布幅δv'および中心のずれΔV'が大きいために、通常、ベリファイ書き込みの方法が用いられる。

【0032】

本発明における書き込み方法を用いた場合には、図3に示したように書き込み後の分布幅δvおよび中心のずれΔVが小さいために、従来の書き込み方法ではベリファイ動作が必要であるようなしきい値電圧の差であっても、ベリファイ動作を行わない書き込み動作を行うことが可能となる。具体的には、異なる状態間のしきい値電圧の差が本発明における書き込み後のしきい値電圧の分布幅δv及び中心のずれΔVより大きい場合にベリファイ動作を行わない書き込み動作が可能となる。

【0033】

また、多値の不揮発性メモリのように、異なる状態を表すしきい値電圧の差が小さい場合には、本発明による書き込み方法を用いる場合においてもベリファイ動作が必要となる。この場合には、書き込み動作をベリファイ動作を行わない第1の書き込み動作とベリファイ動作を行う第2の書き込み動作によって構成するとよい。具体的には、まず第1の書き込み動作によって最終的なしきい値電圧よりもわずかに低い(δvまたはΔV程度)状態への書き込みを行い、次に残ったしきい値電圧の不足分(δvまたはΔV程度)についてベリファイ書き込みを行う。第2の書き込み動作で書き込む量はごく僅かであるため、従来のベリファイ書込と比較してベリファイ回数を大幅に減らすことができる。

【0034】

このように、本発明における書き込み方法を用いる場合、ベリファイを行わない書き込み動作はもちろん、ベリファイを行う書き込み動作においても、ベリファイ回数を減らすことができ、書き込み時間を大幅に短縮することが可能となる。

【0035】

また、従来の書き込み方法では、図2に示すように、しきい値電圧が増加すると電荷注入速度が低下し、書き込み動作が遅くなるが、本発明における書き込み方法では、高いしきい値電圧においても電荷注入速度は一定であり、高速な書き込み動作が可能となる。

【0036】

以下に、本発明の構成を示す。

【0037】

活性領域とコントロールゲート電極との間に電荷蓄積領域を有するメモリ素子によって構成される電気的書き込みおよび消去可能な不揮発性メモリにおいて、前記メモリ素子を流れる電流量と該メモリ素子のドレイン電圧とを制御することによって前記電荷蓄積領域への電荷注入量を制御することを特徴とする不揮発性メモリが提供される。

【0038】

活性領域とコントロールゲート電極との間に電荷蓄積領域を有するメモリ素子によって構成される電気的書き込みおよび消去可能な不揮発性メモリにおいて、前記電荷蓄積領域への電荷注入は、前記メモリ素子を流れる電流量と該メモリ素子のドレイン電圧とを一定とすることによって行い、前記メモリ素子に電流が流れる時間を制御することによって前記電荷蓄積領域への電荷注入量を制御することを特徴とする不揮発性メモリが提供される。

【0039】

複数のメモリセルがマトリクス状に配置されたメモリセルと、書き込み回路とを有する電気的書き込みおよび消去可能な不揮発性メモリであって、前記複数のメモリセルはそれぞれメモリ素子と選択トランジスタとを有し、前記メモリ素子は活性領域とコントロールゲート電極との間に電荷蓄積領域を有し、前記書き込み回路は、前記メモリ素子を流れる電流量と前記メモリ素子のドレイン電圧とを制御することによって書き込み動作を行うことを特徴とする不揮発性メモリが提供される。

【0040】

複数のメモリセルがマトリクス状に配置されたメモリセルと、書き込み回路とを有する電気的書き込みおよび消去可能な不揮発性メモリであって、前記複数のメモリセルはそれぞれメモリ素子と選択トランジスタとを有し、前記メモリ素子は活性領域とコントロールゲート電極との間に電荷蓄積領域を有し、前記書き込み回路は、前記メモリ素子を流れる電流量と前記メモリ素子のドレイン電圧とを一定に保つ機能を有し、前記書き込み回路は、前記メモリ素子を流れる電流量と前記メモリ素子のドレイン電圧とを一定に保つ時間を制御することによって書き込み動作を行うことを特徴とする不揮発性メモリが提供される。

【0041】

複数のメモリセルがマトリクス状に配置されたメモリセルと、書き込み回路とを有する電気的書き込みおよび消去可能な不揮発性メモリであって、前記複数のメモリセルはそれぞれメモリ素子と選択トランジスタとを有し、前記メモリ素子は活性領域とコントロールゲート電極との間に電荷蓄積領域を有し、前記メモリ素子は、2値以上であるk値の状態を、しきい値電圧Vth0を有する消去状態、及び前記消去状態よりも高い(k−1)個の異なるしきい値電圧Vth1、Vth2、〜、Vth(k−1)を有する状態によって記憶し、前記書き込み回路は、前記メモリ素子を流れる電流量と前記メモリ素子のドレイン電圧とを一定に保つ機能を有し、前記書き込み回路は、前記メモリ素子を流れる電流量と前記メモリ素子のドレイン電圧とを一定に保つ書き込み時間を制御することによって書き込み動作を行い、前記消去状態から前記しきい値電圧Vth1、Vth2、〜、Vth(k−1)を有する状態への書き込み時間tw1、tw2、〜、tw(k−1)の比は、tw1:tw2:〜:tw(k−1)=(Vth1−Vth0):(Vth2−Vth0):〜:(Vth(k−1)−Vth0)であることを特徴とする不揮発性メモリが提供される。

【0042】

前記メモリ素子は多値データを記憶してもよい。

【0043】

前記不揮発性メモリは前記メモリ素子のゲート電圧を読み出すことによって読み出し動作を行ってもよい。

【0044】

前記不揮発性メモリの書き込み動作では、ベリファイ動作を行わなくてもよい。

【0045】

前記不揮発性メモリの書き込み動作は第1の書き込み動作と第2の書き込み動作からなり、前記第1の書き込み動作ではベリファイ動作を行わず、前記第2の書き込み動作ではベリファイ動作を行なってもよい。

【0046】

前記不揮発性メモリを構成するメモリ素子は、活性領域上に第1の絶縁膜と、半導体膜または導体膜によって構成されるフローティングゲート電極と、第2の絶縁膜と、コントロールゲート電極とが順に積層されてなるメモリトランジスタであってもよい。

【0047】

前記不揮発性メモリを構成するメモリ素子は、活性領域上に第1の絶縁膜と、半導体または導体からなるクラスタを電荷の捕獲中心として絶縁物内部に有するクラスタ層と、第2の絶縁膜と、コントロールゲート電極とが順に積層されてなるメモリトランジスタであってもよい。

【0048】

前記不揮発性メモリを構成するメモリ素子はMNOS構造またはMONOS構造のメモリトランジスタであってもよい。

【0049】

前記不揮発性メモリを記録媒体として利用することを特徴とする半導体装置が提供される。

【0050】

前記半導体装置として、マイクロプロセッサが提供される。

【0051】

前記半導体装置として、ディスプレイ、ビデオカメラ、頭部取り付け型のディスプレイ、DVDプレーヤー、ヘッドマウントディスプレイ、パーソナルコンピュータ、携帯電話、カーオーディオが提供される。

【0052】

【発明の実施の形態】

本実施の形態では、上述した書き込み動作を行う不揮発性メモリの回路構成と動作方法について説明を行う。なお、ここでは、簡単のため2値の不揮発性メモリの場合について、またベリファイ動作を行わない書き込み方法について述べるが、多値の不揮発性メモリに対しても、またベリファイ書き込みを行う場合においても本実施の形態を適用することは容易である。

【0053】

図4には、m行n列(m、nはそれぞれ1以上の整数)のメモリセルアレイを有する本発明の不揮発性メモリの回路図の一例を示す。図4に示した不揮発性メモリは、メモリセルアレイ401、Xアドレスデコーダ402、Yアドレスデコーダ403、制御回路404(1)〜404(n)、読み出し・書き込み回路405、および他の周辺回路(図示せず)によって構成される。他の周辺回路には、アドレスバッファ回路、電源発生回路、昇圧回路、電源制御回路、その他の制御回路、等が含まれ、必要に応じて設けられる。

【0054】

なお、本明細書において、書き込み回路とは書き込み動作に関与する回路全体を指すが、書き込み動作に関与する一部分だけを取り出して書き込み回路と呼ぶ場合もある。例えば、図4に示した不揮発性メモリの回路図において、書き込み回路は、書込・読出回路405と制御回路404とを含む書き込み動作に関与する回路全体を指すが、その一部分である書込・読出回路405だけを指す場合もある。また、読み出し回路に関しても同様であり、読み出し回路とは、読み出し動作に関与する回路全体を指すが、その一部分だけを取り出して読み出し回路と呼ぶ場合もある。いずれを指すか明確ではない場合には、動作全体に関与する広い意味での書き込み回路および読み出し回路を指すものとする。

【0055】

本実施の形態の不揮発性メモリは、各メモリセルがメモリトランジスタMTr及び選択トランジスタSTrによって構成される。メモリトランジスタMTrはフローティングゲートを有するメモリトランジスタ(実施例3参照)であり、選択トランジスタSTrは通常のトランジスタである。なお、メモリトランジスタMTrとしては、クラスタ層を有するメモリトランジスタ、MNOS構造またはMONOS構造のメモリトランジスタのような電荷蓄積領域が空間的に離散的であるようなメモリ素子を用いることもできる(実施例3)。各メモリセルが1ビットのデータを記憶する場合には、本実施の形態の不揮発性メモリはm×nビットの記憶容量を有することになる。

【0056】

図4において、メモリセル(i,j)(1≦i≦m、1≦j≦n)は、選択線SLi、ワード線WLj、ビット線BLj及び共通ソース線SCと接続されている。具体的には、メモリトランジスタMTrのコントロールゲート電極にワード線WLjが、ソース電極に共通ソース線SCが接続されており、また、選択トランジスタSTrのゲート電極に選択線SLiが、ドレイン電極にビット線BLiが接続されている。また、メモリセル(i,j)を構成するメモリトランジスタMTrと選択トランジスタSTrとは直列に接続されている。選択線SL1〜SLmはYアドレスでコーダ403に、また、ワード線WLjとビット線BLjは制御回路404(j)(1≦j≦n)に接続されている。また制御回路404(1)〜404(n)はXアドレスデコーダ402、及び読み出し・書き込み回路405に接続されている。

【0057】

次に、制御回路404(1)〜(n)について説明する。n個の制御回路は全て同じであるため、以下、一つを代表して制御回路404と書く。図5には、制御回路404の回路図の一例が示されており、制御回路404はオペアンプ501、定電流源502及び複数のスイッチトランジスタ503〜510によって構成されている。オペアンプ501は、入力の一方が電圧Vinと接続されており、他方が定電流源502、及びスイッチトランジスタ506と508を介してビット線BLと接続されている。また、ワード線WLは、スイッチトランジスタ505と507を介してオペアンプ501の出力、スイッチトランジスタ503と510を介して消去電圧Verase、およびスイッチトランジスタ504、509を介して読み出し電位Vout、と接続されている。

【0058】

また、スイッチトランジスタ503および504〜506はXアドレスデコーダの出力信号Vxdec(b)およびVxdec(a)にそれぞれ接続されており、スイッチトランジスタ507、508は書込・読出信号Sw/rに、スイッチトランジスタ509は読み出し信号Sreadに、またスイッチトランジスタ510は消去信号Seraseに接続されている。さらに、Xアドレスデコーダの出力信号Vxdec(a)と書込・読出信号Sw/rが、オペアンプ501に接続されている。

【0059】

オペアンプ501と定電流源502としては、例えば図6及び図7に示した回路図を用いることができる。図6(a)には、オペアンプ501の記号が書かれており、端子A、B、C、D、Eが定義されている。図6(b)には、オペアンプ501の回路図が示されている。オペアンプ501は、2つのpチャネル型トランジスタ602、603と2つのnチャネル型トランジスタ604、605、および定電流源601によって構成される差動増幅回路である。さらに、オペアンプのスイッチとして、nチャネル型のスイッチトランジスタ606、607が定電流源に直列に接続されている。また、図6(c)には、定電流源601として、負荷抵抗610と2つのnチャネル型トランジスタ608、609からなるカレントミラー型の定電流源が示されている。また図7には、図5における定電流源502の回路図として、負荷抵抗703と2つのpチャネル型トランジスタ701、702からなるカレントミラー型の定電流源が示されている。もちろん、オペアンプ501と定電流源502として、他の公知の回路を用いてもよい。

【0060】

次に、本実施の形態の不揮発性メモリの動作方法について述べる。ここでは、メモリセル(1,1)への書き込みおよび読み出しと、一列目のメモリセル(1,1)〜(1,m)の一括消去について説明する。もちろん、他のメモリセルに対しても同様の動作を行うことができる。なお、本実施の形態では、各メモリトランジスタは2値のデータを記憶し、また書き込み時にはベリファイ動作を行わない場合について述べる。

【0061】

まず、各動作が行われる前に、一列目のメモリセルがXアドレスデコーダによって選択される。具体的には、Xアドレスデコーダの出力信号によって、制御回路404(1)を構成するスイッチトランジスタ503〜506がオンとなると共に、制御回路404(2)〜404(n)を構成するスイッチトランジスタ503〜506は全てオフとなる。また、制御回路404(1)が選択されると同時に、消去信号Serase、書込・読出信号Sw/r、及び読み出し信号Sreadによって制御回路404(1)の動作モードが選択される。

【0062】

書き込み動作では、消去信号Seraseと読み出し信号Sreadに接続されるスチッチトランジスタ509、510は全てオフとなる。以下、信号線に接続される全てのスイッチトランジスタがオフとなる信号をオフの信号、信号線に接続される全てのスイッチトランジスタがオンとなる信号をオンの信号、と呼ぶ。つまり、消去信号Seraseと読み出し信号Sreadにはオフの信号が入力される。一方、書込・読出信号Sw/rにはオンの信号が入力される。その結果、メモリセル(1,1)への書き込み動作に関与する回路構成は、図8のように表すことができる。図8において、VWLはワード線の電位、VBLはビット線の電位、Vscは共通ソース線の電位、Vselは選択線の電位、Vpgmは書き込み電位、Iは定電流源が供給する電流である。図8に示した回路図は、選択トランジスタSTrを除いて図1に示した回路図と一致し、その動作原理については既に説明を行った通りである。

【0063】

書き込み時の動作電圧としては、例えば、Vsel=10V、Vsc=GND、Vpgm=6V、I=10mAとすればよい。この場合のメモリトランジスタの動作点を図9に示す。曲線901および902はそれぞれメモリトランジスタMTrおよび選択トランジスタSTrのVd−Id曲線を表し、メモリトランジスタMTrの動作点は2本の曲線の交点Pで表される。ここでは、選択トランジスタSTrのコンダクタンスをメモリトランジスタMTrのコンダクタンスよりも十分大きく設定した。書き込み時の動作電圧は、このように、書き込み電圧Vpgmを弱いインパクトイオン化が起こる程度の大きさとし、また、メモリトランジスタの動作点が線形領域に近い飽和領域となるように設定することが好ましい。

【0064】

上述した書き込み方法によって、メモリセル(1,1)への、電荷注入速度が一定の書き込み動作が可能となる。本実施の形態において、メモリトランジスタは1ビット(“0”または“1”の2値)の情報を記憶するものとし、“0”を書き込む場合には何もせず、“1”を書き込む場合には時間twだけ上述した書き込み動作を行う。なお、書き込み動作はしきい値電圧Vthの良く揃った状態に対して行われるものとする。また、時間twは、“1”の状態を得るのに必要な書き込み時間であり、あらかじめ調べられている。本実施の形態では、このようにベリファイ動作を行わず時間twの書き込み動作を行うだけであるため、書き込み時間は従来のベリファイ書き込みと比較して大幅に短縮することができる。もちろん、このような書き込み動作が可能となるのは、本発明における書き込み方法によって、高精度かつ分布幅の小さいしきい値分布が得られるためである。

【0065】

なお、書き込みを行わないメモリセル(2,1)〜(m,1)においては、選択線の電位Vselを0Vとして、選択トランジスタをオフとする。さらに、書き込み時のワード線の電位VWLが、メモリセル(2,1)〜(m,1)においてトンネル電流による誤書き込みが行われない程度であるように書き込み時の動作電圧を設定する必要がある。また、一列目以外のメモリセルに関しては、制御回路404(2)〜404(n)が非選択の状態であり、ビット線とワード線がいずれも浮遊状態となっているために誤動作の問題はない。

【0066】

次に、読み出し動作について述べる。読み出し動作では、消去信号Seraseにはオフの信号が入力され、書込・読出信号Sw/rと読み出し信号Sreadにはオンの信号が入力される。その結果、メモリセル(1,1)への読み出し動作に関与する回路構成は、図10のように表すことができる。図10において、VWLはワード線の電位、VBLはビット線の電位、Vscは共通ソース線の電位、Vselは選択線の電位、Voutは出力される読み出し電位である。またオペアンプ1001には電位Vreadが入力され、定電流源1002からは定電流Iが供給される。図10に示した回路図は、選択トランジスタSTrと読み出し電位Voutの出力部分を除いて、図1に示した回路図と一致し、その動作原理については既に説明を行った通りである。

【0067】

読み出し時の動作電圧としては、例えば、Vsel=3V、Vsc=GND、Vread=1V、I=1mAとすればよい。この場合のメモリトランジスタの動作点を図11に示す。曲線1101および1102はそれぞれメモリトランジスタMTrおよび選択トランジスタSTrのVd−Id曲線を表し、メモリトランジスタMTrの動作点は2つの曲線の交点Pで表される。なお、選択トランジスタSTrのコンダクタンスはメモリトランジスタMTrのコンダクタンスよりも十分大きく設定してある。読み出し時の動作電圧としては、インパクトイオン化によってホットエレクトロンが発生しない条件とする必要がある。そのためには、図11に示すように、Vreadを低く設定するとよい。

【0068】

そして、この動作電圧のもとで読み出し電位Voutを読み出すことによって、メモリセルに格納されているデータを読み出すことができる。この読み出し動作では、メモリトランジスタMTrのしきい値電圧がΔVthだけ増加すると、制御回路404(1)の負帰還の特性によってメモリトランジスタMTrのコントロールゲート電圧、つまり読み出し電位VoutもΔVthだけ増加することを利用する。

【0069】

なお、読み出しを行わないメモリセル(2,1)〜(m,1)においては、選択線の電位Vselを0Vとして、選択トランジスタをオフとする。その結果、読み出し電位Voutはメモリセル(1,1)のみで決まり、誤読み出しの心配は無い。また、動作電圧が低いために誤書き込みの問題も無い。一列目以外のメモリセルについても、制御回路404(2)〜404(n)が非選択の状態であり、ビット線とワード線がいずれも浮遊状態となっているために誤動作の問題はない。

【0070】

なお、本実施の形態では、読み出し方法としてワード線電位を読み出す方法を採用したが、ビット線電位を読み出す方法を用いることも可能である。

【0071】

最後に、消去動作について述べる。消去動作時には、消去信号Seraseにはオンの信号が入力され、書込・読出信号Sw/rと読み出し信号Sreadにはオフの信号が入力される。その結果、メモリセル(1,1)〜(m,1)への消去動作に関与する回路構成は、図12のように表される。図12において、VWLはワード線の電位、Vscは共通ソース線の電位、Vsel(1)〜Vsel(m)は選択線の電位である。図12に示すように、消去動作においてはオペアンプおよび定電流源は関与しない。

【0072】

消去時の動作電圧としては、例えば、VWL=−8V、全ての選択線の電位Vsel(1)〜Vsel(m)を0V、および基板電位(またはウェル電位)を8Vとすればよい。その結果、一列目のメモリセルを構成するメモリトランジスタのコントロールゲート−基板間には高い電位差が生じ、FNトンネル電流によってフローティングゲートに蓄積されていた電荷が基板へ引き抜かれる。なお、選択トランジスタはオフであり、メモリトランジスタのドレイン領域は浮遊状態となっている。また、一列目以外のメモリセルについては、制御回路404(2)〜404(n)が非選択の状態であり、ワード線が浮遊状態となっているために誤消去の問題はない。なお、基板電位を8Vとするかわりに、メモリトランジスタのソース領域とフローティングゲートとの間に一部重なる領域(オーバーラップ領域)を設けて、共通ソース電位Vscを8Vとすることも可能である。

【0073】

ベリファイを行わない書き込み動作後の分布幅を小さくするには、当然、書き込みを行う前しきい値電圧の分布幅が小さいことが必要である。しかしながら、上述した消去動作では、通常狭い分布幅を実現することは困難である。そこで、本実施の形態においては、FNトンネルによる消去動作の後に、新たに消去状態へのベリファイ書き込みを行うこととする。この消去状態のしきい値電圧としては、消去後の分布のよりもわずかに高い値とすることが好ましい。なお、消去状態へのベリファイ書き込みには、公知の回路構造と公知の動作方法を用いると良い。

【0074】

以上のようにして、本発明の不揮発性メモリの書き込み動作、読み出し動作および消去動作が行われる。本実施の形態で説明した動作電圧をまとめると、表1のようになる。なお、表1には、消去方法としてソース領域へ電荷を引き抜く場合の動作電圧が書かれている。

【0075】

【表1】

【0076】

本実施の形態では、2値の不揮発性メモリについて述べた。しかしながら、本発明は2値の不揮発性メモリに限られるわけではない。むしろ、本発明の不揮発性メモリの特徴は高精度のしきい値制御性にあるから、しきい値分布のマージンが少ない多値の不揮発性メモリにおいて特にその効果を発揮する。本発明を多値の不揮発性メモリに応用することにより、従来の比較して書き込み時間を短縮することができ、また、高い多値度を実現することが可能となる。本発明を多値のメモリに応用した例については実施例1を参照することができる。なお、本明細書では、一つのメモリセルが記憶できる状態数を多値度と呼ぶ。

【0077】

また、本実施の形態ではベリファイ動作を用いない書き込み方法について述べたが、もちろん、ベリファイ動作を用いた書き込み方法を行っても良い。その場合には、書き込み動作をベリファイ動作を行わない第1の書き込み動作とベリファイ動作を行う第2の書き込み動作によって構成するとよい。具体的には、まず第1の書き込み動作では、高精度のしきい値制御特性を活かして、最終的なしきい値電圧よりもわずかに低い状態への書き込みを行い、次に残ったしきい値電圧の不足分についてベリファイ書き込みを行うことが好ましい。その結果、従来のベリファイ書き込みと比較して、ベリファイ動作の回数を少なくすることができ、ベリファイ書き込みの時間を短縮することが可能となる。なお、ベリファイ書き込みとしては、公知の回路構造と公知の動作方法を用いると良い。

【0078】

また、本実施の形態ではメモリセル(1,1)への書き込みと読み出し及び一列目のメモリセル(1,1)〜(m,1)の一括消去の方法を述べたが、これらの動作を複数列に渡って同時に行うことも可能である。特に、制御回路404(1)〜404(n)を全て選択することによって、一行目のメモリセル(1,1)〜(1,n)への同時書き込みと同時読み出し、及び全てのメモリセルの一括消去を行うことが可能である。もちろん、書き込み・読み出し回路405としては、nビットのデータを並列に扱うことのできる回路が必要となる。また、各動作において同時に流れる電流量の合計が、回路の電流駆動能力を越えないことが必要である。

【0079】

なお、本発明における書き込み方法は、負帰還を利用するために、動作電圧が安定するまでに時間がかかる場合が有る。このため、必要に応じて、制御回路にディスチャージ回路やプリチャージ回路を設け、動作電圧が安定するまでの時間を短縮することが好ましい。

【0080】

(実施例1)

本実施例では、本発明の不揮発性メモリを多値に応用した例について説明する。

本発明の不揮発性メモリは、しきい値電圧の制御性に優れた書き込み動作を特徴としており、しきい値分布のマージンが少ない多値の不揮発性メモリにおいて、特にその効果を発揮する。本発明を応用した多値の不揮発性メモリは、従来と比較して書き込み時間を短縮することができ、また、高い多値度を実現することができる。

【0081】

多値の不揮発性メモリは、3つ以上の状態を記憶することのできるメモリ素子によって構成される。例えば、メモリ素子のしきい値電圧を3つ以上の状態に区別する方法や、複数の箇所に電荷を蓄積することのできるメモリ素子を用いる方法等がある。本実施例では、メモリ素子のしきい値電圧を4つの状態に区別して、“0”(消去状態),“1”,“2”,“3”の4状態を記憶する4値の不揮発性メモリについて説明する。図13には、4つの状態を表すしきい値電圧の分布が示されている。図13において、Vth0,Vth1,Vth2,Vth3はそれぞれ、状態“0”,“1”,“2”,“3”のしきい値分布の中心の値である。

【0082】

図14には、本発明の書き込み方法を用いた場合のメモリ素子のしきい値電圧と書き込み時間の関係が示されている。図14において、時間tw1、tw2、tw3はそれぞれ、消去状態“0”から、“1”,“2”,“3”への書き込み時間を表す。しきい値電圧と書き込み時間は線形の関係にあるから、4状態のしきい値電圧の間隔が等しい場合には、tw1、tw2、tw3の比は、tw1:tw2:tw3=1:2:3となる。このように、本発明の書き込み方法では、書き込み時間を制御することによって、容易にかつ高精度にそれぞれの状態への書き込みを行うことができる。より一般的には、一度の書き込み動作によって書き込みを行う場合、必要な書き込み時間の比は各状態のしきい値電圧の間隔の比と一致させればよい。

【0083】

以下に、本発明の4値の不揮発性メモリの回路構成と動作方法について説明する。簡単のため、4値の状態を表すしきい値分布は図13に示したものとし、各状態のしきい値電圧の間隔は等しいとする。

【0084】

多値の不揮発性メモリの回路構成は、基本的には2値の不揮発性メモリと同じとすればよく、メモリセルアレイ、アドレスデコーダおよび制御回路等は、図4〜図7に示した回路図と同じものを用いることができる。多値の回路構成が2値の場合と異なるのは、主に読み出し回路と書き込み回路である。4値の不揮発性メモリでは、読み出し回路は4つの状態を区別して2ビットデータとして読み出し、書き込み回路は2ビットのデータに基づいて4つの状態への書き込みを行う必要がある。従って、読み出し回路および書き込み回路は、多値度の異なる不揮発性メモリ(2値を含む)毎に異なったものとなる。

【0085】

書き込み方法として、ベリファイ動作を行わない一回の書き込み動作を考える。

この場合には、入力される2ビットのデータに基づいて、書き込み時間が0、tw1、tw2またはtw3であるような書き込み動作を行えばよい。書き込み動作は実施の形態で説明した方法と同様とすればよく、書込・読出信号には幅が0、tw1、tw2またはtw3のオンのパルス信号を入力すればよい。もちろん、動作電圧は書き込み時間等によって決まる最適な値を用いることが望ましい。本発明における書き込み方法は、電荷注入速度が一定であるため、4状態への書き込み時間の比が0:1:2:3となる簡単な時間制御によって書き込みを行うことができる。

【0086】

読み出し方法としては、まず、2値のメモリと同様にして制御回路から読み出し電位Voutを読み出す。読み出し回路では、読み出されたVoutの値によって、状態“0”、“1”、“2”、“3”を判断し、2ビットのデータへの変換を行えばよい。読み出し回路には、従来の多値の不揮発性メモリに用いられる公知の読み出し回路を用いることができる。

【0087】

消去方法は、メモリ素子の状態に関わらず“0”(消去状態)への消去を行えば良いので、2値のメモリと同様、FNトンネル電流による消去動作を行えばよい。なお、書き込みにおいてベリファイ動作を行わない場合には、書き込み前のしきい値電圧を揃える必要があるため、実施の形態において説明を行ったのと同様に、FNトンネル消去後に、消去状態“0”へのベリファイ書き込みを行うことが好ましい。消去状態“0”へのベリファイ書き込みには、公知の回路構成と公知の動作方法を用いると良い。

【0088】

書き込み動作の例をもう少し詳しく説明する。図15は書き込み回路図の一例を示したものである。書き込み回路1501は、ラッチ1502、パルス発生回路1503等によって構成される。書き込み回路1501に2ビットの書き込みデータが入力されると、ラッチ1502に保持されると共に、パルス発生回路1503によって複数の信号が形成される。これらの信号は、ラッチ1502に保持されたデータに従って適切に選択され、書き込みパルス信号Swと書き込み終了信号Swfとして出力される。

【0089】

図16には、書き込みパルス信号Swと書き込み終了信号Swfのタイミングチャートが示されている。図16に示すように、書き込みパルス信号Swは、入力されたデータに基づいてそれぞれ異なるパルス幅を有し、書き込み終了信号Swfは、書き込みパルスが立ち下がった後に立ち上がって書き込み終了を伝える。具体的には、状態“0”、“1”、“2”、“3”に対応するデータが入力された場合には、書き込み信号Swは、それぞれ0、tw1、tw2、tw3のパルス幅を有する。

【0090】

出力された書き込みパルス信号Swは、オペアンプの入力端子と、Vpgm及びGNDとの接続を切り替えるスイッチトランジスタへ接続される。書き込みパルス信号Swがオンの場合にVpgmがオペアンプの入力端子に接続され、オフの場合にGNDがオペアンプの入力端子に接続される。

【0091】

上述したパルス発生回路1503では、例えば、シフトレジスタによってtw1,tw2およびtw3だけ時間をずらした3つの立ち上がり信号を作成し、もとの信号とのイクスクルーシブオア(XOR)を取ることによって幅の異なるパルスを作成することができる。そして、書き込みパルス信号Swは幅の異なるパルス信号から、また書き込み終了信号Swfは時間をずらした立ち上がり信号から、入力データに基づいて選択すればよい。

【0092】

以上のようにして、本発明の不揮発性メモリの書き込み動作、読み出し動作および消去動作が行われる。

【0093】

本実施例では、多値メモリを代表して4値の場合について説明を行ったが、8値、16値、或はそれ以上の多値メモリに対しても本実施例と全く同様に本発明を応用することが可能である。また、本実施例では、多値の状態を表すしきい値分布の間隔が均等である場合について述べたが、多値の状態を表すしきい値分布の間隔が均等でない場合においても書き込みパルス幅を変えるだけで全く同様な動作を行うことが可能である。

【0094】

本発明における書き込み動作は、従来と比較して書き込み後のしきい値電圧の分布幅が小さく、分布の制御性に優れるため、多値の不揮発性メモリにおいても、ベリファイ動作を行わない一度の書き込み動作によって書き込みを行うことが可能となりうる。また、ベリファイ動作を行う場合であっても、まず書き込み後の状態よりわずかにしきい値電圧が低い状態への書き込み(第1の書き込み)を行い、次いでベリファイ書き込み(第2の書き込み)を行うことによって、書き込みの時間を大幅に短縮することが可能となる。なお、ベリファイ書き込みは、書き込み終了信号Swfの立ち上がりを確認して始めれば良い。ベリファイ書き込み回路は図示しないが、公知の回路構造と公知の動作方法を用いればよい。

【0095】

また、上述した多値メモリの動作方法は、複数列にわたって同時に行うことも可能である。その場合には、図17に示すような書き込み回路図を用いることができる。図17において、ラッチ1702は各列毎に設けられており、ラッチ1702に保持されたデータに従って、共通のパルス発生回路1701から適切な書き込みパルス信号を選択する構成となっている。書き込み終了信号Swfとしては、例えば書き込み時間tw3の後に立ち上がる信号を用いると良い。このように書き込み動作、読み出し動作および消去動作の並列化を行うことによって、動作の高速化を図ることができる。

【0096】

なお、しきい値電圧を高精度に制御する方法としては、上述したような時間による制御方法が好ましいが、より一般的には、書き込み電圧Vpgmと書き込み時間を自由に設定して、多値のそれぞれの状態への書き込み動作を行えばよい。

【0097】

(実施例2)

本実施例では、実施の形態で説明を行った不揮発性メモリの回路構成とは異なる例について述べる。図18には、m行n列(m、nはそれぞれ1以上の整数)のメモリセルアレイを有する本実施例の不揮発性メモリの回路図を示す。図18に示した不揮発性メモリは、メモリセルアレイ1801、Xアドレスデコーダ1802、Yアドレスデコーダ1803、制御回路1804(1)〜1804(n)、読み出し・書き込み回路1805、および他の周辺回路(図示せず)によって構成される。他の周辺回路には、アドレスバッファ回路、電源発生回路、昇圧回路、電源制御回路、その他の制御回路、等が含まれ、必要に応じて設けられる。

【0098】

各メモリセルは、メモリトランジスタMTr及び選択トランジスタSTrによって構成される。メモリトランジスタMTrはフローティングゲートを有するトランジスタであり、選択トランジスタSTrは通常のトランジスタである。なお、メモリトランジスタMTrとしては、クラスタ層を有するメモリトランジスタ、MNOS構造またはMONOS構造のメモリトランジスタを用いてもよい(実施例3参照)。

【0099】

図18において、メモリセル(i,j)(1≦i≦m、1≦j≦n)は、選択線SLi、ワード線WLj、ビット線BLj及び共通ソース線SCと接続されている。具体的には、メモリトランジスタMTrのコントロールゲート電極に選択トランジスタSTrのソース・ドレイン電極の一方が、ソース電極に共通ソース線SCが、ドレイン電極にビット線BLiが接続されており、また、選択トランジスタSTrのソース・ドレイン電極の残る一方にワード線WLjが、ゲート電極に選択線SLiが接続されている。選択線SL1〜SLmはYアドレスでコーダ1703に、ワード線WLjとビット線BLjは制御回路1804(j)(1≦j≦n)に接続されている。また制御回路1804(1)〜1804(n)はXアドレスでコーダ1802および読み出し・書き込み回路1805に接続されている。

【0100】

次に、制御回路1804(1)〜(n)について説明する。n個の制御回路は全て同じであるため、以下、一つを代表して制御回路1804と書く。図19には、制御回路1804の回路図の一例が示されており、制御回路1804はオペアンプ1901、定電流源1902及び複数のスイッチトランジスタ1903〜1911によって構成されている。制御回路1804を構成するオペアンプ1901、定電流源1902及び複数のスイッチトランジスタ1903〜1910については、図5に示した制御回路と全く同様であるため説明を省略する。また、オペアンプ1901および定電流源1902の回路図としては、例えば、図6及び図7に示した回路図を用いることができる。もちろん、他の公知の回路を用いることもできる。制御回路1804が図5に示した制御回路と異なる点はディスチャージ回路を有する点にある。つまり、ワード線WLはスイッチトランジスタ1911を介してGNDと接続されている。スイッチトランジスタ1911のゲート電極はディスチャージ信号Sdcと接続されている。

【0101】

次に、本実施例の不揮発性メモリの動作方法について述べる。ここでは、メモリセル(1,1)への書き込みおよび読み出しと、一列目のメモリセル(1,1)〜(1,m)の一括消去について説明する。もちろん、他のメモリセルに対しても同様の動作を行うことができる。なお、本実施例では、各メモリトランジスタは2値のデータを記憶し、また書き込み時にはベリファイ動作を行わない場合について述べる。

【0102】

まず、各動作が行われる前に、一列目のメモリセルがXアドレスデコーダによって選択される。具体的には、Xアドレスデコーダの出力信号によって、制御回路1804(1)を構成するスイッチトランジスタ1903〜1906がオンとなると共に、制御回路1804(2)〜1804(n)を構成するスイッチトランジスタ1903〜1906は全てオフとなる。また、制御回路1804(1)が選択されると同時に、消去信号Serase、書込・読出信号Sw/r、及び読み出し信号Sreadによって制御回路1804(1)の動作モードが選択される。

【0103】

本実施例のメモリセルの回路の特徴は、メモリトランジスタMTrのコントロールゲート電極とワード線WLとの間に選択トランジスタが接続されている点にある。以下に述べるように、書き込みおよび読み出し動作では、動作を行わない行を構成する選択トランジスタはオフの状態とするため、メモリトランジスタMTrのコントロールゲート電極は浮遊状態となる。本実施例の駆動方法では、これらのメモリセルにおいて誤動作が起こらないようにするために、書き込みおよび読み出し動作において選択トランジスタをオフとする前に、全てのメモリトランジスタMTrのコントロールゲート電極を、ディスチャージ回路を用いてGNDに落とすことにする。

【0104】

まず、書き込み動作では、消去信号Serase、読み出し信号Sreadにはオフの信号が入力され、書込・読出信号Sw/rにはオンの信号が入力される。その結果、メモリセル(1,1)への書き込み動作に関与する回路構成は、図20のように表される。図20において、VWLはワード線の電位、VBLはビット線の電位、Vscは共通ソース線の電位、Vselは選択線の電位、Vpgmは書き込み電位、Iは定電流源が供給する電流、Sdcはディスチャージ信号である。図20に示した回路図は、選択トランジスタSTrとディスチャージ回路を除いて図1に示した回路図と一致し、その動作原理については既に説明を行ったので省略する。

【0105】

書き込み時の動作電圧としては、例えば、Sdc=0V、Vsel=12V、Vsc=GND、Vpgm=6V、I=10mAとすればよい。この場合のメモリトランジスタの動作点は、実施の形態で示した例(図9参照)とほぼ同様であると考えて良い。書き込み時の動作電圧は、書き込み電圧Vpgmを弱いインパクトイオン化が起こる程度の大きさとし、また、メモリトランジスタの動作点が線形領域に近い飽和領域となるように設定することが好ましい。

【0106】

本実施例において、メモリトランジスタは1ビット(“0”または“1”の2値)の情報を記憶するものとし、“0”を書き込む場合には何もせず、“1”を書き込む場合にはあらかじめ調べられた時間twだけ上述した書き込み動作を行う。なお、書き込み動作はしきい値電圧Vthが正であり、かつ良く揃った状態に対して行われるものとする。

【0107】

本実施例では、このようにベリファイ動作を行わず時間twの書き込み動作を行うため、従来のベリファイ書き込みと比較して書き込み時間を大幅に短縮することができる。もちろん、このような書き込み動作が可能となるのは、本発明における書き込み方法によって、高精度かつ分布幅の小さいしきい値分布が得られるためである。

【0108】

書き込み動作を時間twだけ行った後には、次のように書き込み動作を終了する。まず、制御回路において、書込・読出信号Sw/rにオフの信号を入力すると共に、ディスチャージ信号Sdcにオンの信号を入力し、全てのワード線WLの電位をGNDに落とす。同時に全ての選択線SLの電位Vselを3Vとして、全てのメモリトランジスタのコントロールゲート電極をGNDに落とした後、全ての選択線SLの電位Vselを0Vに落とす。同時にディスチャージ信号Sdcにオフの信号を入力する。

【0109】

なお、書き込み動作において、書き込みを行わないメモリセル(2,1)〜(m,1)は、選択線の電位Vselを0Vとして、選択トランジスタをオフとする。この場合、メモリセル(2,1)〜(m,1)を構成するメモリトランジスタのコントロールゲート電極は浮遊状態となるが、上述したようにコントロールゲートの電位は0Vとなっており、また、メモリトランジスタのしきい値電圧Vthは正に揃えられているために、メモリトランジスタはオフとなり誤動作の心配はない。また、一列目以外のメモリセルに関しては、制御回路1804(2)〜1804(n)が非選択の状態であり、ビット線とワード線がいずれも浮遊状態となっているために誤動作の問題はない。

【0110】

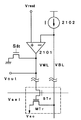

次に、読み出し動作について述べる。読み出し動作では、消去信号Seraseにはオフの信号が入力され、書込・読出信号Sw/rと読み出し信号Sreadにはオンの信号が入力される。その結果、メモリセル(1,1)への読み出し動作に関与する回路構成は、図21のように表すことができる。図21において、VWLはワード線の電位、VBLはビット線の電位、Vscは共通ソース線の電位、Vselは選択線の電位、Voutは出力される読み出し電位、Sdcはディスチャージ信号である。またオペアンプ2101には電位Vreadが入力され、定電流源2102からは定電流Iが供給される。図21に示した回路図は、選択トランジスタSTr、ディスチャージ回路及び読み出し電位Voutの出力部分を除いて、図1に示した回路図と一致し、その動作原理については既に説明を行った通りである。

【0111】

読み出し時の動作電圧としては、例えば、Sdc=0V、Vsel=5V、Vsc=GND、Vread=1V、I=1mAとすればよい。この場合のメモリトランジスタの動作点は、実施の形態で示した例(図11参照)とほぼ同様であると考えて良い。読み出し時の動作電圧としては、インパクトイオン化によってホットエレクトロンが発生しない条件とする必要がある。そのためには、Vreadを低く設定するとよい。

【0112】

そして、この動作電圧のもとで読み出し電位Voutを読み出すことによって、メモリセルに格納されているデータを読み出すことができる。この読み出し動作では、メモリトランジスタのしきい値電圧がΔVthだけ増加すると、制御回路1804(1)の負帰還の特性によってメモリトランジスタのコントロールゲート電圧、つまり読み出し電位VoutもΔVthだけ増加することを利用する。

【0113】

読み出し動作を行った後も、ディスチャージ動作によって全てのメモリトランジスタのコントロールゲート電極をGNDに落とす。まず、制御回路において、書込・読出信号Sw/rにオフの信号を入力すると共に、ディスチャージ信号Sdcにオンの信号を入力し、全てのワード線WLの電位をGNDに落とす。同時に全ての選択線SLの電位Vselを3Vとして、全てのメモリトランジスタのコントロールゲート電極をGNDに落とした後、全ての選択線SLの電位Vselを0Vに落とす。同時にディスチャージ信号Sdcにオフの信号を入力する。

【0114】

なお、読み出しを行わないメモリセル(2,1)〜(m,1)においては、選択線の電位Vselを0Vとして、選択トランジスタをオフとする。その結果、メモリセル(2,1)〜(m,1)を構成するメモリトランジスタはオフとなり、読み出し電位Voutはメモリセル(1,1)のみで決まるため、誤読み出しの心配は無い。また、動作電圧が低いために誤書き込みの問題も無い。一列目以外のメモリセルについても、制御回路1804(2)〜1804(n)が非選択の状態であり、ビット線とワード線がいずれも浮遊状態となっているために誤動作の問題はない。

【0115】

なお、本実施例では、読み出し方法としてワード線電位を読み出す方法を採用したが、ビット線電位を読み出す方法を用いることも可能である。

【0116】

最後に、消去動作について述べる。消去動作時には、消去信号Seraseにはオンの信号が入力され、書込・読出信号Sw/rと読み出し信号Sreadにはオフの信号が入力される。また、ディスチャージ信号Sdcにはオフの信号が入力される。その結果、メモリセル(1,1)〜(m,1)への消去動作に関与する回路構成は、図22のように表される。図22において、VWLはワード線の電位、Vscは共通ソース線の電位、Vsel(1)〜Vsel(m)は選択線の電位である。図22に示すように、消去動作においてはオペアンプおよび定電流源は関与しない。

【0117】

消去時の動作電圧としては、例えば、VWL=−8V、全ての選択線の電位Vsel(1)〜Vsel(m)を0V、および基板電位(またはウェル電位)を8Vとすればよい。その結果、一列目のメモリセルを構成する選択トランジスタはオンとなり、メモリトランジスタのコントロールゲート−基板間には16V程度の高い電位差が生じる。その結果、FNトンネル電流によってフローティングゲートに蓄積されていた電荷が基板へ引き抜かれる。なお、ビット線は浮遊状態となっている。一列目以外のメモリセルについては、制御回路1804(2)〜1804(n)が非選択の状態であり、ワード線が浮遊状態となっているために誤消去の問題はない。なお、基板電位を8Vとするかわりに、メモリトランジスタのソース領域とフローティングゲートとの間に一部重なる領域(オーバーラップ領域)を設けて、共通ソース電位Vscを8Vとすることも可能である。

【0118】

ベリファイを行わない書き込み動作後の分布幅を小さくするには、当然、書き込みを行う前しきい値電圧の分布幅が小さいことが必要である。しかしながら、上述した消去動作では、通常狭い分布幅を実現することは困難である。そこで、本実施例においては、FNトンネルによる消去動作の後に、新たに消去状態へのベリファイ書き込みを行うこととする。この消去状態のしきい値電圧は、0V以上であり、消去後の分布のよりもわずかに高い値とすることが好ましい。なお、消去状態へのベリファイ書き込みには、公知の回路構造と公知の動作方法を用いると良い。また、消去状態へのベリファイ書き込み後には、ディスチャージ動作によって、全てのメモリセルのコントロールゲートの電位を0Vとする。

【0119】

以上のようにして、本発明の不揮発性メモリの書き込み動作、読み出し動作および消去動作が行われる。

【0120】

本実施例では2値の不揮発性メモリについて述べたが、本発明の不揮発性メモリの特徴は高精度のしきい値制御性にあるから、むしろ、しきい値分布のマージンが少ない多値の不揮発性メモリにおいて特にその効果を発揮する。本実施例を実施例1と組み合わせることによって、書き込み時間の短い、また、多値度の高い不揮発性メモリを実現することが可能となる。

【0121】

なお、本実施例ではベリファイ動作を用いない書き込み方法について述べたが、もちろん、ベリファイ書き込みを行っても良い。また、本実施例ではメモリセル(1,1)への書き込みと読み出し及び一列目のメモリセル(1,1)〜(m,1)の一括消去の方法を述べたが、これらの動作を複数列に渡って同時に行うことも可能である。これらの応用については、実施の形態で説明を行った通りである。

【0122】

なお、本実施例では、消去状態におけるメモリトランジスタのしきい値電圧を正としたが、本発明はこの場合に限られるわけではない。消去状態におけるメモリトランジスタのしきい値電圧が負の場合には、ディスチャージ動作によって、コントロールゲートの電位を消去状態のしきい値電圧より低くすることによって、本実施例と全く同様に動作を行うことができる。この他、メモリトランジスタをスプリットゲート構造とすることも有効である。

【0123】

(実施例3)

本発明は、活性領域とコントロールゲート電極の間に電荷蓄積領域を有する様々なメモリ素子に対して適用することが可能である。特に、電化蓄積領域として半導体のクラスタ層、金属のクラスタ層、あるいは窒化膜を設けたメモリ素子に対しても適用することができる。これらのメモリ素子は、電荷を蓄積する領域が空間的に離散的に設けられていることを特徴とする

【0124】

電荷を蓄積する領域として半導体または導体のクラスタ層を用いるメモリ素子としては、例えば、特開昭49−22356号公報に開示されている。その代表的な断面構造を図26(a)に示す。図26(a)に示したメモリ素子は、活性領域2601上に、第1の絶縁膜2602と、クラスタ層2603と、第2の絶縁膜2605と、コントロールゲート電極2606とが順に積層されてなるメモリトランジスタである。クラスタ層2603は、離散的な塊状の半導体または導体(クラスタと呼ぶ)によって構成される層であり、この離散的なクラスタ2604が電荷の捕獲中心としての役割を果たす。

【0125】

また、電荷を蓄積する領域として窒化膜等を用いるメモリ素子としては、MNOS(Metal-Nitride-Oxide-Semiconductor)、MONOS(Metal-Oxide-Nitride-Oxide-Semiconductor)等が知られている。MNOS及びMONOSの代表的な断面構造を図26(b)及び(c)にそれぞれ示す。図26(b)示したメモリ素子は、活性領域上2607に、酸化膜2608、窒化膜2609、コントロールゲート電極2610が積層されてなる。また、図26(c)示したメモリ素子は、活性領域2611上に、酸化膜2612、窒化膜2613、酸化膜2614、コントロールゲート電極2615が積層されてなる。いずれにおいても、窒化膜中の空間的に離散的な不純物準位が電荷の捕獲中心としての役割を果たす。

【0126】

このようなメモリ素子を本発明の不揮発性メモリに応用する場合においても、実施の形態で説明を行った回路構成と動作方法をそのまま用いることができる。もちろん、動作電圧と動作電流はそれぞれの素子において最適な値を用いることが好ましい。

【0127】

メモリ素子として、電荷を蓄積する領域が離散的に設けられている素子を用いた場合、電荷保持特性がトンネル酸化膜の欠陥やピンホールの影響を受けにくいという効果がある。例えば、図26(d)に示すような、フローティングゲートを有するメモリトランジスタのように、電荷を蓄積する領域が連続的に設けられている場合には、トンネル酸化膜に一箇所のピンホールがあると、フローティングゲートに蓄積された電荷は全てそのピンホールからリークしてしまうため、メモリトランジスタの電荷保持特性に大きく影響する。しかし、電荷を蓄積する領域が離散的に設けられている素子を用いた場合には、ピンホールの影響を受ける領域は限定され、多くの電荷蓄積領域はそのピンホールの影響を受けないため、メモリ素子の電荷保持特性への影響は少ない。

【0128】

なお、フローティングゲートを有するメモリトランジスタとは、図26(d)に示すように、活性領域2616上に第1の絶縁膜2617と、半導体膜または導体膜によって構成されるフローティングゲート電極2618と、第2の絶縁膜2619と、コントロールゲート電極2620とが順に積層されてなるメモリトランジスタをいう。

【0129】

本実施例のメモリ素子を本発明の不揮発性メモリに応用する場合には、特に多値のメモリに応用することが好ましい。多値の不揮発性メモリは、異なる状態を表すしきい値電圧のマージンが少ないために、書き込み時や消去時における高精度のしきい値制御や、良好な電荷保持特性が必要となることは良く知られている。

そして、本発明の不揮発性メモリは、しきい値電圧の制御性に優れるために、多値の不揮発性メモリに対して特に有効であることは、実施の形態及び実施例1で述べた通りである。

【0130】

他方、多値の不揮発性メモリのもう一つの問題点である電荷保持特性については、本実施例のメモリ素子を用いることによって、大幅に改善することが可能となる。このように、本実施例で述べたメモリ素子は、本発明を多値の不揮発性メモリに応用する場合に特に好ましいということができる。

【0131】

なお、本実施例の構成は、実施例1、2のいずれの構成とも自由に組み合わせることが可能である。

【0132】

(実施例4)

本実施例では本発明の不揮発性メモリをワンチップ上に集積化されたRISCプロセッサ、ASICプロセッサ等のマイクロプロセッサに適用した場合の例について説明する。

【0133】

図23に示すのは、マイクロプロセッサの一例である。マイクロプロセッサは典型的にはCPUコア2301、フラッシュメモリ2304(RAMでも良い)、クロックコントローラ2303、キャッシュメモリ2302、キャッシュコントローラ2305、シリアルインターフェース2306、I/Oポート2307等から構成される。勿論、図23に示すマイクロプロセッサは簡略化した一例であり、実際のマイクロプロセッサはその用途によって多種多様な回路設計が行われる。

【0134】

図23に示すマイクロプロセッサではCPUコア2301、クロックコントローラ2303、キャッシュコントローラ2305、シリアルインターフェース2306、I/Oポート2307をCMOS回路で構成している。また、フラッシュメモリ2304には本発明の不揮発性メモリが用いられている。フラッシュメモリ2304としては、実施の形態及び実施例1〜3のいずれの構成とも組み合わせることが可能である。なお、キャッシュメモリ2302に本発明の不揮発性メモリを利用することも可能である。

【0135】

なお、本実施例のマイクロプロセッサは、実施例1〜3のどのような組み合わせからなる構成を用いても良い。

【0136】

(実施例5)

本発明の不揮発性メモリはデータの記憶・読み出しを行う記録媒体として、あらゆる分野の電子機器に組み込むことが可能である。本実施例では、その様な電子機器について説明する。

【0137】

本発明の不揮発性メモリを利用しうる電子機器としては、ディスプレイ、ビデオカメラ、デジタルカメラ、頭部取り付け型のディスプレイ、DVDプレーヤー、ゲーム機、ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、カーナビゲーション、音響再生装置(カーオーディオ等)、パーソナルコンピュータ、携帯情報端末(モバイルコンピュータ、携帯電話または電子書籍等)などが挙げられる。それらの一例を図24、25に示す。

【0138】

図24(A)はディスプレイであり、筐体2401、支持台2402、表示部2403等を含む。本発明は表示部2403やその他の信号制御回路に接続され、画像信号の補正や処理データの記憶に利用される。

【0139】

図24(B)はビデオカメラであり、本体2411、表示部2412、音声入力部2413、操作スイッチ2414、バッテリー2415、受像部2416で構成される。本発明は内蔵のLSI基板に組み込まれ、画像データの記憶などの機能に利用される。

【0140】

図24(C)は頭部取り付け型のディスプレイの一部(右片側)であり、本体2421、信号ケーブル2422、頭部固定バンド2423、表示部2424、光学系2425、表示装置2426等を含む。本発明は表示装置2426やその他の信号制御回路に接続され、画像信号の補正や処理データの記憶に利用される。

【0141】

図24(D)は記録媒体を備えた画像再生装置(具体的にはDVD再生装置)であり、本体2431、記録媒体2432、操作スイッチ2433、表示部2434、2435等で構成される。なお、この装置は記録媒体としてDVD(Digital Versatile Disc)、CD等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行うことができる。本発明は内蔵のLSI基板に組み込まれ、画像データや処理データの記憶などの機能に利用される。

【0142】

図24(E)はゴーグル型ディスプレイ(ヘッドマウントディスプレイ)であり、本体2441、表示部2442、アーム部2443を含む。本発明は表示部2442やその他の信号制御回路に接続され、画像信号の補正や処理データの記憶に利用される。

【0143】

図24(F)はパーソナルコンピュータであり、本体2451、筐体2452、表示部2453、キーボード2454等で構成される。本発明は内蔵のLSI基板に組み込まれ、処理データや画像データの記憶に利用される。

【0144】

図25(A)は携帯電話であり、本体2501、音声出力部2502、音声入力部2503、表示部2504、操作スイッチ2505、アンテナ2506を含む。本発明は内蔵のLSI基板に組み込まれ、電話番号を記録するアドレス機能などを付加するために利用される。

【0145】

図25(B)は音響再生装置、具体的にはカーオーディオであり、本体2511、表示部2512、操作スイッチ2513、2514を含む。本発明は内蔵のLSI基板に組み込まれ、画像データや処理データの記憶などの機能に利用される。また、本実施例では車載用オーディオを示すが、携帯型や家庭用の音響再生装置に用いても良い。

【0146】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に適用することが可能である。また、本実施例の電子機器は実施例1〜3のどのような組み合わせからなる構成を用いても実現することができる。

【0147】

【発明の効果】

本発明の不揮発性メモリは、メモリ素子のドレイン電圧とドレイン電流とを制御することによって、書き込み動作において高精度のしきい値制御を行うことが可能となる。

【0148】

その結果、ベリファイ書き込みにおいてベリファイ回数を減らすこと、さらにはベリファイ方式を用いない書き込み方法が可能となり、従来と比較して書き込み時間の大幅な短縮を実現することが可能となる。

【0149】

本発明は、特に多値の不揮発性メモリに応用した場合に、書き込み時間短縮の効果は大きい。さらに、メモリ素子として、離散的な電荷蓄積領域を有するトランジスタを用いた場合には、電荷保持特性に優れ、書き込み時のしきい値制御性にも優れた多値の不揮発性メモリを提供することができる。

【0150】

本発明のしきい値制御性の優れた不揮発性メモリを搭載することによって、高速書き込み動作が可能な不揮発性メモリを具備する半導体装置を提供することができる。

【図面の簡単な説明】

【図1】 本発明の不揮発性メモリの書き込み動作を説明する回路図。

【図2】 本発明の不揮発性メモリのしきい値電圧と書き込み時間の関係を示す図。

【図3】 本発明の不揮発性メモリの書き込み動作後のしきい値分布を表す図。

【図4】 本発明の不揮発性メモリの全体構成を示す図。

【図5】 本発明の不揮発性メモリの部分構成を示す図。

【図6】 本発明の不揮発性メモリの部分構成を示す図。

【図7】 本発明の不揮発性メモリの部分構成を示す図。

【図8】 本発明の不揮発性メモリの書き込み動作を説明する回路図。

【図9】 本発明の不揮発性メモリの書き込み時の動作点を示す図。

【図10】 本発明の不揮発性メモリの読み出し動作を説明する回路図。

【図11】 本発明の不揮発性メモリの読み出し時の動作点を示す図。

【図12】 本発明の不揮発性メモリの消去動作を説明する回路図。

【図13】 本発明の不揮発性メモリのしきい値分布を表す図。

【図14】 本発明の不揮発性メモリのしきい値電圧と書き込み時間の関係を示す図。

【図15】 本発明の不揮発性メモリの書き込み回路図。

【図16】 本発明の不揮発性メモリの書き込み時のタイミングチャート。

【図17】 本発明の不揮発性メモリの書き込み回路図。

【図18】 本発明の不揮発性メモリの全体構成を示す図。

【図19】 本発明の不揮発性メモリの部分構成を示す図。

【図20】 本発明の不揮発性メモリの書き込み動作を説明する回路図。

【図21】 本発明の不揮発性メモリの読み出し動作を説明する回路図。

【図22】 本発明の不揮発性メモリの消去動作を説明する回路図。

【図23】 本発明の不揮発性メモリを用いた半導体回路を示す図。

【図24】 本発明の不揮発性メモリを用いた電子機器を示す図。

【図25】 本発明の不揮発性メモリを用いた電子機器を示す図。

【図26】 本発明の不揮発性メモリを構成するメモリ素子の断面図。

【符号の説明】

101 メモリトランジスタ

102 定電流源

103 オペアンプ

Claims (14)

- メモリトランジスタと、第1の電流源と、オペアンプと、を有し、

前記第1の電流源は、前記メモリトランジスタのドレイン電極と電気的に接続され、

前記オペアンプの出力端子は、前記メモリトランジスタのゲートと電気的に接続され、

前記オペアンプの第1の入力端子は、前記第1の電流源と電気的に接続され、

前記オペアンプの第2の入力端子には、書き込み動作時において前記メモリトランジスタの閾値電圧を変動させる場合には第1の電位が供給され、且つ読み出し動作時において第2の電位が供給され、

前記第2の電位は、前記第1の電位よりも低く、

前記書き込み動作時に前記オペアンプの第2の入力端子に前記第1の電位を供給する時間を制御することによって、前記メモリトランジスタの閾値電圧を制御することを特徴とする半導体装置。 - メモリトランジスタと、第1の電流源と、オペアンプと、を有し、

前記第1の電流源は、前記メモリトランジスタのドレイン電極と電気的に接続され、

前記オペアンプの出力端子は、前記メモリトランジスタのゲートと電気的に接続され、

前記オペアンプの第1の入力端子は、前記第1の電流源と電気的に接続され、

前記オペアンプの第2の入力端子には、書き込み動作時において前記メモリトランジスタの閾値電圧を変動させる場合には第1の電位が供給され、且つ読み出し動作時において第2の電位が供給され、

前記第2の電位は、前記第1の電位よりも低く、

前記第1の電位を前記オペアンプの第2の入力端子に供給するかしないかを制御する第1のトランジスタと、

第3の電位を前記オペアンプの第2の入力端子に供給するかしないかを制御する第2のトランジスタと、

入力データに応じて前記第1のトランジスタの導通状態及び前記第2のトランジスタの導通状態を制御する機能を有する回路と、を有し、

前記書き込み動作時に前記第1のトランジスタがオンになる時間を制御することによって、前記メモリトランジスタの閾値電圧を制御することを特徴とする半導体装置。 - メモリトランジスタと、第1の電流源と、オペアンプと、を有し、

前記第1の電流源は、前記メモリトランジスタのドレイン電極と電気的に接続され、

前記オペアンプの出力端子は、前記メモリトランジスタのゲートと電気的に接続され、

前記オペアンプの第1の入力端子は、前記第1の電流源と電気的に接続され、

前記オペアンプの第2の入力端子には、書き込み動作時において前記メモリトランジスタの閾値電圧を変動させる場合には第1の電位が供給され、且つ読み出し動作時において第2の電位が供給され、

前記第2の電位は、前記第1の電位よりも低く、

第1のトランジスタと、第2のトランジスタと、インバータ回路と、入力データに応じて前記第1のトランジスタのゲートの電位を制御する機能を有する回路と、を有し、

前記第1のトランジスタの第1の端子は、前記第1の電位が供給される第1の配線と電気的に接続され、

前記第1のトランジスタの第2の端子は、前記オペアンプの第2の入力端子と電気的に接続され、

前記第1のトランジスタのゲートは、前記インバータ回路を介して前記第2のトランジスタのゲートと電気的に接続され、

前記第2のトランジスタの第1の端子は、第3の電位が供給される第2の配線と電気的に接続され、

前記第2のトランジスタの第2の端子は、前記オペアンプの第2の入力端子と電気的に接続され、

前記書き込み動作時に前記第1のトランジスタがオンになる時間を制御することによって、前記メモリトランジスタの閾値電圧を制御することを特徴とする半導体装置。 - メモリトランジスタと、第1の電流源と、オペアンプと、選択トランジスタと、を有し、

前記第1の電流源は、前記メモリトランジスタのドレイン電極と電気的に接続され、

前記オペアンプの出力端子は、前記選択トランジスタを介して前記メモリトランジスタのゲートと電気的に接続され、

前記オペアンプの第1の入力端子は、前記第1の電流源と電気的に接続され、

前記オペアンプの第2の入力端子には、書き込み動作時において前記メモリトランジスタの閾値電圧を変動させる場合には第1の電位が供給され、且つ読み出し動作時において第2の電位が供給され、

前記第2の電位は、前記第1の電位よりも低く、

前記書き込み動作時に前記オペアンプの第2の入力端子に前記第1の電位を供給する時間を制御することによって、前記メモリトランジスタの閾値電圧を制御することを特徴とする半導体装置。 - メモリトランジスタと、第1の電流源と、オペアンプと、選択トランジスタと、を有し、

前記第1の電流源は、前記メモリトランジスタのドレイン電極と電気的に接続され、

前記オペアンプの出力端子は、前記選択トランジスタを介して前記メモリトランジスタのゲートと電気的に接続され、

前記オペアンプの第1の入力端子は、前記第1の電流源と電気的に接続され、

前記オペアンプの第2の入力端子には、書き込み動作時において前記メモリトランジスタの閾値電圧を変動させる場合には第1の電位が供給され、且つ読み出し動作時において第2の電位が供給され、

前記第2の電位は、前記第1の電位よりも低く、

前記第1の電位を前記オペアンプの第2の入力端子に供給するかしないかを制御する第1のトランジスタと、

第3の電位を前記オペアンプの第2の入力端子に供給するかしないかを制御する第2のトランジスタと、

入力データに応じて前記第1のトランジスタの導通状態及び前記第2のトランジスタの導通状態を制御する機能を有する回路と、を有し、

前記書き込み動作時に前記第1のトランジスタがオンになる時間を制御することによって、前記メモリトランジスタの閾値電圧を制御することを特徴とする半導体装置。 - メモリトランジスタと、第1の電流源と、オペアンプと、選択トランジスタと、を有し、

前記第1の電流源は、前記メモリトランジスタのドレイン電極と電気的に接続され、

前記オペアンプの出力端子は、前記選択トランジスタを介して前記メモリトランジスタのゲートと電気的に接続され、

前記オペアンプの第1の入力端子は、前記第1の電流源と電気的に接続され、

前記オペアンプの第2の入力端子には、書き込み動作時において前記メモリトランジスタの閾値電圧を変動させる場合には第1の電位が供給され、且つ読み出し動作時において第2の電位が供給され、

前記第2の電位は、前記第1の電位よりも低く、

第1のトランジスタと、第2のトランジスタと、インバータ回路と、入力データに応じて前記第1のトランジスタのゲートの電位を制御する機能を有する回路と、を有し、

前記第1のトランジスタの第1の端子は、前記第1の電位が供給される第1の配線と電気的に接続され、

前記第1のトランジスタの第2の端子は、前記オペアンプの第2の入力端子と電気的に接続され、

前記第1のトランジスタのゲートは、前記インバータ回路を介して前記第2のトランジスタのゲートと電気的に接続され、

前記第2のトランジスタの第1の端子は、第3の電位が供給される第2の配線と電気的に接続され、

前記第2のトランジスタの第2の端子は、前記オペアンプの第2の入力端子と電気的に接続され、

前記書き込み動作時に前記第1のトランジスタがオンになる時間を制御することによって、前記メモリトランジスタの閾値電圧を制御することを特徴とする半導体装置。 - 請求項1乃至請求項6のいずれか一項において、

前記第1の電流源と前記メモリトランジスタのドレイン電極との間には、前記書き込み動作時及び前記読み出し動作時においてオンになり、且つ消去動作時においてオフになる第1のスイッチが設けられ、

前記オペアンプの出力端子と前記メモリトランジスタのゲートとの間には、前記書き込み動作時及び前記読み出し動作時においてオンになり、且つ前記消去動作時においてオフになる第2のスイッチが設けられ、

前記メモリトランジスタのゲートは、前記書き込み動作時及び前記読み出し動作時においてオフになり、且つ前記消去動作時においてオンになる第3のスイッチを介して、消去用電位が供給される第3の配線と電気的に接続されることを特徴とする半導体装置。 - 請求項1乃至請求項6のいずれか一項において、

前記オペアンプは、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第2の電流源と、を有し、

前記第3のトランジスタの第1の端子は、第3の配線と電気的に接続され、

前記第3のトランジスタの第2の端子は、前記第3のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタの第1の端子は、前記第3の配線と電気的に接続され、

前記第4のトランジスタの第2の端子は、前記オペアンプの出力端子と電気的に接続され、

前記第4のトランジスタのゲートは、前記第3のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタの第1の端子は、前記書き込み動作時及び前記読み出し動作時においてオンになり、且つ消去動作時においてオフになる第1のスイッチを介して前記第2の電流源と電気的に接続され、

前記第5のトランジスタの第2の端子は、前記第3のトランジスタの第2の端子と電気的に接続され、

前記第5のトランジスタのゲートは、前記オペアンプの第1の入力端子と電気的に接続され、

前記第6のトランジスタの第1の端子は、前記第5のトランジスタの第1の端子と電気的に接続され、

前記第6のトランジスタの第2の端子は、前記第4のトランジスタの第2の端子と電気的に接続され、

前記第6のトランジスタのゲートは、前記オペアンプの第2の入力端子と電気的に接続されることを特徴とする半導体装置。 - 請求項8において、

前記第1の電流源と前記メモリトランジスタのドレイン電極との間には、前記書き込み動作時及び前記読み出し動作時においてオンになり、且つ前記消去動作時においてオフになる第2のスイッチが設けられ、

前記オペアンプの出力端子と前記メモリトランジスタのゲートとの間には、前記書き込み動作時及び前記読み出し動作時においてオンになり、且つ前記消去動作時においてオフになる第3のスイッチが設けられ、

前記メモリトランジスタのゲートは、前記書き込み動作時及び前記読み出し動作時においてオフになり、且つ前記消去動作時においてオンになる第4のスイッチを介して、消去用電位が供給される第4の配線と電気的に接続されることを特徴とする半導体装置。 - メモリトランジスタと、選択トランジスタと、第1の電流源と、オペアンプと、第1のスイッチと、第2のスイッチと、第3のスイッチと、第4のスイッチと、第5のスイッチと、第6のスイッチと、第7のスイッチと、第8のスイッチと、を有し、

前記第1の電流源は、前記第1のスイッチと前記第2のスイッチと前記選択トランジスタとを順に介して前記メモリトランジスタのドレイン電極と電気的に接続され、

前記オペアンプの出力端子は、前記第3のスイッチと前記第4のスイッチとを順に介して前記メモリトランジスタのゲートと電気的に接続され、

前記オペアンプの第1の入力端子は、前記第1の電流源と電気的に接続され、

前記オペアンプの第2の入力端子には、書き込み動作時において前記メモリトランジスタの閾値電圧を変動させる場合には第1の電位が供給され、且つ読み出し動作時において第2の電位が供給され、

前記メモリトランジスタのゲートは、前記第5のスイッチ及び前記第6のスイッチを介して第1の配線と電気的に接続され、

前記メモリトランジスタのゲートは、前記第7のスイッチ及び前記第8のスイッチを介して消去用電位が供給される第2の配線と電気的に接続され、

前記書き込み動作時において、前記第1のスイッチ、前記第2のスイッチ、前記第3のスイッチ、前記第4のスイッチ、前記第6のスイッチ及び前記第8のスイッチがオンになり、前記第5のスイッチ及び前記第7のスイッチがオフになり、

前記読み出し動作時において、前記第1のスイッチ、前記第2のスイッチ、前記第3のスイッチ、前記第4のスイッチ、前記第5のスイッチ、前記第6のスイッチ及び前記第8のスイッチがオンになり、前記第7のスイッチがオフになり、

消去動作時において、前記第1のスイッチ、前記第3のスイッチ、前記第6のスイッチ、前記第7のスイッチ及び前記第8のスイッチがオンになり、前記第2のスイッチ、前記第4のスイッチ及び前記第5のスイッチがオフになり、

前記第2の電位は、前記第1の電位よりも低く、

前記書き込み動作時に前記オペアンプの第2の入力端子に前記第1の電位を供給する時間を制御することによって、前記メモリトランジスタの閾値電圧を制御することを特徴とする半導体装置。 - メモリトランジスタと、選択トランジスタと、第1の電流源と、オペアンプと、第1のスイッチと、第2のスイッチと、第3のスイッチと、第4のスイッチと、第5のスイッチと、第6のスイッチと、第7のスイッチと、第8のスイッチと、を有し、

前記第1の電流源は、前記第1のスイッチと前記第2のスイッチと前記選択トランジスタとを順に介して前記メモリトランジスタのドレイン電極と電気的に接続され、

前記オペアンプの出力端子は、前記第3のスイッチと前記第4のスイッチとを順に介して前記メモリトランジスタのゲートと電気的に接続され、

前記オペアンプの第1の入力端子は、前記第1の電流源と電気的に接続され、

前記オペアンプの第2の入力端子には、書き込み動作時において前記メモリトランジスタの閾値電圧を変動させる場合には第1の電位が供給され、且つ読み出し動作時において第2の電位が供給され、

前記メモリトランジスタのゲートは、前記第5のスイッチ及び前記第6のスイッチを介して第1の配線と電気的に接続され、

前記メモリトランジスタのゲートは、前記第7のスイッチ及び前記第8のスイッチを介して消去用電位が供給される第2の配線と電気的に接続され、

前記書き込み動作時において、前記第1のスイッチ、前記第2のスイッチ、前記第3のスイッチ、前記第4のスイッチ、前記第6のスイッチ及び前記第8のスイッチがオンになり、前記第5のスイッチ及び前記第7のスイッチがオフになり、

前記読み出し動作時において、前記第1のスイッチ、前記第2のスイッチ、前記第3のスイッチ、前記第4のスイッチ、前記第5のスイッチ、前記第6のスイッチ及び前記第8のスイッチがオンになり、前記第7のスイッチがオフになり、

消去動作時において、前記第1のスイッチ、前記第3のスイッチ、前記第6のスイッチ、前記第7のスイッチ及び前記第8のスイッチがオンになり、前記第2のスイッチ、前記第4のスイッチ及び前記第5のスイッチがオフになり、

前記第2の電位は、前記第1の電位よりも低く、

前記第1の電位を前記オペアンプの第2の入力端子に供給するかしないかを制御する第1のトランジスタと、

第3の電位を前記オペアンプの第2の入力端子に供給するかしないかを制御する第2のトランジスタと、

入力データに応じて前記第1のトランジスタの導通状態及び前記第2のトランジスタの導通状態を制御する機能を有する回路と、を有し、

前記書き込み動作時に前記第1のトランジスタがオンになる時間を制御することによって、前記メモリトランジスタの閾値電圧を制御することを特徴とする半導体装置。 - メモリトランジスタと、選択トランジスタと、第1の電流源と、オペアンプと、第1のスイッチと、第2のスイッチと、第3のスイッチと、第4のスイッチと、第5のスイッチと、第6のスイッチと、第7のスイッチと、第8のスイッチと、を有し、

前記第1の電流源は、前記第1のスイッチと前記第2のスイッチと前記選択トランジスタとを順に介して前記メモリトランジスタのドレイン電極と電気的に接続され、

前記オペアンプの出力端子は、前記第3のスイッチと前記第4のスイッチとを順に介して前記メモリトランジスタのゲートと電気的に接続され、

前記オペアンプの第1の入力端子は、前記第1の電流源と電気的に接続され、

前記オペアンプの第2の入力端子には、書き込み動作時において前記メモリトランジスタの閾値電圧を変動させる場合には第1の電位が供給され、且つ読み出し動作時において第2の電位が供給され、

前記メモリトランジスタのゲートは、前記第5のスイッチ及び前記第6のスイッチを介して第1の配線と電気的に接続され、

前記メモリトランジスタのゲートは、前記第7のスイッチ及び前記第8のスイッチを介して消去用電位が供給される第2の配線と電気的に接続され、

前記書き込み動作時において、前記第1のスイッチ、前記第2のスイッチ、前記第3のスイッチ、前記第4のスイッチ、前記第6のスイッチ及び前記第8のスイッチがオンになり、前記第5のスイッチ及び前記第7のスイッチがオフになり、

前記読み出し動作時において、前記第1のスイッチ、前記第2のスイッチ、前記第3のスイッチ、前記第4のスイッチ、前記第5のスイッチ、前記第6のスイッチ及び前記第8のスイッチがオンになり、前記第7のスイッチがオフになり、

消去動作時において、前記第1のスイッチ、前記第3のスイッチ、前記第6のスイッチ、前記第7のスイッチ及び前記第8のスイッチがオンになり、前記第2のスイッチ、前記第4のスイッチ及び前記第5のスイッチがオフになり、

前記第2の電位は、前記第1の電位よりも低く、

第1のトランジスタと、第2のトランジスタと、インバータ回路と、入力データに応じて前記第1のトランジスタのゲートの電位を制御する機能を有する回路と、を有し、

前記第1のトランジスタの第1の端子は、前記第1の電位が供給される第3の配線と電気的に接続され、

前記第1のトランジスタの第2の端子は、前記オペアンプの第2の入力端子と電気的に接続され、

前記第1のトランジスタのゲートは、前記インバータ回路を介して前記第2のトランジスタのゲートと電気的に接続され、

前記第2のトランジスタの第1の端子は、第3の電位が供給される第4の配線と電気的に接続され、

前記第2のトランジスタの第2の端子は、前記オペアンプの第2の入力端子と電気的に接続され、

前記書き込み動作時に前記第1のトランジスタがオンになる時間を制御することによって、前記メモリトランジスタの閾値電圧を制御することを特徴とする半導体装置。 - 請求項10乃至請求項12のいずれか一項において、

前記オペアンプは、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第2の電流源と、を有し、

前記第3のトランジスタの第1の端子は、第5の配線と電気的に接続され、

前記第3のトランジスタの第2の端子は、前記第3のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタの第1の端子は、前記第5の配線と電気的に接続され、

前記第4のトランジスタの第2の端子は、前記オペアンプの出力端子と電気的に接続され、

前記第4のトランジスタのゲートは、前記第3のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタの第1の端子は、第9のスイッチと第10のスイッチとを順に介して前記第2の電流源と電気的に接続され、

前記第5のトランジスタの第2の端子は、前記第3のトランジスタの第2の端子と電気的に接続され、

前記第5のトランジスタのゲートは、前記オペアンプの第1の入力端子と電気的に接続され、

前記第6のトランジスタの第1の端子は、前記第5のトランジスタの第1の端子と電気的に接続され、

前記第6のトランジスタの第2の端子は、前記第4のトランジスタの第2の端子と電気的に接続され、

前記第6のトランジスタのゲートは、前記オペアンプの第2の入力端子と電気的に接続され、

前記書き込み動作時及び前記読み出し動作時において、前記第9のスイッチ及び前記第10のスイッチはオンになり、

前記消去動作時において、前記第9のスイッチはオフになり、前記第10のスイッチはオンになることを特徴とする半導体装置。 - 請求項1乃至請求項13のいずれか一項において、

前記読み出し動作時における前記第1の電流源の電流値は、前記書き込み動作時における前記第1の電流源の電流値よりも小さいことを特徴とする半導体装置。

Priority Applications (8)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000314369A JP4663094B2 (ja) | 2000-10-13 | 2000-10-13 | 半導体装置 |

| US09/976,770 US6556475B2 (en) | 2000-10-13 | 2001-10-12 | Non-volatile memory and semiconductor device |

| US10/383,209 US6914818B2 (en) | 2000-10-13 | 2003-03-06 | Non-volatile memory and semiconductor device |

| US11/109,325 US7298652B2 (en) | 2000-10-13 | 2005-04-19 | Non-volatile memory and semiconductor device |

| US11/924,090 US7512006B2 (en) | 2000-10-13 | 2007-10-25 | Non-volatile memory and semiconductor device |

| US12/407,539 US7855919B2 (en) | 2000-10-13 | 2009-03-19 | Non-volatile memory and semiconductor device |

| US12/814,761 US8054690B2 (en) | 2000-10-13 | 2010-06-14 | Non-volatile memory and semiconductor device |

| US13/288,383 US8315101B2 (en) | 2000-10-13 | 2011-11-03 | Non-volatile memory and semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000314369A JP4663094B2 (ja) | 2000-10-13 | 2000-10-13 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002124091A JP2002124091A (ja) | 2002-04-26 |

| JP2002124091A5 JP2002124091A5 (ja) | 2007-11-01 |

| JP4663094B2 true JP4663094B2 (ja) | 2011-03-30 |

Family

ID=18793641

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000314369A Expired - Fee Related JP4663094B2 (ja) | 2000-10-13 | 2000-10-13 | 半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (7) | US6556475B2 (ja) |

| JP (1) | JP4663094B2 (ja) |

Families Citing this family (49)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4663094B2 (ja) | 2000-10-13 | 2011-03-30 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| TW559814B (en) * | 2001-05-31 | 2003-11-01 | Semiconductor Energy Lab | Nonvolatile memory and method of driving the same |

| EP1365417A1 (en) | 2002-05-13 | 2003-11-26 | STMicroelectronics S.r.l. | Programming method of the memory cells in a multilevel non-volatile memory device |

| EP1363292B1 (en) * | 2002-05-13 | 2012-08-08 | STMicroelectronics Srl | Programming method of the memory cells in a multilevel non-volatile memory device |

| JP4236152B2 (ja) * | 2002-07-29 | 2009-03-11 | 富士フイルム株式会社 | 固体撮像素子 |

| JP4086583B2 (ja) * | 2002-08-08 | 2008-05-14 | シャープ株式会社 | 不揮発性半導体メモリ装置およびデータ書き込み制御方法 |

| KR100476928B1 (ko) * | 2002-08-14 | 2005-03-16 | 삼성전자주식회사 | 비트라인 커플링과 로딩 효과에 대해 안정적인 소스라인을 갖는 플레쉬 메모리 어레이 |

| US7630237B2 (en) * | 2003-02-06 | 2009-12-08 | Sandisk Corporation | System and method for programming cells in non-volatile integrated memory devices |

| US7453427B2 (en) * | 2003-05-09 | 2008-11-18 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and driving method thereof |

| WO2004107078A1 (ja) * | 2003-05-14 | 2004-12-09 | Semiconductor Energy Laboratory Co., Ltd. | 半導体装置 |

| WO2004109638A1 (ja) * | 2003-06-06 | 2004-12-16 | Semiconductor Energy Laboratory Co., Ltd. | 半導体装置 |

| US8350785B2 (en) | 2003-09-12 | 2013-01-08 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and driving method of the same |

| JP4649156B2 (ja) * | 2004-09-28 | 2011-03-09 | シチズンホールディングス株式会社 | 半導体装置およびそのデータ書き込み方法 |

| WO2006064859A1 (en) * | 2004-12-14 | 2006-06-22 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP4884784B2 (ja) * | 2005-01-28 | 2012-02-29 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法及び半導体装置 |

| JP2006286118A (ja) * | 2005-04-01 | 2006-10-19 | Matsushita Electric Ind Co Ltd | 閾値電圧制御機能を有する不揮発性記憶装置 |

| US7656710B1 (en) | 2005-07-14 | 2010-02-02 | Sau Ching Wong | Adaptive operations for nonvolatile memories |

| EP1793367A3 (en) * | 2005-12-02 | 2009-08-26 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US7968932B2 (en) | 2005-12-26 | 2011-06-28 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US7349264B2 (en) * | 2005-12-28 | 2008-03-25 | Sandisk Corporation | Alternate sensing techniques for non-volatile memories |

| US7616481B2 (en) * | 2005-12-28 | 2009-11-10 | Sandisk Corporation | Memories with alternate sensing techniques |

| US8077521B2 (en) * | 2006-03-16 | 2011-12-13 | Freescale Semiconductor, Inc. | Bitline current generator for a non-volatile memory array and a non-volatile memory array |

| EP2002445B1 (en) * | 2006-03-16 | 2011-04-27 | Freescale Semiconductor, Inc. | A non-volatile memory device and programmable voltage reference for a non-volatile memory device |

| WO2007104335A1 (en) * | 2006-03-16 | 2007-09-20 | Freescale Semiconductor, Inc. | A wordline driver for a non-volatile memory device, a non-volatile memory device and method |

| US7692973B2 (en) * | 2006-03-31 | 2010-04-06 | Semiconductor Energy Laboratory Co., Ltd | Semiconductor device |

| US7554854B2 (en) * | 2006-03-31 | 2009-06-30 | Semiconductor Energy Laboratory Co., Ltd. | Method for deleting data from NAND type nonvolatile memory |

| US7760552B2 (en) * | 2006-03-31 | 2010-07-20 | Semiconductor Energy Laboratory Co., Ltd. | Verification method for nonvolatile semiconductor memory device |

| US7671405B2 (en) * | 2006-12-26 | 2010-03-02 | Spansion Llc | Deep bitline implant to avoid program disturb |

| US7626868B1 (en) * | 2007-05-04 | 2009-12-01 | Flashsilicon, Incorporation | Level verification and adjustment for multi-level cell (MLC) non-volatile memory (NVM) |

| KR101508492B1 (ko) * | 2008-05-09 | 2015-05-18 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 비휘발성 반도체 기억 장치 |

| US8188535B2 (en) * | 2008-05-16 | 2012-05-29 | Semiconductor Energy Laboratory Co., Ltd. | Nonvolatile semiconductor memory device and manufacturing method thereof |

| JP5191834B2 (ja) | 2008-08-12 | 2013-05-08 | セイコーインスツル株式会社 | 半導体不揮発性記憶装置 |

| JP2010079977A (ja) * | 2008-09-25 | 2010-04-08 | Toppan Printing Co Ltd | 定電流型電源回路を有する不揮発性半導体メモリ装置 |

| US8198666B2 (en) * | 2009-02-20 | 2012-06-12 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device including a nonvolatile memory element having first, second and third insulating films |

| US8110029B2 (en) * | 2009-05-08 | 2012-02-07 | Alstom Technology Ltd | Integrated mercury control system |

| KR101932909B1 (ko) * | 2010-03-04 | 2018-12-27 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 메모리 장치 및 반도체 장치 |

| WO2011114866A1 (en) * | 2010-03-17 | 2011-09-22 | Semiconductor Energy Laboratory Co., Ltd. | Memory device and semiconductor device |

| US8411524B2 (en) | 2010-05-06 | 2013-04-02 | Micron Technology, Inc. | Techniques for refreshing a semiconductor memory device |

| US8416624B2 (en) | 2010-05-21 | 2013-04-09 | SanDisk Technologies, Inc. | Erase and programming techniques to reduce the widening of state distributions in non-volatile memories |

| JP6099368B2 (ja) | 2011-11-25 | 2017-03-22 | 株式会社半導体エネルギー研究所 | 記憶装置 |

| JP2014049151A (ja) * | 2012-08-30 | 2014-03-17 | Ememory Technology Inc | フラッシュメモリ |

| US8971147B2 (en) | 2012-10-30 | 2015-03-03 | Freescale Semiconductor, Inc. | Control gate word line driver circuit for multigate memory |

| KR102178068B1 (ko) | 2012-11-06 | 2020-11-12 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 구동 방법 |

| KR102112367B1 (ko) | 2013-02-12 | 2020-05-18 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| US9218883B2 (en) * | 2013-03-15 | 2015-12-22 | West Virginia University | Continuous-time floating gate memory cell programming |

| WO2014157019A1 (en) | 2013-03-25 | 2014-10-02 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP6442321B2 (ja) | 2014-03-07 | 2018-12-19 | 株式会社半導体エネルギー研究所 | 半導体装置及びその駆動方法、並びに電子機器 |

| US10258411B1 (en) | 2014-04-18 | 2019-04-16 | Riverpoint Medical, Llc | Video processing headband |

| KR102583770B1 (ko) * | 2016-09-12 | 2023-10-06 | 삼성디스플레이 주식회사 | 메모리 트랜지스터 및 이를 갖는 표시장치 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5748534A (en) * | 1996-03-26 | 1998-05-05 | Invox Technology | Feedback loop for reading threshold voltage |

| JP2001015716A (ja) * | 1999-06-30 | 2001-01-19 | Matsushita Electric Ind Co Ltd | 半導体記憶装置 |

Family Cites Families (43)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5120346B2 (ja) | 1972-06-23 | 1976-06-24 | ||

| US5050124A (en) * | 1986-09-30 | 1991-09-17 | Kabushiki Kaisha Toshiba | Semiconductor memory having load transistor circuit |

| US4999525A (en) * | 1989-02-10 | 1991-03-12 | Intel Corporation | Exclusive-or cell for pattern matching employing floating gate devices |

| JPH0453096A (ja) * | 1990-06-19 | 1992-02-20 | Toshiba Corp | アナログ記憶装置 |

| US5130777A (en) * | 1991-01-04 | 1992-07-14 | Actel Corporation | Apparatus for improving antifuse programming yield and reducing antifuse programming time |

| TW208086B (ja) * | 1991-03-21 | 1993-06-21 | Shibata Naoru | |

| US5231315A (en) * | 1991-10-29 | 1993-07-27 | Lattice Semiconductor Corporation | Temperature compensated CMOS voltage to current converter |

| US6222762B1 (en) * | 1992-01-14 | 2001-04-24 | Sandisk Corporation | Multi-state memory |

| EP0576774B1 (en) * | 1992-06-30 | 1999-09-15 | STMicroelectronics S.r.l. | Voltage regulator for memory devices |

| JP3373632B2 (ja) * | 1993-03-31 | 2003-02-04 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| US5488415A (en) * | 1993-07-09 | 1996-01-30 | Olympus Optical Co., Ltd. | Solid-state image pickup device having a photoelectric conversion detection cell with high sensitivity |

| JP3289748B2 (ja) * | 1993-11-30 | 2002-06-10 | 直 柴田 | 半導体装置 |

| JP3570692B2 (ja) * | 1994-01-18 | 2004-09-29 | ローム株式会社 | 不揮発性メモリ |

| JP3563452B2 (ja) * | 1994-08-10 | 2004-09-08 | 株式会社東芝 | セル閾値分布検知回路およびセル閾値分布検知方法 |

| US5495453A (en) * | 1994-10-19 | 1996-02-27 | Intel Corporation | Low power voltage detector circuit including a flash memory cell |

| WO1996030948A1 (fr) * | 1995-03-31 | 1996-10-03 | Tadashi Shibata | Memoire non volatile a semi-conducteurs |

| JP3710845B2 (ja) * | 1995-06-21 | 2005-10-26 | 株式会社ルネサステクノロジ | 半導体記憶装置 |

| US5815435A (en) * | 1995-10-10 | 1998-09-29 | Information Storage Devices, Inc. | Storage cell for analog recording and playback |

| KR100217917B1 (ko) | 1995-12-20 | 1999-09-01 | 김영환 | 플래쉬 메모리셀의 문턱전압 조정회로 |

| JP3920943B2 (ja) * | 1996-05-10 | 2007-05-30 | 株式会社ルネサステクノロジ | 不揮発性半導体記憶装置 |

| JP3543493B2 (ja) * | 1996-06-07 | 2004-07-14 | 株式会社デンソー | 電子回路の動作特性補正装置 |

| JP2845212B2 (ja) * | 1996-08-29 | 1999-01-13 | 日本電気株式会社 | 半導体記憶装置 |

| EP0833348B1 (en) | 1996-09-30 | 2003-07-09 | STMicroelectronics S.r.l. | Method and circuit for checking multilevel programming of floating-gate nonvolatile memory cells, particlarly flash cells |

| JPH10154803A (ja) * | 1996-11-25 | 1998-06-09 | Toshiba Corp | 不揮発性半導体メモリ |

| DE69723227T2 (de) * | 1997-04-14 | 2004-06-03 | Stmicroelectronics S.R.L., Agrate Brianza | Hochpräzisionsanalogleseschaltkreis für Speichermatrizen, insbesondere für Flash-Analogspeichermatrizen |

| EP0908895A1 (en) | 1997-10-09 | 1999-04-14 | STMicroelectronics S.r.l. | Controlled hot-electron writing method for non-volatile memory cells |

| ITMI981193A1 (it) * | 1998-05-29 | 1999-11-29 | St Microelectronics Srl | Dispositivo circuitale e relativo metodo per la propgrammazione di una cella di memoria non volatile a singola tensione di |

| US6194967B1 (en) * | 1998-06-17 | 2001-02-27 | Intel Corporation | Current mirror circuit |

| IT1305181B1 (it) * | 1998-11-13 | 2001-04-10 | St Microelectronics Srl | Dispositivo e metodo di programmazione di celle di memoria nonvolatile con generazione automatica della tensione di programmazione. |

| JP2000348493A (ja) * | 1999-06-03 | 2000-12-15 | Fujitsu Ltd | 不揮発性メモリ回路 |

| JP3933817B2 (ja) * | 1999-06-24 | 2007-06-20 | 富士通株式会社 | 不揮発性メモリ回路 |

| US6108241A (en) * | 1999-07-01 | 2000-08-22 | Micron Technology, Inc. | Leakage detection in flash memory cell |

| JP3954245B2 (ja) * | 1999-07-22 | 2007-08-08 | 株式会社東芝 | 電圧発生回路 |

| JP3943790B2 (ja) * | 2000-02-24 | 2007-07-11 | 株式会社東芝 | 負電位検知回路及びこの負電位検知回路を備えた半導体記憶装置 |

| US6411549B1 (en) * | 2000-06-21 | 2002-06-25 | Atmel Corporation | Reference cell for high speed sensing in non-volatile memories |

| JP4043703B2 (ja) * | 2000-09-04 | 2008-02-06 | 株式会社ルネサステクノロジ | 半導体装置、マイクロコンピュータ、及びフラッシュメモリ |

| JP4663094B2 (ja) * | 2000-10-13 | 2011-03-30 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US6625057B2 (en) * | 2000-11-17 | 2003-09-23 | Kabushiki Kaisha Toshiba | Magnetoresistive memory device |

| JP2002184190A (ja) * | 2000-12-11 | 2002-06-28 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2002258955A (ja) * | 2001-02-27 | 2002-09-13 | Toshiba Corp | 半導体装置 |

| US6456557B1 (en) * | 2001-08-28 | 2002-09-24 | Tower Semiconductor Ltd | Voltage regulator for memory device |

| US7245536B1 (en) * | 2006-02-15 | 2007-07-17 | Catalyst Semiconductor, Inc. | Precision non-volatile CMOS reference circuit |

| US7428172B2 (en) * | 2006-07-17 | 2008-09-23 | Freescale Semiconductor, Inc. | Concurrent programming and program verification of floating gate transistor |

-

2000

- 2000-10-13 JP JP2000314369A patent/JP4663094B2/ja not_active Expired - Fee Related

-

2001

- 2001-10-12 US US09/976,770 patent/US6556475B2/en not_active Expired - Lifetime

-

2003

- 2003-03-06 US US10/383,209 patent/US6914818B2/en not_active Expired - Lifetime

-

2005

- 2005-04-19 US US11/109,325 patent/US7298652B2/en not_active Expired - Fee Related

-

2007

- 2007-10-25 US US11/924,090 patent/US7512006B2/en not_active Expired - Fee Related

-

2009

- 2009-03-19 US US12/407,539 patent/US7855919B2/en not_active Expired - Fee Related

-

2010

- 2010-06-14 US US12/814,761 patent/US8054690B2/en not_active Expired - Fee Related

-

2011

- 2011-11-03 US US13/288,383 patent/US8315101B2/en not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5748534A (en) * | 1996-03-26 | 1998-05-05 | Invox Technology | Feedback loop for reading threshold voltage |

| JP2001015716A (ja) * | 1999-06-30 | 2001-01-19 | Matsushita Electric Ind Co Ltd | 半導体記憶装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US6556475B2 (en) | 2003-04-29 |

| US20100296343A1 (en) | 2010-11-25 |

| US20020064070A1 (en) | 2002-05-30 |

| US20030128582A1 (en) | 2003-07-10 |

| US6914818B2 (en) | 2005-07-05 |

| US7855919B2 (en) | 2010-12-21 |

| US20080117680A1 (en) | 2008-05-22 |

| JP2002124091A (ja) | 2002-04-26 |

| US7298652B2 (en) | 2007-11-20 |

| US8054690B2 (en) | 2011-11-08 |

| US8315101B2 (en) | 2012-11-20 |

| US20050185462A1 (en) | 2005-08-25 |

| US7512006B2 (en) | 2009-03-31 |

| US20090180326A1 (en) | 2009-07-16 |

| US20120044763A1 (en) | 2012-02-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4663094B2 (ja) | 半導体装置 | |

| JP4907011B2 (ja) | 不揮発性メモリとその駆動方法、及び半導体装置 | |

| US6646922B2 (en) | Nonvolatile memory and method of driving the same | |

| JP2004079602A (ja) | トラップ層を有する不揮発性メモリ | |

| JP2014197442A (ja) | 不揮発性半導体記憶装置及びその読み出し方法 | |

| KR101357068B1 (ko) | 비휘발성 메모리들에 대한 바디 효과 감지 방법 | |

| JP4064154B2 (ja) | 不揮発性メモリ及びそれを用いた電子機器 | |

| JP2011233209A (ja) | 半導体記憶装置 | |

| KR100632637B1 (ko) | 낸드 플래시 메모리 소자의 소거 검증방법 및 그 낸드플래시 메모리 소자 | |

| JP2007042166A (ja) | 不揮発性半導体記憶装置及びその動作方法 | |

| JP2011070712A (ja) | Nand型フラッシュメモリ | |

| US20080056013A1 (en) | Method and Related Apparatus Capable of Improving Endurance of Memory | |

| JP2011222101A (ja) | 半導体記憶装置 | |

| JP2007164898A (ja) | 不揮発性半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070912 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070912 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100422 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100518 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100702 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101012 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101203 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101221 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110105 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140114 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |