JP4481284B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP4481284B2 JP4481284B2 JP2006254027A JP2006254027A JP4481284B2 JP 4481284 B2 JP4481284 B2 JP 4481284B2 JP 2006254027 A JP2006254027 A JP 2006254027A JP 2006254027 A JP2006254027 A JP 2006254027A JP 4481284 B2 JP4481284 B2 JP 4481284B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- film

- gate electrode

- forming

- silicide

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Thin Film Transistor (AREA)

Description

このような問題のうち後者を解決する方法としては、TFTのソース、ドレインに相当する部分のほとんどをシリサイドとしてしまう方法が提案されている。図2を用いてその例を説明する。

そして、熱アニール、ラピッド・サーマル・アニール、光アニール等の手段により、金属層29と活性層22を界面で反応させ、シリサイド層30および31が得られる。シリサイド層は図に示すように活性層の底部にまで到達するまで反応させても、途中でとまる程度に反応させてもよい。いずれにせよ、金属層29と活性層22の接触部分から反応が進行するので、側壁28の下部のソース、ドレインは半導体のままである。(図2(D))

最後に、公知の多層配線技術を用い、層間絶縁物33上に上層の配線34、35を形成する。上層の配線はシリサイド層30および31とコンタクト32aおよび32bをそれぞれ形成し、また、ゲイト配線25とコンタクト32cを形成する。

図2の例では、異方性エッチングによる側壁を用いる場合を示したが、他に、特開平7−169974、同7−169975、同7−218932等に開示されるようにゲイト電極の陽極酸化技術を用いてもよい。

ゲイト電極と、ゲイト電極よりも幅の広いゲイト絶縁膜と、

活性層中に形成されたN型もしくはP型の1対の不純物領域と、

ゲイト絶縁膜に対して自己整合的に形成された1対のシリサイド層と、

シリサイド層に密着し、かつ、選択的に設けられた金属層と、

を有し、シリサイド層は、金属層を構成する金属元素と珪素を主成分とする(本発明1)。

ゲイト電極より上の層には上層配線が設けられ、これと金属層とが少なくとも1つのコンタクトを有してもよい(本発明2)。例えば、上層配線とTFTのソース、ドレイン(シリサイド層)の間のコンタクトはかくするとよい。特に、図2で示した従来の例で問題となった極めて薄いシリサイド層と上層配線間のコンタクト不良を防ぐ上で効果的である。

一般的にゲイト電極・配線とソース、ドレインの配線とは層間絶縁物を隔てて形成されるので、その間のコンタクトを取るには、かならず、コンタクトホールが必要であったが、上記のように、ゲイト配線とソース、ドレインとの接続にコンタクトホールが不要となれば、回路配置上、有利なことは言うまでもない。

なお、金属層の材料には、チタン、モリブテン、タングステン、白金、クロム、コバルトから選ばれた元素を主成分とするとよい。

(1)活性層上にゲイト絶縁層とゲイト電極を形成する工程

(2)ゲイト絶縁層をエッチングして、ゲイト電極より幅の広いゲイト絶縁膜を形成する工程

(3)活性層に密着した金属層を形成する工程

(4)活性層と金属層を反応させてゲイト絶縁膜に対して自己整合的にシリサイド層を形成する工程

(5)金属層を選択的にエッチングする工程

前記金属層に密着して、前記金属層の材料よりも抵抗率の小さな材料の別の金属層を形成する工程

を設けると良いが、例えば、アルミニウムのような耐熱性の低い金属を用いる倍には、高温を伴う工程(4)は避ける方がよい。したがって、上記の工程は工程(4)と工程(5)の間に設けるとよい。

工程(2)においては、ゲイト配線も露呈されるような構成にすると、金属層がゲイト配線と接合を形成するので、適当な選択的エッチングにより、本発明3の構成を得ることができる。

(6)層間絶縁物を形成する工程

(7)層間絶縁物をエッチングして金属層に達するコンタクトホールを形成する工程

(8)コンタクトホールを介して金属層とコンタクトする上層の配線を形成する工程

(1)マスク合わせの問題が無い。

(2)コンタクト形成の際の諸問題がない。

といった有用性を得ることができる。かくして、TFTおよび半導体回路の特性、歩留り、信頼性、生産性を向上させることができる。

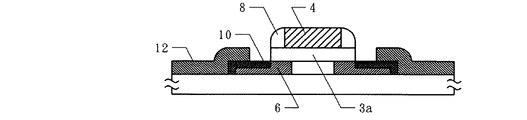

次に、Ti(チタン)の膜を成膜する。本実施例では厚さ3000〜6000ÅのTi膜9をスパッタリング法によって全面に形成する。(図1(C))

図では、シリサイド層10、11は活性層の底部に達する状態に描かれているが、反応を途中で止めて、図6に示すように、シリサイド層が活性層の底に到達しない構造としてもよい。いずれでも本質的な違いはない。(図6)

そして、熱アニールにより、Tiと活性層(珪素) を反応させ、シリサイド層50、51をソース46、ドレイン47に形成する。(図3(D))

さらに、全面に厚さ6000〜10000Åのアルミニウム膜52をスパッタ法で堆積する。(図3(E))

さらに、実施例1と同様に、多層配線技術により、上層の配線を設けてもよい。

さらに、Ti(チタン)の膜を成膜する。本実施例では、厚さ3000〜6000ÅのTi膜71をスパッタリング法によって全面に形成する。(図4(C))

この後、Ti膜を選択的にエッチングする。Tiのエッチング条件は実施例1と同じとする。上記の工程の結果、ソース69(シリサイド72)にコンタクト76aで接合する配線74およびドレイン70(シリサイド73)にコンタクト76bで接合する配線75を得る。配線75はコンタクト76cにおいてゲイト配線65とも接合する。(図4(E))

本実施例では、図7に示すように、シリサイド層72、73が活性層の底部に到達しないようにしてもよい。また、図4では明らかでないが、いずれにしても、図7に示すように、低濃度N型不純物領域66とシリサイド層72の間には、ソース(高濃度不純物領域)69が残存する。ドレイン近傍も同様である。このような構造はソース、ドレイン近傍の電界強度を低減する上で効果的である。(図7)

次に、N型の導電型を付与するための不純物P(燐)をイオン注入法により、活性層82をドーピングする。この際、ゲイト電極84a、85aがマスクとなり、自己整合的に不純物領域86、87、88が形成される。(図5(C))

この後、Ti膜を選択的にエッチングする。Tiのエッチング条件は実施例1と同じとする。上記の工程の結果、配線93、94を得る。(図5(E))

さらに、実施例1と同様に、多層配線技術により、層間絶縁物95を堆積し、これにコンタクトホールを形成し、配線96、97を設ける。(図5(F))

さらに、Ti(チタン)の膜を成膜する。本実施例では、厚さ3000〜6000ÅのTi膜129をスパッタリング法によって全面に形成する。(図9(B))

この後、Ti膜を選択的にエッチングし、配線133、134を得る。(図9(C))

次に、ゲイト絶縁膜123a、123bの一部(図に示すように、低濃度不純物領域127に重なる部分)をエッチングする。(図9(D))

特に本実施例では、中央の不純物領域の抵抗率を高濃度不純物のドーピングにより低下させることで、直列抵抗を減らすことに特徴がある。また、図9では、明らかではないが、図10に拡大して示すように、TFTの両端のシリサイド層130、132と低濃度不純物漁期126、128の間には、高濃度不純物領域136が残存する。このような構造はソース、ドレイン近傍の電界強度を低減する上で効果的である。(図10)

2・・・・・珪素半導体膜(活性層)

3・・・・・酸化珪素膜(ゲイト絶縁層)

3a、3b・ゲイト絶縁膜

4・・・・・ゲイト電極

5・・・・・ゲイト配線

6・・・・・ソース

7・・・・・ドレイン

8・・・・・側壁

9・・・・・Ti膜

10、11・・シリサイド層

12、13・・配線

14・・・・・コンタクト部分

15・・・・・コンタクトホール

16・・・・・層間絶縁物

17、18・・上層配線

Claims (9)

- 酸化珪素膜上の結晶性珪素膜上にゲイト絶縁層を形成し、

前記ゲイト絶縁層上に多結晶珪素膜をパターニングしてゲイト電極を形成し、

前記ゲイト電極をマスクとして前記結晶性珪素膜にN型又はP型の導電型を付与する不純物元素を添加してソース領域及びドレイン領域を形成し、

前記ゲイト電極の側面に側壁を形成し、

前記ゲイト電極及び前記側壁と重ならない前記ゲイト絶縁層をエッチングし、前記ソース領域及びドレイン領域を露出させ、

露出する前記ゲイト電極、前記ソース領域及びドレイン領域に接するように第1の金属膜を形成し、

熱アニールにより前記ソース領域と前記ドレイン領域にそれぞれシリサイドを形成するとともに前記ゲイト電極上部をシリサイド化させ、

前記第1の金属膜上に第2の金属膜を形成し、

前記第1及び第2の金属膜を選択的にエッチングして前記ソース領域に接合する第1の金属配線と、前記ドレイン領域に接合する第2の金属配線を形成することを特徴とする半導体装置の作製方法。 - 酸化珪素膜上の結晶性珪素膜上にゲイト絶縁層を形成し、

前記ゲイト絶縁層上に多結晶珪素膜をパターニングしてゲイト電極を形成し、

前記ゲイト電極をマスクとして前記結晶性珪素膜にN型又はP型の導電型を付与する不純物元素を添加してソース領域及びドレイン領域を形成し、

前記ゲイト電極の側面に側壁を形成し、

前記ゲイト電極及び前記側壁と重ならない前記ゲイト絶縁層をエッチングし、前記ソース領域及びドレイン領域を露出させ、

露出する前記ゲイト電極、前記ソース領域及びドレイン領域に接するように第1の金属膜を形成し、

熱アニールにより前記ソース領域と前記ドレイン領域にそれぞれシリサイドを形成するとともに前記ゲイト電極上部をシリサイド化させ、

前記第1の金属膜上に第2の金属膜を形成し、

前記第1及び第2の金属膜を選択的にエッチングして前記ソース領域に接合する第1の金属配線と、前記ドレイン領域に接合する第2の金属配線を形成し、

前記シリサイドと重ならない領域において前記第2の金属配線と接続される配線を形成することを特徴とする半導体装置の作製方法。 - 酸化珪素膜上の結晶性珪素膜上にゲイト絶縁層を形成し、

前記ゲイト絶縁層上に多結晶珪素膜をパターニングしてゲイト電極を形成し、

前記ゲイト電極をマスクとして前記結晶性珪素膜にN型又はP型の導電型を付与する不純物元素を添加してソース領域及びドレイン領域を形成し、

前記ゲイト電極の側面に側壁を形成し、

前記ゲイト電極及び前記側壁と重ならない前記ゲイト絶縁層をエッチングし、前記ソース領域及びドレイン領域を露出させ、

露出する前記ゲイト電極、前記ソース領域及びドレイン領域に接するように第1の金属膜を形成し、

熱アニールにより前記ソース領域と前記ドレイン領域にそれぞれシリサイドを形成するとともに前記ゲイト電極上部をシリサイド化させ、

前記第1の金属膜上に第2の金属膜を形成し、

前記第2の金属膜を選択的にエッチングした後に、エッチングした前記第2の金属膜をマスクとして前記第1の金属膜を選択的にエッチングし、その後、エッチングした前記第2の金属膜の側面のエッチングを行い前記ソース領域に接合する第1の金属配線と、前記ドレイン領域に接合する第2の金属配線を形成することを特徴とする半導体装置の作製方法。 - 酸化珪素膜上の結晶性珪素膜上にゲイト絶縁層を形成し、

前記ゲイト絶縁層上に多結晶珪素膜をパターニングしてゲイト電極を形成し、

前記ゲイト電極をマスクとして前記結晶性珪素膜にN型又はP型の導電型を付与する不純物元素を添加してソース領域及びドレイン領域を形成し、

前記ゲイト電極の側面に側壁を形成し、

前記ゲイト電極及び前記側壁と重ならない前記ゲイト絶縁層をエッチングし、前記ソース領域及びドレイン領域を露出させ、

露出する前記ゲイト電極、前記ソース領域及びドレイン領域に接するように第1の金属膜を形成し、

熱アニールにより前記ソース領域と前記ドレイン領域にそれぞれシリサイドを形成するとともに前記ゲイト電極上部をシリサイド化させ、

前記第1の金属膜上に第2の金属膜を形成し、

前記第2の金属膜を選択的にエッチングした後に、エッチングした前記第2の金属膜をマスクとして前記第1の金属膜を選択的にエッチングし、その後、エッチングした前記第2の金属膜の側面のエッチングを行い前記ソース領域に接合する第1の金属配線と、前記ドレイン領域に接合する第2の金属配線を形成し、

前記シリサイドと重ならない領域において前記第2の金属配線と接続される配線を形成することを特徴とする半導体装置の作製方法。 - 請求項1乃至4のいずれか一において、前記第1の金属膜は、チタン、モリブデン、タングステン、白金、クロム、コバルトから選択された元素を主成分に有することを特徴とする半導体装置の作製方法。

- 請求項1乃至4のいずれか一において、前記第1の金属膜はチタン膜であり、前記第2の金属膜は、アルミニウム膜であることを特徴とする半導体装置の作製方法。

- 請求項1乃至6のいずれか一において、前記側壁と重なり、かつ、前記ソース領域とチャネル形成領域の間と、前記ドレイン領域と前記チャネル形成領域の間にそれぞれ前記ソース領域及び前記ドレイン領域よりも低濃度の不純物領域を形成することを特徴とする半導体装置の作製方法。

- 請求項1乃至7のいずれか一において、前記ソース領域と前記ドレイン領域に形成された前記シリサイドは、前記半導体層の上面及び側面に形成されていることを特徴とする半導体装置の作製方法。

- 酸化珪素膜と、結晶性珪素膜と、第1及び第2のゲイト絶縁膜と、第1及び第2のゲイト電極と、第1及び第2の金属配線とを有し、

前記結晶性珪素膜は、第1乃至第3のシリサイド層と、第1及び第2の高濃度不純物領域と、第1及び第3の低濃度不純物領域と、第1及び第2のチャネル形成領域とを有し、

前記第1のチャネル形成領域は、前記第1のシリサイド層と前記第2のシリサイド層の間に設けられ、

前記第2のチャネル形成領域は、前記第2のシリサイド層と前記第3のシリサイド層の間に設けられ、

前記第1の低濃度不純物領域は、前記第1のシリサイド層と前記第1のチャネル形成領域の間に設けられ、

前記第3の低濃度不純物領域は、前記第2のチャネル形成領域と前記第3のシリサイド層の間に設けられ、

前記第1の高濃度不純物領域は、前記第1のチャネル形成領域と前記第2のシリサイド層の間に設けられ、

前記第2の高濃度不純物領域は、前記第2のシリサイド層と前記第2のチャネル形成領域の間に設けられている半導体装置の作製方法であって、

前記酸化珪素膜上の前記結晶性珪素膜上にゲイト絶縁層を形成し、

前記ゲイト絶縁層上に前記第1及び第2のゲイト電極を形成し、

前記第1及び第2のゲイト電極をマスクとして前記結晶性珪素膜に不純物元素をドープして前記第1及び第3の低濃度不純物領域、前記第1及び第2のチャネル形成領域の間の第2の低濃度不純物領域、前記第1のゲイト電極と重なる前記第1のチャネル形成領域、並びに、前記第2のゲイト電極と重なる前記第2のチャネル形成領域を形成し、

前記第1乃至第3の低濃度不純物領域のそれぞれが一部露出するように前記ゲイト絶縁層を選択的にエッチングして、前記第1のゲイト電極と重なる領域を含む領域に前記第1のゲイト絶縁膜、前記第2のゲイト電極と重なる領域を含む領域に前記第2のゲイト絶縁膜を形成し、

露出した前記第1乃至第3の低濃度不純物領域に接するように前記結晶性珪素膜上に金属膜を形成し、

熱アニールにより、前記金属膜と前記結晶性珪素膜を反応させ、前記第1乃至第3のシリサイド層を形成し、

前記第1乃至第3のシリサイド層を形成した後、前記金属膜を選択的にエッチングして前記第1のシリサイド層に接合する前記第1の金属配線と、前記第3のシリサイド層に接合する前記第2の金属配線を形成し、

前記第2の低濃度不純物領域に重なる領域の前記第1及び第2のゲイト絶縁膜を選択的にエッチングして前記第2の低濃度不純物領域を露出し、

露出した前記第2の低濃度不純物領域に不純物イオンをドープして前記第1及び第2の高濃度不純物領域を形成することを特徴とする半導体装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006254027A JP4481284B2 (ja) | 2006-09-20 | 2006-09-20 | 半導体装置の作製方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006254027A JP4481284B2 (ja) | 2006-09-20 | 2006-09-20 | 半導体装置の作製方法 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP8307443A Division JPH10135475A (ja) | 1996-10-31 | 1996-10-31 | 半導体装置およびその作製方法 |

Related Child Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009234439A Division JP4481361B2 (ja) | 2009-10-08 | 2009-10-08 | 半導体装置 |

| JP2010032871A Division JP4628485B2 (ja) | 2010-02-17 | 2010-02-17 | 薄膜トランジスタの作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006345003A JP2006345003A (ja) | 2006-12-21 |

| JP2006345003A5 JP2006345003A5 (ja) | 2009-11-26 |

| JP4481284B2 true JP4481284B2 (ja) | 2010-06-16 |

Family

ID=37641657

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006254027A Expired - Fee Related JP4481284B2 (ja) | 2006-09-20 | 2006-09-20 | 半導体装置の作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4481284B2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100875432B1 (ko) | 2007-05-31 | 2008-12-22 | 삼성모바일디스플레이주식회사 | 다결정 실리콘층의 제조 방법, 이를 이용하여 형성된박막트랜지스터, 그의 제조방법 및 이를 포함하는유기전계발광표시장치 |

| KR100889626B1 (ko) | 2007-08-22 | 2009-03-20 | 삼성모바일디스플레이주식회사 | 박막트랜지스터, 그의 제조방법, 이를 구비한유기전계발광표시장치, 및 그의 제조방법 |

| KR100889627B1 (ko) | 2007-08-23 | 2009-03-20 | 삼성모바일디스플레이주식회사 | 박막트랜지스터, 그의 제조방법, 및 이를 구비한유기전계발광표시장치 |

| JP2009260327A (ja) * | 2008-03-26 | 2009-11-05 | Advanced Lcd Technologies Development Center Co Ltd | 薄膜半導体装置およびその製造方法 |

| KR100982310B1 (ko) | 2008-03-27 | 2010-09-15 | 삼성모바일디스플레이주식회사 | 박막트랜지스터, 그의 제조방법, 및 이를 포함하는유기전계발광표시장치 |

| KR100989136B1 (ko) | 2008-04-11 | 2010-10-20 | 삼성모바일디스플레이주식회사 | 박막트랜지스터, 그의 제조방법, 및 이를 포함하는유기전계발광표시장치 |

| KR101002666B1 (ko) | 2008-07-14 | 2010-12-21 | 삼성모바일디스플레이주식회사 | 박막트랜지스터, 그의 제조방법, 및 이를 포함하는유기전계발광표시장치 |

| US8741702B2 (en) * | 2008-10-24 | 2014-06-03 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4788160A (en) * | 1987-03-31 | 1988-11-29 | Texas Instruments Incorporated | Process for formation of shallow silicided junctions |

| JP3506445B2 (ja) * | 1992-05-12 | 2004-03-15 | 沖電気工業株式会社 | 半導体装置の製造方法 |

| JP3152739B2 (ja) * | 1992-05-19 | 2001-04-03 | 株式会社日立製作所 | 半導体集積回路装置の製造方法 |

| JPH0766426A (ja) * | 1993-08-27 | 1995-03-10 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JPH07135323A (ja) * | 1993-10-20 | 1995-05-23 | Semiconductor Energy Lab Co Ltd | 薄膜状半導体集積回路およびその作製方法 |

| JP2833468B2 (ja) * | 1994-02-17 | 1998-12-09 | 日本電気株式会社 | 半導体装置の製造方法 |

| JPH07283400A (ja) * | 1994-04-08 | 1995-10-27 | Nippon Steel Corp | 半導体装置及びその製造方法 |

-

2006

- 2006-09-20 JP JP2006254027A patent/JP4481284B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2006345003A (ja) | 2006-12-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JPH10135475A (ja) | 半導体装置およびその作製方法 | |

| US5818070A (en) | Electro-optical device incorporating a peripheral dual gate electrode TFT driver circuit | |

| JP4481284B2 (ja) | 半導体装置の作製方法 | |

| CN107403758B (zh) | 阵列基板及其制备方法、显示装置 | |

| JPH10144928A (ja) | 半導体装置及びその作製方法 | |

| JP2008147516A (ja) | 薄膜トランジスタ及びその製造方法 | |

| TW200409364A (en) | Structure of thin film transistor array and driving circuits | |

| JP4723800B2 (ja) | アレイ基板の製造方法 | |

| JP3708837B2 (ja) | 半導体装置 | |

| JP4481361B2 (ja) | 半導体装置 | |

| JP4628485B2 (ja) | 薄膜トランジスタの作製方法 | |

| JPH11111992A (ja) | 薄膜トランジスタ、相補型薄膜トランジスタ、および薄膜トランジスタの製造方法 | |

| JP3708836B2 (ja) | 半導体装置 | |

| JPH1197699A (ja) | 薄膜トランジスタ | |

| JPS6370576A (ja) | 薄膜トランジスタおよびその製造方法 | |

| CN110047848B (zh) | 一种阵列基板及其制备方法 | |

| JP4610455B2 (ja) | 半導体装置 | |

| JP3868735B2 (ja) | 半導体装置 | |

| KR100477106B1 (ko) | 엠아이씨/엠아이엘씨를 이용한 평판표시장치의 제조방법 | |

| JP4197270B2 (ja) | 半導体集積回路の作製方法 | |

| JPH08204202A (ja) | 薄膜トランジスタの製造方法 | |

| JPH07321337A (ja) | 半導体集積回路およびその作製方法 | |

| JPH1197696A (ja) | 薄膜半導体装置 | |

| JP4249512B2 (ja) | 絶縁ゲイト型半導体装置 | |

| JP2002033488A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060927 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091008 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20091218 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100105 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100217 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100316 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100317 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130326 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130326 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130326 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140326 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |