JP4327096B2 - 外部接続用クリップを有する半導体装置 - Google Patents

外部接続用クリップを有する半導体装置 Download PDFInfo

- Publication number

- JP4327096B2 JP4327096B2 JP2004555560A JP2004555560A JP4327096B2 JP 4327096 B2 JP4327096 B2 JP 4327096B2 JP 2004555560 A JP2004555560 A JP 2004555560A JP 2004555560 A JP2004555560 A JP 2004555560A JP 4327096 B2 JP4327096 B2 JP 4327096B2

- Authority

- JP

- Japan

- Prior art keywords

- base

- semiconductor device

- conductive

- connection

- clip

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/492—Bases or plates or solder therefor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49541—Geometry of the lead-frame

- H01L23/49562—Geometry of the lead-frame for devices being provided for in H01L29/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/34—Strap connectors, e.g. copper straps for grounding power devices; Manufacturing methods related thereto

- H01L24/36—Structure, shape, material or disposition of the strap connectors prior to the connecting process

- H01L24/37—Structure, shape, material or disposition of the strap connectors prior to the connecting process of an individual strap connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/34—Strap connectors, e.g. copper straps for grounding power devices; Manufacturing methods related thereto

- H01L24/39—Structure, shape, material or disposition of the strap connectors after the connecting process

- H01L24/40—Structure, shape, material or disposition of the strap connectors after the connecting process of an individual strap connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/34—Strap connectors, e.g. copper straps for grounding power devices; Manufacturing methods related thereto

- H01L24/39—Structure, shape, material or disposition of the strap connectors after the connecting process

- H01L24/41—Structure, shape, material or disposition of the strap connectors after the connecting process of a plurality of strap connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0556—Disposition

- H01L2224/05568—Disposition the whole external layer protruding from the surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05573—Single external layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L2224/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

- H01L2224/29001—Core members of the layer connector

- H01L2224/29099—Material

- H01L2224/29198—Material with a principal constituent of the material being a combination of two or more materials in the form of a matrix with a filler, i.e. being a hybrid material, e.g. segmented structures, foams

- H01L2224/29199—Material of the matrix

- H01L2224/2929—Material of the matrix with a principal constituent of the material being a polymer, e.g. polyester, phenolic based polymer, epoxy

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L2224/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

- H01L2224/29001—Core members of the layer connector

- H01L2224/29099—Material

- H01L2224/29198—Material with a principal constituent of the material being a combination of two or more materials in the form of a matrix with a filler, i.e. being a hybrid material, e.g. segmented structures, foams

- H01L2224/29298—Fillers

- H01L2224/29299—Base material

- H01L2224/293—Base material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/29338—Base material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/29339—Silver [Ag] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/34—Strap connectors, e.g. copper straps for grounding power devices; Manufacturing methods related thereto

- H01L2224/36—Structure, shape, material or disposition of the strap connectors prior to the connecting process

- H01L2224/37—Structure, shape, material or disposition of the strap connectors prior to the connecting process of an individual strap connector

- H01L2224/37001—Core members of the connector

- H01L2224/37099—Material

- H01L2224/371—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/37138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/37147—Copper [Cu] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/34—Strap connectors, e.g. copper straps for grounding power devices; Manufacturing methods related thereto

- H01L2224/39—Structure, shape, material or disposition of the strap connectors after the connecting process

- H01L2224/40—Structure, shape, material or disposition of the strap connectors after the connecting process of an individual strap connector

- H01L2224/401—Disposition

- H01L2224/40151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/40221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/40225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73253—Bump and layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73255—Bump and strap connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/818—Bonding techniques

- H01L2224/81801—Soldering or alloying

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/838—Bonding techniques

- H01L2224/83801—Soldering or alloying

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/838—Bonding techniques

- H01L2224/8385—Bonding techniques using a polymer adhesive, e.g. an adhesive based on silicone, epoxy, polyimide, polyester

- H01L2224/83851—Bonding techniques using a polymer adhesive, e.g. an adhesive based on silicone, epoxy, polyimide, polyester being an anisotropic conductive adhesive

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/84—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a strap connector

- H01L2224/848—Bonding techniques

- H01L2224/84801—Soldering or alloying

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/84—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a strap connector

- H01L2224/848—Bonding techniques

- H01L2224/8485—Bonding techniques using a polymer adhesive, e.g. an adhesive based on silicone, epoxy, polyimide, polyester

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01047—Silver [Ag]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01057—Lanthanum [La]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01068—Erbium [Er]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01082—Lead [Pb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/013—Alloys

- H01L2924/014—Solder alloys

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1305—Bipolar Junction Transistor [BJT]

- H01L2924/13055—Insulated gate bipolar transistor [IGBT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1306—Field-effect transistor [FET]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1306—Field-effect transistor [FET]

- H01L2924/13091—Metal-Oxide-Semiconductor Field-Effect Transistor [MOSFET]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/30107—Inductance

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Lead Frames For Integrated Circuits (AREA)

- Structures Or Materials For Encapsulating Or Coating Semiconductor Devices Or Solid State Devices (AREA)

- Testing Or Measuring Of Semiconductors Or The Like (AREA)

- Die Bonding (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Description

Claims (17)

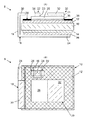

- 半導体装置において、

第1主表面及び前記第1主表面の反対側の第2主表面を有する半導体ダイと、

前記半導体ダイの前記第1主表面に配置された制御電極及び第1主電極と、

前記半導体ダイの前記第2主表面に配置された第2主電極と、

対応する電極に電気的に接続される第1基部、及び、外部部材に電気的に接続するための第1接続部をそれぞれ有する複数の第1導電クリップと、

前記制御電極及び前記第1主電極を覆うように配された保護層と、

前記複数の第1導電クリップの各第1導電クリップの前記第1基部と各電極とを接続する導電性接着素材の層とを備え、

前記各第1導電クリップの前記第1基部は、前記保護層の開口部を通じて、前記導電性接着素材の層によって前記制御電極及び前記第1主電極にそれぞれ電気的に接続されており、

少なくとも、前記制御電極に接続される第1導電クリップの第1基部は、前記制御電極を覆うように形成される前記保護層の開口部よりも大きく形成されており、

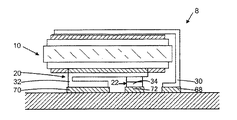

前記第2主電極は、前記第2基部、前記第2接続部、および前記第2基部と前記第2接続部とを接続する第2延長部を有する第2導電クリップに接続され、当該第2延長部は、少なくとも前記半導体ダイの第2主表面と前記半導体ダイの前記第1主表面との間に伸びるように形成されており、

前記第1導電クリップの第1接続部および第2導電クリップの第2接続部は、ともに前記第1主表面の直下に形成されており、

前記各第1導電クリップの第1基部及び第1接続部が、前記半導体ダイの外周より外にはみ出さずに当該外周よりも内側に形成されてなることを特徴とする半導体装置。 - 前記複数の第1導電クリップは、前記第1接続部と前記第1基部との間隔を空ける第1延長部をそれぞれ備えることを特徴とする請求項1に記載の半導体装置。

- 各第1導電クリップの前記第1延長部は、実質的に各第1導電クリップの前記第1基部に対して垂直に伸び、

各第1導電クリップの前記第1接続部は、実質的に各第1導電クリップの前記第1基部に対して並行であること

を特徴とする請求項2に記載の半導体装置。 - 前記半導体ダイは、MOSFETであること

を特徴とする請求項1に記載の半導体装置。 - 前記制御電極に接続される前記第1導電クリップの第1基部と、前記保護層との間に接着の層が設けられており、当該第1基部と半導体ダイとの間の接続が強化されてなることを特徴とする請求項1に記載の半導体装置。

- 前記導電性接着素材の層は、はんだから成ること

を特徴とする請求項1に記載の半導体装置。 - 前記導電性接着素材は、導電性エポキシから成ること

を特徴とする請求項1に記載の半導体装置。 - 前記各第1導電クリップは、前記第1基部と前記第1接続部とを繋ぐ第1延長部を備え、

前記第1延長部は、各第1基部及び各第1接続部と一体で形成されていること

を特徴とする請求項1に記載の半導体装置。 - 前記第1接続部の少なくとも一つは、バンプであること

を特徴とする請求項1に記載の半導体装置。 - 前記第1接続部の少なくとも一つは、平坦な接続面を有する円柱であること

を特徴とする請求項1に記載の半導体装置。 - 前記第1接続部の少なくとも一つは、平坦な接続面を有する一段高い部分であること

を特徴とする請求項1に記載の半導体装置。 - 半導体装置において、

第1主表面及び前記第1主表面の反対側の第2主表面を有する半導体ダイと、

前記半導体ダイの前記第1主表面に配置された第1主電極と、

前記半導体ダイにおける前記第1主表面と反対側の前記第2主表面に配置された第2主電極と、

前記第2主電極と電気的に接続される第2基部、外部部材に電気的に接触するための第2接続部、及び、前記第2基部と前記第2接続部を繋ぎ、前記半導体ダイの第1主表面と前記半導体ダイの第2主表面との間に伸びる第2延長部を備える第2導電クリップと、

前記第1主電極と電気的に接続される第1基部、及び、外部部材に電気的に接触するための第1接続部とを備える第1導電クリップと、を備え、

前記第1接続部および第2接続部は、前記第1主表面の直下に形成されており、

前記第1導電クリップの第1基部及び第1接続部が、前記半導体ダイの外周より外にはみ出さずに当該外周よりも内側に形成されており、

保護層が少なくとも一つの電極に配され、

前記保護層は、前記第1導電クリップの一つの第1基部と前記電極の一つとを電気的に接続する導電層を囲んでいること

を特徴とする半導体装置。 - 前記半導体ダイは、MOSFETであること

を特徴とする請求項12に記載の半導体装置。 - 前記制御電極に接続される前記第1導電クリップの第1基部と、前記保護層との間に接着の層が設けられており、当該第1基部と半導体ダイとの間の接続が強化されてなることを特徴とする請求項12に記載の半導体装置。

- 前記導電層は、はんだから成ること

を特徴とする請求項12に記載の半導体装置。 - 前記導電層は、導電性エポキシから成ること

を特徴とする請求項12に記載の半導体装置。 - 前記第1導電クリップは、第1基部と第1接続部とを繋ぐ第1延長部を備え、

前記第1延長部は、前記第1基部及び第1接続部と一体で形成されていること、

を特徴とする請求項15に記載の半導体装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/303,523 US6841865B2 (en) | 2002-11-22 | 2002-11-22 | Semiconductor device having clips for connecting to external elements |

| PCT/US2003/037314 WO2004049435A1 (en) | 2002-11-22 | 2003-11-21 | Semiconductor device having clips for connecting to external elements |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006507688A JP2006507688A (ja) | 2006-03-02 |

| JP2006507688A5 JP2006507688A5 (ja) | 2009-03-05 |

| JP4327096B2 true JP4327096B2 (ja) | 2009-09-09 |

Family

ID=32325025

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004555560A Expired - Fee Related JP4327096B2 (ja) | 2002-11-22 | 2003-11-21 | 外部接続用クリップを有する半導体装置 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US6841865B2 (ja) |

| JP (1) | JP4327096B2 (ja) |

| CN (1) | CN100421240C (ja) |

| AU (1) | AU2003295783A1 (ja) |

| DE (1) | DE10393769B4 (ja) |

| TW (1) | TWI228317B (ja) |

| WO (1) | WO2004049435A1 (ja) |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6930397B2 (en) * | 2001-03-28 | 2005-08-16 | International Rectifier Corporation | Surface mounted package with die bottom spaced from support board |

| US7208347B2 (en) * | 2003-02-28 | 2007-04-24 | Siemens Aktiengesellschaft | Connection technology for power semiconductors comprising a layer of electrically insulating material that follows the surface contours |

| US7692316B2 (en) | 2004-10-01 | 2010-04-06 | International Rectifier Corporation | Audio amplifier assembly |

| US20060145319A1 (en) * | 2004-12-31 | 2006-07-06 | Ming Sun | Flip chip contact (FCC) power package |

| CN100435324C (zh) * | 2004-12-20 | 2008-11-19 | 半导体元件工业有限责任公司 | 具有增强散热性的半导体封装结构 |

| JP4917296B2 (ja) * | 2005-10-28 | 2012-04-18 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| WO2007052199A1 (en) * | 2005-11-01 | 2007-05-10 | Nxp B.V. | Methods of packaging a semiconductor die and package formed by the methods |

| DE102005061015B4 (de) * | 2005-12-19 | 2008-03-13 | Infineon Technologies Ag | Verfahren zum Herstellen eines Halbleiterbauteils mit einem vertikalen Halbleiterbauelement |

| US20070215997A1 (en) * | 2006-03-17 | 2007-09-20 | Martin Standing | Chip-scale package |

| US7663212B2 (en) * | 2006-03-21 | 2010-02-16 | Infineon Technologies Ag | Electronic component having exposed surfaces |

| US7733659B2 (en) * | 2006-08-18 | 2010-06-08 | Delphi Technologies, Inc. | Lightweight audio system for automotive applications and method |

| DE102007009521B4 (de) * | 2007-02-27 | 2011-12-15 | Infineon Technologies Ag | Bauteil und Verfahren zu dessen Herstellung |

| US8222078B2 (en) * | 2009-07-22 | 2012-07-17 | Alpha And Omega Semiconductor Incorporated | Chip scale surface mounted semiconductor device package and process of manufacture |

| CN201629397U (zh) * | 2009-11-30 | 2010-11-10 | 鸿富锦精密工业(深圳)有限公司 | 集成电路组合 |

| US20120175688A1 (en) * | 2011-01-10 | 2012-07-12 | International Rectifier Corporation | Semiconductor Package with Reduced On-Resistance and Top Metal Spreading Resistance with Application to Power Transistor Packaging |

| US9536800B2 (en) | 2013-12-07 | 2017-01-03 | Fairchild Semiconductor Corporation | Packaged semiconductor devices and methods of manufacturing |

| US10064287B2 (en) | 2014-11-05 | 2018-08-28 | Infineon Technologies Austria Ag | System and method of providing a semiconductor carrier and redistribution structure |

| US10553557B2 (en) * | 2014-11-05 | 2020-02-04 | Infineon Technologies Austria Ag | Electronic component, system and method |

| US10192846B2 (en) | 2014-11-05 | 2019-01-29 | Infineon Technologies Austria Ag | Method of inserting an electronic component into a slot in a circuit board |

| CN109979825A (zh) * | 2017-12-15 | 2019-07-05 | 胡志良 | 阵列批次式封装元件晶粒的电路元件制作方法 |

Family Cites Families (54)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3403438A (en) | 1964-12-02 | 1968-10-01 | Corning Glass Works | Process for joining transistor chip to printed circuit |

| US3871014A (en) | 1969-08-14 | 1975-03-11 | Ibm | Flip chip module with non-uniform solder wettable areas on the substrate |

| US3972062A (en) | 1973-10-04 | 1976-07-27 | Motorola, Inc. | Mounting assemblies for a plurality of transistor integrated circuit chips |

| GB1487945A (en) | 1974-11-20 | 1977-10-05 | Ibm | Semiconductor integrated circuit devices |

| US4604644A (en) | 1985-01-28 | 1986-08-05 | International Business Machines Corporation | Solder interconnection structure for joining semiconductor devices to substrates that have improved fatigue life, and process for making |

| JPS63281451A (ja) * | 1987-05-13 | 1988-11-17 | Hitachi Ltd | 半導体装置 |

| JPH01161707A (ja) * | 1987-12-17 | 1989-06-26 | Nec Corp | チップ部品 |

| JPH0357251A (ja) * | 1989-07-26 | 1991-03-12 | Hitachi Ltd | 半導体装置 |

| JPH04159704A (ja) * | 1990-10-23 | 1992-06-02 | Nec Corp | 電気二重層コンデンサ |

| JP2984068B2 (ja) | 1991-01-31 | 1999-11-29 | 株式会社日立製作所 | 半導体装置の製造方法 |

| JPH05129516A (ja) | 1991-11-01 | 1993-05-25 | Hitachi Ltd | 半導体装置 |

| US5311402A (en) | 1992-02-14 | 1994-05-10 | Nec Corporation | Semiconductor device package having locating mechanism for properly positioning semiconductor device within package |

| JP2833326B2 (ja) | 1992-03-03 | 1998-12-09 | 松下電器産業株式会社 | 電子部品実装接続体およびその製造方法 |

| JPH0637143A (ja) | 1992-07-15 | 1994-02-10 | Toshiba Corp | 半導体装置および半導体装置の製造方法 |

| US5394490A (en) | 1992-08-11 | 1995-02-28 | Hitachi, Ltd. | Semiconductor device having an optical waveguide interposed in the space between electrode members |

| US5313366A (en) | 1992-08-12 | 1994-05-17 | International Business Machines Corporation | Direct chip attach module (DCAM) |

| JPH06244231A (ja) | 1993-02-01 | 1994-09-02 | Motorola Inc | 気密半導体デバイスおよびその製造方法 |

| US5371404A (en) | 1993-02-04 | 1994-12-06 | Motorola, Inc. | Thermally conductive integrated circuit package with radio frequency shielding |

| JP2795788B2 (ja) | 1993-02-18 | 1998-09-10 | シャープ株式会社 | 半導体チップの実装方法 |

| US5703405A (en) | 1993-03-15 | 1997-12-30 | Motorola, Inc. | Integrated circuit chip formed from processing two opposing surfaces of a wafer |

| US5510758A (en) | 1993-04-07 | 1996-04-23 | Matsushita Electric Industrial Co., Ltd. | Multilayer microstrip wiring board with a semiconductor device mounted thereon via bumps |

| JP3258764B2 (ja) | 1993-06-01 | 2002-02-18 | 三菱電機株式会社 | 樹脂封止型半導体装置の製造方法ならびに外部引出用電極およびその製造方法 |

| US5397921A (en) | 1993-09-03 | 1995-03-14 | Advanced Semiconductor Assembly Technology | Tab grid array |

| US5734201A (en) | 1993-11-09 | 1998-03-31 | Motorola, Inc. | Low profile semiconductor device with like-sized chip and mounting substrate |

| US5367435A (en) | 1993-11-16 | 1994-11-22 | International Business Machines Corporation | Electronic package structure and method of making same |

| US5454160A (en) | 1993-12-03 | 1995-10-03 | Ncr Corporation | Apparatus and method for stacking integrated circuit devices |

| JPH07193184A (ja) | 1993-12-27 | 1995-07-28 | Fujitsu Ltd | マルチチップモジュールの製造方法及びマルチチップモジュール |

| US5578869A (en) | 1994-03-29 | 1996-11-26 | Olin Corporation | Components for housing an integrated circuit device |

| HU212428B (en) * | 1994-05-13 | 1996-06-28 | Egyt Gyogyszervegyeszeti Gyar | Process to prepare pharmaceutical compositions containing gemfibrozyl |

| JP3377867B2 (ja) | 1994-08-12 | 2003-02-17 | 京セラ株式会社 | 半導体素子収納用パッケージ |

| JP2546192B2 (ja) | 1994-09-30 | 1996-10-23 | 日本電気株式会社 | フィルムキャリア半導体装置 |

| US5532512A (en) | 1994-10-03 | 1996-07-02 | General Electric Company | Direct stacked and flip chip power semiconductor device structures |

| JP3138159B2 (ja) | 1994-11-22 | 2001-02-26 | シャープ株式会社 | 半導体装置、半導体装置実装体、及び半導体装置の交換方法 |

| JPH08335653A (ja) | 1995-04-07 | 1996-12-17 | Nitto Denko Corp | 半導体装置およびその製法並びに上記半導体装置の製造に用いる半導体装置用テープキャリア |

| US5655703A (en) | 1995-05-25 | 1997-08-12 | International Business Machines Corporation | Solder hierarchy for chip attachment to substrates |

| US5674785A (en) | 1995-11-27 | 1997-10-07 | Micron Technology, Inc. | Method of producing a single piece package for semiconductor die |

| US5726502A (en) | 1996-04-26 | 1998-03-10 | Motorola, Inc. | Bumped semiconductor device with alignment features and method for making the same |

| JP2000049184A (ja) * | 1998-05-27 | 2000-02-18 | Hitachi Ltd | 半導体装置およびその製造方法 |

| US6423623B1 (en) * | 1998-06-09 | 2002-07-23 | Fairchild Semiconductor Corporation | Low Resistance package for semiconductor devices |

| EP0966038A3 (en) * | 1998-06-15 | 2001-02-28 | Ford Motor Company | Bonding of semiconductor power devices |

| US6133634A (en) | 1998-08-05 | 2000-10-17 | Fairchild Semiconductor Corporation | High performance flip chip package |

| JP2000077435A (ja) * | 1998-08-31 | 2000-03-14 | Hitachi Ltd | 半導体装置及びその製造方法 |

| JP3867881B2 (ja) * | 1998-09-09 | 2007-01-17 | 新電元工業株式会社 | 半導体装置 |

| KR20000057810A (ko) * | 1999-01-28 | 2000-09-25 | 가나이 쓰토무 | 반도체 장치 |

| JP4408475B2 (ja) * | 1999-02-23 | 2010-02-03 | 三洋電機株式会社 | ボンディングワイヤを採用しない半導体装置 |

| JP3895884B2 (ja) * | 1999-03-25 | 2007-03-22 | 三洋電機株式会社 | 半導体装置 |

| US6624522B2 (en) * | 2000-04-04 | 2003-09-23 | International Rectifier Corporation | Chip scale surface mounted device and process of manufacture |

| JP3639515B2 (ja) * | 2000-09-04 | 2005-04-20 | 三洋電機株式会社 | Mosfetの実装構造の製造方法 |

| US6391687B1 (en) | 2000-10-31 | 2002-05-21 | Fairchild Semiconductor Corporation | Column ball grid array package |

| US6717260B2 (en) * | 2001-01-22 | 2004-04-06 | International Rectifier Corporation | Clip-type lead frame for source mounted die |

| US6711317B2 (en) * | 2001-01-25 | 2004-03-23 | Lucent Technologies Inc. | Resiliently packaged MEMs device and method for making same |

| US6469398B1 (en) * | 2001-03-29 | 2002-10-22 | Kabushiki Kaisha Toshiba | Semiconductor package and manufacturing method thereof |

| JP2003110077A (ja) * | 2001-10-02 | 2003-04-11 | Mitsubishi Electric Corp | 半導体装置 |

| US6781227B2 (en) * | 2002-01-25 | 2004-08-24 | International Rectifier Corporation | Compression assembled electronic package having a plastic molded insulation ring |

-

2002

- 2002-11-22 US US10/303,523 patent/US6841865B2/en not_active Expired - Lifetime

-

2003

- 2003-11-21 CN CNB200380107276XA patent/CN100421240C/zh not_active Expired - Fee Related

- 2003-11-21 AU AU2003295783A patent/AU2003295783A1/en not_active Abandoned

- 2003-11-21 WO PCT/US2003/037314 patent/WO2004049435A1/en active Application Filing

- 2003-11-21 TW TW092132751A patent/TWI228317B/zh not_active IP Right Cessation

- 2003-11-21 JP JP2004555560A patent/JP4327096B2/ja not_active Expired - Fee Related

- 2003-11-21 DE DE10393769T patent/DE10393769B4/de not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| DE10393769B4 (de) | 2012-09-27 |

| CN1729568A (zh) | 2006-02-01 |

| US6841865B2 (en) | 2005-01-11 |

| DE10393769T5 (de) | 2006-02-09 |

| TW200414533A (en) | 2004-08-01 |

| US20040099940A1 (en) | 2004-05-27 |

| TWI228317B (en) | 2005-02-21 |

| JP2006507688A (ja) | 2006-03-02 |

| CN100421240C (zh) | 2008-09-24 |

| WO2004049435A1 (en) | 2004-06-10 |

| AU2003295783A1 (en) | 2004-06-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4327096B2 (ja) | 外部接続用クリップを有する半導体装置 | |

| US6650006B2 (en) | Semiconductor package with stacked chips | |

| US5521429A (en) | Surface-mount flat package semiconductor device | |

| KR100363776B1 (ko) | 리드와 직접 접속된 집적회로 칩 패키지 | |

| US9218987B2 (en) | Method for top-side cooled semiconductor package with stacked interconnection plates | |

| US7880282B2 (en) | Semiconductor package with integrated heatsink and electromagnetic shield | |

| US8030131B2 (en) | Semiconductor module | |

| KR100298162B1 (ko) | 수지봉지형반도체장치 | |

| US7495323B2 (en) | Semiconductor package structure having multiple heat dissipation paths and method of manufacture | |

| US8324739B2 (en) | Semiconductor device | |

| US20130337612A1 (en) | Heat dissipation methods and structures for semiconductor device | |

| JP2003086737A (ja) | 半導体装置 | |

| US20100059783A1 (en) | Light Emitting Chip Package With Metal Leads For Enhanced Heat Dissipation | |

| KR100902766B1 (ko) | 절연성 세라믹 히트 싱크를 갖는 디스크리트 패키지 | |

| KR20170086828A (ko) | 메탈범프를 이용한 클립 본딩 반도체 칩 패키지 | |

| JPH0476212B2 (ja) | ||

| JP4435050B2 (ja) | 半導体装置 | |

| KR102016019B1 (ko) | 고열전도성 반도체 패키지 | |

| JPH08148647A (ja) | 半導体装置 | |

| KR102332716B1 (ko) | 반도체 패키지 | |

| KR100481926B1 (ko) | 일반칩형반도체패키지및플립칩형반도체패키지와그제조방법 | |

| JPH11135532A (ja) | 半導体チップ及び半導体装置 | |

| JP2004119610A (ja) | リードフレーム、それを用いた樹脂封止型半導体装置及び樹脂封止型半導体装置の製造方法 | |

| US20030205793A1 (en) | Wire-bonded chip on board package | |

| EP1365450A1 (en) | An improved wire-bonded chip on board package |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080616 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080708 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20081007 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20081015 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20081107 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20081114 |

|

| A524 | Written submission of copy of amendment under article 19 pct |

Free format text: JAPANESE INTERMEDIATE CODE: A524 Effective date: 20081205 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090224 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090402 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090526 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090610 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120619 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4327096 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130619 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |