JP3713401B2 - チャージポンプ回路 - Google Patents

チャージポンプ回路 Download PDFInfo

- Publication number

- JP3713401B2 JP3713401B2 JP7349199A JP7349199A JP3713401B2 JP 3713401 B2 JP3713401 B2 JP 3713401B2 JP 7349199 A JP7349199 A JP 7349199A JP 7349199 A JP7349199 A JP 7349199A JP 3713401 B2 JP3713401 B2 JP 3713401B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- charge pump

- input

- level

- potential

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

- G11C5/145—Applications of charge pumps; Boosted voltage circuits; Clamp circuits therefor

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/30—Power supply circuits

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Dram (AREA)

- Dc-Dc Converters (AREA)

- Read Only Memory (AREA)

- Static Random-Access Memory (AREA)

Description

【発明の属する技術分野】

本発明は、昇圧電圧を生成するチャージポンプ回路に関する。特にチャージポンプ回路が組み込まれたデバイスの動作停止中、または待機中の低消費電力が要求されるチャージポンプ回路に関する。

【0002】

【従来の技術】

半導体デバイスは、微細加工技術と、電源電圧の低電圧化により、その性能を向上させてきた。その中でメモリ等のデバイスにおいては、メモリセル等に印加する電圧を外部電圧と同等に設定できず、チップ内部に昇圧回路、いわゆるチャージ・ポンプ回路を持つものがある。

【0003】

チャージポンプ回路によりチップ内部で昇圧された電位は、チップ停止時(チップ非活性時:Stand−by(スタンド・バイ状態))においても保たれる。これは、スタンド・バイ状態→アクティブ状態の変化直後においてもアクセス・タイム等、チップ性能を保証するためである。

【0004】

よって、スタンド・バイ状態においても、昇圧電位を保持するため、チャージポンプ回路は常に昇圧レベルを監視し内部電位がトランジスタのリーク等により電位低下を起こすと、チャージポンプ動作を自動的に再開する設定となっている。このため、内部昇圧を行うデバイスではスタンド・バイ時でも消費する電流(スタンド・バイ電流と称する)はゼロとはならない。

【0005】

【発明が解決しようとする課題】

最近、このような内部昇圧を伴うデバイスは、携帯機器の中に組み込まれることが多くなり、スタンド・バイ電流の低減化の要求が厳しい。その理由は、携帯機器は基本的に電池駆動であるため、微小電流でも流すとそのデバイスの待機時間が短くなる等、その機器の性能に直接かかわってくるためである。このため、チャージポンプ回路のスタンド・バイ電流の許容値はより小さくなり、従来のような値を許容されなくなってきた。

【0006】

この発明は上記事情を考慮してなされたものであり、その課題は、チャージポンプ動作の停止時(デバイスのスタンド・バイ時)の電流消費を削減し、かつ復帰時のチャージポンプ出力が最大電流を出すまでの時間が短縮できるチャージポンプ回路を提供することにある。

【0007】

【課題を解決するための手段】

この発明の一視点に係るチャージポンプ回路は、第1の電位を昇圧して第2の電位を生成し、且つ直列に接続された複数の回路部分を含み、前記複数の回路部分のそれぞれは、ドレインとゲートとが接続されたトランジスタと、前記トランジスタに接続ノードを介して接続されたキャパシタとを有し、前記キャパシタは、前記接続ノードに接続された第1の電極と、駆動電位が供給される第2の電極とを有するチャージポンプ回路であって、

前記複数の回路部分のうち奇数番目の回路部分のキャパシタに駆動電位を供給する第1の回路と、前記複数の回路部分のうち偶数番目の回路部分のキャパシタに駆動電位を供給する第2の回路とを有し、チャージポンプ動作時に、前記第1の回路及び前記第2の回路は前記奇数番目の回路部分のキャパシタ及び前記偶数番目の回路部分のキャパシタにハイレベル/ローレベルの互い違いの駆動電位を供給し、チャージポンプ動作停止時に、前記第1の回路及び前記第2の回路は各キャパシタに前記第2の電位に近い方のレベルの駆動電位を供給する駆動電位供給回路を具備する。

【0008】

本発明によれば、チャージポンプ動作停止時、チャージポンプ出力レベルに近い方の同一レベルの状態にキャパシタの駆動電位を揃えておくことにより、各段に接続されたゲート・ドレイン共通接続のトランジスタからの逆流電流による内部昇圧電位のロスを最小限におさえる。しかもチャージポンプ動作初期においては、各段の間にキャパシタ駆動電圧の電圧差は最低限保証される。

【0009】

【発明の実施の形態】

本発明を説明する前提としてまず、一般的なチャージポンプ回路に関し、スタンド・バイ時の電流削減の観点からチャージポンプ動作を検証する。

【0010】

図6は一般的なチャージポンプ回路の構成を示す回路図である。ゲート・ドレインを共通接続(ダイオード接続)したトランジスタQxのドレインにキャパシタCxの一方電極が接続されている。このトランジスタQxとキャパシタCxの回路構成を多数直列に接続し(この例ではxが1 〜4 )、各段のキャパシタCxを“H”レベル(ハイレベル)/“L”レベル(ローレベル)交互に駆動することにより電荷を転送していく。Qinは入力用トランジスタであり、電流通路の一端は外部電源VDDOに接続されている。昇圧出力VDDRは最終段のトランジスタQ4 のソースにて得られる。

【0011】

上記チャージポンプ回路の制御系は次のように構成されている。

NANDゲートNAND1,2それぞれは一方の入力端子にイネーブル信号ENABLEが供給される。NAND1の出力はインバータIV1を介して上記トランジスタQinのゲートに供給される。

【0012】

NAND2の他方の入力端子には図示しない発振器の出力信号OSCが供給される。NAND2の出力は2つに分かれて上記キャパシタCxを交互に駆動する。すなわち、NAND2の出力はインバータIV2,3,4を介してキャパシタC1とC3それぞれの他方電極に供給される。また、NAND2の出力はインバータIV2,5を介してNAND1の他方の入力端子、キャパシタC2,C4の他方電極それぞれに供給される。

【0013】

このチャージポンプ回路はENABLE信号が“H”レベル(ハイレベル)になることによって活性化する。ENABLE信号が“H”レベルになると、NAND2の出力は発振器出力OSC信号(“H”/“L”レベル)を伝達する。また、NAND1の出力はインバータIV1を介してインバータIV5の出力を伝達し、“H”/“L”のタイミング信号がトランジスタQinのゲートに与えられる。電荷転送用のトランジスタQxを隔てて隣り合うノードに接続された各キャパシタCxは、動作時“H”/“L”レベルの互い違いのレベルに駆動され電荷が転送されることにより、最終段のトランジスタQ4に昇圧電位VDDRが得られる。

【0014】

電荷の転送の観点から、ダイオード接続のトランジスタQxのしきい値はできる限り0Vに近いことが望ましい。このためチャージポンプ回路構成するトランジスタ(Qin,Qx)には、基板上にチャネル・イオン注入をしない状態で形成されたトランジスタ(Intrinsic トランジスタ:I−タイプトランジスタ)が使用される。基板上のI−タイプトランジスタではチャネル部の不純物濃度が希薄なためトランジスタのしきい値を略0Vとすることができる。

【0015】

図7(a)は基板上に形成されるダイオード接続のI−タイプトランジスタの各電位点を示す回路図、図7(b)は(a)で示す条件のときのドレイン電圧VDに対するドレイン電流IDの特性曲線図である。ここでは基板電位VBは接地電位とする(VB=0V)。ドレイン電圧VDがソース電圧VS(=ゲート電圧VG)より小さい条件では主にlogスケール(グラフ左側の目盛り)を参照し、ドレイン電圧VDがソース電圧VS(=ゲート電圧VG)より大きい条件では主に通常のスケール(グラフ右側の目盛り)を参照する。

【0016】

図8(a)は基板上に形成されるI−タイプトランジスタの各電位点を示す回路図、図8(b)は(a)で示す条件(VB=0,−1,−2,−3,−4,−5V)のときのゲート電圧VGに対するドレイン電流IDの特性曲線図である。ゲート電圧VGが0V以下の条件では主にlogスケール(グラフ左側の目盛り)を参照し、ゲート電圧VGが0V以上の条件では主に通常のスケール(グラフ右側の目盛り)を参照する。

【0017】

図9(a)は基板上に形成されるI−タイプトランジスタの各電位点を示す回路図、図9(b)は(a)で示す条件のときのゲート電圧VGに対するドレイン電流IDの特性曲線図である。ゲート電圧VGが0V以下の条件では主にlogスケール(グラフ左側の目盛り)を参照し、ゲート電圧VGが0V以上の条件では主に通常のスケール(グラフ右側の目盛り)を参照する。

【0018】

さて、図6のチャージポンプ回路がアクティブ→スタンド・バイ状態となり、チャージポンプ動作が停止した時の、チャージポンプ回路内部の各ノードの状態に注目する。

【0019】

一般にチャージポンプ動作が停止するスタンド・バイ時には、ENABLE信号が“L”レベルとなる。これにより、発振器の出力OSCの供給は強制的にストップさせられるため、各段のキャパシタのノードN1〜N4は“H”レベルと“L”レベルが交互になった状態で停止する。

【0020】

図7(a)におけるダイオード接続のように、各段のダイオード接続トランジスタQxは、バックバイアスがかかった状態でもカット・オフしないことがわかる。特にVDが10Vでは、VS(=VG)が1Vのとき、20μA近い電流が流れる。また、図8(b)及び図9(b)からわかるように、I−タイプトランジスタはそのしきい値が負でもあり、ゲート電圧がマイナスになってもオフせずに微少な電流が流れ続ける。

【0021】

つまり、図6に示すチャージポンプ回路は停止したその瞬間より、各段のトランジスタQxを通じて、電荷の逆流が起こる。この逆流電荷の量は、チャージポンプ駆動電圧(VDDO)と昇圧電圧(VDDR)の差が大きいほど大きくなる。

【0022】

この逆流電荷による昇圧ノードのレベル低下が起こると、チャージポンプ回路は、前述のように、電位を補給するために動作しなければならなくなる。つまり、チャージポンプの逆流電荷の存在は、スタンド・バイ電流の増加要因となり、この逆流電荷量は、外部電位と昇圧電位のレベル差が大きいほど大きくなる。従って、近年の外部電位の低電圧化と、スタンド・バイ電流の低減化は両立困難となる。

【0023】

もし、逆流電流を無視できるほどトランジスタのカット・オフ特性を良くするためには、図9(b)におけるI=10-9[A]でのポイントをVG=0V以上にシフトさせる必要があり、これはトランジスタのしきい値Vthを+0.5V以上にしなければ実現できないことを示している。

【0024】

しかしながら、前述のように、チャネルイオン注入等でトランジスタのVthを上げるとバックバイアス効果が増大し、チャージポンプ動作における電流供給能力を極端に悪化させるため、現状ではI−タイプトランジスタを使わざるを得ない。

【0025】

そこで、本発明におけるチャージポンプ回路は、I−タイプトランジスタを使用して、かつ、スタンド・バイ時の逆流を極力抑えることのできる制御方式を有する構成とした。

【0026】

図1は、本発明の基本的な実施形態に係るチャージポンプ回路及びその制御回路の構成を示すブロック図である。本発明において、チャージポンプ動作の停止時(スタンド・バイ状態時)には、チャージポンプ回路1の各キャパシタノードの駆動電圧が、全て昇圧ノードの電位VDDRに近い方の電圧に固定される、逆流抑制用の同一レベルになることが特徴となっている。すなわち、昇圧ノードの電位VDDRが正の電位であればキャパシタ駆動用の“H”レベルであり、VDDRが負の電位であればキャパシタ駆動用の“L”レベルである。

【0027】

すなわち、通常“H”/“L”レベルを伝達する発振器2の出力OSC信号がENABLE信号によるチャージポンプ動作停止の制御によって無効となる。この時点でチャージポンプ回路は、各キャパシタノードに逆流抑制用の同一レベルを伝達する。

【0028】

もちろんスタンド・バイ時でも時間が経つに連れて昇圧ノードが基準電位より低くなる。その時は検知回路3がENABLE信号を制御し、チャージポンプ動作を再開させる。昇圧ノードが基準電位に達すると検知回路3がENABLE信号を制御し、チャージポンプ動作を停止させる。このときも逆流抑制用の同一レベルが各キャパシタノードに伝達される。

【0029】

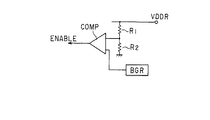

なお、検知回路3は、図2のように例えば昇圧ノードの電位VDDRをR1,R2で抵抗分割した所定電位と、BGR(バンドギャップリファレンス)回路からの基準電位とを比較する比較器COMPを含んで構成される。

【0030】

また、検知回路3は、早急に昇圧電位を補給しなければならない実動作に比べて、スタンド・バイ時は緩慢に昇圧電位を補給しても支障はないので、より低消費電力を優先する理由から2系統に回路が分かれているものもある。すなわち検知回路3は、比較的感度の高い性能を有して構成された実動作用のものと、比較的感度の低い性能を有して構成されたスタンド・バイ用のものとの2系統の回路で構成される。

【0031】

本発明によれば、半導体デバイスをスタンド・バイ状態で停止させる時、内部に設けられたチャージポンプ回路の各段のキャパシタ駆動電位を全て昇圧レベルに近い方の、“H”レベル(ハイレベル)、“L”レベル(ローレベル)いずれかのレベルに統一し、キャパシタ接続ノード(N1〜N4)をすべて逆流抑制レベルにしてキャパシタ駆動を停止させる。これにより、次のような利点が得られる。

【0032】

第1に、スタンド・バイ中に各段に接続されたゲート・ドレイン共通接続のトランジスタからの逆流電流による内部昇圧電位のロスを最小限におさえる。第2に、スタンド・バイ→アクティブ状態移行時におけるチャージポンプ動作初期においては、各段の間にキャパシタ駆動電圧の電圧差は最低限保証されるため、チャージポンプが最大電流を出すまでの時間を短縮できる。これについて以下に具体的な回路を参照して説明する。

【0033】

図3は、本発明の一実施形態に係るチャージポンプ回路の構成を示す回路図である。ゲート・ドレインを共通接続(ダイオード接続)したI−タイプのトランジスタQxのドレインにキャパシタCxの一方電極が接続されている。このトランジスタQxとキャパシタCxの回路構成を多数直列に接続し(この例ではxが1 〜4 )、各段のキャパシタCxを“H”レベル/“L”レベル交互に駆動することにより電荷を転送していく。Qinは入力用トランジスタであり、電流通路の一端は外部電源VDDOに接続されている。昇圧出力VDDRは最終段のトランジスタQ4 のソースにて得られる。

【0034】

上記チャージポンプ回路の制御系は次のように構成されている。

NANDゲートNAND1,2,3それぞれは一方の入力端子にイネーブル信号ENABLEが供給される。NAND1の出力はインバータIV1を介して上記トランジスタQinのゲートに供給される。

【0035】

NAND2の他方の入力端子には図示しない発振器の出力信号OSCが供給される。NAND2の出力はインバータIV11,12を介してキャパシタC1とC3それぞれの他方電極に供給される。

【0036】

NAND3の他方の入力端子にはインバータIV13を介して図示しない発振器の出力信号OSCの反転信号が供給される。NAND3の出力はインバータIV14,15を介してNAND1の他方の入力端子に供給されると共に、キャパシタC2とC4それぞれの他方電極に供給される。

【0037】

このチャージポンプ回路はENABLE信号が“H”レベル(ハイレベル)になることによって活性化する。ENABLE信号が“H”レベルになると、NAND2,3の出力は発振器出力OSC信号(“H”/“L”レベル)を伝達する。また、NAND1の出力はインバータIV1を介してインバータIV15の出力を伝達し、“H”/“L”のタイミング信号がトランジスタQinのゲートに与えられる。電荷転送用のトランジスタQxを隔てて隣り合うノードに接続された各キャパシタCxは、動作時“H”/“L”レベルの互い違いのレベルに駆動され電荷が転送されることにより、最終段のトランジスタQ4に昇圧電位VDDRが得られる。

【0038】

上記構成のチャージポンプ回路の動作が停止するスタンド・バイ時には、ENABLE信号は“L”レベルとなる。発振器の出力OSCの供給は強制的にストップさせられるが、各段のキャパシタの駆動電位はすべて“H”レベルとなり、ノードN1〜N4はすべて“H”レベルとなった状態で停止する。

【0039】

この停止制御では、従来“L”レベルで停止していたノードへの逆流電流による充電電荷をQ=C・Vだけ削減することができる。(C:各段につくキャパシタCxの容量、V:外部電源VDDOレベル)

図4は、本発明におけるチャージポンプ回路(全段“H”停止)の逆流特性のシミュレーション結果を、図6の各段“H”/“L”互い違いの停止方式に比べて示す特性図である。逆流による昇圧レベルの低下は本発明は従来回路に比較して2/3程度にまで減少している。これより、電源電圧の低下と低スタンド・バイ電流の両立をより低い電源電圧まで可能にする。

【0040】

図5(a),(b)は、図1の本発明のチャージポンプ回路に係るスタンド・バイ→アクティブ状態移行時におけるチャージポンプ動作初期特性のシミュレーション結果を示す特性図である。(a)は、再起動時キャパシタノードが“H”/“L”交互安定レベルに復帰するまでの推移、(b)は、(a)により安定した電流供給までの推移を示す。

【0041】

図10(a),(b)は、図6のチャージポンプ回路に係るスタンド・バイ→アクティブ状態移行時におけるチャージポンプ動作初期特性の図4と同様なシミュレーション結果を示す特性図である。各キャパシタノードが昇圧レベルからの逆流により適切なレベルにないため、復帰時“H”/“L”交互に差がついたレベルになるまで時間がかかり、チャージポンプが最大電流を出すまでに時間がかかる問題があった。

【0042】

この実効的なスタンド・バイ→アクティブまでのチャージポンプ動作時間を短縮できないと、アクティブになった直後は、チップ内部での昇圧電流の消費をチャージポンプが補給できず、アクセス・タイム等のチップ能力を保証できなくなる。

【0043】

本発明に係る図5の特性図を参照すると、動作開始直後は、全て“H”となっていた各ノード(図3のN1〜N4)が“H”/“L”交互のレベルにもどり、各段にキャパシタ駆動電圧(VDDO)の電位差が確保される。この状態よりチャージポンプは動作を続けるので、チャージポンプが最大電流を出し始めるまでの時間(矢印の期間A)が図10の構成における同期間(矢印の期間B)と比べて略1/2に短縮できる。

【0044】

これにより、アクティブ直後におけるチップ内部の昇圧電位の消費を、本発明のチャージポンプ回路が短時間で補給することが可能となり、アクセス・タイム等のチップ能力を保証可能となる。

【0045】

このように上記実施形態によれば、半導体装置をスタンド・バイ状態で停止させる時、各段のキャパシタ駆動電位を全て“H”レベルにし、各キャパシタ接続ノードを全て“H”状態で停止させる。これにより、(1)スタンド・バイ中に各段に接続されたゲート・ドレイン共通接続のトランジスタからの逆流電流による内部昇圧電位のロスを最小限におさえる効果がある。さらに、(2)スタンド・バイ→アクティブ状態移行時におけるチャージポンプ動作初期においては、各段の間にキャパシタ駆動電圧(VDDO)の電圧差は最低限保証されるため、チャージポンプが最大電流を出すまでの時間を短縮できる効果がある。

【0046】

なお、本発明はチャージポンプ動作停止時に各キャパシタ全ノードを逆流抑制用の同一レベルにするための様々な回路構成が考えられ、上記図2の回路構成に限らない。また、負の昇圧電位をチャージポンプ出力するものについては、チャージポンプ動作停止時に各キャパシタ全ノードを逆流抑制用の同一レベル“L”レベル(キャパシタ駆動用の“L”レベル)にすればよい。

【0047】

【発明の効果】

以上説明したようにこの発明によれば、チャージポンプ動作停止時、格段のキャパシタノードを全てチャージポンプ出力に対する逆流抑制用のレベルにするという比較的簡単な制御構成で、電荷転送効率のよいI−タイプトランジスタを用いつつ、チャージポンプ動作の停止時(デバイスのスタンド・バイ時)の電流消費を削減し、かつ復帰時のチャージポンプ出力が最大電流を出すまでの時間が短縮でき、デバイスの低電圧化にも対応可能なチャージポンプ回路を提供することができる。

【図面の簡単な説明】

【図1】本発明の基本的な実施形態に係るチャージポンプ回路及びその制御回路の構成を示すブロック図。

【図2】図1中の一部の回路図。

【図3】本発明の一実施形態に係るチャージポンプ回路の構成を示す回路図。

【図4】本発明におけるチャージポンプ回路の逆流特性のシミュレーション結果を従来の構成に比べて示す特性図。

【図5】(a),(b)は、図1のチャージポンプ回路に係るスタンド・バイ→アクティブ状態移行時におけるチャージポンプ動作初期特性のシミュレーション結果を示す特性図。

【図6】一般的なチャージポンプ回路の構成を示す回路図。

【図7】(a)は基板上に形成されるダイオード接続のI−タイプトランジスタの各電位点を示す回路図、(b)は(a)で示す条件のときのドレイン電圧VDに対するドレイン電流IDの特性曲線図。

【図8】(a)は基板上に形成されるI−タイプトランジスタの各電位点を示す回路図、(b)は(a)で示す条件のときのゲート電圧VGに対するドレイン電流IDの特性曲線図。

【図9】(a)は基板上に形成されるI−タイプトランジスタの各電位点を示す回路図、(b)は(a)で示す条件のときのゲート電圧VGに対するドレイン電流IDの特性曲線図。

【図10】(a),(b)は、図6のチャージポンプ回路に係るスタンド・バイ→アクティブ状態移行時におけるチャージポンプ動作初期特性のシミュレーション結果を示す特性図。

【符号の説明】

1…チャージポンプ回路

2…発振器

3…検知回路

Qin,Qx(xは1 〜4 )…I−タイプトランジスタ(Intrinsic トランジスタ)

Cx…キャパシタ

NAND1〜3…NANDゲート

IV1,IV11〜15…インバータ

Claims (5)

- 第1の電位を昇圧して第2の電位を生成し、且つ直列に接続された複数の回路部分を含み、前記複数の回路部分のそれぞれは、ドレインとゲートとが接続されたトランジスタと、前記トランジスタに接続ノードを介して接続されたキャパシタとを有し、前記キャパシタは、前記接続ノードに接続された第1の電極と、駆動電位が供給される第2の電極とを有するチャージポンプ回路であって、

前記複数の回路部分のうち奇数番目の回路部分のキャパシタに駆動電位を供給する第1の回路と、前記複数の回路部分のうち偶数番目の回路部分のキャパシタに駆動電位を供給する第2の回路とを有し、チャージポンプ動作時に、前記第1の回路及び前記第2の回路は前記奇数番目の回路部分のキャパシタ及び前記偶数番目の回路部分のキャパシタにハイレベル/ローレベルの互い違いの駆動電位を供給し、チャージポンプ動作停止時に、前記第1の回路及び前記第2の回路は各キャパシタに前記第2の電位に近い方のレベルの駆動電位を供給する駆動電位供給回路を具備することを特徴とするチャージポンプ回路。 - 前記第2の電圧は、正であり、

前記各回路部分に含まれる接続ノードは、前記チャージポンプ動作停止時に、ハイレベルの電位に設定されることを特徴とする請求項1記載のチャージポンプ回路。 - 前記第1の回路は、第の1NAND回路と、この第1のNAND回路の出力が入力される第1のインバータ回路と、この第1のインバータ回路の出力が入力される第2のインバータ回路とを有し、

前記第2の回路は、第2のNAND回路と、この第2のNAND回路の出力が入力される第3のインバータ回路と、この第3のインバータ回路の出力が入力される第4のインバータ回路とを有し、

前記第1のNAND回路の一方の入力には発振器からのクロック信号が入力されると共に他方の入力には前記チャージポンプ動作時にハイレベルとなり前記チャージポンプ動作停止時にローレベルとなるイネーブル信号が入力され、

前記第2のNAND回路の一方の入力には前記クロック信号の反転信号が入力されると共に他方の入力には前記イネーブル信号が入力され、

前記第2のインバータ回路及び前記第4のインバータ回路は、チャージポンプ動作停止時に、ハイレベルの駆動電位を前記各キャパシタに供給することを特徴とする請求項2記載のチャージポンプ回路。 - 前記イネーブル信号は、前記第2の電圧が基準電圧より小さい場合にハイレベルとなり、前記第2の電圧が前記基準電圧より大きい場合にローレベルとなることを特徴とする請求項3記載のチャージポンプ回路。

- 前記トランジスタは、I( Intrinsic )−タイプトランジスタであることを特徴とする請求項1乃至4のいずれかに記載のチャージポンプ回路。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP7349199A JP3713401B2 (ja) | 1999-03-18 | 1999-03-18 | チャージポンプ回路 |

| TW089103238A TW451490B (en) | 1999-03-18 | 2000-02-24 | Charge-pumping circuit |

| US09/523,729 US6373325B1 (en) | 1999-03-18 | 2000-03-13 | Semiconductor device with a charge pumping circuit |

| KR10-2000-0013555A KR100383205B1 (ko) | 1999-03-18 | 2000-03-17 | 차지 펌프 회로를 구비한 반도체 디바이스 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP7349199A JP3713401B2 (ja) | 1999-03-18 | 1999-03-18 | チャージポンプ回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2000270541A JP2000270541A (ja) | 2000-09-29 |

| JP2000270541A5 JP2000270541A5 (ja) | 2005-05-12 |

| JP3713401B2 true JP3713401B2 (ja) | 2005-11-09 |

Family

ID=13519805

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP7349199A Expired - Fee Related JP3713401B2 (ja) | 1999-03-18 | 1999-03-18 | チャージポンプ回路 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US6373325B1 (ja) |

| JP (1) | JP3713401B2 (ja) |

| KR (1) | KR100383205B1 (ja) |

| TW (1) | TW451490B (ja) |

Families Citing this family (41)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4149637B2 (ja) * | 2000-05-25 | 2008-09-10 | 株式会社東芝 | 半導体装置 |

| JP2002208290A (ja) * | 2001-01-09 | 2002-07-26 | Mitsubishi Electric Corp | チャージポンプ回路およびこれを用いた不揮発性メモリの動作方法 |

| JP4627920B2 (ja) * | 2001-04-24 | 2011-02-09 | Okiセミコンダクタ株式会社 | 電源装置 |

| US6515902B1 (en) * | 2001-06-04 | 2003-02-04 | Advanced Micro Devices, Inc. | Method and apparatus for boosting bitlines for low VCC read |

| US7941675B2 (en) * | 2002-12-31 | 2011-05-10 | Burr James B | Adaptive power control |

| US7180322B1 (en) | 2002-04-16 | 2007-02-20 | Transmeta Corporation | Closed loop feedback control of integrated circuits |

| JP3873838B2 (ja) * | 2002-07-25 | 2007-01-31 | ソニー株式会社 | 電池電圧動作回路 |

| US7228242B2 (en) | 2002-12-31 | 2007-06-05 | Transmeta Corporation | Adaptive power control based on pre package characterization of integrated circuits |

| US7953990B2 (en) | 2002-12-31 | 2011-05-31 | Stewart Thomas E | Adaptive power control based on post package characterization of integrated circuits |

| US6965264B1 (en) * | 2003-06-30 | 2005-11-15 | National Semiconductor Corporation | Adaptive threshold scaling circuit |

| KR100498505B1 (ko) * | 2003-07-15 | 2005-07-01 | 삼성전자주식회사 | 승압전압 발생회로 및 승압전압 발생방법 |

| JP2005151468A (ja) | 2003-11-19 | 2005-06-09 | Sanyo Electric Co Ltd | アンプ |

| US7012461B1 (en) * | 2003-12-23 | 2006-03-14 | Transmeta Corporation | Stabilization component for a substrate potential regulation circuit |

| US7129771B1 (en) | 2003-12-23 | 2006-10-31 | Transmeta Corporation | Servo loop for well bias voltage source |

| US7692477B1 (en) | 2003-12-23 | 2010-04-06 | Tien-Min Chen | Precise control component for a substrate potential regulation circuit |

| US7649402B1 (en) * | 2003-12-23 | 2010-01-19 | Tien-Min Chen | Feedback-controlled body-bias voltage source |

| US7774625B1 (en) | 2004-06-22 | 2010-08-10 | Eric Chien-Li Sheng | Adaptive voltage control by accessing information stored within and specific to a microprocessor |

| US7562233B1 (en) | 2004-06-22 | 2009-07-14 | Transmeta Corporation | Adaptive control of operating and body bias voltages |

| KR100680503B1 (ko) | 2004-11-08 | 2007-02-08 | 주식회사 하이닉스반도체 | 반도체 메모리 장치의 내부전압 발생기 |

| KR100636508B1 (ko) * | 2004-11-11 | 2006-10-18 | 삼성에스디아이 주식회사 | 차지펌프 회로와 이를 이용한 직류 변환장치 |

| KR100805542B1 (ko) * | 2004-12-24 | 2008-02-20 | 삼성에스디아이 주식회사 | 발광 표시장치 및 그의 구동방법 |

| KR100723488B1 (ko) * | 2005-06-16 | 2007-05-31 | 삼성전자주식회사 | 플래쉬 메모리 장치의 프로그램 동작을 위한 고전압 발생회로 및 고전압 발생 방법 |

| KR100762690B1 (ko) * | 2005-11-07 | 2007-10-01 | 삼성에스디아이 주식회사 | 데이터구동회로와 이를 이용한 유기발광표시장치 |

| KR100713995B1 (ko) * | 2005-11-07 | 2007-05-04 | 삼성에스디아이 주식회사 | Dcdc 변환기 및 그를 이용한 유기발광표시장치 |

| KR100762691B1 (ko) * | 2005-11-07 | 2007-10-01 | 삼성에스디아이 주식회사 | Dcdc 변환기 및 그를 이용한 유기발광표시장치 |

| KR100703460B1 (ko) * | 2005-11-07 | 2007-04-03 | 삼성에스디아이 주식회사 | Dcdc 변환기 및 그를 이용한 유기발광표시장치 |

| KR100729353B1 (ko) * | 2005-11-22 | 2007-06-15 | 삼성전자주식회사 | 통합된 레귤레이터/펌프 구조를 갖는 플래시 메모리 장치 |

| JP4692327B2 (ja) * | 2006-02-24 | 2011-06-01 | 株式会社デンソー | 負荷駆動装置 |

| US7348832B2 (en) * | 2006-03-20 | 2008-03-25 | Taiwan Semiconductor Manufacturing Co., Ltd. | Dual-voltage generation system |

| US7626865B2 (en) | 2006-06-13 | 2009-12-01 | Micron Technology, Inc. | Charge pump operation in a non-volatile memory device |

| US8547756B2 (en) | 2010-10-04 | 2013-10-01 | Zeno Semiconductor, Inc. | Semiconductor memory device having an electrically floating body transistor |

| US8130547B2 (en) * | 2007-11-29 | 2012-03-06 | Zeno Semiconductor, Inc. | Method of maintaining the state of semiconductor memory having electrically floating body transistor |

| US7839689B2 (en) | 2008-01-31 | 2010-11-23 | Mosaid Technologies Incorporated | Power supplies in flash memory devices and systems |

| JP5011182B2 (ja) * | 2008-03-24 | 2012-08-29 | ルネサスエレクトロニクス株式会社 | チャージポンプ回路 |

| KR100902060B1 (ko) * | 2008-05-08 | 2009-06-15 | 주식회사 하이닉스반도체 | 반도체 메모리 장치의 펌핑 전압 생성 회로 및 방법 |

| JP5535600B2 (ja) | 2009-11-30 | 2014-07-02 | ピーエスフォー ルクスコ エスエイアールエル | 半導体装置 |

| US10340276B2 (en) | 2010-03-02 | 2019-07-02 | Zeno Semiconductor, Inc. | Method of maintaining the state of semiconductor memory having electrically floating body transistor |

| US8648654B1 (en) * | 2012-09-25 | 2014-02-11 | Arm Limited | Integrated circuit and method for generating a layout of such an integrated circuit |

| TWI643435B (zh) | 2013-08-21 | 2018-12-01 | 日商半導體能源研究所股份有限公司 | 電荷泵電路以及具備電荷泵電路的半導體裝置 |

| KR102267237B1 (ko) | 2014-03-07 | 2021-06-18 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 전자 기기 |

| US9312280B2 (en) | 2014-07-25 | 2016-04-12 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS57130293A (en) * | 1981-02-05 | 1982-08-12 | Toshiba Corp | Semiconductor boosting circuit |

| JPH01133294A (ja) * | 1987-11-18 | 1989-05-25 | Ricoh Co Ltd | メモリ用昇圧回路装置 |

| JPH0453260A (ja) | 1990-06-20 | 1992-02-20 | Mitsubishi Electric Corp | 半導体装置 |

| JPH04268294A (ja) * | 1991-02-25 | 1992-09-24 | Nec Corp | 昇圧回路 |

| US5168174A (en) * | 1991-07-12 | 1992-12-01 | Texas Instruments Incorporated | Negative-voltage charge pump with feedback control |

| JP3190086B2 (ja) * | 1992-01-10 | 2001-07-16 | 株式会社日立製作所 | 昇圧回路 |

| US5291446A (en) * | 1992-10-22 | 1994-03-01 | Advanced Micro Devices, Inc. | VPP power supply having a regulator circuit for controlling a regulated positive potential |

| JPH0721790A (ja) * | 1993-07-05 | 1995-01-24 | Mitsubishi Electric Corp | 半導体集積回路 |

| JP3378457B2 (ja) * | 1997-02-26 | 2003-02-17 | 株式会社東芝 | 半導体装置 |

| JPH114575A (ja) * | 1997-06-11 | 1999-01-06 | Nec Corp | 昇圧回路 |

| JPH1146138A (ja) | 1997-07-24 | 1999-02-16 | Sharp Corp | 電流を充放電させる装置 |

| US6002630A (en) * | 1997-11-21 | 1999-12-14 | Macronix International Co., Ltd. | On chip voltage generation for low power integrated circuits |

-

1999

- 1999-03-18 JP JP7349199A patent/JP3713401B2/ja not_active Expired - Fee Related

-

2000

- 2000-02-24 TW TW089103238A patent/TW451490B/zh not_active IP Right Cessation

- 2000-03-13 US US09/523,729 patent/US6373325B1/en not_active Expired - Fee Related

- 2000-03-17 KR KR10-2000-0013555A patent/KR100383205B1/ko not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| US6373325B1 (en) | 2002-04-16 |

| TW451490B (en) | 2001-08-21 |

| KR20010029599A (ko) | 2001-04-06 |

| JP2000270541A (ja) | 2000-09-29 |

| KR100383205B1 (ko) | 2003-05-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3713401B2 (ja) | チャージポンプ回路 | |

| KR100298159B1 (ko) | 충전펌프 | |

| US6343044B1 (en) | Super low-power generator system for embedded applications | |

| JPH07303369A (ja) | 半導体デバイス用内部電圧発生器 | |

| US20050218966A1 (en) | Booster circuit | |

| US6912159B2 (en) | Boosting circuit and non-volatile semiconductor storage device containing the same | |

| KR19980071694A (ko) | 승압 회로 및 반도체 기억 장치 | |

| US20060028266A1 (en) | Voltage generating circuit | |

| JP2812230B2 (ja) | バイアス電圧発生回路 | |

| US6774708B2 (en) | Voltage boosting circuit with two main charge pumps | |

| US5412257A (en) | High efficiency N-channel charge pump having a primary pump and a non-cascaded secondary pump | |

| JP4090537B2 (ja) | 半導体メモリ装置の内部昇圧電圧発生器 | |

| WO2007043095A9 (ja) | 記憶装置、および記憶装置の制御方法 | |

| JPH08287677A (ja) | 半導体集積回路 | |

| JP3110257B2 (ja) | 半導体集積回路 | |

| US7511559B2 (en) | Booster circuit | |

| US20180374852A1 (en) | Semiconductor device | |

| KR100564414B1 (ko) | 반도체장치의 차지펌프 | |

| JPH0430207B2 (ja) | ||

| JP3888949B2 (ja) | 半導体集積回路 | |

| US5905400A (en) | Circuit configuration for generating a boosted output voltage | |

| US12040705B2 (en) | Self clocked low power doubling charge pump | |

| JP2000011673A (ja) | 負昇圧回路 | |

| KR100587026B1 (ko) | 백-바이어스 전압 발생회로 | |

| JP3789409B2 (ja) | 半導体集積回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040629 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040629 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20050516 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20050524 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050725 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050816 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050822 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090826 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090826 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100826 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100826 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110826 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110826 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120826 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120826 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130826 Year of fee payment: 8 |

|

| LAPS | Cancellation because of no payment of annual fees |