JP2011155152A - 固体撮像装置とその製造方法、並びに電子機器 - Google Patents

固体撮像装置とその製造方法、並びに電子機器 Download PDFInfo

- Publication number

- JP2011155152A JP2011155152A JP2010016000A JP2010016000A JP2011155152A JP 2011155152 A JP2011155152 A JP 2011155152A JP 2010016000 A JP2010016000 A JP 2010016000A JP 2010016000 A JP2010016000 A JP 2010016000A JP 2011155152 A JP2011155152 A JP 2011155152A

- Authority

- JP

- Japan

- Prior art keywords

- region

- conductivity type

- ion implantation

- type ion

- state imaging

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/803—Pixels having integrated switching, control, storage or amplification elements

- H10F39/8037—Pixels having integrated switching, control, storage or amplification elements the integrated elements comprising a transistor

- H10F39/80377—Pixels having integrated switching, control, storage or amplification elements the integrated elements comprising a transistor characterised by the channel of the transistor, e.g. channel having a doping gradient

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/011—Manufacture or treatment of image sensors covered by group H10F39/12

- H10F39/014—Manufacture or treatment of image sensors covered by group H10F39/12 of CMOS image sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/803—Pixels having integrated switching, control, storage or amplification elements

- H10F39/8033—Photosensitive area

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/807—Pixel isolation structures

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/813—Electronic components shared by multiple pixels, e.g. one amplifier shared by two pixels

Landscapes

- Solid State Image Pick-Up Elements (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

Abstract

【解決手段】半導体基板に形成された光電変換部PDと画素トランジスタからなる複数の画素と、画素内のフローティングディフージョン部FDを有する。また、画素における光電変換部PD側の表面と、画素トランジスタのうちの転送トランジスタの転送ゲート電極28下の半導体基板表面との全面にわたって形成された表面ピニング用の第1導電型半導体領域31を有する。さらに、第1導電型半導体領域31の全域下に形成され、フローティングディフージョン部へのオ−バーフローパスとなるオ−バーフローパス形成用の第2導電型半導体領域32を有する。転送ゲート電極下の第2導電型半導体領域によりオ−バーフローパスを形成するオ−バーフローバリアが形成され、光電変換部の第2導電型半導体領域とオ−バーフローパス形成用の第2導電型半導体領域との重なる領域により電荷蓄積領域が形成される。

【選択図】図3

Description

特許文献1には、フォトダイオードをフローティングディフージョン部の下まで延長する構成が開示されている。

特許文献2には、裏面照射型のCMOS固体撮像装置が開示されている。

特許文献3、4には、CMOS固体撮像装置の画素トランジスタにおいて、ゲート電極側面にサイドウォールを形成した構成が開示されている。

特許文献5には、CMOS固体撮像装置におけるフローティングディフージョン部の周りに素子分離領域が形成された構成が開示されている。

特許文献6には、CMOS固体撮像装置の画素トランジスタが拡散層またはSTI構造の素子分離領域で分離された構成が開示されている。

特許文献7には、CMOS固体撮像装置における転送トランジスタのゲート電極のフォトダイオード側にn型半導体領域が形成された構成が開示されている。

本発明は、この固体撮像装置を備えた電子機器を提供するものである。

さらに、本発明は、半導体基板上にゲート絶縁膜を介して転送トランジスタを含む画素トランジスタのゲート電極を形成する工程と、半導体基板に第2導電型不純物をイオン注入してフローティングディフージョン部を形成する工程を有する。

そして、転送ゲート電極下の第2導電型イオン注入領域によりオ−バーフローパスを形成するオ−バーフローバリアを形成し、光電変換部に形成した第2導電型半導体領域と第2導電型イオン注入領域との重なる領域により電荷蓄積領域を形成する。

固体撮像装置は、半導体基板に形成された光電変換部と画素トランジスタからなる複数の画素と、画素内のフローティングディフージョン部を有する。本発明は、さらに画素における光電変換部の表面と、画素トランジスタのうちの転送トランジスタの転送ゲート電極下の半導体基板表面との全面にわたって形成された表面ピニング用の第1導電型イオン注入領域を有する。本発明は、さらに第1導電型イオン注入領域の全域下に形成されてフローティングディフージョン部へのオ−バーフローパスとなるオ−バーフローパス形成用の第2導電型イオン注入領域を有する。そして、転送ゲート電極下の前記第2導電型イオン注入領域によりオ−バーフローパスを形成するオ−バーフローバリアが形成され、光電変換部の第2導電型半導体領域と第2導電型イオン注入領域と重なる領域で電荷蓄積領域が形成される。

1.MOS固体撮像装置の概略構成例

2.第1実施の形態(固体撮像装置の構成例及び製造方法例)

3.第2実施の形態(固体撮像装置の構成例及び製造方法例)

4.第3実施の形態(電子機器の構成例)

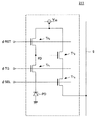

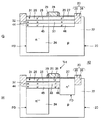

図1に、本発明の各実施の形態に適用されるMOS固体撮像装置の一例の概略構成を示す。本例の固体撮像装置1は、図1に示すように、半導体基板11例えばシリコン基板に光電変換部を含む複数の画素2が規則的に2次元的に配列された画素領域(いわゆる撮像領域)3と、周辺回路部とを有して構成される。画素2としては、1つの光電変換部と複数の画素トランジスタからなる単位画素を適用することができる。また、画素2としては、複数の光電変換部が転送トランジスタを除く他の画素トランジスタを共有したいわゆる画素共有の構造を適用することができる。複数の画素トランジスタは、例えば、転送トランジスタ、リセットトランジスタ及び増幅トランジスタの3トランジスタ、あるいは選択トランジスタを追加した4トランジスタで構成することができる。

[固体撮像装置の構成例]

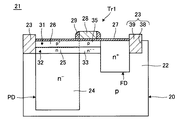

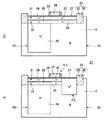

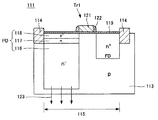

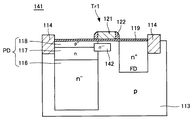

図3に、本発明に係る固体撮像装置、すなわちCMOS固体撮像装置の第1実施の形態を示す。図3は、表面照射型、裏面照射型を問わず適用できる横型オ−バーフロー構造を有するCMOS固体撮像装置であり、フォトダイオードPDと転送トランジスタを含む要部の概略構成を示す。

第1実施の形態に係る固体撮像装置21では、転送ゲート電極28下にフォトダイオードPDからフローティングディフージョン部FDに連接するようにn型半導体領域33によるオ−バーフローパスが形成される。電荷蓄積時、照射した光がフォトダイオードPD内で光電変換され、発生した信号電荷が電荷蓄積領域25に蓄積される。フォトダイオードPDでは、蓄積できる最大電荷量が決まっており、それより強い光が照射すると、電荷がフォトダイオードPDから溢れる。フォトダイオードPDから溢れた電荷は、転送ゲート電極28下のオ−バーフローパスとなるn型半導体領域33を通ってフローティングディフージョン部FDへ流れ、排出される。

次に、図4〜図6を用いて第1実施の形態に係る固体撮像装置21の製造方法例を説明する。まず、図4Aに示すように、シリコン半導体基板20の上面に熱酸化により絶縁膜37を形成する。次に、シリコン半導体基板20にp型半導体ウェル領域22を形成する。p型半導体ウェル領域22は、例えば、シリコン半導体基板20の形成すべきp型半導体ウェル領域以外の領域上に、レジストマスクなどのマスクを形成して、p型不純物をイオン注入して形成する。

裏面照射型固体撮像装置であれば、半導体基板表面の上方に層間絶縁膜を介して複数層の配線を形成してなる多層配線層を形成し、多層配線層上に平坦化膜を介してシリコン基板などによる支持基板を接合する。次いで、半導体基板の裏面側から例えば化学機械研磨(CMP)法により薄膜化する。次いで、半導体基板の裏面上に、反射防止膜などを介してカラーフィルタ及びオンチップレンズを形成する。このようにして、目的の固体撮像装置21を得る。

この結果、オ−バーフローバリアのばらつきを抑制し、画素特性を向上させた横型オ−バーフロー構造のCMOS固体撮像装置を精度よく製造することができる。

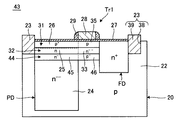

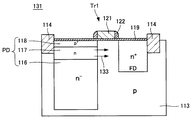

[固体撮像装置の構成例]

図7に、本発明に係る固体撮像装置、すなわちCMOS固体撮像装置の第2実施の形態を示す。図7は、表面照射型、裏面照射型を問わず適用できる横型オ−バーフロー構造を有するCMOS固体撮像装置であり、フォトダイオードPDと転送トランジスタを含む要部の概略構成を示す。

第2実施の形態に係る固体撮像装置43では、第1実施の形態と同様に、転送ゲート電極28下にフォトダイオードPDからフローティングディフージョン部FDに連接するようにn型半導体領域33によるオ−バーフローパスが形成される。電荷蓄積時、照射した光がフォトダイオードPD内で光電変換され、発生した信号電荷が電荷蓄積領域25に蓄積される。強い光が照射されて生じた最大電荷量を超える電荷は、転送ゲート電極28下のオ−バーフローパスとなるn型半導体領域33を通ってフローティングディフージョン部FDへ流れ、排出される。

次に、図8〜図10を用いて第2実施の形態に係る固体撮像装置43の製造方法例を説明する。まず、図8Aに示すように、シリコン半導体基板20の上面に熱酸化により絶縁膜37を形成する。次に、シリコン半導体基板20にp型半導体ウェル領域22を形成する。p型半導体ウェル領域22は、例えば、シリコン半導体基板20の形成すべきp型半導体ウェル領域以外の領域上に、レジストマスクなどのマスクを形成して、p型不純物をイオン注入して形成する。

裏面照射型固体撮像装置であれば、半導体基板表面の上方に層間絶縁膜を介して複数層の配線を形成してなる多層配線層を形成し、多層配線層上に平坦化膜を介してシリコン基板などによる支持基板を接合する。次いで、半導体基板の裏面側から例えば化学機械研磨(CMP)法により薄膜化する。次いで、半導体基板の裏面上に、反射防止膜などを介してカラーフィルタ及びオンチップレンズを形成する。このようにして、目的の固体撮像装置43を得る。

この結果、さらにオ−バーフローバリアのばらつきを抑制し、画素特性を向上させた横型オ−バーフロー構造のCMOS固体撮像装置を精度よく製造することができる。

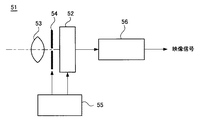

[電子機器の構成例]

上述の本発明に係る固体撮像装置は、例えば、デジタルスチルカメラ、デジタルビデオカメラ、さらにカメラ付き携帯電話などの各種携帯端末機器、プリンター等の電子機器に適用することができる。

Claims (12)

- 半導体基板に形成された光電変換部と画素トランジスタからなる複数の画素と、

前記画素内のフローティングディフージョン部と、

前記画素における光電変換部側の表面と、画素トランジスタのうちの転送トランジスタの転送ゲート電極下の半導体基板表面との全面にわたって形成された表面ピニング用の第1導電型イオン注入領域と、

前記第1導電型イオン注入領域の全域下に形成され、前記フローティングディフージョン部へのオ−バーフローパスとなるオ−バーフローパス形成用の第2導電型イオン注入領域とを有し、

前記転送ゲート電極下の前記第2導電型イオン注入領域によりオ−バーフローパスを形成するオ−バーフローバリアが形成され、

前記光電変換部における第2導電型半導体領域と前記オ−バーフローパス形成用の第2導電型イオン注入領域との重なる領域により電荷蓄積領域が形成される

固体撮像装置。 - 前記オ−バーフローパス形成用の第2導電型イオン注入領域の全域下に前記オ−バーフローバリアを安定させる第1導電型イオン注入領域を有する

請求項1記載の固体撮像装置。 - 前記表面ピニング用の第1の第1導電型イオン注入領域の前記光電変換部に対応する部分の不純物濃度が、該第1の第1導電型イオン注入領域の前記転送ゲート電極下の部分より高濃度である

請求項1または2記載の固体撮像装置。 - 前記表面ピニング用の第1導電型イオン注入領域の前記光電変換部に対応する部分の不純物濃度が、該表面ピニング用の第1導電型イオン注入領域の前記転送ゲート電極下の部分より高濃度であり、

前記オ−バーフローバリアを安定させる第1導電型イオン注入領域は、前記光電変換部に対応する部分が第2導電型半導体領域であって、前記転送ゲート電極下に対応した部分が第1導電型半導体領域である

請求項2記載の固体撮像装置。 - 半導体基板の各画素形成領域に形成すべき光電変換部の側の表面と、画素トランジスタのうちの転送トランジスタの転送ゲート電極下に対応する半導体基板表面と、フローティングディフージョン部に対応する半導体基板表面との全面にわたって、イオン注入法により表面ピニング用の第1導電型イオン注入領域と、該第1導電型イオン注入領域の全域下のオ−バーフローパス形成用の第2導電型イオン注入領域を形成する工程と、

前記半導体基板上にゲート絶縁膜を介して転送トランジスタを含む前記画素トランジスタのゲート電極を形成する工程と、

前記半導体基板に第2導電型不純物をイオン注入してフローティングディフージョン部を形成する工程と、

を有し、

前記転送ゲート電極下の前記第2導電型イオン注領域によりオ−バーフローパスを形成するオ−バーフローバリアを形成し、

前記光電変換部に形成した第2導電型半導体領域と前記オ−バーフローパス形成用の第2導電型イオン注入領域とが重なる領域により電荷蓄積領域を形成する

固体撮像装置の製造方法。 - 前記画素トランジスタのゲート電極を形成する前に、前記オ−バーフローパス形成用の第2導電型イオン注入領域の全域下に第1導電型不純物をイオン注入して前記オ−バーフローバリアを安定させる第1導電型イオン注入領域を形成する工程を有する

請求項5記載の固体撮像装置の製造方法。 - 前記表面ピニング用の第1導電型不純物のイオン注入により、前記光電変換部に対応する部分に、前記転送ゲート電極下の表面ピニング用の第1導電型イオン注入領域より高不純物濃度の表面ピニング用の第1導電型イオン注入領域を形成する

請求項5または請求項6記載の固体撮像装置の製造方法。 - 前記表面ピニング用の第1導電型不純物のイオン注入により、前記光電変換部に対応する部分に、前記転送ゲート電極下の表面ピニング用の第1導電型イオン注入領域より高不純物濃度の表面ピニング用の第1導電型イオン注入領域を形成し、

前記オ−バーフローバリアを安定化させる半導体領域は、前記光電変換に対応する部分を第2導電型とし、前記転送ゲート電極下に対応する部分を第1導電型とする

請求項6記載の固体撮像素子の製造方法。 - 固体撮像装置と、

前記固体撮像装置のフォトダイオードに入射光を導く光学系と、

前記固体撮像装置の出力信号を処理する信号処理回路を備え、

前記固体撮像装置は、

半導体基板に形成された光電変換部と画素トランジスタからなる複数の画素と、

前記画素内のフローティングディフージョン部と、

前記画素における光電変換部の第2導電型半導体領域の表面と、画素トランジスタのうちの転送トランジスタの転送ゲート電極下の半導体基板表面との全面にわたって形成された表面ピニング用の第1導電型イオン注入領域と、

前記第1導電型イオン注入領域の全域下に形成され、前記フローティングディフージョン部へのオ−バーフローパスとなるオ−バーフローパス形成用の第2導電型イオン注入領域とを有し、

前記転送ゲート電極下の前記第2導電型イオン注領域によりオ−バーフローパスを形成するオ−バーフローバリアが形成され、

前記光電変換部の第2導電型半導体領域と前記オ−バーフローパス形成用の第2導電型イオン注入領域との重なる領域により電荷蓄積領域が形成される

電子機器。 - 前記固体撮像装置において、

前記オ−バーフローパス形成用の第2導電型イオン注入領域の全域下に前記オ−バーフローバリアを安定させる第1導電型イオン注入領域を有する

請求項9記載の電子機器。 - 前記固体撮像装置において、

前記表面ピニング用の第1導電型イオン注入領域の前記光電変換部に対応する部分の不純物濃度が、該第1導電型イオン注入領域の前記転送ゲート電極下の部分より高濃度である

請求項9または10記載の電子機器。 - 前記固体撮像装置において、

前記表面ピニング用の第1導電型イオン注入領域の前記光電変換部に対応する部分の不純物濃度が、該第1導電型イオン注入領域の前記転送ゲート電極下の部分より高濃度であり、

前記オ−バーフローバリアを安定させる第1導電型イオン注入領域は、前記光電変換部に対応する部分が第2導電型半導体領域であって、前記転送ゲート電極下に対応した部分が第1導電型半導体領域である

請求項10記載の電子機器。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010016000A JP5621266B2 (ja) | 2010-01-27 | 2010-01-27 | 固体撮像装置とその製造方法、並びに電子機器 |

| US12/926,998 US8809921B2 (en) | 2010-01-27 | 2010-12-22 | Solid-state imaging apparatus, method of manufacturing same, and electronic apparatus |

| CN201110022293XA CN102169883A (zh) | 2010-01-27 | 2011-01-20 | 固态成像装置及其制造方法、电子设备 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010016000A JP5621266B2 (ja) | 2010-01-27 | 2010-01-27 | 固体撮像装置とその製造方法、並びに電子機器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011155152A true JP2011155152A (ja) | 2011-08-11 |

| JP5621266B2 JP5621266B2 (ja) | 2014-11-12 |

Family

ID=44308314

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010016000A Expired - Fee Related JP5621266B2 (ja) | 2010-01-27 | 2010-01-27 | 固体撮像装置とその製造方法、並びに電子機器 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8809921B2 (ja) |

| JP (1) | JP5621266B2 (ja) |

| CN (1) | CN102169883A (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014204043A (ja) * | 2013-04-08 | 2014-10-27 | キヤノン株式会社 | 光電変換装置および撮像システム |

| JP2015536569A (ja) * | 2012-11-16 | 2015-12-21 | エスアールアイ インターナショナルSRI International | Cmosマルチピンド(mp)ピクセル |

| WO2016125601A1 (ja) * | 2015-02-05 | 2016-08-11 | ソニー株式会社 | 固体撮像装置および電子機器 |

| JP2020080377A (ja) * | 2018-11-13 | 2020-05-28 | 国立大学法人静岡大学 | 固体撮像装置 |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI505453B (zh) * | 2011-07-12 | 2015-10-21 | Sony Corp | 固態成像裝置,用於驅動其之方法,用於製造其之方法,及電子裝置 |

| EP2822270A1 (en) * | 2012-02-27 | 2015-01-07 | Sony Corporation | Imaging element and electronic equipment |

| CN102709304B (zh) * | 2012-06-26 | 2013-06-19 | 天津大学 | 提高图像传感器满阱容量与量子效率光电二极管及方法 |

| DE102013110695A1 (de) * | 2012-10-02 | 2014-04-03 | Samsung Electronics Co., Ltd. | Bildsensor, Verfahren zum Betreiben desselben und Bildverarbeitungssystem mit demselben |

| US11322533B2 (en) * | 2013-03-14 | 2022-05-03 | Sony Semiconductor Solutions Corporation | Solid state image sensor tolerant to misalignment and having a high photoelectric conversion efficiency |

| US20140347442A1 (en) * | 2013-05-23 | 2014-11-27 | Yibing M. WANG | Rgbz pixel arrays, imaging devices, controllers & methods |

| CN103346161A (zh) * | 2013-06-24 | 2013-10-09 | 上海华力微电子有限公司 | 改善重叠背照式cmos图像传感器图像信号质量的方法 |

| CN103500750B (zh) * | 2013-10-21 | 2016-06-15 | 上海华力微电子有限公司 | 一种cmos图像传感器有源像素的结构及其制造方法 |

| KR20150109559A (ko) * | 2014-03-20 | 2015-10-02 | 주식회사 동부하이텍 | 씨모스 이미지 센서 및 그 제조 방법 |

| JP6623594B2 (ja) * | 2015-07-22 | 2019-12-25 | セイコーエプソン株式会社 | 固体撮像素子及びその製造方法 |

| FR3046495B1 (fr) | 2015-12-30 | 2018-02-16 | Stmicroelectronics (Crolles 2) Sas | Pixel de detection de temps de vol |

| CN115863370A (zh) * | 2016-10-28 | 2023-03-28 | 索尼公司 | 光检测装置 |

| JP6840555B2 (ja) * | 2017-01-30 | 2021-03-10 | キヤノン株式会社 | 固体撮像装置及び撮像システム |

| JP6855287B2 (ja) * | 2017-03-08 | 2021-04-07 | ソニーセミコンダクタソリューションズ株式会社 | 固体撮像装置、および電子機器 |

| KR102427832B1 (ko) * | 2017-04-12 | 2022-08-02 | 삼성전자주식회사 | 이미지 센서 |

| JP6650909B2 (ja) * | 2017-06-20 | 2020-02-19 | キヤノン株式会社 | 撮像装置、撮像システム、移動体、および、撮像装置の製造方法 |

| CN108231813A (zh) * | 2018-01-24 | 2018-06-29 | 德淮半导体有限公司 | 像素单元及其制造方法以及成像装置 |

| CN109273470A (zh) * | 2018-09-17 | 2019-01-25 | 德淮半导体有限公司 | 图像传感器及其形成方法 |

| KR20220030948A (ko) * | 2019-07-12 | 2022-03-11 | 소니 세미컨덕터 솔루션즈 가부시키가이샤 | 광 검출 장치 |

| KR20220125930A (ko) | 2021-03-08 | 2022-09-15 | 에스케이하이닉스 주식회사 | 이미지 센싱 장치 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003115580A (ja) * | 2001-10-04 | 2003-04-18 | Sony Corp | 固体撮像素子およびその製造方法 |

| JP2006019487A (ja) * | 2004-07-01 | 2006-01-19 | Nikon Corp | 増幅型固体撮像素子 |

| JP2006024962A (ja) * | 2002-06-27 | 2006-01-26 | Canon Inc | 固体撮像装置及び固体撮像装置を用いたカメラシステム |

| JP2006245499A (ja) * | 2005-03-07 | 2006-09-14 | Sony Corp | 固体撮像装置 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6489643B1 (en) * | 1998-06-27 | 2002-12-03 | Hynix Semiconductor Inc. | Photodiode having a plurality of PN junctions and image sensor having the same |

| JP3576033B2 (ja) | 1999-03-31 | 2004-10-13 | 株式会社東芝 | 固体撮像装置 |

| JP3759435B2 (ja) | 2001-07-11 | 2006-03-22 | ソニー株式会社 | X−yアドレス型固体撮像素子 |

| JP3840203B2 (ja) * | 2002-06-27 | 2006-11-01 | キヤノン株式会社 | 固体撮像装置及び固体撮像装置を用いたカメラシステム |

| US7420233B2 (en) * | 2003-10-22 | 2008-09-02 | Micron Technology, Inc. | Photodiode for improved transfer gate leakage |

| JP4810806B2 (ja) | 2004-07-30 | 2011-11-09 | ソニー株式会社 | 固体撮像装置 |

| KR100699849B1 (ko) * | 2005-06-21 | 2007-03-27 | 삼성전자주식회사 | 국부적인 불순물 영역을 갖는 cmos 이미지 소자 및 그제조방법 |

| JP5320659B2 (ja) | 2005-12-05 | 2013-10-23 | ソニー株式会社 | 固体撮像装置 |

| JP2008166607A (ja) | 2006-12-28 | 2008-07-17 | Sony Corp | 固体撮像装置とその製造方法、並びに半導体装置とその製造方法 |

| JP4420039B2 (ja) | 2007-02-16 | 2010-02-24 | ソニー株式会社 | 固体撮像装置 |

| US8072015B2 (en) | 2007-06-04 | 2011-12-06 | Sony Corporation | Solid-state imaging device and manufacturing method thereof |

| US8357984B2 (en) * | 2008-02-08 | 2013-01-22 | Omnivision Technologies, Inc. | Image sensor with low electrical cross-talk |

-

2010

- 2010-01-27 JP JP2010016000A patent/JP5621266B2/ja not_active Expired - Fee Related

- 2010-12-22 US US12/926,998 patent/US8809921B2/en active Active

-

2011

- 2011-01-20 CN CN201110022293XA patent/CN102169883A/zh active Pending

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003115580A (ja) * | 2001-10-04 | 2003-04-18 | Sony Corp | 固体撮像素子およびその製造方法 |

| JP2006024962A (ja) * | 2002-06-27 | 2006-01-26 | Canon Inc | 固体撮像装置及び固体撮像装置を用いたカメラシステム |

| JP2006019487A (ja) * | 2004-07-01 | 2006-01-19 | Nikon Corp | 増幅型固体撮像素子 |

| JP2006245499A (ja) * | 2005-03-07 | 2006-09-14 | Sony Corp | 固体撮像装置 |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015536569A (ja) * | 2012-11-16 | 2015-12-21 | エスアールアイ インターナショナルSRI International | Cmosマルチピンド(mp)ピクセル |

| JP2014204043A (ja) * | 2013-04-08 | 2014-10-27 | キヤノン株式会社 | 光電変換装置および撮像システム |

| WO2016125601A1 (ja) * | 2015-02-05 | 2016-08-11 | ソニー株式会社 | 固体撮像装置および電子機器 |

| US11195873B2 (en) | 2015-02-05 | 2021-12-07 | Sony Corporation | Solid-state imaging device and electronic device |

| US11791366B2 (en) | 2015-02-05 | 2023-10-17 | Sony Group Corporation | Solid-state imaging device and electronic device |

| JP2020080377A (ja) * | 2018-11-13 | 2020-05-28 | 国立大学法人静岡大学 | 固体撮像装置 |

| JP7340218B2 (ja) | 2018-11-13 | 2023-09-07 | 国立大学法人静岡大学 | 固体撮像装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5621266B2 (ja) | 2014-11-12 |

| US8809921B2 (en) | 2014-08-19 |

| US20110180860A1 (en) | 2011-07-28 |

| CN102169883A (zh) | 2011-08-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5621266B2 (ja) | 固体撮像装置とその製造方法、並びに電子機器 | |

| JP5365144B2 (ja) | 固体撮像装置とその製造方法、及び電子機器 | |

| US10306166B2 (en) | Solid-state imaging device, manufacturing method thereof, camera, and electronic device | |

| JP5564909B2 (ja) | 固体撮像装置とその製造方法、及び電子機器 | |

| JP5493430B2 (ja) | 固体撮像装置とその製造方法、及び電子機器 | |

| KR101683309B1 (ko) | 고체 촬상 장치 및 전자 기기 | |

| JP5564874B2 (ja) | 固体撮像装置、及び電子機器 | |

| JP2011159757A (ja) | 固体撮像装置とその製造方法、固体撮像装置の駆動方法、及び電子機器 | |

| TWI455295B (zh) | 固態成像裝置、電子設備及製造固態成像裝置之方法 | |

| JP2009272596A (ja) | 固体撮像装置とその製造方法、及び電子機器 | |

| WO2014002361A1 (ja) | 固体撮像装置及びその製造方法 | |

| TWI505454B (zh) | 固態攝像裝置及其驅動方法、固態攝像裝置之製造方法、以及電子資訊機器 | |

| JP5407282B2 (ja) | 固体撮像装置とその製造方法、及び電子機器 | |

| JP2011159758A (ja) | 固体撮像装置とその製造方法、並びに電子機器 | |

| JP5458135B2 (ja) | 固体撮像素子の製造方法 | |

| JP5600924B2 (ja) | 固体撮像装置とその製造方法並びにカメラ | |

| JP5842903B2 (ja) | 固体撮像装置、及び電子機器 | |

| JP2005317639A (ja) | 光電変換装置及びその製造方法 | |

| JP2011009466A (ja) | 固体撮像装置及び電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20121205 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131227 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140107 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140228 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140826 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140908 |

|

| LAPS | Cancellation because of no payment of annual fees |