JP2011040702A - コアレスパッケージ基板及びその製造方法 - Google Patents

コアレスパッケージ基板及びその製造方法 Download PDFInfo

- Publication number

- JP2011040702A JP2011040702A JP2009263062A JP2009263062A JP2011040702A JP 2011040702 A JP2011040702 A JP 2011040702A JP 2009263062 A JP2009263062 A JP 2009263062A JP 2009263062 A JP2009263062 A JP 2009263062A JP 2011040702 A JP2011040702 A JP 2011040702A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- package substrate

- circuit

- metal

- dielectric layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

- H05K3/4007—Surface contacts, e.g. bumps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/03—Conductive materials

- H05K2201/0332—Structure of the conductor

- H05K2201/0335—Layered conductors or foils

- H05K2201/0355—Metal foils

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/03—Conductive materials

- H05K2201/0332—Structure of the conductor

- H05K2201/0364—Conductor shape

- H05K2201/0367—Metallic bump or raised conductor not used as solder bump

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10613—Details of electrical connections of non-printed components, e.g. special leads

- H05K2201/10954—Other details of electrical connections

- H05K2201/10984—Component carrying a connection agent, e.g. solder, adhesive

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/10—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern

- H05K3/20—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern by affixing prefabricated conductor pattern

- H05K3/205—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern by affixing prefabricated conductor pattern using a pattern electroplated or electroformed on a metallic carrier

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistor

- H05K3/32—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits

- H05K3/34—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits by soldering

- H05K3/3457—Solder materials or compositions; Methods of application thereof

- H05K3/3473—Plating of solder

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4644—Manufacturing multilayer circuits by building the multilayer layer by layer, i.e. build-up multilayer circuits

- H05K3/4682—Manufacture of core-less build-up multilayer circuits on a temporary carrier or on a metal foil

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49117—Conductor or circuit manufacturing

- Y10T29/49124—On flat or curved insulated base, e.g., printed circuit, etc.

- Y10T29/49147—Assembling terminal to base

Abstract

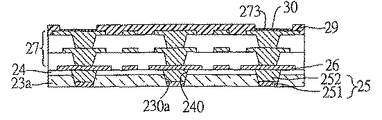

【解決手段】対向する第1の表面24aと第2の表面24bを有する補助誘電体層24と、第2の表面に設けられた内層回路26と、第2の表面と内層回路に設けられたビルドアップ構造からなる基板本体2と、対向する第1端252aと第2端252bを有する金属柱252と、第1端に設けられた半田層251とからなる複数の電気接触バンプ25とを備え、金属柱の第2端が補助誘電体層に位置して内層回路26に電気的に接続され、金属柱の第1端と半田層が補助誘電体層の第1の表面に突出される。

【選択図】図11

Description

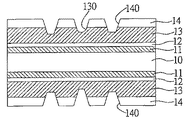

図12に示すように、まず、搭載板10を用意し、前記搭載板10の両表面に薄膜金属層11、離型膜12、キャリア金属層13が順次に設けられている。

図14に示すように、前記第1の誘電体層14にフォトリソグラフィ(photolithography)またはレーザーアブレーション(laser ablation)によって複数のビア140が形成され、エッチングによってそれらのビア140が露出されたキャリア金属層13の表面に複数の凹部(concave)130が形成されている。

図17に示すように、前記キャリア金属層13を除去し、第1の誘電体層14の表面に突出される半田バンプ141aが複数形成され、コアレスパッケージ基板を作成する。前記半田バンプ141aは後の工程において半導体チップ(図示せず)に接続され、前記電気接触パッド154は後にプリント回路基板(図示せず)に接続される。

本発明は、対向する両表面を有するキャリア層と、前記キャリア層の対向する両表面に形成された離型膜と、前記離型膜上に形成された金属層と、前記金属層に形成された第1のレジスト層と、前記第1のレジスト層に形成された補助誘電体層とからなり、且つ前記の各補助誘電体層に有効領域が定義された基材を用意する工程と、前記補助誘電体層及び前記第1のレジスト層に金属層の表面の一部を露出させる複数の開孔を形成する工程と、前記各開孔にめっきによって半田層と金属柱を順次に形成する工程と、前記補助誘電体層に第2のレジスト層を形成し、前記第2のレジスト層にフォトリソグラフィにより複数の開口領域を形成することにより、補助誘電体層の一部を露出させ、それに対応して前記の各金属柱を露出させる工程と、前記の各開口領域にめっきによって内層回路を形成し、且つ前記内層回路をそれらの前記金属柱に接続させる工程と、前記第2のレジスト層を除去する工程と、少なくとも一つの誘電体層と、前記誘電体層に設けられた回路層と、前記誘電体層に設けられ前記回路層と内層回路に電気的に接続された導電ビアとを備え、且つ、最外層の回路層に複数の電気接触パッドを備えたビルドアップ構造を、前記補助誘電体層と内層回路に形成する工程と、前記ビルドアップ構造に、前記の各電気接触パッドを対応させて露出するための絶縁保護層開孔を複数備えた絶縁保護層を形成する工程と、前記有効領域以外の部分を除去する工程と、前記キャリア層と離型膜を除去して前記金属層を露出させ、二つの基礎基板を形成する工程と、前記金属層を除去して前記各開孔における半田層と金属柱で電気接触バンプを形成する工程と、前記第1のレジスト層を除去し、補助誘電体層と、内層回路と、ビルドアップ構造とからなるコア層がない基板本体を形成し、前記の各電気接触バンプを前記補助誘電体層の表面に突出させる工程と、を備えるコアレスパッケージ基板の製造方法がさらに掲示されている。

また、前記製造方法は、電気接触パッドに表面処理層を形成する工程をさらに含み、前記表面処理層は、めっきニッケル/金、めっき銀、めっきスズ、電気ニッケル・無電解金(EGIN)、無電解ニッケル・無電解パラジウム・置換金(ENEPIG)、無電解スズめっき(Immersion Tin)、化学金、化学銀、プリフラックス(OSP)からなる群の一つから選ばれて成るものである。

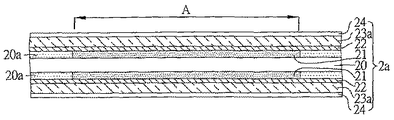

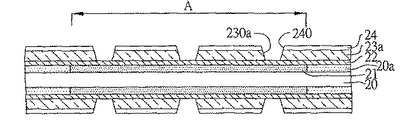

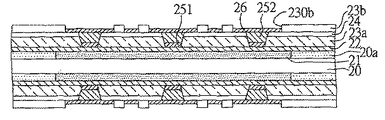

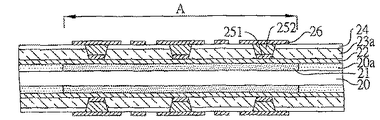

図1乃至図11は本発明に係るコアレスパッケージ基板の製造方法を示す図である。

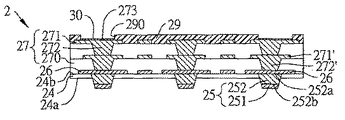

図2に示すように、補助誘電体層24と第1のレジスト層23aに複数の開孔240を形成し、金属層22表面の一部を露出させる。前記開孔240は、フォトリソグラフィ(photolithography)、レーザーアブレーション、またはプラズマ(plasma)によって形成される。また、開孔240を形成する工程について、まず、補助誘電体層24に孔状構造を形成した後、第1のレジスト層23aに前記孔状構造に対応するビア230aを形成し、連通された孔状構造とビア230aによって開孔240を形成し、または補助誘電体層24と第1のレジスト層23aを同時に貫通することで開孔240を形成する。また、第1のレジスト層23aは、フォトレジスト材または感光可能な樹脂材から成り、補助誘電体層24は、誘電体材から成る。

図4に示すように、補助誘電体層24に第2のレジスト層23bを形成し、フォトリソグラフィによって前記第2のレジスト層23bに複数の開口領域230bを形成することで、補助誘電体層24の一部を露出させ且つ各金属柱252を対応的に露出させた後、各開口領域230bにおける補助誘電体層24と金属柱252に、めっきにより、金属柱252に電気的に接続された内層回路26を形成する。

図6に示すように、補助誘電体層24と内層回路26に、少なくとも一つの誘電体層270と、前記誘電体層270に設けられた回路層271と、前記誘電体層270に設けられ前記回路層271に電気的に接続された導電ビア272とを備えたビルドアップ構造27を形成し、導電ビア272’の 一部は回路層271’と内層回路26に電気的に接続され、且つ、最外層の回路層271にプリント回路基板(図示せず)に接続されるための複数の電気接触パッド273を備える。

図10に示すように、金属層22を除去し、各開孔240における半田層251と金属柱252で電気接触バンプ25を形成する。また、各電気接触パッド273に表面処理層30を形成する。

前記基板本体2は、対向する第1の表面24aと第2の表面24bを有する補助誘電体層24と、前記第2の表面24bに設けられた内層回路26と、前記第2の表面24bと前記内層回路26上に設けられたビルドアップ構造27からなる。前記ビルドアップ構造27は、少なくとも一つの誘電体層270と、前記誘電体層270に設けられた回路層271と、前記誘電体層270に形成され前記回路層271に電気的に接続された複数の導電ビア272とを備え、導電ビア272’の一部が回路層271’と内層回路26に電気的に接続され、且つ、最外層の回路層271にプリント回路基板(図示せず)に接続されるための複数の電気接触パッド273を備える。

2 基板本体

2’ 基礎基板

2a 基材

10 搭載板

11 薄膜金属層

12、21 離型膜

13 キャリア金属層

14 第1の誘電体層

15、27 ビルドアップ構造

16、29 絶縁保護層

20 キャリア層

20a 接着層

22 金属層

23a 第1のレジスト層

23b 第2のレジスト層

24 補助誘電体層

24a 第1の表面

24b 第2の表面

25 電気接触バンプ

26 内層回路

30 表面処理層

130 凹部

140、230a ビア

141a 半田バンプ

141b 第1の導電ビア

142 第1の回路層

151 第2の誘電体層

152 第2の回路層

153 第2の導電ビア

154、273 電気接触パッド

160、290 絶縁保護層開孔

230b 開口領域

240 開孔

251 半田層

252 金属柱

252a 第1端

252b 第2端

270 誘電体層

271、271’ 回路層

272、272’ 導電ビア

A 有効領域

S-S 切断線

Claims (14)

- 対向する第1の表面と第2の表面を有する補助誘電体層と、前記第2の表面に設けられた内層回路と、前記第2の表面と前記内層回路に設けられたビルドアップ構造とからなり、前記ビルドアップ構造は、少なくとも一つの誘電体層と、前記誘電体層に設けられた回路層と、前記誘電体層に形成され前記回路層に電気的に接続された複数の導電ビアとを備え、且つ前記導電ビアの一部は前記回路層と前記内層回路に電気的に接続され、また、前記ビルドアップ構造の最外層の回路層に複数の電気接触パッドをさらに備える基板本体と、

対向する第1端と第2端を有する金属柱と、前記第1端に設けられた半田層とからなり、前記金属柱の前記第2端が前記補助誘電体層に位置して前記内層回路に電気的に接続され、且つ前記金属柱の前記第1端と前記半田層が前記補助誘電体層の前記第1の表面に突出される複数の電気接触バンプと、

を備えることを特徴とするコアレスパッケージ基板。 - 前記ビルドアップ構造に設けられ、且つ前記の各電気接触パッドを対応させて露出させるための絶縁保護層開孔が複数形成された絶縁保護層をさらに備えることを特徴とする請求項1に記載のコアレスパッケージ基板。

- 前記の各電気接触パッドに設けられた表面処理層をさらに備えることを特徴とする請求項2に記載のコアレスパッケージ基板。

- 前記表面処理層は、めっきニッケル/金、めっき銀、めっきスズ、電気ニッケル・無電解金(EGIN)、無電解ニッケル・無電解パラジウム・置換金(ENEPIG)、無電解スズめっき(Immersion Tin)、化学金、化学銀、プリフラックス(OSP)からなる群の一つから選ばれて成るものであることを特徴とする請求項3に記載のコアレスパッケージ基板。

- 前記金属柱は、銅柱であることを特徴とする請求項1に記載のコアレスパッケージ基板。

- 対向する両表面を有するキャリア層と、前記キャリア層の対向する両表面に形成された離型膜と、前記離型膜上に形成された金属層と、前記金属層に形成された第1のレジスト層と、前記第1のレジスト層に形成された補助誘電体層とからなり、且つ前記の各補助誘電体層に有効領域が定義された基材を用意する工程と、

前記補助誘電体層及び前記第1のレジスト層に金属層の一部の表面を露出させる複数の開孔を形成する工程と、

前記の各開孔にめっきによって半田層と金属柱を順次に形成する工程と、

前記補助誘電体層に第2のレジスト層を形成し、前記第2のレジスト層にフォトリソグラフィにより複数の開口領域を形成することにより、補助誘電体層の一部を露出させ、それに対応して前記の各金属柱を露出させる工程と、

前記の各開口領域にめっきによって内層回路を形成し、且つ前記内層回路をそれらの前記金属柱に接続させる工程と、

前記第2のレジスト層を除去する工程と、

少なくとも一つの誘電体層と、前記誘電体層に設けられた回路層と、前記誘電体層に設けられ前記回路層と前記内層回路に電気的に接続された導電ビアとを備え、且つ、最外層の前記回路層に複数の電気接触パッドを備えたビルドアップ構造を、前記補助誘電体層と前記内層回路に形成する工程と、

前記ビルドアップ構造に、前記の各電気接触パッドを対応させて露出させるための絶縁保護層開孔を複数備えた絶縁保護層を形成する工程と、

前記有効領域以外の部分を除去する工程と、

前記キャリア層と前記離型膜を除去して前記金属層を露出させ、二つの基礎基板を形成する工程と、

前記金属層を除去して前記各開孔における半田層と金属柱で電気接触バンプを形成する工程と、

前記第1のレジスト層を除去し、補助誘電体層と、内層回路と、ビルドアップ構造とからなり、コア層がない基板本体を形成し、前記の各電気接触バンプを前記補助誘電体層の表面に突出させる工程と、を備えることを特徴とするコアレスパッケージ基板の製造方法。 - 前記キャリア層と前記金属層の面積は前記有効領域に対応する前記離型膜の面積より大きいことを特徴とする請求項6に記載のコアレスパッケージ基板の製造方法。

- 前記基材は、前記キャリア層と前記金属層との間、及び前記離型膜以外の領域に接着層が形成されることを特徴とする請求項7に記載のコアレスパッケージ基板の製造方法。

- 前記有効領域以外の部分を除去する時、前記接着層をともに除去することを特徴とする請求項8に記載のコアレスパッケージ基板の製造方法。

- 前記金属層は銅箔であることを特徴とする請求項6に記載のコアレスパッケージ基板の製造方法。

- 前記金属柱は銅柱であることを特徴とする請求項6に記載のコアレスパッケージ基板の製造方法。

- 切断方法によって前記有効領域以外の部分を除去することを特徴とする請求項6に記載のコアレスパッケージ基板の製造方法。

- 前記電気接触パッドに表面処理層を形成する工程をさらに含むことを特徴とする請求項6に記載のコアレスパッケージ基板の製造方法。

- 前記表面処理層は、めっきニッケル/金、めっき銀、めっきスズ、電気ニッケル・無電解金(EGIN)、無電解ニッケル・無電解パラジウム・置換金(ENEPIG)、無電解スズめっき(Immersion Tin)、化学金、化学銀、プリフラックス(OSP)からなる群の一つから選ばれて成るものであることを特徴とする請求項13に記載のコアレスパッケージ基板の製造方法。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| TW098127676A TWI393233B (zh) | 2009-08-18 | 2009-08-18 | 無核心層封裝基板及其製法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011040702A true JP2011040702A (ja) | 2011-02-24 |

| JP2011040702A5 JP2011040702A5 (ja) | 2013-01-10 |

Family

ID=43768133

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009263062A Pending JP2011040702A (ja) | 2009-08-18 | 2009-11-18 | コアレスパッケージ基板及びその製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8227711B2 (ja) |

| JP (1) | JP2011040702A (ja) |

| TW (1) | TWI393233B (ja) |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012186270A (ja) * | 2011-03-04 | 2012-09-27 | Toppan Printing Co Ltd | 半導体パッケージの製造方法 |

| KR101222828B1 (ko) | 2011-06-24 | 2013-01-15 | 삼성전기주식회사 | 코어리스 기판의 제조방법 |

| JP2014049645A (ja) * | 2012-08-31 | 2014-03-17 | Panasonic Corp | 剥離可能銅箔付き基板及び回路基板の製造方法 |

| JP2015211146A (ja) * | 2014-04-28 | 2015-11-24 | 京セラサーキットソリューションズ株式会社 | 配線基板の製造方法 |

| CN106816388A (zh) * | 2015-12-02 | 2017-06-09 | 南茂科技股份有限公司 | 半导体封装结构及其制作方法 |

| CN106816389A (zh) * | 2015-12-02 | 2017-06-09 | 南茂科技股份有限公司 | 半导体封装结构及其制作方法 |

| KR20230096382A (ko) | 2021-12-23 | 2023-06-30 | 삼성전기주식회사 | 인쇄회로기판 제조 방법 |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009194321A (ja) * | 2008-02-18 | 2009-08-27 | Shinko Electric Ind Co Ltd | 配線基板及びその製造方法、半導体パッケージ |

| TWI419278B (zh) * | 2010-10-26 | 2013-12-11 | Unimicron Technology Corp | 封裝基板及其製法 |

| TWI411362B (zh) * | 2011-08-09 | 2013-10-01 | Unimicron Technology Corp | 無核心層之封裝基板及其製法 |

| US20170374748A1 (en) * | 2011-10-31 | 2017-12-28 | Unimicron Technology Corp. | Package structure and manufacturing method thereof |

| KR20140047967A (ko) * | 2012-10-15 | 2014-04-23 | 삼성전기주식회사 | 다층형 코어리스 인쇄회로기판 및 그 제조 방법 |

| US9491871B2 (en) | 2013-05-07 | 2016-11-08 | Unimicron Technology Corp. | Carrier substrate |

| KR20140143567A (ko) * | 2013-06-07 | 2014-12-17 | 삼성전기주식회사 | 반도체 패키지 기판 및 반도체 패키지 기판 제조 방법 |

| KR20150064976A (ko) * | 2013-12-04 | 2015-06-12 | 삼성전기주식회사 | 인쇄회로기판 및 그 제조방법 |

| US20150195912A1 (en) * | 2014-01-08 | 2015-07-09 | Zhuhai Advanced Chip Carriers & Electronic Substrate Solutions Technologies Co. Ltd. | Substrates With Ultra Fine Pitch Flip Chip Bumps |

| TWI655727B (zh) * | 2014-06-17 | 2019-04-01 | 恆勁科技股份有限公司 | 封裝基板及包含該封裝基板的覆晶封裝電路 |

| US9603247B2 (en) * | 2014-08-11 | 2017-03-21 | Intel Corporation | Electronic package with narrow-factor via including finish layer |

| CN105722299B (zh) * | 2014-12-03 | 2018-08-31 | 恒劲科技股份有限公司 | 中介基板及其制法 |

| CN106550554B (zh) | 2015-09-17 | 2020-08-25 | 奥特斯(中国)有限公司 | 用于制造部件载体的上面具有伪芯和不同材料的两个片的保护结构 |

| US9922845B1 (en) | 2016-11-03 | 2018-03-20 | Micron Technology, Inc. | Semiconductor package and fabrication method thereof |

| JP7154913B2 (ja) * | 2018-09-25 | 2022-10-18 | 株式会社東芝 | 半導体装置及びその製造方法 |

| TWI693872B (zh) | 2018-10-29 | 2020-05-11 | 欣興電子股份有限公司 | 電路板製造方法 |

| CN111148373B (zh) * | 2018-11-06 | 2021-06-29 | 欣兴电子股份有限公司 | 电路板制造方法 |

| US11637060B2 (en) | 2019-07-18 | 2023-04-25 | Unimicron Technology Corp. | Wiring board and method of manufacturing the same |

| TWI728410B (zh) * | 2019-07-18 | 2021-05-21 | 欣興電子股份有限公司 | 電路板結構及其製作方法 |

| CN112420522B (zh) * | 2019-08-23 | 2024-03-15 | 欣兴电子股份有限公司 | 封装结构及其制备方法 |

| CN115101424A (zh) * | 2022-08-22 | 2022-09-23 | 盛合晶微半导体(江阴)有限公司 | 一种有机中介层封装结构及制作方法 |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09283925A (ja) * | 1996-04-16 | 1997-10-31 | Toppan Printing Co Ltd | 半導体装置及びその製造方法 |

| JP2007158174A (ja) * | 2005-12-07 | 2007-06-21 | Shinko Electric Ind Co Ltd | 配線基板の製造方法及び電子部品実装構造体の製造方法 |

| JP2007158150A (ja) * | 2005-12-07 | 2007-06-21 | Shinko Electric Ind Co Ltd | 配線基板の製造方法及び電子部品実装構造体の製造方法 |

| JP2007173622A (ja) * | 2005-12-22 | 2007-07-05 | Kyocer Slc Technologies Corp | 配線基板の製造方法 |

| JP2007173775A (ja) * | 2005-12-20 | 2007-07-05 | Phoenix Precision Technology Corp | 回路基板構造及びその製法 |

| JP2007335700A (ja) * | 2006-06-16 | 2007-12-27 | Fujitsu Ltd | 配線基板の製造方法 |

| JP2008177619A (ja) * | 2008-04-11 | 2008-07-31 | Toppan Printing Co Ltd | チップキャリア及び半導体装置並びにチップキャリアの製造方法 |

| JP2010092907A (ja) * | 2008-10-03 | 2010-04-22 | Mitsui Mining & Smelting Co Ltd | 多層プリント配線板の製造方法及びその方法を用いて得られる多層プリント配線板 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7640655B2 (en) * | 2005-09-13 | 2010-01-05 | Shinko Electric Industries Co., Ltd. | Electronic component embedded board and its manufacturing method |

| KR100704919B1 (ko) * | 2005-10-14 | 2007-04-09 | 삼성전기주식회사 | 코어층이 없는 기판 및 그 제조 방법 |

| TWI295842B (en) * | 2006-04-19 | 2008-04-11 | Phoenix Prec Technology Corp | A method for manufacturing a coreless package substrate |

| JP5175489B2 (ja) * | 2007-04-27 | 2013-04-03 | 新光電気工業株式会社 | 半導体パッケージの製造方法 |

| JP4993739B2 (ja) * | 2007-12-06 | 2012-08-08 | 新光電気工業株式会社 | 配線基板、その製造方法及び電子部品装置 |

-

2009

- 2009-08-18 TW TW098127676A patent/TWI393233B/zh active

- 2009-11-18 JP JP2009263062A patent/JP2011040702A/ja active Pending

-

2010

- 2010-08-18 US US12/858,759 patent/US8227711B2/en active Active

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09283925A (ja) * | 1996-04-16 | 1997-10-31 | Toppan Printing Co Ltd | 半導体装置及びその製造方法 |

| JP2007158174A (ja) * | 2005-12-07 | 2007-06-21 | Shinko Electric Ind Co Ltd | 配線基板の製造方法及び電子部品実装構造体の製造方法 |

| JP2007158150A (ja) * | 2005-12-07 | 2007-06-21 | Shinko Electric Ind Co Ltd | 配線基板の製造方法及び電子部品実装構造体の製造方法 |

| JP2007173775A (ja) * | 2005-12-20 | 2007-07-05 | Phoenix Precision Technology Corp | 回路基板構造及びその製法 |

| JP2007173622A (ja) * | 2005-12-22 | 2007-07-05 | Kyocer Slc Technologies Corp | 配線基板の製造方法 |

| JP2007335700A (ja) * | 2006-06-16 | 2007-12-27 | Fujitsu Ltd | 配線基板の製造方法 |

| JP2008177619A (ja) * | 2008-04-11 | 2008-07-31 | Toppan Printing Co Ltd | チップキャリア及び半導体装置並びにチップキャリアの製造方法 |

| JP2010092907A (ja) * | 2008-10-03 | 2010-04-22 | Mitsui Mining & Smelting Co Ltd | 多層プリント配線板の製造方法及びその方法を用いて得られる多層プリント配線板 |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012186270A (ja) * | 2011-03-04 | 2012-09-27 | Toppan Printing Co Ltd | 半導体パッケージの製造方法 |

| KR101222828B1 (ko) | 2011-06-24 | 2013-01-15 | 삼성전기주식회사 | 코어리스 기판의 제조방법 |

| JP2014049645A (ja) * | 2012-08-31 | 2014-03-17 | Panasonic Corp | 剥離可能銅箔付き基板及び回路基板の製造方法 |

| JP2015211146A (ja) * | 2014-04-28 | 2015-11-24 | 京セラサーキットソリューションズ株式会社 | 配線基板の製造方法 |

| CN106816388A (zh) * | 2015-12-02 | 2017-06-09 | 南茂科技股份有限公司 | 半导体封装结构及其制作方法 |

| CN106816389A (zh) * | 2015-12-02 | 2017-06-09 | 南茂科技股份有限公司 | 半导体封装结构及其制作方法 |

| KR20230096382A (ko) | 2021-12-23 | 2023-06-30 | 삼성전기주식회사 | 인쇄회로기판 제조 방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| US8227711B2 (en) | 2012-07-24 |

| TWI393233B (zh) | 2013-04-11 |

| US20110042128A1 (en) | 2011-02-24 |

| TW201108367A (en) | 2011-03-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2011040702A (ja) | コアレスパッケージ基板及びその製造方法 | |

| JP2008085089A (ja) | 樹脂配線基板および半導体装置 | |

| US7698813B2 (en) | Method for fabricating conductive blind via of circuit substrate | |

| TWI530238B (zh) | 晶片封裝基板及其製作方法 | |

| JP2011134957A (ja) | 多層配線基板 | |

| JP2009253261A (ja) | 高密度回路基板及びその形成方法 | |

| JP2010171387A (ja) | 回路基板構造及びその製造方法 | |

| US9380712B2 (en) | Wiring substrate and semiconductor device | |

| KR102069659B1 (ko) | 반도체 패키지 기판 제조방법 및 이를 이용하여 제조된 반도체 패키지 기판 | |

| KR20130057314A (ko) | 인쇄회로기판 및 인쇄회로기판 제조 방법 | |

| CN102054814B (zh) | 无核心层封装基板及其制法 | |

| US8186043B2 (en) | Method of manufacturing a circuit board | |

| TWI393229B (zh) | 封裝基板的製作方法及其結構 | |

| KR100772432B1 (ko) | 인쇄 회로 기판 제조 방법 | |

| KR20150065029A (ko) | 인쇄회로기판, 그 제조방법 및 반도체 패키지 | |

| JP2007214568A (ja) | 回路基板構造 | |

| JP2009099730A (ja) | パッケージ基板の半田ボール配置側表面構造およびその製造方法 | |

| KR101523840B1 (ko) | 프린트 배선판 및 프린트 배선판의 제조 방법 | |

| TWI429348B (zh) | 側邊具有導電接觸件的積層印刷電路板模組及其製造方法 | |

| TWI566648B (zh) | Wiring board | |

| KR101222820B1 (ko) | 반도체 패키지 및 그 제조방법 | |

| JP2007324232A (ja) | Bga型多層配線板及びbga型半導体パッケージ | |

| JP2006049457A (ja) | 部品内蔵配線板、部品内蔵配線板の製造方法 | |

| JP2017103350A (ja) | プリント配線板及びその製造方法 | |

| JP2014072371A (ja) | プリント配線板及びプリント配線板の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121116 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20121116 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130514 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130521 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130820 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130910 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140401 |