JP2010066984A - 電流制限回路及び電流制限回路の駆動方法 - Google Patents

電流制限回路及び電流制限回路の駆動方法 Download PDFInfo

- Publication number

- JP2010066984A JP2010066984A JP2008232344A JP2008232344A JP2010066984A JP 2010066984 A JP2010066984 A JP 2010066984A JP 2008232344 A JP2008232344 A JP 2008232344A JP 2008232344 A JP2008232344 A JP 2008232344A JP 2010066984 A JP2010066984 A JP 2010066984A

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- bias voltage

- current

- transistor

- current limiting

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G05—CONTROLLING; REGULATING

- G05F—SYSTEMS FOR REGULATING ELECTRIC OR MAGNETIC VARIABLES

- G05F1/00—Automatic systems in which deviations of an electric quantity from one or more predetermined values are detected at the output of the system and fed back to a device within the system to restore the detected quantity to its predetermined value or values, i.e. retroactive systems

- G05F1/10—Regulating voltage or current

- G05F1/46—Regulating voltage or current wherein the variable actually regulated by the final control device is dc

- G05F1/56—Regulating voltage or current wherein the variable actually regulated by the final control device is dc using semiconductor devices in series with the load as final control devices

- G05F1/565—Regulating voltage or current wherein the variable actually regulated by the final control device is dc using semiconductor devices in series with the load as final control devices sensing a condition of the system or its load in addition to means responsive to deviations in the output of the system, e.g. current, voltage, power factor

- G05F1/569—Regulating voltage or current wherein the variable actually regulated by the final control device is dc using semiconductor devices in series with the load as final control devices sensing a condition of the system or its load in addition to means responsive to deviations in the output of the system, e.g. current, voltage, power factor for protection

- G05F1/573—Regulating voltage or current wherein the variable actually regulated by the final control device is dc using semiconductor devices in series with the load as final control devices sensing a condition of the system or its load in addition to means responsive to deviations in the output of the system, e.g. current, voltage, power factor for protection with overcurrent detector

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Electromagnetism (AREA)

- General Physics & Mathematics (AREA)

- Radar, Positioning & Navigation (AREA)

- Automation & Control Theory (AREA)

- Amplifiers (AREA)

- Continuous-Control Power Sources That Use Transistors (AREA)

Abstract

【解決手段】電流制限回路は、ドライバトランジスタ(M1)と、センス抵抗(Rsns)を介して入力端子(IN)に一端が接続され、他端が出力端子(OUT)に接続され、制御端子がドライバトランジスタ(M1)の制御端子に接続されたセンストランジスタ(M2)と、入力端子の電位を基準電位とするバイアス電圧(Vbais)と、センス抵抗の電圧降下とを入力し、ドライバトランジスタとセンストランジスタの制御端子に出力が接続された演算増幅回路(1)を備える。電流制限回路は、バイアス電圧の電圧値を、入力端子と出力端子の差電圧に応じて、所定のバイアス電圧以下になるように制御するバイアス電圧変更回路(10)をさらに備える。

【選択図】図1

Description

Ilim=Vbias(Rd+Rs)/(Rd・Rsns) ・・・(1)

なお、上記のような従来技術としては特許文献1に開示の技術がある。

Isns=(Vi−Vo)/(Rsns+Rs0) ・・・(2)

Vsns=Rsns・Isns=Rsns(Vi−Vo)/(Rsns+Rs0) ・・・(3)

Id=(Vi−Vo)/(Rd0+Rpara) ・・・(4)

Io=(Vi−Vo)/(Rsns+Rs0)+(Vi−Vo)/(Rd0+Rpara) ・・・(5)

Vi−Vo=Vbias0(Rsns+Rs0)/Rsns ・・・(6)

Imax=Vbias0(Rd0+Rpara+Rsns+Rs0)/Rsns(Rd0+Rpara) ・・・(7)

Isns=Vbias0/Rsns ・・・(8)

Id=K・Isns=K・Vbias0/Rsns ・・・(9)

K:ドライバトランジスタM1とセンストランジスタM2の素子サイズ比

Io=Vbias0(1+K)/Rsns ・・・(10)

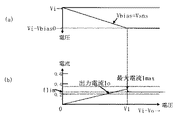

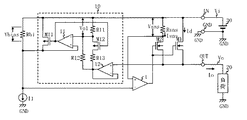

図1は、本発明の第1の実施形態における電流制限回路の回路図である。図12(a)に示す従来の電流制限回路と異なる点は、本実施形態の電流制限回路がバイアス電圧変更回路10をさらに備えている点である。バイアス電圧変更回路10以外の回路の部分に関しては、従来技術で既に説明を行なっているので、ここでの説明は省略する。

演算増幅回路12はボルテージフォロア回路を構成しているので、その出力電圧は、その入力電圧である出力端子OUTの電圧と同じである。抵抗R11とR12は直列接続され、入力端子INと演算増幅回路12の出力との間に接続されている。よって、抵抗R11と抵抗R12間の接続ノードの電圧は、入力電圧Viと出力電圧Voの差電圧(Vi−Vo)を、抵抗R11とR12の抵抗値で分圧した電圧となる。抵抗R11における電圧降下を電圧Vo1とすると電圧Vo1は次式で得られる。

Vo1=(Vi−Vo)・R11/(R11+R12) ・・・(11)

ここで、R11/(R11+R12)=1/Nとすると、式(11)から次式を得る。

Vo1=(Vi−Vo)/N ・・・(12)

Vbias=Vo1=(Vi−Vo)/N ・・・(12')

Isns=Vbias/Rsns ・・・(13)

また、ドライバトランジスタM1のドレイン電流Idは式(9)で表される。

Imax=Vbias(Rd0+Rpara+Rsns+Rs0)/Rsns(Rd0+Rpara) ・・・(7')

式(7')より最大出力電流Imaxの値はバイアス電圧Vbiasの値に比例することが分かるが、式(12')より、バイアス電圧Vbiasは差電圧(Vi−Vo)の1/Nに制御される。よって、Nを適宜設定することで、差電圧(Vi−Vo)が小さい場合、バイアス電圧Vbiasを小さくでき、最大出力電流Imaxを従来に比して低減することができる。

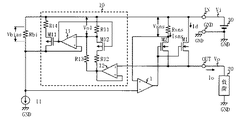

図3は、本発明の第2の実施形態における電流制限回路の回路図である。図1に示す実施の形態1の構成と異なる点は、バイアス電圧変更回路10bにおいて、抵抗R12と並列にPMOSトランジスタM12と抵抗R13の直列回路が接続され、PMOSトランジスタM12のゲートが演算増幅回路11の出力に接続されている点である。実施形態1の場合と同様、バイアス電圧変更回路10以外の回路の部分に関しての説明は省略する。

図5に、本発明の第3の実施形態における電流制限回路の回路図を示す。図3に示す実施の形態2の構成と異なる点は、抵抗R11とR12の接続ノードと接地端子GND間に電流源I11がさらに接続されている点である。前述の実施形態と同様、バイアス電圧変更回路10以外の電流制限回路部分に関しての説明は省略する。

Vo1={I11・R11・R23+(Vi−Vo)R11}/(R11+R23) (14)

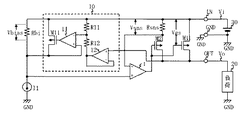

図7は、本発明の第4の実施形態における電流制限回路の回路図である。図3に示す実施の形態2の構成と異なる点は、抵抗R14がPMOSトランジスタM11のドレインと入力端子IN間に挿入されている点である。

Vb0=I1・Rbi・R14/(Rbi+R14) ・・・(15)

となり、数値を代入すると、Vb0=0.1×1×0.3/(1+0.3)≒0.023Vとなる。

図9は、本発明の第5の実施形態における電流制限回路の回路図である。この回路は図1に示す電流制限回路におけるMOSトランジスタM1、M2、M11の導電型を全て逆にして構成した回路である。そのため、ドライバトランジスタM1は接地端子GNDと出力端子OUT間に接続され、負荷20は入力端子INと出力端子OUT間に接続されている。また、他の回路も入力電圧Viと接地電位GND間の接続関係が全て逆になっている。

図10は、本発明の第6の実施形態における電流制限回路の回路図である。この回路は図1に示す電流制限回路におけるドライバトランジスタM1とセンストランジスタM2をPMOSトランジスタに置き換えたときの回路図である。

Rss=Rs・Vgs/(Vgs−Vbias) ・・・(16)

Rss≒1.11・Rs ・・・(17)

Ilim=0.1(0.1+1.11×1)/0.1×5=0.242A

図11は、本発明の第7の実施形態を示す電流制限回路の回路図である。この回路は、図10に示した電流制限回路に用いたMOSトランジスタM1、M2、M11の導電型を全て逆にして構成した回路である。そのため、ドライバトランジスタM1は接地端子GNDと出力端子OUT間に接続され、負荷20は入力端子INと出力端子OUT間に接続される。また、他の回路素子についても入力電圧Viと接地電位GNDに対する接続関係が全て逆になっている。

20 負荷

1、11 演算増幅回路

M1 ドライバトランジスタ

M2 センストランジスタ

Rbi バイアス抵抗

Rsns センス抵抗

R11〜R14 抵抗

I1,I11 電流源

Claims (12)

- 入力電圧が印加される入力端子と、

出力電圧を出力する出力端子と、

一端が入力端子に接続され、他端が前記出力端子に接続され、制御端子を備えたドライバトランジスタと、

一端がセンス抵抗を介して前記入力端子に接続され、他端が前記出力端子に接続され、制御端子が前記ドライバトランジスタの制御端子に接続されたセンストランジスタと、

前記入力端子の電位を基準電位とする、バイアス電圧と、前記センス抵抗における電圧降下とを入力し、前記ドライバトランジスタと前記センストランジスタの制御端子に出力が接続された第1演算増幅回路と、

前記バイアス電圧の電圧値を、前記入力端子と前記出力端子の差電圧に応じて、所定のバイアス電圧以下になるように制御するバイアス電圧変更回路と

を備えた電流制限回路。 - 前記バイアス電圧変更回路は、前記差電圧が小さいほど、前記バイアス電圧を小さくするように前記バイアス電圧の電圧値を制御する請求項1記載の電流制限回路。

- 前記バイアス電圧変更回路は、前記バイアス電圧が前記所定のバイアス電圧に達するまでは、前記バイアス電圧を前記差電圧の1/N(N>1)に制御する請求項2記載の電流制限回路。

- 前記バイアス電圧変更回路は、前記差電圧に応じて前記Nの値を変化させる請求項3記載の電流制限回路。

- 前記バイアス電圧に下限値を設定した請求項2ないし4のいずれか1つに記載の電流制限回路。

- 前記バイアス電圧は、前記入力端子に一端が接続されたバイアス抵抗に所定の電流を供給することで生成され、

前記バイアス電圧変更回路は、前記バイアス抵抗に並列に接続した可変インピーダンス素子のインピーダンスを前記差電圧に応じて制御する、請求項1ないし5のいずれか1つに記載の電流制限回路。 - 前記可変インピーダンス素子は第1MOSトランジスタである請求項6記載の電流制限回路。

- 前記バイアス電圧変更回路は、前記バイアス電圧を入力する第1入力端子と、前記差電圧を抵抗で分圧した電圧を入力する第2入力端子と、前記第1MOSトランジスタのゲートに接続された出力端子とを有する第2演算増幅回路を備える請求項7記載の電流制限回路。

- 前記バイアス電圧変更回路は、前記バイアス電圧を入力する第1入力端子と、前記差電圧を抵抗で分圧した電圧を入力する第2入力端子と、前記第1MOSトランジスタのゲートに接続された出力端子とを有する第2演算増幅回路を備え、

前記第2演算増幅回路の第2入力端子と、前記電流制限回路の出力端子との間に、前記第1MOSトランジスタと同じ導電型の第2MOSトランジスタと抵抗とが直列に接続され、前記第2MOSトランジスタのゲートに前記第2演算増幅回路の出力が接続された

請求項7記載の電流制限回路。 - 前記ドライバトランジスタと前記センストランジスタは同じ導電型のMOSトランジスタであり、両トランジスタのソースが前記電流制限回路の出力端子に接続された、請求項1ないし9のいずれか1つに記載の電流制限回路。

- 前記ドライバトランジスタと前記センストランジスタは同じ導電型のMOSトランジスタであり、両トランジスタのドレインが前記電流制限回路の出力端子に接続された請求項1ないし9のいずれか1つに記載の電流制限回路。

- 入力電圧が印加される入力端子と、

出力電圧を出力する出力端子と、

一端が入力端子に接続され、他端が前記出力端子に接続され、制御端子を備えたドライバトランジスタと、

一端がセンス抵抗を介して前記入力端子に接続され、他端が前記出力端子に接続され、制御端子が前記ドライバトランジスタの制御端子に接続されたセンストランジスタと、

前記入力端子の電位を基準電位とする、バイアス電圧と、前記センス抵抗における電圧降下とを入力し、前記ドライバトランジスタと前記センストランジスタの制御端子に出力が接続された第1演算増幅回路とを備えた電流制限回路の駆動方法であって、

バイアス電圧の電圧値を、前記入力端子と前記出力端子の差電圧に応じて、所定のバイアス電圧以下になるように制御する、

電流制限回路の駆動方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008232344A JP5089536B2 (ja) | 2008-09-10 | 2008-09-10 | 電流制限回路及び電流制限回路の駆動方法 |

| US12/555,107 US8149063B2 (en) | 2008-09-10 | 2009-09-08 | Current-restriction circuit and driving method therefor |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008232344A JP5089536B2 (ja) | 2008-09-10 | 2008-09-10 | 電流制限回路及び電流制限回路の駆動方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010066984A true JP2010066984A (ja) | 2010-03-25 |

| JP5089536B2 JP5089536B2 (ja) | 2012-12-05 |

Family

ID=41798673

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008232344A Expired - Fee Related JP5089536B2 (ja) | 2008-09-10 | 2008-09-10 | 電流制限回路及び電流制限回路の駆動方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8149063B2 (ja) |

| JP (1) | JP5089536B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2018197975A (ja) * | 2017-05-24 | 2018-12-13 | 新日本無線株式会社 | 過電流保護回路 |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10965254B2 (en) | 2018-06-04 | 2021-03-30 | Stmicroelectronics S.R.L. | Low noise amplifier circuit for a thermal varying resistance |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08116221A (ja) * | 1994-10-19 | 1996-05-07 | Nippondenso Co Ltd | 定電流回路 |

| JPH10289578A (ja) * | 1997-04-16 | 1998-10-27 | Fujitsu Ltd | 半導体記憶装置 |

| JP2001111369A (ja) * | 1999-10-14 | 2001-04-20 | Hitachi Ltd | 利得制御増幅回路、ミクサ回路及びそれらを用いた受信機、送信機 |

| JP2003017954A (ja) * | 2001-06-29 | 2003-01-17 | Hitachi Ltd | 高周波電力増幅回路 |

| JP3606994B2 (ja) * | 1996-02-27 | 2005-01-05 | 新日本無線株式会社 | 出力電流制限回路及び出力電流制限回路における出力電流調整方法 |

| JP2005080090A (ja) * | 2003-09-02 | 2005-03-24 | Toyota Industries Corp | 差動増幅回路の出力電圧制御回路及び電圧検出器 |

| JP2005322152A (ja) * | 2004-05-11 | 2005-11-17 | Toshiba Corp | 基準電圧回路 |

| JP2008181451A (ja) * | 2007-01-26 | 2008-08-07 | Ricoh Co Ltd | 定電流回路 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4451779A (en) * | 1982-04-22 | 1984-05-29 | Honeywell Inc. | Voltage controlled current source |

| US4553084A (en) * | 1984-04-02 | 1985-11-12 | Motorola, Inc. | Current sensing circuit |

| JPH0754336B2 (ja) | 1989-01-04 | 1995-06-07 | 日産自動車株式会社 | 電流センス回路 |

| JPH04223508A (ja) | 1990-12-26 | 1992-08-13 | Mitsumi Electric Co Ltd | 定電圧回路 |

| US5159516A (en) * | 1991-03-14 | 1992-10-27 | Fuji Electric Co., Ltd. | Overcurrent-detection circuit |

| US5233309A (en) * | 1992-01-09 | 1993-08-03 | Analog Devices, Inc. | Programmable gain amplifier |

| JP3644156B2 (ja) | 1996-11-13 | 2005-04-27 | 株式会社デンソー | 電流制限回路 |

| US6137366A (en) * | 1998-04-07 | 2000-10-24 | Maxim Integrated Products, Inc. | High VSWR mismatch output stage |

| JP2003333831A (ja) | 2002-05-15 | 2003-11-21 | Ricoh Co Ltd | 電源供給回路 |

| JP2006048394A (ja) | 2004-08-05 | 2006-02-16 | Toshiba Corp | 電流制限回路およびそれを用いた半導体集積装置、レギュレータ装置 |

| JP5057883B2 (ja) | 2007-08-09 | 2012-10-24 | 株式会社リコー | チャージポンプ回路 |

| US7760524B2 (en) * | 2007-10-17 | 2010-07-20 | Power Integrations, Inc. | Method and apparatus to reduce the volume required for bulk capacitance in a power supply |

-

2008

- 2008-09-10 JP JP2008232344A patent/JP5089536B2/ja not_active Expired - Fee Related

-

2009

- 2009-09-08 US US12/555,107 patent/US8149063B2/en not_active Expired - Fee Related

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08116221A (ja) * | 1994-10-19 | 1996-05-07 | Nippondenso Co Ltd | 定電流回路 |

| JP3606994B2 (ja) * | 1996-02-27 | 2005-01-05 | 新日本無線株式会社 | 出力電流制限回路及び出力電流制限回路における出力電流調整方法 |

| JPH10289578A (ja) * | 1997-04-16 | 1998-10-27 | Fujitsu Ltd | 半導体記憶装置 |

| JP2001111369A (ja) * | 1999-10-14 | 2001-04-20 | Hitachi Ltd | 利得制御増幅回路、ミクサ回路及びそれらを用いた受信機、送信機 |

| JP2003017954A (ja) * | 2001-06-29 | 2003-01-17 | Hitachi Ltd | 高周波電力増幅回路 |

| JP2005080090A (ja) * | 2003-09-02 | 2005-03-24 | Toyota Industries Corp | 差動増幅回路の出力電圧制御回路及び電圧検出器 |

| JP2005322152A (ja) * | 2004-05-11 | 2005-11-17 | Toshiba Corp | 基準電圧回路 |

| JP2008181451A (ja) * | 2007-01-26 | 2008-08-07 | Ricoh Co Ltd | 定電流回路 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2018197975A (ja) * | 2017-05-24 | 2018-12-13 | 新日本無線株式会社 | 過電流保護回路 |

Also Published As

| Publication number | Publication date |

|---|---|

| US8149063B2 (en) | 2012-04-03 |

| JP5089536B2 (ja) | 2012-12-05 |

| US20100060249A1 (en) | 2010-03-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5008472B2 (ja) | ボルテージレギュレータ | |

| US9298200B2 (en) | Constant voltage circuit with drooping and foldback overcurrent protection | |

| JP4443301B2 (ja) | ボルテージ・レギュレータ | |

| US9411345B2 (en) | Voltage regulator | |

| JP2010218543A (ja) | ボルテージレギュレータ | |

| JP2008015925A (ja) | 基準電圧発生回路 | |

| JP2009087203A (ja) | 定電流源回路 | |

| US20170205840A1 (en) | Power-supply circuit | |

| JP6498503B2 (ja) | 電流検出回路 | |

| US8040650B2 (en) | Excess-current protection circuit and power supply | |

| JP4058334B2 (ja) | ヒステリシスコンパレータ回路 | |

| US8674671B2 (en) | Constant-voltage power supply circuit | |

| JP6700550B2 (ja) | レギュレータ | |

| JP5089536B2 (ja) | 電流制限回路及び電流制限回路の駆動方法 | |

| KR101362474B1 (ko) | Cmos 서브밴드갭 기준발생기 | |

| US20150263679A1 (en) | Inverting amplifier | |

| JP5543059B2 (ja) | 差動増幅回路 | |

| JP4892366B2 (ja) | 過電流保護回路およびボルテージレギュレータ | |

| JP4773991B2 (ja) | ソースフォロア回路及び半導体装置 | |

| JP4555131B2 (ja) | 定電圧電源回路 | |

| JP5788739B2 (ja) | 電圧可変利得増幅回路 | |

| JP2015046193A (ja) | 定電流源回路 | |

| KR101141456B1 (ko) | 전압 레벨 시프터 | |

| KR101089849B1 (ko) | 씨모스(cmos) 회로에 적합한 전압 레귤레이터 | |

| JP6837894B2 (ja) | 降圧回路及び半導体集積回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110803 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120808 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120821 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120911 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150921 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |