JP5543059B2 - 差動増幅回路 - Google Patents

差動増幅回路 Download PDFInfo

- Publication number

- JP5543059B2 JP5543059B2 JP2007264532A JP2007264532A JP5543059B2 JP 5543059 B2 JP5543059 B2 JP 5543059B2 JP 2007264532 A JP2007264532 A JP 2007264532A JP 2007264532 A JP2007264532 A JP 2007264532A JP 5543059 B2 JP5543059 B2 JP 5543059B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- transistors

- circuit

- gate

- drain

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/45—Differential amplifiers

- H03F3/45071—Differential amplifiers with semiconductor devices only

- H03F3/45076—Differential amplifiers with semiconductor devices only characterised by the way of implementation of the active amplifying circuit in the differential amplifier

- H03F3/45179—Differential amplifiers with semiconductor devices only characterised by the way of implementation of the active amplifying circuit in the differential amplifier using MOSFET transistors as the active amplifying circuit

- H03F3/45183—Long tailed pairs

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/45—Differential amplifiers

- H03F3/45071—Differential amplifiers with semiconductor devices only

- H03F3/45076—Differential amplifiers with semiconductor devices only characterised by the way of implementation of the active amplifying circuit in the differential amplifier

- H03F3/45475—Differential amplifiers with semiconductor devices only characterised by the way of implementation of the active amplifying circuit in the differential amplifier using IC blocks as the active amplifying circuit

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/45—Differential amplifiers

- H03F3/45071—Differential amplifiers with semiconductor devices only

- H03F3/45479—Differential amplifiers with semiconductor devices only characterised by the way of common mode signal rejection

- H03F3/45632—Differential amplifiers with semiconductor devices only characterised by the way of common mode signal rejection in differential amplifiers with FET transistors as the active amplifying circuit

- H03F3/45744—Differential amplifiers with semiconductor devices only characterised by the way of common mode signal rejection in differential amplifiers with FET transistors as the active amplifying circuit by offset reduction

- H03F3/45748—Differential amplifiers with semiconductor devices only characterised by the way of common mode signal rejection in differential amplifiers with FET transistors as the active amplifying circuit by offset reduction by using a feedback circuit

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45136—One differential amplifier in IC-block form being shown

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45212—Indexing scheme relating to differential amplifiers the differential amplifier being designed to have a reduced offset

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45244—Indexing scheme relating to differential amplifiers the differential amplifier contains one or more explicit bias circuits, e.g. to bias the tail current sources, to bias the load transistors

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45626—Indexing scheme relating to differential amplifiers the LC comprising biasing means controlled by the input signal

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45674—Indexing scheme relating to differential amplifiers the LC comprising one current mirror

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45682—Indexing scheme relating to differential amplifiers the LC comprising one or more op-amps

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45696—Indexing scheme relating to differential amplifiers the LC comprising more than two resistors

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45702—Indexing scheme relating to differential amplifiers the LC comprising two resistors

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45732—Indexing scheme relating to differential amplifiers the LC comprising a voltage generating circuit

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Amplifiers (AREA)

Description

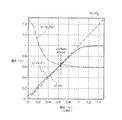

1)V(OUTb)とV(OUT)が等しい時、即ちトランジスタM3とトランジスタM4のドレイン電圧が等しい時にオフセット電圧はゼロになる。

2)上記以外の条件では、有限のrds4(即ち有限のゲインrds4・gm2)では、オフセットをゼロにする事はできない。

図1は、本発明の差動増幅回路の基本的構成を示すブロック図であり、図2は、図1の差動増幅回路の具体的構成例(第1の実施の形態)で構成したボルテージフォロワ回路を示す回路図である。

図4は本発明の第2の実施の形態の差動増幅回路を用いて構成したボルテージフォロワ回路の例を示している。第1の実施の形態の場合には、予め目標電圧が与えられている場合に適しているが、図4の場合は、比較的広い範囲で任意の電圧に対してオフセットを抑制する事が可能である。なお、図4において、図2と同一の構成には同一の参照符号を付けている。

図7は、本発明の第3の実施の形態の差動増幅回路を用いて構成したボルテージフォロワ回路の例を示している。図2の第1の実施の形態の抵抗R2をNチャネルMOSトランジスタM11で置き換え、そのゲート電圧を出力電圧V(OUT)に応じて制御する事で(より詳細には出力電圧V(OUT)と接点OUTbの電圧V(OUTb)の電位差を無くすように制御する事で)、任意の目標電圧に対応できるようにしたものである。トランジスタM11のゲート電圧制御手段として差動増幅回路A1を設け、その正入力端子を出力端子OUTに、負入力端子を接点OUTbに接続している。この回路の場合、トランジスタM11は可変抵抗素子というよりは、ソースフォロワ回路として動作する事になる。即ち、トランジスタM11のゲート電位は、トランジスタM11のゲート・ソース間電圧をVGS11とすると、V(OUT)+VGS11であり、このVGS11は抵抗R1の電圧降下R1・I3がトランジスタM3のゲート・ソース間電圧VGS3になるように決まる。このVGS3とVGS11はV(OUT)にはあまり依存しないので、ほぼ一定と見做す事ができるので、トランジスタM11はソースフォロワ回路として動作する事が分かる。トランジスタM11と差動増幅回路A1によって、接点OUTbと出力端子OUTは等しい電圧に制御されるので、式1に従ってオフセット電圧がゼロになる。

図8は、本発明の第4の実施の形態の差動増幅回路を用いて構成したボルテージフォロワ回路の例を示している。図7のゲート電圧制御手段である差動増幅回路A1を抵抗R3とNチャネルMOSトランジスタM12で置き換えた構成になっている。すなわち、差動増幅回路A1を無くし、一端が電源VDDに接続され他端がトランジスタM12のドレインに接続された抵抗R3と、ゲートがドレインおよびトランジスタM11のゲートに接続されソースが出力端子OUTに接続されたトランジスタM12を設けている。

図10は、本発明の第5の実施の形態の差動増幅回路を用いて構成したボルテージフォロワ回路の例を示している。図8の抵抗R1とR3をPチャネルMOSトランジスタM13、M14に置き換えたものである。すなわち、抵抗R1とR3を無くし、ソースを電源VDDにドレインをトランジスタM11のドレインに接続したトランジスタM13と、ソースを電源VDDにドレインをトランジスタM12のドレインに接続したトランジスタM14を設けている。抵抗よりもMOSトランジスタで抵抗手段を代替したほうが面積の節約ができる場合に有効である。

これまでの説明で既に明らかであるように、上記の各実施の形態は、図1の出力端子OUTと接点OUTbの電位を等しくする事により、差動増幅回路の入力オフセット電圧を抑制する事が可能である。

2 定電流源回路

3 カレントミラー負荷回路

4 バイアス発生回路

M3、M4、M5、M9、M10、M13、M14 PチャネルMOSトランジスタ

M0、M1、M2、M6、M7、M8、M11、M12 NチャネルMOSトランジスタ

R1、R2、R3 抵抗

A1、DA1 差動増幅回路

Claims (6)

- 1対のNチャネルMOSトランジスタからなり、各トランジスタのゲートに差動入力信号端子を接続し、各トランジスタのソースが互いに接続された差動トランジスタ対と、

差動トランジスタ対のソースと接地との間に接続された定電流源回路と、

1対のPチャネルMOSトランジスタからなり、各トランジスタのゲートが互いに接続され、各トランジスタのソースが電源に接続され、各トランジスタのドレインが差動トランジスタ対の各トランジスタの各ドレインにそれぞれ接続されたカレントミラー負荷回路と、

カレントミラー負荷回路の各トランジスタの各ドレインの一方の電位と他方の電位を等しくするように、各トランジスタのゲートバイアスおよびドレインバイアスを発生するバイアス発生回路とを備え、

前記バイアス発生回路が、

前記カレントミラー負荷回路の各トランジスタのゲートと電源の間に接続された第1の抵抗と、

前記カレントミラー負荷回路の一方のトランジスタのドレインとゲートの間に接続された第2の抵抗素子と

からなることを特徴とする差動増幅回路。 - 1対のNチャネルMOSトランジスタからなり、各トランジスタのゲートに差動入力信号端子を接続し、各トランジスタのソースが互いに接続された差動トランジスタ対と、

差動トランジスタ対のソースと接地との間に接続された定電流源回路と、

1対のPチャネルMOSトランジスタからなり、各トランジスタのゲートが互いに接続され、各トランジスタのソースが電源に接続され、各トランジスタのドレインが差動トランジスタ対の各トランジスタの各ドレインにそれぞれ接続されたカレントミラー負荷回路と、

カレントミラー負荷回路の各トランジスタの各ドレインの一方の電位と他方の電位を等しくするように、各トランジスタのゲートバイアスおよびドレインバイアスを発生するバイアス発生回路とを備え、

前記バイアス発生回路が、

前記カレントミラー負荷回路の各トランジスタのゲートと電源の間に接続されたPチャネルMOSトランジスタと、

前記カレントミラー負荷回路の一方のトランジスタのドレインとゲートの間に接続された抵抗素子と、

そのPチャネルMOSトランジスタのゲートに出力が接続されたバイアス制御用の差動増幅回路であって、その負入力端子が前記カレントミラー負荷の一方のトランジスタのドレインに接続され、正入力端子が他方のトランジスタのドレインに接続されたものと

からなることを特徴とする差動増幅回路。 - 1対のNチャネルMOSトランジスタからなり、各トランジスタのゲートに差動入力信号端子を接続し、各トランジスタのソースが互いに接続された差動トランジスタ対と、

差動トランジスタ対のソースと接地との間に接続された定電流源回路と、

1対のPチャネルMOSトランジスタからなり、各トランジスタのゲートが互いに接続され、各トランジスタのソースが電源に接続され、各トランジスタのドレインが差動トランジスタ対の各トランジスタの各ドレインにそれぞれ接続されたカレントミラー負荷回路と、

カレントミラー負荷回路の各トランジスタの各ドレインの一方の電位と他方の電位を等しくするように、各トランジスタのゲートバイアスおよびドレインバイアスを発生するバイアス発生回路とを備え、

前記バイアス発生回路が、

前記カレントミラー負荷回路の各トランジスタのゲートと電源の間に接続された抵抗素子と、

前記カレントミラー負荷回路の一方のトランジスタのドレインとゲートの間に接続されたNチャネルMOSトランジスタと、

そのNチャネルMOSトランジスタのゲートに出力が接続されたバイアス制御用の差動増幅回路であって、その負入力端子が前記カレントミラー負荷の一方のトランジスタのドレインに接続され、正入力端子が他方のトランジスタのドレインに接続されたものと

からなることを特徴とする差動増幅回路。 - 1対のNチャネルMOSトランジスタからなり、各トランジスタのゲートに差動入力信号端子を接続し、各トランジスタのソースが互いに接続された差動トランジスタ対と、

差動トランジスタ対のソースと接地との間に接続された定電流源回路と、

1対のPチャネルMOSトランジスタからなり、各トランジスタのゲートが互いに接続され、各トランジスタのソースが電源に接続され、各トランジスタのドレインが差動トランジスタ対の各トランジスタの各ドレインにそれぞれ接続されたカレントミラー負荷回路と、

カレントミラー負荷回路の各トランジスタの各ドレインの一方の電位と他方の電位を等しくするように、各トランジスタのゲートバイアスおよびドレインバイアスを発生するバイアス発生回路とを備え、

前記バイアス発生回路が、

前記カレントミラー負荷回路の各トランジスタのゲートと電源の間に接続された第1の抵抗素子と、

前記カレントミラー負荷回路の一方のトランジスタのドレインとゲートの間に接続された第1のNチャネルMOSトランジスタと、

前記カレントミラー負荷回路の他方のトランジスタのドレインにソースを接続され、ゲートとドレインが第1のNチャネルMOSトランジスタのゲートに接続された第2のNチャネルMOSトランジスタと

電源と第2のNチャネルMOSのゲートの間に接続された第2の抵抗素子と

からなることを特徴とする差動増幅回路。 - 前記第1の抵抗素子と第2の抵抗素子を各々MOSトランジスタで置き換えた

ことを特徴とする請求項4に記載の差動増幅回路。 - 前記差動入力信号端子の一方と、前記カレントミラー負荷回路の一方のトランジスタのドレインとを接続することでボルテージフォロワ回路を形成している

ことを特徴とする請求項1〜5のいずれか1項に記載の差動増幅回路。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007264532A JP5543059B2 (ja) | 2007-10-10 | 2007-10-10 | 差動増幅回路 |

| US12/285,598 US7859339B2 (en) | 2007-10-10 | 2008-10-09 | Differential amplification circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007264532A JP5543059B2 (ja) | 2007-10-10 | 2007-10-10 | 差動増幅回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009094878A JP2009094878A (ja) | 2009-04-30 |

| JP5543059B2 true JP5543059B2 (ja) | 2014-07-09 |

Family

ID=40533600

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007264532A Expired - Fee Related JP5543059B2 (ja) | 2007-10-10 | 2007-10-10 | 差動増幅回路 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7859339B2 (ja) |

| JP (1) | JP5543059B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011155488A (ja) * | 2010-01-27 | 2011-08-11 | Ricoh Co Ltd | 差動入力段回路、差動入力段回路を備えた演算増幅器及び電圧レギュレータ回路 |

| US8928408B2 (en) * | 2013-01-24 | 2015-01-06 | Aeroflex Colorado Springs Inc. | High-gain low-noise preamplifier and associated amplification and common-mode control method |

| JP6082297B2 (ja) * | 2013-03-27 | 2017-02-15 | 新日本無線株式会社 | 電流源回路 |

| DE102014109118B4 (de) * | 2014-06-30 | 2016-01-14 | Intel IP Corporation | Schaltung, integrierte Schaltung, Empfänger, Sende-Empfangs-Gerät und ein Verfahren zum Verstärken eines Eingangssignals |

| EP3228002A1 (en) * | 2014-12-05 | 2017-10-11 | Analog Devices, Inc. | High gain load circuit for a differential pair using depletion mode transistors |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4334196A (en) * | 1980-03-18 | 1982-06-08 | Rca Corporation | Amplifier using lateral and vertical transistors |

| JPS6253512A (ja) * | 1985-09-03 | 1987-03-09 | Anritsu Corp | パルス出力装置 |

| JPS62104305A (ja) | 1985-10-31 | 1987-05-14 | Toshiba Corp | カレントミラ−回路 |

| JPH0697490B2 (ja) | 1987-09-28 | 1994-11-30 | シャープ株式会社 | ダブルアジマスヘッド |

| JPS6486606A (en) * | 1987-09-28 | 1989-03-31 | Nec Corp | Operational amplifier circuit |

| US4972158A (en) * | 1989-10-31 | 1990-11-20 | International Business Machines Corporation | Transistor amplifier with variable bias circuits |

| JPH03169107A (ja) | 1989-11-28 | 1991-07-22 | Nec Corp | カレントミラー回路 |

| JPH0514075A (ja) | 1991-07-05 | 1993-01-22 | Matsushita Electric Ind Co Ltd | 差動増幅回路 |

| EP0840951B1 (en) * | 1996-05-22 | 2001-10-04 | Koninklijke Philips Electronics N.V. | Amplifier with active-bootstrapped gain-enhancement technique |

| JPH11284448A (ja) * | 1998-03-31 | 1999-10-15 | Nec Corp | 差動増幅器 |

| JP4029958B2 (ja) * | 2001-04-16 | 2008-01-09 | 日本電信電話株式会社 | 半導体回路 |

| JP4251826B2 (ja) * | 2002-06-26 | 2009-04-08 | 株式会社リコー | 定電圧回路 |

| US6967532B2 (en) * | 2003-12-30 | 2005-11-22 | Intel Corporation | Offset-compensated self-biased differential amplifier |

| JP4703133B2 (ja) * | 2004-05-25 | 2011-06-15 | ルネサスエレクトロニクス株式会社 | 内部電圧発生回路および半導体集積回路装置 |

| US20110018621A1 (en) * | 2006-01-31 | 2011-01-27 | Nxp B.V. | Current mirror circuit |

-

2007

- 2007-10-10 JP JP2007264532A patent/JP5543059B2/ja not_active Expired - Fee Related

-

2008

- 2008-10-09 US US12/285,598 patent/US7859339B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20090096523A1 (en) | 2009-04-16 |

| US7859339B2 (en) | 2010-12-28 |

| JP2009094878A (ja) | 2009-04-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4834347B2 (ja) | 定電流回路 | |

| CN101615049B (zh) | 参考缓冲电路 | |

| JP4676885B2 (ja) | バイアス回路 | |

| JP4800781B2 (ja) | 電圧レベルシフト回路、および半導体集積回路 | |

| JP5657853B2 (ja) | 定電流源回路 | |

| JP5690469B2 (ja) | 差動増幅器、基準電圧発生回路、差動増幅方法及び基準電圧発生方法 | |

| JP5334180B2 (ja) | 分圧回路 | |

| JP5543059B2 (ja) | 差動増幅回路 | |

| JP5092687B2 (ja) | 増幅装置及びGm補償バイアス回路 | |

| JP2005244276A (ja) | 差動増幅回路 | |

| JP4058334B2 (ja) | ヒステリシスコンパレータ回路 | |

| JP4829650B2 (ja) | 差動増幅回路 | |

| TW201838327A (zh) | 跨導放大器 | |

| JP4555131B2 (ja) | 定電圧電源回路 | |

| JP2012216171A (ja) | 基準電圧回路 | |

| JP6949463B2 (ja) | シングル差動変換回路 | |

| JP6705233B2 (ja) | オフセット補正回路およびトランスコンダクタンス比例電流生成回路 | |

| JP2007180796A (ja) | 差動増幅回路 | |

| JP2000252768A (ja) | 演算増幅器 | |

| JP2015046193A (ja) | 定電流源回路 | |

| JP4819583B2 (ja) | Ota回路 | |

| JP7025498B2 (ja) | メモリ制御装置及びメモリ制御方法 | |

| KR100338340B1 (ko) | 연산 증폭기 | |

| JP2005080090A (ja) | 差動増幅回路の出力電圧制御回路及び電圧検出器 | |

| JP5203809B2 (ja) | 電流ミラー回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100913 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111027 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20130731 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20130801 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130905 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131008 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20131030 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20131213 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20131226 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20140107 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140403 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140422 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140508 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5543059 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |