JP2010061801A - ダイナミック連想メモリセル - Google Patents

ダイナミック連想メモリセル Download PDFInfo

- Publication number

- JP2010061801A JP2010061801A JP2009278793A JP2009278793A JP2010061801A JP 2010061801 A JP2010061801 A JP 2010061801A JP 2009278793 A JP2009278793 A JP 2009278793A JP 2009278793 A JP2009278793 A JP 2009278793A JP 2010061801 A JP2010061801 A JP 2010061801A

- Authority

- JP

- Japan

- Prior art keywords

- line

- search

- data

- cell

- content addressable

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims abstract description 25

- 239000003990 capacitor Substances 0.000 claims abstract description 24

- 229920005591 polysilicon Polymers 0.000 claims description 24

- 210000004027 cell Anatomy 0.000 description 92

- 238000000034 method Methods 0.000 description 10

- 238000010586 diagram Methods 0.000 description 8

- 238000013461 design Methods 0.000 description 7

- 230000000295 complement effect Effects 0.000 description 6

- 239000002184 metal Substances 0.000 description 6

- 239000004065 semiconductor Substances 0.000 description 4

- 238000013500 data storage Methods 0.000 description 3

- 230000003068 static effect Effects 0.000 description 3

- 210000000352 storage cell Anatomy 0.000 description 3

- 230000008878 coupling Effects 0.000 description 2

- 238000010168 coupling process Methods 0.000 description 2

- 238000005859 coupling reaction Methods 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 230000006872 improvement Effects 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 230000003213 activating effect Effects 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 239000003989 dielectric material Substances 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 230000000977 initiatory effect Effects 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 239000000758 substrate Substances 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C15/00—Digital stores in which information comprising one or more characteristic parts is written into the store and in which information is read-out by searching for one or more of these characteristic parts, i.e. associative or content-addressed stores

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/565—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using capacitive charge storage elements

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C15/00—Digital stores in which information comprising one or more characteristic parts is written into the store and in which information is read-out by searching for one or more of these characteristic parts, i.e. associative or content-addressed stores

- G11C15/04—Digital stores in which information comprising one or more characteristic parts is written into the store and in which information is read-out by searching for one or more of these characteristic parts, i.e. associative or content-addressed stores using semiconductor elements

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C15/00—Digital stores in which information comprising one or more characteristic parts is written into the store and in which information is read-out by searching for one or more of these characteristic parts, i.e. associative or content-addressed stores

- G11C15/04—Digital stores in which information comprising one or more characteristic parts is written into the store and in which information is read-out by searching for one or more of these characteristic parts, i.e. associative or content-addressed stores using semiconductor elements

- G11C15/043—Digital stores in which information comprising one or more characteristic parts is written into the store and in which information is read-out by searching for one or more of these characteristic parts, i.e. associative or content-addressed stores using semiconductor elements using capacitive charge storage elements

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Dram (AREA)

- Semiconductor Memories (AREA)

- Static Random-Access Memory (AREA)

Abstract

【解決手段】ダイナミック連想メモリは、ビット・ラインとワード・ラインの交差部に位置する複数のダイナミック連想メモリセルを備える。各セルは、ワード・ラインに接続されるゲート端子およびビット・ラインに接続される第1ソース/ドレイン端子を有するアクセス・トランジスタと、アクセス・トランジスタの第2ソース/ドレイン端子に接続される第1プレートを有する第1メモリセル・キャパシタと、ポリシリコン相互接続層だけを介してアクセス・トランジスタの第2ソース/ドレイン端子に接続されるゲート端子を有する、マッチ・ラインの整合結果または不整合結果を示すための比較トランジスタとを含む。

【選択図】図2

Description

(1.発明の分野)

本発明は、ダイナミック動作をする連想メモリ(CAM)に関し、さらに特定すると高速で大容量のダイナミックCAMアレイを形成するのに適したダイナミック連想メモリセルに関する。

連想メモリ(CAM)はメモリ素子のグループが物理的な位置よりもむしろその内容で選択または識別されるメモリである。概して、CAMは縦列および横列に配置されたCAMセルのマトリクスを含む。それぞれのCAMセルは1ビットのデジタル・データを保存し、保存したデータと外部から供給される探索データとを比較することのできる回路を含む。1つまたは複数ビットの横列が1つのワードを構成する。連想メモリは探索ワードをCAM内部に保存したワードのセットと比較する。探索および比較の作業の間において、それぞれのワードに組み込まれた表示装置が比較結果を生み出し、探索ワードが保存ワードと一致するかどうかを表示する。

本発明の目的は、改良したダイナミック連想メモリ(CAM)セルを提供することであり、これは、2値および3値の記憶能力を有する、比較的高速で大容量のCAMアレイを構築するのに適している。

第1のデータ・ビットを記憶するための第1の記憶装置と、

第1のデータ・ビットと無関係の値を有する第2のデータ・ビットを記憶するための第2の記憶装置と、

第1および第2のデータ・ビットを独立して第1および第2のデータ記憶装置に書き込むための、第1および第2の記憶装置に接続される第1および第2のビット・ラインと、

第1および第2の記憶装置及び第2および第1の探索ラインにそれぞれ接続される第1および第2のプルダウン回路を有する比較手段とを含み、第1および第2のプルダウン回路がマッチ・ラインとディスチャージ・ラインとの間に接続され、前記比較手段が第2および第1の探索ライン上に搬送されてくる第2および第1の探索ビットを第1および第2の記憶装置の中に記憶された第1および第2のデータ・ビットとそれぞれ比較するものであり、第1および第2の探索ビットと第1および第2のデータ・ビットとの間に不整合があった場合、および第1および第2のデータ・ビットが相補的な値を有するとき、前記比較手段がマッチ・ラインをディスチャージ・ラインに結合させることを特徴とするダイナミック連想メモリセルが提供される。

(a)電源端子と接地端子の間で所定の電圧レベルを有する低電圧端子に結合されているか、

(b)電源に端子に結合されているゲートを有するトランジスタで形成されていることが好ましい電流制限器を介して接地端子に結合されている。

a)少なくとも1つの高度にドープされたエリアが、各前記FETのドレイン端子とソース端子を形成する活性領域と、

b)各前記FETのゲート端子を形成する第1ポリシリコン導電層と、

c)第1および第2ビット・ラインと、前記活性領域と前記第1ポリシリコンの間の少なくとも1つの相互接続とを形成する第2ポリシリコン導電層と、

d)前記活性領域の高度にドープされたエリアにおいて選択された点へのコンタクトを提供し、かつ、前記第1および第2ポリシリコン導電層の間の相互接続を提供する金属導電層と、

e)各前記キャパシタの第1および第2プレートをそれぞれ形成する第3および第4ポリシリコン導電層とを備える複数の半導体層を使用して、集積回路内において製作されており、

前記活性領域が、前記第2ポリシリコン導電層と前記金属導電層によって形成された相互接続を介して、前記比較手段のゲートを形成する前記第1ポリシリコン導電層のエリアに結合されている。

a)少なくとも1つの高度にドープされたエリアが、各前記FETのドレイン端子とソース端子を形成する活性領域と、

b)各前記FETのゲート端子を形成する第1ポリシリコン導電層と、

c)第1および第2ビット・ラインと、前記活性領域と前記第1ポリシリコンの間の少なくとも1つの相互接続とを形成する第2ポリシリコン導電層と、

d)各前記キャパシタの第1および第2プレートをそれぞれ形成する第3および第4ポリシリコン導電層とを備える複数の半導体層を使用して、集積回路内において製作されており、

前記活性領域が、前記第2ポリシリコン導電層と前記金属導電層によって形成された相互接続を介して、前記比較手段のゲートを形成する前記第1ポリシリコン導電層のエリアに結合されている。

1.ダイナミック連想メモリセルにビット・データを書き込む方法であって、

a)マッチ・ラインを予め設定した事前充電電圧レベルに保つステップと、

b)第1および第2探索ラインをロー・ロジック・レベルに保つステップと、

c)前記ビット・データを第1および第2ビット・ライン上に配置するステップと、

d)ワード・ラインをハイ・ロジック・レベルに上げるステップと、

e)ワード・ラインをロー・ロジック・レベルに下げ、それにより、前記データを第1および第2記憶装置に記憶するステップとを含む方法。

2.ダイナミック連想メモリセルの中で探索データを記憶データと比較する方法であって、

a)ワード・ラインをロー・ロジック・レベルに保つステップと、

b)マッチ・ラインを予め設定した事前充電電圧レベルに事前充電するステップと、

c)前記探索データを第1および第2探索ライン上に配置するステップと、

d)マッチ・ライン上の電圧変化を、探索データと記憶データの比較の結果を示すものとして検出するステップとを含む方法。

3.ダイナミック連想メモリセルから記憶データを読み出す方法であって、

a)マッチ・ラインを予め設定した事前充電電圧レベルに保つステップと、

b)第1および第2探索ラインをロー・ロジック・レベルに保つステップと、

c)第1および第2ビット・ラインが、中間電圧レベルで浮動することを可能にするステップと、

d)ワード・ラインをハイ・ロジック・レベルに上げるステップと、

e)読み出しデータを示すために、前記中間電圧レベルから、第1および第2ビット・ラインの各々における電圧レベルの差を感知して増幅するステップと、

f)読み出しデータを第1および第2記憶装置に再記憶するステップとを含む方法。

a)複数の記憶セルに結合されているマッチ・ラインを、事前充電電圧レベルまで事前充電するステップと、

b)反対または同じレベルの探索データを、複数の記憶セルに結合されている第1および第2探索ライン上に配置するステップと、

c)前記マッチ・ラインに結合されている前記複数の記憶セルに記憶されているデータを探索し、前記探索データと比較するステップと、

d)前記複数の記憶セルの少なくとも1つが、反対のロジック位相のデータを前記探索データに記憶する場合、比較手段を介してディスチャージ・ラインに結合するステップとを含む。

a)第1および第2データ・ビットをそれぞれ記憶する第1および第2記憶手段と、

b)第1および第2ビット・ライン上で搬送された第1および第2探索ビットを、前記第1および第2記憶手段に記憶されている第1および第2データ・ビットと比較する比較手段であって、前記第1および第2探索ビットと前記第1および第2データ・ビットとの間で不整合が生じる場合、および前記第1および第2データ・ビットが反対のレベルを有するとき、マッチ・ラインをディスチャージ・ラインに結合する比較手段と、

c)ワード・ラインによって起動されるとき、前記第1および第2記憶手段を前記第1および第2ビット・ラインにそれぞれ結合する第1および第2アクセス手段とを備える。

本発明の好ましい実施形態によるダイナミックCAMセルを図2のトランジスタ回路構成に示す。この図に示したように、CAMセルは、キャパシタC1およびC2の形態にある、第1および第2記憶装置を含む。各記憶装置は、「1」(記憶されている電圧がVcpより高い)または「0」(記憶されている電圧がVcpより低い)を記憶することができる。2値の構成では、CAMセルは、C1上の「0」とC2上の「1」、またはC1上の「1」とC2上の「0」として、2値ビットのデジタル情報を記憶する。さらに、3値の構成では、CAMセルは、両方の記憶装置が、C1とC2の両方で「0」を記憶するなど、「0」を記憶するとき、追加の「ドントケア」状態を獲得する。

電源端子VDD

接地端子VSS

それらのVDDとVSSの間にある電圧レベルを有するセル・プレート電圧端子Vcp

それらのVDDとVSSの間にある電圧レベルを有する低電圧端子VG、または接地VSS

VDD、Vcp、およびVSSの通常の値は、それぞれ、3.3V、1.65V、および0Vである。

(a)マッチ・ラインMLを所定のレベルに保ち、第1探索ラインSL1と第2探索ラインSL2をロー・レベルに保つ。

(b)CAMセルに書き込まれるデータに対応する2値信号レベル(ロジック・ハイおよびロジック・ロー)を第1ビット・ラインBL1と第2ビット・ラインBL2の上に配置する。

(c)ワード・ラインWLをVPPレベル(VDDより高い)まで上げ、第1セル・ノードN1がBL1において信号レベルを獲得するように、第1記憶キャパシタC1を充電し、第2セル・ノードN2が、BL2の上において信号レベルを獲得するように、第2記憶キャパシタC2を充電する。

(d)次いで、ワード・ラインWLの信号レベルをVSSまで下げ、第1ノードN1と第2ノードN2において獲得された信号レベルを、それぞれ第1キャパシタC1と第2キャパシタC2に記憶する。

(a)マッチ・ラインMLを事前充電レベルに保ち、第1探索ラインSL1と第2探索ラインSL2をロー・レベルに保つ。

(b)ロー・ロジック・レベル信号「0」を、それぞれBL1とBL2の上に配置する。

(c)ワード・ラインWLをVPPまで上げ、アクセス・トランジスタT1とT2が完全に導通して、ビット・ライン・データをそれぞれノードN1およびN2上に渡す。

(d)ワード・ラインWLをVSSまで下げ、ノードN1とN2の上の「0」データを、それぞれキャパシタC1とC2に記憶する。

(a)探索と比較の全シーケンス中に、ワード・ラインWLをロー・レベルに保ち、一方、第1ビット・ラインBL1と第2ビット・ラインBL2を事前充電レベルに保つこと、または「0」あるいは「1」に駆動すること、または浮動させることが可能である、

(b)マッチ・ラインMLが、VDDまたはVDDよりわずかに低い事前充電レベルで開始される。

(c)CAMセルに記憶されているデータと比較される探索データに対応する2値信号レベル(ハイおよびロー)を、この場合、SL1=「1」、SL2=「2」である、第1探索ラインSL1と第2探索ラインSL2の上に配置する。

(d)探索データと記憶されているデータの比較の結果を、ML上の後続信号レベルによって示す。探索データが記憶データと同じである場合、すなわち、整合している場合、第1プルダウン回路または第2プルダウン回路のいずれも、導通しているトランジスタを有していないので、MLは、事前充電レベルに留まる。探索レベルが記憶データと異なる場合、すなわち整合していない場合、両方のトランジスタとも導通しており、電流が流れ、MLを事前充電レベルより低い信号レベルまで下げることが可能になるので、2つのプルダウン回路の一方が起動される。この場合、例えば、SL1=「0」、SL2=「1」、およびN1=「1」である場合、不整合が存在し、トランジスタT3とT4は導通して、それにより、図4の点線によって示したように、事前充電からMLを引き離す。

(a)全読取りシーケンス中、MLを事前充電レベルに保ち、探索ラインSL1とSL2をロー・レベルに保つ。

(b)ビット・ラインBL1とBL2が、中間レベル(VDD/2)まで事前充電することによって開始される。

(c)ワード・ラインWLを、BL1とC1の間、およびBL2とC2の間で電荷を共有することを可能にするVppレベルまで上げ、したがって、BL1とBL2の電圧レベルが、C1とC2に記憶されているデータを追跡するために、当初の事前充電レベルから逸脱し始める。

(d)事前充電レベルから逸脱したBL1とBL2の信号レベルの差を感知して、第1および第2ビット・ラインのセンスアンプ(それぞれ図8でSA1およびSA2として示す)によって増幅し、読取りシーケンスの出力を提供する。

(e)次いで、増幅した読取りシーケンスの出力を使用して、C1とC2を読取りシーケンス直前の状態まで再充電することによって、当初記憶されていたCAMセルにデータを再記憶する。

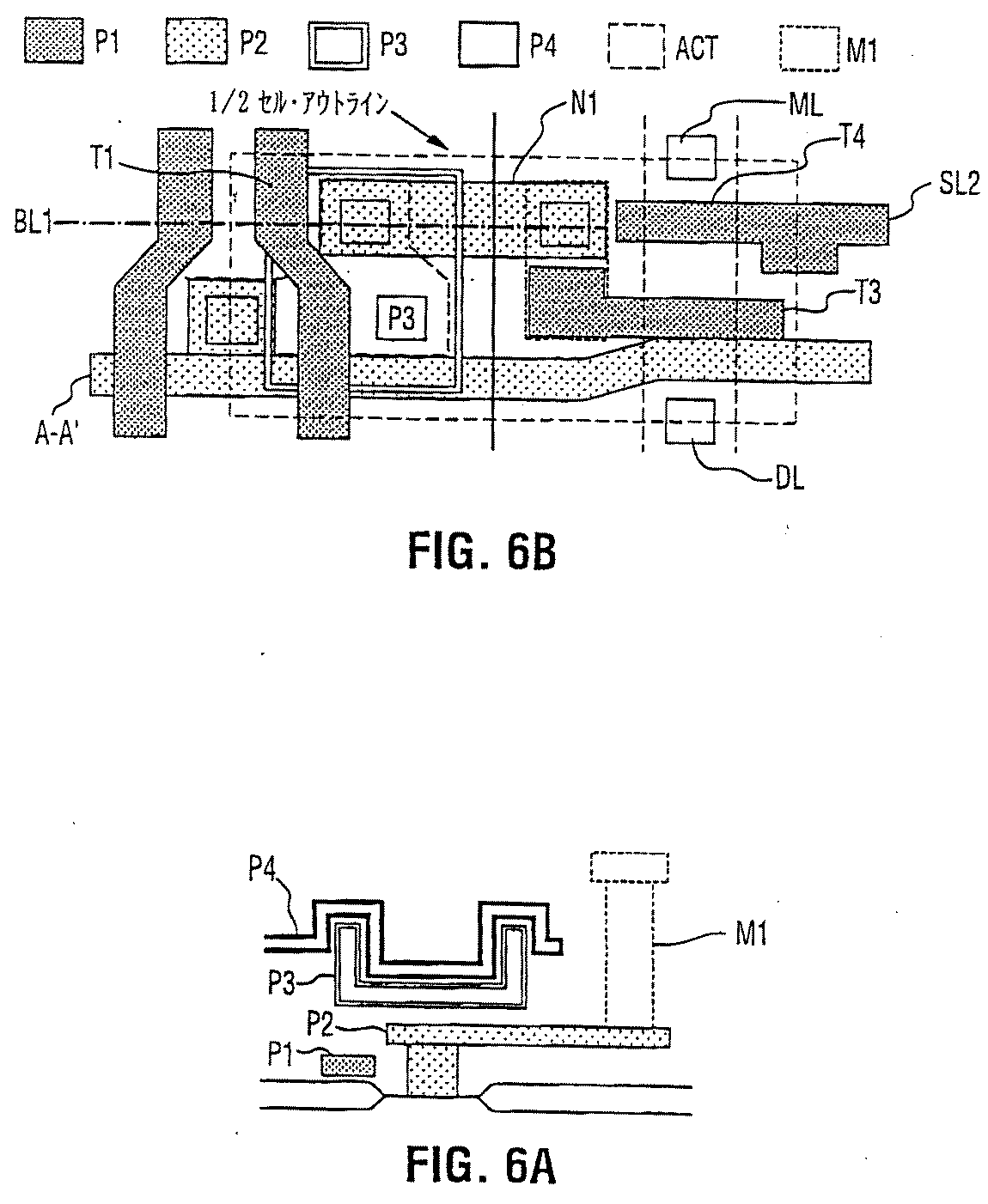

(a)ドレイン端子とソース端子、および各FET T1〜T7のチャネルを形成するための、高度にドープされた半導体活性(ACT)領域、

(b)各FETのゲート端子を形成するための第1ポリシリコン層(p1)、

(c)第1ビット・ラインBL1と第2ビット・ラインBL2および局所的な相互接続を形成するための第2ポリシリコン層(P2)、

(d)セル・キャパシタC1とC2の底部プレートを形成するための第3ポリシリコン層(P3)、

(e)セル・キャパシタC1とC2の上部プレートを形成するための第4ポリシリコン層(P4)、

(f)さらに局所的な相互接続と、ならびに、以下で記述するように、活性領域へのコンタクトを提供するための導電金属層(M1)からなる。

Claims (5)

- 第1の方向に伸びる複数のビット・ラインと、

前記第1の方向と直交する第2の方向に伸びる複数のワード・ラインと、

前記第2の方向に伸びる複数のマッチ・ラインと、

前記ビット・ラインとワード・ラインの交差部に位置する複数のダイナミック連想メモリセルとを備え、前記各セルが、

ワード・ラインに接続されるゲート端子およびビット・ラインに接続される第1ソース/ドレイン端子を有するアクセス・トランジスタと、

前記アクセス・トランジスタの第2ソース/ドレイン端子に接続される第1プレートを有する第1メモリセル・キャパシタと、

ポリシリコン相互接続層だけを介して前記アクセス・トランジスタの第2ソース/ドレイン端子に接続されるゲート端子を有する、マッチ・ラインの整合結果または不整合結果を示すための比較トランジスタとを含む、ダイナミック連想メモリ。 - 前記ビット・ラインが、前記ポリシリコン相互接続層で形成される請求項1記載のダイナミック連想メモリ。

- 第2プレートを有する第2メモリセル・キャパシタをさらに備え、前記第1および第2プレートが前記ポリシリコン相互接続層で形成される請求項1記載のダイナミック連想メモリ。

- ビット・ラインとワード・ラインの前記交差部に位置する連想メモリセルの対が3値連想メモリセルを構成する請求項1記載のダイナミック連想メモリ。

- 前記第1の方向に伸びる複数の探索ラインをさらに備え、前記各ダイナミック連想メモリセルが、探索ラインに接続されるゲート端子を有するプルダウン・トランジスタをさらに備え、前記プルダウン・トランジスタおよび前記比較トランジスタのソース/ドレイン端子がマッチ・ラインとディスチャージ・ライン間に直列接続される請求項1記載のダイナミック連想メモリ。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CA2,266,062 | 1999-03-31 | ||

| CA002266062A CA2266062C (en) | 1999-03-31 | 1999-03-31 | Dynamic content addressable memory cell |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000610011A Division JP2002541610A (ja) | 1999-03-31 | 2000-03-30 | ダイナミック連想記憶セル |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010061801A true JP2010061801A (ja) | 2010-03-18 |

| JP5066727B2 JP5066727B2 (ja) | 2012-11-07 |

Family

ID=4163388

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000610011A Withdrawn JP2002541610A (ja) | 1999-03-31 | 2000-03-30 | ダイナミック連想記憶セル |

| JP2009278793A Expired - Fee Related JP5066727B2 (ja) | 1999-03-31 | 2009-12-08 | ダイナミック連想メモリセル |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000610011A Withdrawn JP2002541610A (ja) | 1999-03-31 | 2000-03-30 | ダイナミック連想記憶セル |

Country Status (8)

| Country | Link |

|---|---|

| US (2) | US6320777B1 (ja) |

| JP (2) | JP2002541610A (ja) |

| KR (1) | KR100603228B1 (ja) |

| AU (1) | AU3413700A (ja) |

| CA (1) | CA2266062C (ja) |

| DE (1) | DE10084440B4 (ja) |

| GB (1) | GB2363663B (ja) |

| WO (1) | WO2000060604A1 (ja) |

Families Citing this family (48)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4732596B2 (ja) * | 2000-03-03 | 2011-07-27 | 川崎マイクロエレクトロニクス株式会社 | 連想メモリ装置 |

| CA2299991A1 (en) * | 2000-03-03 | 2001-09-03 | Mosaid Technologies Incorporated | A memory cell for embedded memories |

| CA2307240C (en) * | 2000-05-01 | 2011-04-12 | Mosaid Technologies Incorporated | Matchline sense circuit and method |

| US6262907B1 (en) * | 2000-05-18 | 2001-07-17 | Integrated Device Technology, Inc. | Ternary CAM array |

| JP2001338990A (ja) * | 2000-05-26 | 2001-12-07 | Fujitsu Ltd | 半導体装置 |

| JP3921331B2 (ja) * | 2000-05-26 | 2007-05-30 | 富士通株式会社 | 半導体装置 |

| CA2313275C (en) | 2000-06-30 | 2006-10-17 | Mosaid Technologies Incorporated | Searchline control circuit and power reduction method |

| US6430073B1 (en) * | 2000-12-06 | 2002-08-06 | International Business Machines Corporation | Dram CAM cell with hidden refresh |

| JP2002298588A (ja) * | 2001-03-30 | 2002-10-11 | Fujitsu Ltd | 半導体装置及びその検査方法 |

| CA2342575A1 (en) | 2001-04-03 | 2002-10-03 | Mosaid Technologies Incorporated | Content addressable memory cell |

| US6888730B2 (en) | 2001-04-03 | 2005-05-03 | Mosaid Technologies Incorporated | Content addressable memory cell |

| US6480406B1 (en) * | 2001-08-22 | 2002-11-12 | Cypress Semiconductor Corp. | Content addressable memory cell |

| US6822886B2 (en) * | 2001-09-24 | 2004-11-23 | Micron Technology, Inc. | Reducing signal swing in a match detection circuit |

| KR100406924B1 (ko) * | 2001-10-12 | 2003-11-21 | 삼성전자주식회사 | 내용 주소화 메모리 셀 |

| US6442055B1 (en) * | 2001-12-12 | 2002-08-27 | International Business Machines Corporation | System and method for conserving power in a content addressable memory by providing an independent search line voltage |

| US7301961B1 (en) | 2001-12-27 | 2007-11-27 | Cypress Semiconductor Corportion | Method and apparatus for configuring signal lines according to idle codes |

| US6751110B2 (en) * | 2002-03-08 | 2004-06-15 | Micron Technology, Inc. | Static content addressable memory cell |

| JP2003272386A (ja) | 2002-03-20 | 2003-09-26 | Mitsubishi Electric Corp | Tcamセル、tcamセルアレイ、アドレス検索メモリおよびネットワークアドレス検索装置 |

| US20040013803A1 (en) * | 2002-07-16 | 2004-01-22 | Applied Materials, Inc. | Formation of titanium nitride films using a cyclical deposition process |

| US6744654B2 (en) * | 2002-08-21 | 2004-06-01 | Micron Technology, Inc. | High density dynamic ternary-CAM memory architecture |

| US6836419B2 (en) * | 2002-08-23 | 2004-12-28 | Micron Technology, Inc. | Split word line ternary CAM architecture |

| US6760241B1 (en) | 2002-10-18 | 2004-07-06 | Netlogic Microsystems, Inc. | Dynamic random access memory (DRAM) based content addressable memory (CAM) cell |

| US6760240B2 (en) * | 2002-11-22 | 2004-07-06 | International Business Machines Corporation | CAM cell with interdigitated search and bit lines |

| JP4282319B2 (ja) * | 2002-12-13 | 2009-06-17 | 株式会社ルネサステクノロジ | 半導体記憶装置 |

| JP2004214512A (ja) * | 2003-01-07 | 2004-07-29 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| JP4149296B2 (ja) | 2003-03-26 | 2008-09-10 | 株式会社ルネサステクノロジ | 半導体記憶装置 |

| KR100505684B1 (ko) * | 2003-04-25 | 2005-08-02 | 삼성전자주식회사 | 칼럼 결함 복구가 가능한 캠 및 캄럼 결함 복구 방법 |

| EP1471537B1 (en) * | 2003-04-25 | 2006-07-26 | Samsung Electronics Co., Ltd. | TCAM device and operating method |

| JP2004362696A (ja) * | 2003-06-05 | 2004-12-24 | Nec Electronics Corp | 半導体記憶装置 |

| JP2005032991A (ja) * | 2003-07-14 | 2005-02-03 | Renesas Technology Corp | 半導体装置 |

| US6954369B2 (en) * | 2003-07-25 | 2005-10-11 | Micron Technology, Inc. | Noise reduction in a CAM memory cell |

| US7254753B2 (en) * | 2003-07-25 | 2007-08-07 | Micron Technology, Inc. | Circuit and method for configuring CAM array margin test and operation |

| US7173837B1 (en) | 2003-09-26 | 2007-02-06 | Netlogic Microsystems, Inc. | Content addressable memory (CAM) cell bit line architecture |

| US7019999B1 (en) | 2003-10-08 | 2006-03-28 | Netlogic Microsystems, Inc | Content addressable memory with latching sense amplifier |

| JPWO2005050663A1 (ja) * | 2003-11-21 | 2007-08-23 | 株式会社日立製作所 | 半導体集積回路装置 |

| US7120040B2 (en) * | 2004-06-01 | 2006-10-10 | Mosaid Technologies Incorporation | Ternary CAM cell for reduced matchline capacitance |

| US7319602B1 (en) * | 2004-07-01 | 2008-01-15 | Netlogic Microsystems, Inc | Content addressable memory with twisted data lines |

| US7324362B1 (en) * | 2005-03-01 | 2008-01-29 | Netlogic Microsystems Inc. | Content addressable memory cell configurable between multiple modes and method therefor |

| US7633784B2 (en) * | 2007-05-17 | 2009-12-15 | Dsm Solutions, Inc. | Junction field effect dynamic random access memory cell and content addressable memory cell |

| JP5372578B2 (ja) | 2009-04-09 | 2013-12-18 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP4764493B2 (ja) * | 2009-04-22 | 2011-09-07 | ルネサスエレクトロニクス株式会社 | 半導体装置及びそれを用いた表示装置のデータドライバ |

| US7944724B2 (en) * | 2009-04-28 | 2011-05-17 | Netlogic Microsystems, Inc. | Ternary content addressable memory having reduced leakage effects |

| FR2955195B1 (fr) | 2010-01-14 | 2012-03-09 | Soitec Silicon On Insulator | Dispositif de comparaison de donnees dans une memoire adressable par contenu sur seoi |

| US7920397B1 (en) | 2010-04-30 | 2011-04-05 | Netlogic Microsystems, Inc. | Memory device having bit line leakage compensation |

| US8259518B2 (en) * | 2010-06-08 | 2012-09-04 | Sichuan Kiloway Electronics Inc. | Low voltage and low power memory cell based on nano current voltage divider controlled low voltage sense MOSFET |

| US9208880B2 (en) | 2013-01-14 | 2015-12-08 | Zeno Semiconductor, Inc. | Content addressable memory device having electrically floating body transistor |

| KR20160074826A (ko) | 2014-12-18 | 2016-06-29 | 삼성전자주식회사 | 반도체 장치 |

| CN115881189A (zh) * | 2021-09-27 | 2023-03-31 | 三星电子株式会社 | 内容可寻址存储器和包括其的电子装置 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0352196A (ja) * | 1989-07-20 | 1991-03-06 | Toshiba Corp | 連想メモリ |

| JPH04372795A (ja) * | 1991-06-21 | 1992-12-25 | Nissan Motor Co Ltd | 連想メモリ装置 |

| JPH0896585A (ja) * | 1994-07-11 | 1996-04-12 | Hyundai Electron Ind Co Ltd | セルフ リフレッシュ可能なデュアル ポート動的camセル及びリフレッシュ装置 |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3701980A (en) | 1970-08-03 | 1972-10-31 | Gen Electric | High density four-transistor mos content addressed memory |

| JPS62118434A (ja) | 1985-11-19 | 1987-05-29 | Matsushita Electric Ind Co Ltd | 比較回路 |

| US4831585A (en) | 1985-11-27 | 1989-05-16 | Massachusetts Institute Of Technology | Four transistor cross-coupled bitline content addressable memory |

| JPS62165794A (ja) | 1986-01-17 | 1987-07-22 | Toshiba Corp | 連想記憶用メモリセル |

| JPS62195794A (ja) * | 1986-02-24 | 1987-08-28 | Hitachi Ltd | 内容呼び出しメモリ |

| US4791606A (en) * | 1987-09-01 | 1988-12-13 | Triad Semiconductors International Bv | High density CMOS dynamic CAM cell |

| JPH01307095A (ja) | 1988-06-01 | 1989-12-12 | Mitsubishi Electric Corp | 不揮発性cam |

| JPH02187993A (ja) * | 1989-01-13 | 1990-07-24 | Mitsubishi Electric Corp | 連想メモリ装置 |

| US5146300A (en) | 1989-11-27 | 1992-09-08 | Mitsubishi Denki Kabushiki Kaisha | Semiconductor integrated circuit device having improved stacked capacitor and manufacturing method therefor |

| JP2966638B2 (ja) | 1992-04-17 | 1999-10-25 | 三菱電機株式会社 | ダイナミック型連想メモリ装置 |

| US5428564A (en) | 1992-08-03 | 1995-06-27 | Advanced Hardware Architectures, Inc. | Six transistor dynamic content addressable memory circuit |

| US5319590A (en) * | 1992-12-04 | 1994-06-07 | Hal Computer Systems, Inc. | Apparatus for storing "Don't Care" in a content addressable memory cell |

| US5446685A (en) | 1993-02-23 | 1995-08-29 | Intergraph Corporation | Pulsed ground circuit for CAM and PAL memories |

| US5396449A (en) | 1993-12-21 | 1995-03-07 | International Business Machines Corporation | Fast content addressable memory with reduced power consumption |

| US5808929A (en) * | 1995-12-06 | 1998-09-15 | Sheikholeslami; Ali | Nonvolatile content addressable memory |

| JP2836596B2 (ja) * | 1996-08-02 | 1998-12-14 | 日本電気株式会社 | 連想メモリ |

| US5859791A (en) | 1997-01-09 | 1999-01-12 | Northern Telecom Limited | Content addressable memory |

| US5949696A (en) * | 1997-06-30 | 1999-09-07 | Cypress Semiconductor Corporation | Differential dynamic content addressable memory and high speed network address filtering |

| US6044005A (en) * | 1999-02-03 | 2000-03-28 | Sibercore Technologies Incorporated | Content addressable memory storage device |

-

1999

- 1999-03-31 CA CA002266062A patent/CA2266062C/en not_active Expired - Fee Related

-

2000

- 2000-03-23 US US09/533,128 patent/US6320777B1/en not_active Expired - Lifetime

- 2000-03-30 AU AU34137/00A patent/AU3413700A/en not_active Abandoned

- 2000-03-30 DE DE10084440T patent/DE10084440B4/de not_active Expired - Fee Related

- 2000-03-30 GB GB0125244A patent/GB2363663B/en not_active Expired - Fee Related

- 2000-03-30 WO PCT/CA2000/000344 patent/WO2000060604A1/en not_active Ceased

- 2000-03-30 JP JP2000610011A patent/JP2002541610A/ja not_active Withdrawn

- 2000-03-30 KR KR1020017012599A patent/KR100603228B1/ko not_active Expired - Fee Related

-

2001

- 2001-10-17 US US09/977,982 patent/US6483733B2/en not_active Expired - Lifetime

-

2009

- 2009-12-08 JP JP2009278793A patent/JP5066727B2/ja not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0352196A (ja) * | 1989-07-20 | 1991-03-06 | Toshiba Corp | 連想メモリ |

| JPH04372795A (ja) * | 1991-06-21 | 1992-12-25 | Nissan Motor Co Ltd | 連想メモリ装置 |

| JPH0896585A (ja) * | 1994-07-11 | 1996-04-12 | Hyundai Electron Ind Co Ltd | セルフ リフレッシュ可能なデュアル ポート動的camセル及びリフレッシュ装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR100603228B1 (ko) | 2006-07-24 |

| GB0125244D0 (en) | 2001-12-12 |

| JP2002541610A (ja) | 2002-12-03 |

| US6483733B2 (en) | 2002-11-19 |

| US20020044475A1 (en) | 2002-04-18 |

| US6320777B1 (en) | 2001-11-20 |

| DE10084440T1 (de) | 2002-05-08 |

| WO2000060604A1 (en) | 2000-10-12 |

| JP5066727B2 (ja) | 2012-11-07 |

| CA2266062C (en) | 2004-03-30 |

| AU3413700A (en) | 2000-10-23 |

| DE10084440B4 (de) | 2010-11-11 |

| GB2363663B (en) | 2003-09-10 |

| KR20020012168A (ko) | 2002-02-15 |

| GB2363663A (en) | 2002-01-02 |

| CA2266062A1 (en) | 2000-09-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5066727B2 (ja) | ダイナミック連想メモリセル | |

| US8018751B1 (en) | Ternary content addressable memory (TCAM) cells with low signal line numbers | |

| US9502112B2 (en) | Semiconductor memory device | |

| US8144526B2 (en) | Method to improve the write speed for memory products | |

| US7558095B2 (en) | Memory cell for content-addressable memory | |

| CN1248237C (zh) | 一种改进的高密度存储单元 | |

| EP1241676B1 (en) | Pseudo differential sensing method and apparatus for dram cell | |

| JP2002541610A5 (ja) | ||

| US4831585A (en) | Four transistor cross-coupled bitline content addressable memory | |

| KR20070024680A (ko) | 감소된 매치라인 용량을 위한 터너리 내용 주소화 메모리셀 | |

| US7259979B2 (en) | Area efficient stacked TCAM cell for fully parallel search | |

| JP4583703B2 (ja) | 半導体記憶装置 | |

| US7173837B1 (en) | Content addressable memory (CAM) cell bit line architecture | |

| US7619911B2 (en) | Semiconductor integrated circuit device | |

| US20040240277A1 (en) | Semiconductor device | |

| US8730704B1 (en) | Content addressable memory array having local interconnects | |

| US6741491B2 (en) | Integrated dynamic memory, and method for operating the integrated dynamic memory | |

| KR100755793B1 (ko) | 반도체집적회로장치 | |

| US20250118360A1 (en) | Memory device, assist cell and double assist cell for a memory device | |

| KR100502661B1 (ko) | 반도체메모리장치의 비트라인센싱회로 | |

| EP0247182A1 (en) | Four transistor cross-coupled bitline content addressable memory | |

| WO1987003415A1 (en) | Four transistor cross-coupled bitline content addressable memory | |

| JPH0370877B2 (ja) | ||

| JP2008124350A (ja) | 半導体記憶装置 | |

| JPH0194597A (ja) | 内容呼び出しメモリ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20091208 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111129 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20120224 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20120229 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20120426 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20120502 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120528 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120703 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120720 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150824 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |