JP2009164558A - 半導体装置とその製造方法、並びにトレンチゲートの製造方法 - Google Patents

半導体装置とその製造方法、並びにトレンチゲートの製造方法 Download PDFInfo

- Publication number

- JP2009164558A JP2009164558A JP2008156240A JP2008156240A JP2009164558A JP 2009164558 A JP2009164558 A JP 2009164558A JP 2008156240 A JP2008156240 A JP 2008156240A JP 2008156240 A JP2008156240 A JP 2008156240A JP 2009164558 A JP2009164558 A JP 2009164558A

- Authority

- JP

- Japan

- Prior art keywords

- trench

- trench gate

- region

- gate

- manufacturing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims description 125

- 238000004519 manufacturing process Methods 0.000 title claims description 75

- 238000000034 method Methods 0.000 claims description 64

- 238000001312 dry etching Methods 0.000 claims description 44

- 239000000758 substrate Substances 0.000 claims description 41

- 230000015572 biosynthetic process Effects 0.000 claims description 36

- 238000005530 etching Methods 0.000 claims description 26

- 239000000463 material Substances 0.000 claims description 12

- 238000001039 wet etching Methods 0.000 claims description 6

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 4

- 229910052710 silicon Inorganic materials 0.000 claims description 4

- 239000010703 silicon Substances 0.000 claims description 4

- 210000000746 body region Anatomy 0.000 abstract description 32

- 239000000969 carrier Substances 0.000 abstract description 3

- 239000012212 insulator Substances 0.000 abstract description 2

- 230000004048 modification Effects 0.000 description 18

- 238000012986 modification Methods 0.000 description 18

- 230000002093 peripheral effect Effects 0.000 description 8

- 238000005468 ion implantation Methods 0.000 description 7

- 230000003647 oxidation Effects 0.000 description 7

- 238000007254 oxidation reaction Methods 0.000 description 7

- 229910003691 SiBr Inorganic materials 0.000 description 5

- 238000005229 chemical vapour deposition Methods 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 238000005516 engineering process Methods 0.000 description 5

- 239000000126 substance Substances 0.000 description 5

- 238000009825 accumulation Methods 0.000 description 4

- 230000007423 decrease Effects 0.000 description 4

- 239000000243 solution Substances 0.000 description 3

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 239000007864 aqueous solution Substances 0.000 description 2

- 230000004888 barrier function Effects 0.000 description 2

- 239000012141 concentrate Substances 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- 229910002601 GaN Inorganic materials 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/739—Transistor-type devices, i.e. able to continuously respond to applied control signals controlled by field-effect, e.g. bipolar static induction transistors [BSIT]

- H01L29/7393—Insulated gate bipolar mode transistors, i.e. IGBT; IGT; COMFET

- H01L29/7395—Vertical transistors, e.g. vertical IGBT

- H01L29/7396—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions

- H01L29/7397—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions and a gate structure lying on a slanted or vertical surface or formed in a groove, e.g. trench gate IGBT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/08—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/083—Anode or cathode regions of thyristors or gated bipolar-mode devices

- H01L29/0834—Anode regions of thyristors or gated bipolar-mode devices, e.g. supplementary regions surrounding anode regions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42356—Disposition, e.g. buried gate electrode

- H01L29/4236—Disposition, e.g. buried gate electrode within a trench, e.g. trench gate electrode, groove gate electrode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42364—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the insulating layer, e.g. thickness or uniformity

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66234—Bipolar junction transistors [BJT]

- H01L29/66325—Bipolar junction transistors [BJT] controlled by field-effect, e.g. insulated gate bipolar transistors [IGBT]

- H01L29/66333—Vertical insulated gate bipolar transistors

- H01L29/66348—Vertical insulated gate bipolar transistors with a recessed gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66674—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/66712—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/66734—Vertical DMOS transistors, i.e. VDMOS transistors with a step of recessing the gate electrode, e.g. to form a trench gate electrode

Abstract

【課題】 高耐量なIGBTを提供すること。

【解決手段】 IGBT10は、n+型のエミッタ領域34と、n−型のドリフト領域26と、エミッタ領域34とドリフト領域26を隔てているp型のボディ領域28と、エミッタ領域34からドリフト領域26に向けてボディ領域28内を伸びているトレンチゲート40と、絶縁体の突出部60を備えている。突出部60は、一端がトレンチゲート40の表面に接しているとともに、少なくとも一部がドリフト領域26内に突出している。

【選択図】 図1

【解決手段】 IGBT10は、n+型のエミッタ領域34と、n−型のドリフト領域26と、エミッタ領域34とドリフト領域26を隔てているp型のボディ領域28と、エミッタ領域34からドリフト領域26に向けてボディ領域28内を伸びているトレンチゲート40と、絶縁体の突出部60を備えている。突出部60は、一端がトレンチゲート40の表面に接しているとともに、少なくとも一部がドリフト領域26内に突出している。

【選択図】 図1

Description

本発明は、トレンチゲートを有する半導体装置とその製造方法に関する。また、本発明は、そのトレンチゲートを製造する方法にも関する。

図33に、トレンチゲート140を有するIGBT(Insulated Gate Bipolar Transistor)100の要部断面図を模式的に示す。IGBT100は、p+型のコレクタ領域122と、n型のバッファ領域124と、n−型のドリフト領域126と、p型のボディ領域128と、p+型のボディコンタクト領域132と、n+型のエミッタ領域134と、トレンチゲート140を備えている。トレンチゲート140は、エミッタ領域134からドリフト領域126に向けてボディ領域128を貫通して伸びている。トレンチゲート140は、ゲート絶縁膜144と、そのゲート絶縁膜144で被覆されているゲート電極142を有している。

図33に示すように、IGBT100がオンすると、エミッタ領域134から電子が供給される。電子は、トレンチゲート140の側面に沿ってボディ領域128を通過し、ドリフト領域126に供給される。一方、コレクタ領域122からは正孔が供給される。正孔は、バッファ領域124を通過してドリフト領域126に供給される。

図33に示すように、エミッタ領域134から供給された電子は、ゲート電極142の電位に引き寄せられるので、トレンチゲート140の側方から下方に移動する。一方、コレクタ領域122から供給された正孔は、その電子に引き寄せられるので、トレンチゲート140の下方に移動する。したがって、トレンチゲート140の下方には、正孔が集中する。トレンチゲート140の下方に正孔が集中すると、ゲート容量が経時的に変動する。例えば、IGBT100がオフからオンに切換わるときに、ゲート容量が経時的に変動すると、コレクタ電流やコレクタ・エミッタ間電圧も経時的に変動し、その結果、サージ電圧を引き起こしてしまう。

特許文献1及び特許文献2は、トレンチゲート140の底面のゲート絶縁膜144を厚く形成する技術を開示している。この技術によると、トレンチゲート140の下方に移動する電子量を減少させることができるので、トレンチゲート140の下方に移動する正孔量も減少させることができる。この結果、ゲート容量の経時的な変動を緩和させ、サージ電圧の発生を抑制することができる。

しかしながら、ゲート電極142に印加されるゲート電位が大きい場合は、ゲート絶縁膜144を厚く形成したとしても、ゲート電極142の電位に引き寄せられてトレンチゲート140の下方に電子が移動し、その電子に引き寄せられてトレンチゲート140の下方に正孔も移動してしまう。ゲート絶縁膜144を厚く形成する技術は、根本的な解決策を提供するものではない。

本発明は、キャリアがトレンチゲートの下方へ移動するのを物理的に抑制し、高耐量な半導体装置を提供することを目的としている。

本明細書で開示される技術は、トレンチゲートの表面の一部に絶縁体の突出部を設けることを特徴としている。突出部の少なくとも一部は、ドリフト領域内に突出している。このため、ドリフト領域内に突出している突出部の一部は、ドリフト領域で囲まれているので、一方の表面とそれに対向する表面の間に電位差が生じない。このため、ドリフト領域内に突出している突出部の一部の表面には反転層が形成されない。したがって、エミッタ領域から供給された電子は、この突出部を超えて移動することができない。この結果、トレンチゲートの下方に移動する電子量が減少し、その電子に引き寄せられてトレンチゲートの下方に移動する正孔量も減少する。

即ち、本明細書で開示される半導体装置は、第1導電型の表面部半導体領域と、第1導電型の深部半導体領域と、表面部半導体領域と深部半導体領域を隔てている第2導電型の中間部半導体領域と、トレンチゲートと、絶縁体の突出部を備えている。トレンチゲートは、表面部半導体領域から深部半導体領域に向けて中間部半導体領域内を伸びている。トレンチゲートは、中間部半導体領域を貫通して深部半導体領域内に侵入してもよいし、侵入しなくてもよい。トレンチゲートが中間部半導体領域を貫通していない場合は、後述するように、突出部による第2の反転層を利用してキャリアを流すことが可能である。トレンチゲートは、ゲート絶縁膜と、そのゲート絶縁膜で被覆されているゲート電極を有している。突出部は、一端がトレンチゲートの表面に接しているとともに、少なくとも一部が深部半導体領域内に突出している。

一般的に、上記半導体装置では、トレンチゲートのゲート絶縁膜は、表面部半導体領域から深部半導体領域に向けて延びているとともに相互に対向している一対の側面と、一方の側面から他方の側面まで延びている底面を有していることが多い。突出部は、ゲート絶縁膜の底面に接していてもよく、ゲート絶縁膜の側面に接していてもよい。

突出部がゲート絶縁膜の底面に接している場合、複数の突出部がその底面に接しているのが好ましい。

一般的に、上記半導体装置では、中間部半導体領域は、イオン注入技術を利用して形成される。複数の突出部がゲート絶縁膜の底面に接していると、中間部半導体領域がトレンチゲートを超えて深い位置まで拡散したとしても、突出部によってトレンチゲートの下方にまで拡散することを防止することができる。したがって、中間部半導体領域がトレンチゲートを超えて深い位置まで拡散したとしても、隣接する突出部の間のトレンチゲートの下方に深部半導体領域を存在させることができる。即ち、深部半導体領域と中間部半導体領域が突出部を挟んで存在することになる。この場合、半導体装置がオンしているときに、深部半導体領域と中間部半導体領域の間に電位差が生じるので、中間部半導体領域が接する突出部の表面の一部には第2の反転層が形成される。このため、表面部半導体領域から供給されたキャリアは、その第2の反転層を通過して深部半導体領域内に移動することができる。通常のトレンチゲートでは、中間部半導体領域がトレンチゲートを超えて拡散すると、オンとオフを切換えることができなくなる。しかし、上記半導体装置のように、ゲート絶縁膜の底面に複数の突出部が設けられていると、中間部半導体領域がトレンチゲートを超えて深い位置まで拡散したとしても、オンとオフを切換えることに支障がない。上記形態の半導体装置は、製造し易い特徴を有する。なお、前記したように、突出部の一部は深部半導体領域内に存在しているので、その部分には第2の反転層が形成されない。このため、キャリアが突出部を超えてトレンチゲートの下方にまで移動することはない。即ち、上記形態の突出部は、キャリアがトレンチゲートの下方に移動するのを物理的に抑制する効果に加えて、半導体装置の製造を容易にするという効果をも有する。

一般的に、上記半導体装置では、中間部半導体領域は、イオン注入技術を利用して形成される。複数の突出部がゲート絶縁膜の底面に接していると、中間部半導体領域がトレンチゲートを超えて深い位置まで拡散したとしても、突出部によってトレンチゲートの下方にまで拡散することを防止することができる。したがって、中間部半導体領域がトレンチゲートを超えて深い位置まで拡散したとしても、隣接する突出部の間のトレンチゲートの下方に深部半導体領域を存在させることができる。即ち、深部半導体領域と中間部半導体領域が突出部を挟んで存在することになる。この場合、半導体装置がオンしているときに、深部半導体領域と中間部半導体領域の間に電位差が生じるので、中間部半導体領域が接する突出部の表面の一部には第2の反転層が形成される。このため、表面部半導体領域から供給されたキャリアは、その第2の反転層を通過して深部半導体領域内に移動することができる。通常のトレンチゲートでは、中間部半導体領域がトレンチゲートを超えて拡散すると、オンとオフを切換えることができなくなる。しかし、上記半導体装置のように、ゲート絶縁膜の底面に複数の突出部が設けられていると、中間部半導体領域がトレンチゲートを超えて深い位置まで拡散したとしても、オンとオフを切換えることに支障がない。上記形態の半導体装置は、製造し易い特徴を有する。なお、前記したように、突出部の一部は深部半導体領域内に存在しているので、その部分には第2の反転層が形成されない。このため、キャリアが突出部を超えてトレンチゲートの下方にまで移動することはない。即ち、上記形態の突出部は、キャリアがトレンチゲートの下方に移動するのを物理的に抑制する効果に加えて、半導体装置の製造を容易にするという効果をも有する。

複数の突出部がゲート絶縁膜の底面に接している場合、隣接する突出部の間に第2導電型の半導体領域が設けられており、その半導体領域がフローティングであることが好ましい。

トレンチゲートの下方にフローティングの半導体領域が設けられていると、ゲート容量を小さくすることができるので、スイッチングを高速化させることができる。

トレンチゲートの下方にフローティングの半導体領域が設けられていると、ゲート容量を小さくすることができるので、スイッチングを高速化させることができる。

本明細書で開示される技術は、トレンチゲートを製造する方法も提供することができる。本明細書で開示されるトレンチゲートの製造方法は、半導体基板のトレンチゲート形成領域の表面の一部からドライエッチングによって第1の深さを有する第1トレンチを形成する第1工程を備えている。さらに、このトレンチゲートの製造方法は、半導体基板のトレンチゲート形成領域の表面の残部からドライエッチングによって第2の深さを有する第2トレンチを形成する第2工程を備えている。第1の深さは第2の深さよりも深いことを特徴とする。第1工程と第2工程は、どちらが先に実施されてもよい。

上記製造方法によると、第1トレンチが第2トレンチよりも深く形成される。このため、第2トレンチから突出する第1トレンチによって、トレンチゲートの底面に突出トレンチが形成される。この突出トレンチが深部半導体領域内に位置すると、突出トレンチの相互に対向する側面はいずれも、深部半導体領域に接するようになる。このため、突出トレンチの一方の側面と他方の側面の間には電位差が生じないので、突出トレンチの側面の少なくとも一部には反転層が形成されない。即ち、上記製造方法によると、本明細書で開示される技術を具現化したトレンチゲートを製造することができる。

なお、第1トレンチを形成する位置は、トレンチゲート形成領域の少なくとも一部であればよい。例えば、第1トレンチをトレンチゲート形成領域の中心側に形成すれば、トレンチゲートの底面の中心側から突出する突出トレンチが形成される。好ましくは、第1トレンチをトレンチゲート形成領域の周縁に沿った位置の少なくとも一部に形成するのが良い。より好ましくは、第1トレンチをトレンチゲート形成領域の周縁に沿って一巡して形成するのが良い。

上記製造方法によると、第1トレンチが第2トレンチよりも深く形成される。このため、第2トレンチから突出する第1トレンチによって、トレンチゲートの底面に突出トレンチが形成される。この突出トレンチが深部半導体領域内に位置すると、突出トレンチの相互に対向する側面はいずれも、深部半導体領域に接するようになる。このため、突出トレンチの一方の側面と他方の側面の間には電位差が生じないので、突出トレンチの側面の少なくとも一部には反転層が形成されない。即ち、上記製造方法によると、本明細書で開示される技術を具現化したトレンチゲートを製造することができる。

なお、第1トレンチを形成する位置は、トレンチゲート形成領域の少なくとも一部であればよい。例えば、第1トレンチをトレンチゲート形成領域の中心側に形成すれば、トレンチゲートの底面の中心側から突出する突出トレンチが形成される。好ましくは、第1トレンチをトレンチゲート形成領域の周縁に沿った位置の少なくとも一部に形成するのが良い。より好ましくは、第1トレンチをトレンチゲート形成領域の周縁に沿って一巡して形成するのが良い。

本明細書で開示される技術は、トレンチゲートを製造する他の方法も提供することができる。本明細書で開示されるトレンチゲートの製造方法は、半導体基板のトレンチゲート形成領域の表面の一部からドライエッチングによって複数のトレンチを形成する第1工程を備えている。さらに、このトレンチゲートの製造方法は、複数のトレンチ内にエッチング液を供給し、トレンチの底面から下方に向けて突出する突出トレンチをウェットエッチングによって形成する第2工程を備えている。第1工程で形成されるトレンチの側面は第1面方位を有しており、第2工程で形成される突出トレンチの側面は第2面方位を有している。第1側面と第2側面は、非平行であることを特徴としている。なお、第2工程では、ウェットエッチングによってトレンチとトレンチの間の壁を除去してもよく、必要に応じて除去しなくてもよい。例えば、トレンチとトレンチの間の壁を酸化する工程を追加し、トレンチゲートが複数の部屋に分割された形態にしてもよい。

上記製造方法では、ドライエッチングとウェットエッチングを組合せてトレンチゲートを形成することによって、各トレンチの底面に下方に突出する突出トレンチを形成することができる。上記製造方法では、複数のトレンチが1つのトレンチゲートを画定しているので、トレンチゲートの底面に複数の突出トレンチが形成される。これら突出トレンチが深部半導体領域内に位置すると、突出トレンチの相互に対向する側面はいずれも、深部半導体領域に接するようになる。このため、突出トレンチの一方の側面と他方の側面の間には電位差が生じないので、突出トレンチの側面の少なくとも一部には反転層が形成されない。即ち、上記製造方法によると、本明細書で開示される技術を具現化したトレンチゲートを製造することができる。

なお、半導体基板にシリコン基板を用いた場合は、第1面方位は(100)面であり、第2面方位は(111)面であることが好ましい。この場合、例えば、ドライエッチングにはHBrガスを用いることができ、ウェットエッチングにはKOH水溶液を用いることができる。

上記製造方法では、ドライエッチングとウェットエッチングを組合せてトレンチゲートを形成することによって、各トレンチの底面に下方に突出する突出トレンチを形成することができる。上記製造方法では、複数のトレンチが1つのトレンチゲートを画定しているので、トレンチゲートの底面に複数の突出トレンチが形成される。これら突出トレンチが深部半導体領域内に位置すると、突出トレンチの相互に対向する側面はいずれも、深部半導体領域に接するようになる。このため、突出トレンチの一方の側面と他方の側面の間には電位差が生じないので、突出トレンチの側面の少なくとも一部には反転層が形成されない。即ち、上記製造方法によると、本明細書で開示される技術を具現化したトレンチゲートを製造することができる。

なお、半導体基板にシリコン基板を用いた場合は、第1面方位は(100)面であり、第2面方位は(111)面であることが好ましい。この場合、例えば、ドライエッチングにはHBrガスを用いることができ、ウェットエッチングにはKOH水溶液を用いることができる。

本明細書で開示される技術は、トレンチゲートを製造するさらに他の方法も提供することができる。本明細書で開示されるトレンチゲートの製造方法は、半導体基板のトレンチゲート形成領域の表面からドライエッチングによってトレンチを形成する第1工程を備えている。さらに、このトレンチゲートの製造方法は、ドライエッチングによって生成される半導体基板とエッチングガスが結合した揮発性物質が前記トレンチの底面に堆積する条件のドライエッチングによって、トレンチを更に深くする第2工程を備えている。

上記製造方法では、少なくとも2回のドライエッチングを実施してトレンチを形成する。第2工程で実施するドライエッチングは、半導体基板とエッチングガスが結合した揮発性物質がトレンチの底面に堆積する条件で行われる。一般的に、トレンチの底面に揮発性物質が堆積すると、その揮発性物質はトレンチの底面の中心側に多く堆積する。このため、この条件でドライエッチングを実施し続けると、トレンチの底面において、周縁側のエッチングが中心側のエッチングよりも早く進行する。この結果、トレンチの底面の周縁側に突出トレンチが形成される。これら突出トレンチが深部半導体領域内に位置すると、突出トレンチの相互に対向する側面はいずれも、深部半導体領域に接するようになる。このため、突出トレンチの一方の側面と他方の側面の間には電位差が生じないので、突出トレンチの側面の少なくとも一部には反転層が形成されない。即ち、上記製造方法によると、本明細書で開示される技術を具現化したトレンチゲートを製造することができる。

上記製造方法では、少なくとも2回のドライエッチングを実施してトレンチを形成する。第2工程で実施するドライエッチングは、半導体基板とエッチングガスが結合した揮発性物質がトレンチの底面に堆積する条件で行われる。一般的に、トレンチの底面に揮発性物質が堆積すると、その揮発性物質はトレンチの底面の中心側に多く堆積する。このため、この条件でドライエッチングを実施し続けると、トレンチの底面において、周縁側のエッチングが中心側のエッチングよりも早く進行する。この結果、トレンチの底面の周縁側に突出トレンチが形成される。これら突出トレンチが深部半導体領域内に位置すると、突出トレンチの相互に対向する側面はいずれも、深部半導体領域に接するようになる。このため、突出トレンチの一方の側面と他方の側面の間には電位差が生じないので、突出トレンチの側面の少なくとも一部には反転層が形成されない。即ち、上記製造方法によると、本明細書で開示される技術を具現化したトレンチゲートを製造することができる。

本明細書で開示される技術は、トレンチゲートを製造するさらに他の方法も提供することができる。本明細書で開示されるトレンチゲートの製造方法は、半導体基板のトレンチゲート形成領域の表面の一部にマスクを形成する第1工程と、半導体基板のトレンチゲート形成領域の表面からドライエッチングによってトレンチを形成する第2工程を備えている。第2工程では、トレンチゲート形成領域の表面のマスクが消失した後もドライエッチングを継続することを特徴としている。

上記製造方法の第2工程は、2つの段階に分けられる。まず、第1段階では、マスクで被覆されていないトレンチゲート形成領域の表面がエッチングされる。この第1段階では、エッチングレートは遅いものの、トレンチゲート形成領域の表面に形成されたマスクも少しずつエッチングされ、最終的には消失する。マスクが消失したときには、マスクによって被覆されていなかった部分のエッチングが進行しており、初期トレンチが形成される。即ち、第1段階では、トレンチ形成領域の表面の一部にマスクを形成することによって、トレンチ形成領域のエッチングの進行度に差を設ける。次に、第2段階では、マスクが消失した後もドライエッチングを継続することによって、トレンチ形成領域のトレンチを更に掘下げていく。第1段階で設けられたエッチングの進行度の差によって、第2段階が終了したときのトレンチの底面には突出トレンチが形成される。この突出トレンチが深部半導体領域内に位置すると、突出トレンチの相互に対向する側面はいずれも、深部半導体領域に接するようになる。このため、突出トレンチの一方の側面と他方の側面の間には電位差が生じないので、突出トレンチの側面の少なくとも一部には反転層が形成されない。上記製造方法によると、1回のドライエッチングを実施するだけで、本明細書で開示される技術を具現化したトレンチゲートを製造することができる。

また、第1工程では、トレンチゲート形成領域の表面に複数のマスクを分散して形成することが好ましい。複数のマスクを分散して配置することによって、幅広なトレンチを形成することができる。

上記製造方法の第2工程は、2つの段階に分けられる。まず、第1段階では、マスクで被覆されていないトレンチゲート形成領域の表面がエッチングされる。この第1段階では、エッチングレートは遅いものの、トレンチゲート形成領域の表面に形成されたマスクも少しずつエッチングされ、最終的には消失する。マスクが消失したときには、マスクによって被覆されていなかった部分のエッチングが進行しており、初期トレンチが形成される。即ち、第1段階では、トレンチ形成領域の表面の一部にマスクを形成することによって、トレンチ形成領域のエッチングの進行度に差を設ける。次に、第2段階では、マスクが消失した後もドライエッチングを継続することによって、トレンチ形成領域のトレンチを更に掘下げていく。第1段階で設けられたエッチングの進行度の差によって、第2段階が終了したときのトレンチの底面には突出トレンチが形成される。この突出トレンチが深部半導体領域内に位置すると、突出トレンチの相互に対向する側面はいずれも、深部半導体領域に接するようになる。このため、突出トレンチの一方の側面と他方の側面の間には電位差が生じないので、突出トレンチの側面の少なくとも一部には反転層が形成されない。上記製造方法によると、1回のドライエッチングを実施するだけで、本明細書で開示される技術を具現化したトレンチゲートを製造することができる。

また、第1工程では、トレンチゲート形成領域の表面に複数のマスクを分散して形成することが好ましい。複数のマスクを分散して配置することによって、幅広なトレンチを形成することができる。

本明細書で開示される突出部は、表面部半導体領域から供給される一方のキャリアがトレンチゲートの下方に移動するのを物理的に抑制し、これにより、その一方のキャリアに引き寄せられてトレンチゲートの下方に他方のキャリアが集中するのを抑制することができる。この結果、ゲート容量がキャリアの集中によって経時的に変動するのを抑制することができ、高耐量な半導体装置を提供することができる。

本発明の好ましい特徴を列記する。

(第1特徴) 突出部がゲート絶縁膜から突出する厚みは、ゲート絶縁膜の厚みよりも厚い。

(第2特徴) 突出部は、第1表面とその第1表面に対向する第2表面を有している。第1表面と第2表面は、エミッタ領域とトレンチゲートの下方を結ぶ方向を隔てるように設けられている。

(第3特徴) 突出部は、ゲート絶縁膜の底面の周縁部に設けられている。

(第4特徴) 第2及び第3特徴において、第1表面はゲート絶縁膜の底面と非平行であり、第2表面はゲート絶縁膜の側面と平行である。

(第1特徴) 突出部がゲート絶縁膜から突出する厚みは、ゲート絶縁膜の厚みよりも厚い。

(第2特徴) 突出部は、第1表面とその第1表面に対向する第2表面を有している。第1表面と第2表面は、エミッタ領域とトレンチゲートの下方を結ぶ方向を隔てるように設けられている。

(第3特徴) 突出部は、ゲート絶縁膜の底面の周縁部に設けられている。

(第4特徴) 第2及び第3特徴において、第1表面はゲート絶縁膜の底面と非平行であり、第2表面はゲート絶縁膜の側面と平行である。

以下、図面を参照して各実施例を説明する。なお、各図面において、共通する構成要素に関しては共通の符号を付し、その説明を省略する。また、以下で説明する各実施例では、ノンパンチスルー(Non Punch Through)型のIGBTを説明するが、本明細書で開示される技術は、パンチスルー(Punch Through)型のIGBTにも適用可能である。また、以下で説明する各実施例のIGBTには、半導体材料にシリコンが用いられている。しかし、本明細書で開示される技術は、シリコン以外の半導体材料のIGBTにも適用可能である。例えば、半導体材料が窒化ガリウム系、炭化シリコン系、ガリウム砒素系等の化合物半導体のIGBTにも適用可能である。

図1〜3にIGBT10の要部断面図、図4にIGBT10の要部上面図を模式的に示す。図1は図4のI-I線に対応した断面図であり、図2は図4のII-II線に対応した断面図であり、図3は図4のIII-III線に対応した断面図である。なお、図1〜4は、IGBT10の基本構造を示すものであり、実際はこの基本構造が繰り返して設けられ、1つの半導体装置を構成している。

図1に示すように、IGBT10は、p+型のコレクタ領域22と、コレクタ領域22上に設けられているn型のバッファ領域24と、バッファ領域24上に設けられているn−型のドリフト領域26(深部半導体領域の一例)と、ドリフト領域26上に設けられているp型のボディ領域28(中間部半導体領域の一例)を備えている。コレクタ領域22は、図示しないコレクタ電極と電気的に接続されている。コレクタ領域22とバッファ領域24は、イオン注入技術を利用して、ドリフト領域26の裏面に形成される。ボディ領域28も、イオン注入技術を利用して、ドリフト領域26の表面に形成される。n型のドリフト領域26及びバッファ領域24は、p型のボディ領域28とコレクタ領域22を隔てている。

IGBT10はさらに、ボディ領域28の表面に設けられているp+型のボディコンタクト領域32とn+型のエミッタ領域34(表面部半導体領域の一例)を備えている。エミッタ領域34は、トレンチゲート40に接している。エミッタ領域34とドリフト領域26は、ボディ領域28によって隔てられている。ボディコンタクト領域32とエミッタ領域34は、図示しないエミッタ電極と電気的に接続されている。ボディコンタクト領域32とエミッタ領域34は、イオン注入技術を利用して、ボディ領域28の表面に形成される。

IGBT10はさらに、トレンチゲート40を備えている。トレンチゲート40は、エミッタ領域34からドリフト領域26に向けてボディ領域28内を伸びている。トレンチゲート40は、ボディ領域28を貫通しており、一端がエミッタ領域34に接しており、他端がドリフト領域26内に侵入している。トレンチゲート40は、ゲート絶縁膜44と、そのゲート絶縁膜44で被覆されているゲート電極42を有している。ゲート絶縁膜44には酸化シリコンが用いられており、ゲート電極42には不純物を高濃度に含むポリシリコンが用いられている。

図1に示すように、トレンチゲート40のゲート絶縁膜44は、エミッタ領域34からドリフト領域26に向けて縦方向に延びているとともに相互に対向している一対の側面44aと、一方の側面44aから他方の側面44aまで横方向に延びている底面44bを有している。図4に示すように、トレンチゲート40を平面視すると、トレンチゲート40は一方向に長く伸びている。

図1に示すように、IGBT10はさらに、トレンチゲート40からドリフト領域26内を下方に向けて突出する2つの突出部46を備えている。右側の突出部46Rはゲート絶縁膜44の底面44bの右側周縁部に接して設けられており、左側の突出部46Lはゲート絶縁膜44の底面44bの左側周縁部に接して設けられている。図3に示すように、突出部46は、トレンチゲート40の長手方向に沿って延びており、その長手方向に沿ってゲート絶縁膜44の底面44bに接している。突出部46には、酸化シリコンが用いられている。

図1に示すように、突出部46は、第1表面46aと、その第1表面46aに対向する第2表面46bを有している。第1表面46aと第2表面46bはいずれも、エミッタ領域34とトレンチゲート40の下方の間に設けられており、エミッタ領域34とトレンチゲート40の下方を結ぶ方向を隔てるように設けられている。また、第1表面46aと第2表面46bはいずれも、ドリフト領域26に接している。第1表面46aは、ゲート絶縁膜44の底面44bと非平行であり、非連続的に接している。第2表面46bは、ゲート絶縁膜44の側面44aと平行であり、連続的に接している。ゲート絶縁膜44の底面44bから突出する突出部46の厚み46Tは、ゲート絶縁膜44の底面の厚み44Tよりも厚い。

次に、IGBT10の特徴を説明する。IGBT10は、突出部46を備えていることを特徴としている。さらに、突出部46の第1表面46aと第2表面46bがいずれも、ドリフト領域26に接していることを特徴としている。第1表面46aと第2表面46bがいずれもドリフト領域26に接しているので、第1表面46aと第2表面46bの間には電位差が生じない。このため、突出部46の第1表面46aと第2表面46bには反転層が形成されない。したがって、エミッタ領域34から供給された電子は、この突出部46を超えてトレンチゲート40の下方に移動することができない。この結果、トレンチゲート40の下方に移動する電子量が減少し、その電子に引き寄せられてトレンチゲート40の下方に移動する正孔量も減少する。

前記した課題で説明したように、トレンチゲート40の下方に正孔が集中すると、ゲート容量が経時的に変動し、サージ電圧を引き起こす原因となってしまう。IGBT10では、突出部46が設けられていることによって、電子がトレンチゲート40の下方に移動するのを物理的に抑制することができ、トレンチゲート40の下方に正孔が集中するのを抑制することができる。この結果、ゲート容量が経時的に変動することが抑制され、高耐量なIGBT10を得るこができる。

また、IGBT10は、次の特徴も有する。前記したように、IGBT10のボディ領域28は、イオン注入技術を利用して形成される。図5に示すように、ボディ領域28を熱拡散したときに、ボディ領域28がトレンチゲート40を超えて深い位置まで拡散してしまうことがある。この場合、図5に示すように、突出部46は、ボディ領域28がトレンチゲート40の下方にまで拡散することを防止することができる。このため、ボディ領域28がトレンチゲート40を超えて深い位置まで拡散したとしても、隣接する突出部46の間のトレンチゲート40の下方には、ドリフト領域26が存在している。これにより、ボディ領域28がトレンチゲート40を超えて深い位置まで拡散したとしても、ボディ領域28とドリフト領域26が突出部46を挟んで存在することになる。この場合、IGBT10がオンしているときに、ドリフト領域26とボディ領域28の間に電位差が生じるので、突出部46の第2表面46bの一部46cには第2の反転層が形成される。このため、エミッタ領域34から供給された電子は、その第2の反転層を通過してドリフト領域26まで移動することができる。したがって、IGBT10では、イオン注入技術を利用してボディ領域28を形成したときに、ボディ領域28がトレンチゲート40を超えて深い位置まで拡散したとしても、オンとオフを切換えることに支障がない。IGBT10は、イオン注入に係る製造公差を緩和する形態を備えていると評価することができる。IGBT10は、製造し易い特徴を有する。

なお、前記したように、突出部46の一部はドリフト領域26内に存在しているので、その部分には第2の反転層が形成されない。このため、電子が突出部46を超えてトレンチゲート40の下方にまで移動することはない。即ち、IGBT10の突出部46は、電子がトレンチゲート40の下方に移動するのを物理的に抑制する効果に加えて、IGBT10の製造を容易にするという効果をも有する。

なお、前記したように、突出部46の一部はドリフト領域26内に存在しているので、その部分には第2の反転層が形成されない。このため、電子が突出部46を超えてトレンチゲート40の下方にまで移動することはない。即ち、IGBT10の突出部46は、電子がトレンチゲート40の下方に移動するのを物理的に抑制する効果に加えて、IGBT10の製造を容易にするという効果をも有する。

以下、IGBT10の複数の変形例を説明する。

図6に示す変形例のIGBT10は、ドリフト領域26とボディ領域28の間にn型の正孔蓄積層27が設けられていることを特徴としている。正孔蓄積層27は、正孔に対してエネルギー障壁を形成し、ドリフト領域26からボディ領域28への正孔の移動を妨げる。これにより、ドリフト領域26内の正孔濃度を高くすることができる。このため、ドリフト領域26の抵抗値が低下し、オン電圧を低くすることができる。

図6に示す変形例のIGBT10は、ドリフト領域26とボディ領域28の間にn型の正孔蓄積層27が設けられていることを特徴としている。正孔蓄積層27は、正孔に対してエネルギー障壁を形成し、ドリフト領域26からボディ領域28への正孔の移動を妨げる。これにより、ドリフト領域26内の正孔濃度を高くすることができる。このため、ドリフト領域26の抵抗値が低下し、オン電圧を低くすることができる。

図7に示す変形例のIGBT10は、ボディ領域28内にn型の正孔蓄積層29が設けられていることを特徴としている。正孔蓄積層29は、正孔に対するエネルギー障壁を形成し、ボディ領域28内の正孔濃度を高くすることができる。このため、ボディ領域28の抵抗値が低下し、オン電圧を低くすることができる。

図8に示す変形例のIGBT10は、隣接する突出部46の間にp型のフローティング半導体領域52が設けられていることを特徴としている。フローティング半導体領域52は、ゲート絶縁膜44の底面44bに接している。フローティング半導体領域52は、ボディ領域28から電気的に絶縁されており、その電位はドリフト領域26の電位に応じて変動する。フローティング半導体領域52がトレンチゲート40の下方に設けられていると、ゲート容量が小さくなり、スイッチングを高速化することができる。

なお、p型のフローティング半導体領域52に代えて、i型の半導体領域を設けてもよい。

なお、p型のフローティング半導体領域52に代えて、i型の半導体領域を設けてもよい。

図9に示す変形例のIGBT10は、隣接する突出部46の間にp型のフローティング半導体領域52とn型のフローティング半導体領域54とp型の第2フローティング半導体領域56の積層が設けられていることを特徴としている。この作用効果も、図8に示す例と同様であり、ゲート容量が小さくなり、スイッチングを高速化することができる。

以下、突出部の形態が異なる複数の変形例を説明する。

図10に、IGBT11の要部断面図を模式的に示す。IGBT11は、突出部146がドリフト領域26を貫通してバッファ領域24にまで達していることを特徴としている。IGBT11によると、エミッタ領域34から供給された電子がトレンチゲート40の下方に移動するのを完全に防止することができる。したがって、コレクタ領域22から供給された正孔がトレンチゲート40の下方に集中する現象も顕著に抑制される。

なお、IGBT11では、隣接する突出部146の間において、コレクタ領域22を形成しない形態を採用するのが好ましい。これにより、隣接する突出部146の間のドリフト領域26に正孔が供給されないので、トレンチゲート40の下方に正孔が集中する現象をさらに抑制することができる。

図10に、IGBT11の要部断面図を模式的に示す。IGBT11は、突出部146がドリフト領域26を貫通してバッファ領域24にまで達していることを特徴としている。IGBT11によると、エミッタ領域34から供給された電子がトレンチゲート40の下方に移動するのを完全に防止することができる。したがって、コレクタ領域22から供給された正孔がトレンチゲート40の下方に集中する現象も顕著に抑制される。

なお、IGBT11では、隣接する突出部146の間において、コレクタ領域22を形成しない形態を採用するのが好ましい。これにより、隣接する突出部146の間のドリフト領域26に正孔が供給されないので、トレンチゲート40の下方に正孔が集中する現象をさらに抑制することができる。

図11に、IGBT12の要部断面図を模式的に示す。IGBT12は、4つの突出部246がゲート絶縁膜44の底面44bに接して設けられている。図12に示すように、トレンチゲート40の底面に設ける突出部246の個数は特に制限されるものではない。また、この形態は、後述する第2の製造方法によって作製され得るものである。

図12に、IGBT13の要部断面図を模式的に示す。IGBT13は、2つの突出部346がゲート絶縁膜44の側面44aに接して設けられていることを特徴としている。この例でも、突出部346の第1表面346aと第2表面346bのいずれもが、エミッタ領域34とトレンチゲート40の下方の間に設けられている。さらに、突出部346の第1表面346aと第2表面346bのいずれもが、ドリフト領域26に接している。したがって、エミッタ領域34から供給された電子は、この突出部346を超えてトレンチゲート40の下方にまで移動することが物理的に抑制されている。

図13に、IGBT14の要部断面図を模式的に示す。IGBT14では、突出部446の一端が、ボディ領域28内のゲート絶縁膜44の側面44aに接して設けられていることを特徴としている。さらに、突出部446は、その先端がドリフト領域26内に侵入していることを特徴としている。この例でも、突出部446の第1表面446aと第2表面446bのいずれもが、エミッタ領域34とトレンチゲート40の下方の間に設けられている。さらに、突出部446の第1表面446aと第2表面446bの一部が、ドリフト領域26に接している。したがって、エミッタ領域34から供給された電子は、この突出部446を超えてトレンチゲート40の下方にまで移動することが物理的に抑制されている。

また、突出部446の第2表面446bの一部446cは、ドリフト領域26に対向している。したがって、IGBT14がオンしているときに、ドリフト領域26とボディ領域28の間に電位差が生じるので、突出部446の第2表面446bの一部446cには第2の反転層が形成される。このため、エミッタ領域34から供給された電子は、その第2の反転層を通過してドリフト領域26まで移動することができる。

また、突出部446の第2表面446bの一部446cは、ドリフト領域26に対向している。したがって、IGBT14がオンしているときに、ドリフト領域26とボディ領域28の間に電位差が生じるので、突出部446の第2表面446bの一部446cには第2の反転層が形成される。このため、エミッタ領域34から供給された電子は、その第2の反転層を通過してドリフト領域26まで移動することができる。

以下、上記したIGBTのトレンチゲートを製造するいくつかの方法を説明する。以下に説明する製造方法は、本明細書で初めて開示された新規なトレンチゲートの製造方法に好適に用いられる工程のみを説明する。IGBTを製造するために要する他の工程は、従来既知の技術を利用することができる。

(トレンチゲートの第1製造方法)

以下、図14〜18を参照して、上記したトレンチゲート40の第1の製造方法を説明する。

まず、図14に示すように、n−型の半導体基板26(後に、ドリフト領域26になる)を準備する。

以下、図14〜18を参照して、上記したトレンチゲート40の第1の製造方法を説明する。

まず、図14に示すように、n−型の半導体基板26(後に、ドリフト領域26になる)を準備する。

次に、図15に示すように、半導体基板26の表面にマスク62をパターニングする。マスク62の材料にはCVD酸化膜が用いられる。マスク62の開口は、半導体基板26のトレンチ形成領域40Aの周縁に沿った位置の少なくとも一部に形成される。好ましくは、マスク62の開口は、半導体基板26のトレンチ形成領域40Aの周縁に沿って一巡して形成される。次に、ドライエッチング技術を利用して、マスク62の開口から露出する半導体基板26の表面をエッチングし、半導体基板26内に伸びる第1トレンチ71を形成する。このドライエッチングは、エッチングガスにHBrガスが用いられる。第1トレンチ71を形成した後に、マスク62は除去される。

次に、図16に示すように、熱酸化技術を利用して、第1トレンチ71を熱酸化膜63で充填する。

次に、図17に示すように、熱酸化膜63の表面にマスク64をパターニングする。マスク64の開口は、トレンチ形成領域40Aのうちの第1トレンチ71が形成されていない位置に対応して形成される。次に、ドライエッチング技術を利用して、マスク64の開口から露出する熱酸化膜63とその熱酸化膜63の下方の半導体基板26をエッチングし、半導体基板26内に伸びる第2トレンチ72を形成する。このドライエッチングは、エッチングガスにCF4、HBrガスが用いられる。第2トレンチ72の深さは、第1トレンチ71の深さよりも浅い。

次に、熱酸化膜63とマスク64を除去すると、図18に示すトレンチ73が形成される。上記製造方法によると、第1トレンチ71が第2トレンチ72よりも深く形成される。このため、第2トレンチ72から突出する第1トレンチ71によって、トレンチ73の底面の周縁部に突出トレンチ73aが形成される。この後に、熱酸化技術を利用して、突出トレンチ73aに熱酸化膜を充填すると、本明細書で開示される突出部が得られる。さらに、既知の熱酸化技術及びCVD(Chemical Vapor Deposition)技術を利用して、ゲート絶縁膜とゲート電極を形成し、トレンチゲートを完成させることができる。

(トレンチゲートの第2の製造方法)

以下、図19〜22を参照して、トレンチゲート40の第2の製造方法を説明する。

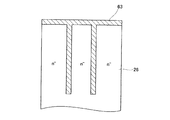

まず、図19に示すように、半導体基板26の表面にマスク65をパターニングする。マスク65の材料にはCVD酸化膜が用いられる。マスク65の開口は、半導体基板26のトレンチ形成領域40Aに複数個が設けられるように形成される。

以下、図19〜22を参照して、トレンチゲート40の第2の製造方法を説明する。

まず、図19に示すように、半導体基板26の表面にマスク65をパターニングする。マスク65の材料にはCVD酸化膜が用いられる。マスク65の開口は、半導体基板26のトレンチ形成領域40Aに複数個が設けられるように形成される。

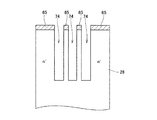

次に、図20に示すように、ドライエッチング技術を利用して、マスク65の開口から露出する半導体基板26の表面から半導体基板26内に伸びる複数のトレンチ74を形成する。このドライエッチングは、エッチングガスにHBrガスが用いられる。このため、複数のトレンチ74の側面は、(100)面である。

次に、図21に示すように、複数のトレンチ74内にエッチング液を供給し、トレンチ74の底面から下方に向けて突出する突出トレンチ75aを形成する。エッチング液には、KOH水溶液が用いられる。したがたって、突出トレンチ75aの側面は、(111)面である。このウェットエッチングでは、トレンチ74とトレンチ74の間の壁も同時に除去され、1つのトレンチ75が形成される。

次に、図22に示すように、熱酸化技術を利用して、トレンチ75の内壁に熱酸化膜44(後にゲート絶縁膜44になる)を形成する。この熱酸化では、トレンチ75の底面の突出トレンチ75aがほぼ熱酸化膜44で充填される。これらの工程を得て、本明細書で開示される突出部が得られる。

(トレンチゲートの第3の製造方法)

以下、図23〜26を参照して、トレンチゲート40の第3の製造方法を説明する。

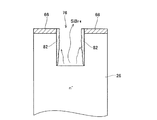

まず、図23に示すように、半導体基板26の表面にマスク66をパターニングする。マスク66の開口は、半導体基板26のトレンチ形成領域40Aに対応して形成される。次に、ドライエッチング技術を利用して、マスク66の開口から露出する半導体基板26の表面をエッチングし、トレンチ76を形成する。このドライエッチングは、エッチングガスにHBrガスが用いられる。このドライエッチングでは、ドライエッチングによって生成される半導体基板26とエッチングガス(HBr)が結合した揮発性物質(SiBr4)がトレンチ76の底面に堆積しない条件で行われる。なお、図示82に示すように、揮発性物質(SiBr4)の一部は、トレンチ76の側面に堆積することがある。

以下、図23〜26を参照して、トレンチゲート40の第3の製造方法を説明する。

まず、図23に示すように、半導体基板26の表面にマスク66をパターニングする。マスク66の開口は、半導体基板26のトレンチ形成領域40Aに対応して形成される。次に、ドライエッチング技術を利用して、マスク66の開口から露出する半導体基板26の表面をエッチングし、トレンチ76を形成する。このドライエッチングは、エッチングガスにHBrガスが用いられる。このドライエッチングでは、ドライエッチングによって生成される半導体基板26とエッチングガス(HBr)が結合した揮発性物質(SiBr4)がトレンチ76の底面に堆積しない条件で行われる。なお、図示82に示すように、揮発性物質(SiBr4)の一部は、トレンチ76の側面に堆積することがある。

次に、ドライエッチングの条件を変更する。このドライエッチングでは、ドライエッチングによって生成される半導体基板26とエッチングガス(HBr)が結合した揮発性物質(SiBr4)がトレンチ76の底面に堆積する条件で行われる。具体的には、エッチングレートが遅くなる条件で実施するのが良い。例えば、通常のエッチングレート(4000Å/min)の約1/2の速度で実施するのが良い。図25に示すように、トレンチ75の底面に揮発性物質(SiBr4)が堆積すると、トレンチ76の底面の中心側に多く堆積する(図示84参照)。このため、この条件でドライエッチングを実施し続けると、トレンチ76の底面において、周縁側のエッチングが中心側のエッチングよりも早く進行する。この結果、トレンチ76の底面の周縁側に突出トレンチ76aが形成される。

次に、図26に示すように、堆積した揮発性物質(SiBr4)を除去すると、底面の周縁に突出トレンチ76aを有するトレンチ76が得られる。この後に、熱酸化技術を利用して、突出トレンチ76aに熱酸化膜を充填することによって、本明細書で開示される突出部が得られる。

(トレンチゲートの第4の製造方法)

以下、図27〜29を参照して、トレンチゲート40の第4の製造方法を説明する。

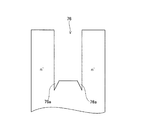

まず、図27に示すように、半導体基板26の表面にマスク67をパターニングする。マスク67の材料には、CVD酸化膜が用いられる。マスク67の開口は、半導体基板26のトレンチ形成領域40Aに対応して形成される。さらに、図27に示すように、マスク67の一部67a(以下、犠牲マスクという)が、半導体基板26のトレンチ形成領域40Aの表面にも形成される。犠牲マスク67aの幅67Wは、極めて小さい。なお、この例では、犠牲マスク67aがマスク67の一部として形成されている。この例に代えて、犠牲マスク67aをマスク67とは異なる材料で形成してもよい。

以下、図27〜29を参照して、トレンチゲート40の第4の製造方法を説明する。

まず、図27に示すように、半導体基板26の表面にマスク67をパターニングする。マスク67の材料には、CVD酸化膜が用いられる。マスク67の開口は、半導体基板26のトレンチ形成領域40Aに対応して形成される。さらに、図27に示すように、マスク67の一部67a(以下、犠牲マスクという)が、半導体基板26のトレンチ形成領域40Aの表面にも形成される。犠牲マスク67aの幅67Wは、極めて小さい。なお、この例では、犠牲マスク67aがマスク67の一部として形成されている。この例に代えて、犠牲マスク67aをマスク67とは異なる材料で形成してもよい。

次に、図28に示すように、ドライエッチング技術を利用して、マスク67の開口から露出する半導体基板26の表面をエッチングし、初期トレンチ77eを形成する。このドライエッチングは、エッチングガスにHBrガスが用いられる。犠牲マスク67aのエッチングレートは遅いものの、ドライエッチングによって犠牲マスク67aも少しずつエッチングされる。犠牲マスク67aのエッチング選択比にもよるが、犠牲マスク67aの幅67Wは、初期トレンチ77eが最終的なトレンチの深さに達するよりも先に消失するように調整されている。具体的には、初期トレンチ77eが最終的なトレンチの深さに達するまでの犠牲マスク67aの膜減り量を「X」とすると、犠牲マスク67aの幅67Wは、「2X」よりも小さく調整されている。ここで、膜減り量「X」は、犠牲マスク67aの一方の側面から削れる長さである。したがって、犠牲マスク67aの幅67Wが「2X」よりも小さく調整されていると、初期トレンチ77eが最終的なトレンチの深さに達するまでに犠牲マスク67aが消失する。犠牲マスク67aをトレンチ形成領域40Aの表面に形成することによって、トレンチ形成領域40Aにおけるエッチングの進行度に差を設けることができる。

ドライエッチングは、犠牲マスク67aが消失した後も続けられる。これにより、図29に示すように、初期トレンチ77eと初期トレンチ77eの間の壁もエッチングされ、底面に突出トレンチ77aを有するトレンチ77が形成される。この後に、熱酸化技術を利用して、突出部トレンチ77aに熱酸化膜を充填することによって、本明細書で開示される突出部が得られる。

(トレンチゲートの第4の製造方法の変形例)

図30に示すように、半導体基板26のトレンチゲート形成領域40Aの表面に複数の犠牲マスク68aを形成してもよい。この場合も、図31に示すように、犠牲マスク68aの幅68Wが極めて小さいので、ドライエッチングを実施すると、初期トレンチ78e,79eがある程度の深さに達したときに犠牲マスク68aが消失する。犠牲マスク68aが消失した後もドライエッチングを継続すると、図32に示すように、底面に突出トレンチ78aを有するトレンチ78が形成される。この後に、熱酸化技術を利用して、突出部トレンチ78aに熱酸化膜を充填することによって、本明細書で開示される突出部が得られる。

図30に示すように、半導体基板26のトレンチゲート形成領域40Aの表面に複数の犠牲マスク68aを形成してもよい。この場合も、図31に示すように、犠牲マスク68aの幅68Wが極めて小さいので、ドライエッチングを実施すると、初期トレンチ78e,79eがある程度の深さに達したときに犠牲マスク68aが消失する。犠牲マスク68aが消失した後もドライエッチングを継続すると、図32に示すように、底面に突出トレンチ78aを有するトレンチ78が形成される。この後に、熱酸化技術を利用して、突出部トレンチ78aに熱酸化膜を充填することによって、本明細書で開示される突出部が得られる。

このように、複数の犠牲マスク68aを分散して配置することによって、幅広なトレンチ78を形成することができる。

また、この例では、犠牲マスク68aと犠牲マスク68aの間の距離が狭いので、その間に形成される初期トレンチ79eの深さが浅い。このため、その後のドライエッチングによって、初期トレンチ79eの形態が最終的なトレンチ78において消失している。しかし、犠牲マスク68aと犠牲マスク68aの間の距離を長くすると、初期トレンチ79eも深く形成され、初期トレンチ79eの形態が最終的なトレンチ78の底面に現れる。この場合、最終的なトレンチ78の底面に3つ以上の突出トレンチが形成される。このような形態が必要とされる場合には、犠牲マスク68aのパターニングを工夫することによって対応することが可能である。

また、この例では、犠牲マスク68aと犠牲マスク68aの間の距離が狭いので、その間に形成される初期トレンチ79eの深さが浅い。このため、その後のドライエッチングによって、初期トレンチ79eの形態が最終的なトレンチ78において消失している。しかし、犠牲マスク68aと犠牲マスク68aの間の距離を長くすると、初期トレンチ79eも深く形成され、初期トレンチ79eの形態が最終的なトレンチ78の底面に現れる。この場合、最終的なトレンチ78の底面に3つ以上の突出トレンチが形成される。このような形態が必要とされる場合には、犠牲マスク68aのパターニングを工夫することによって対応することが可能である。

以上、本発明の具体例を詳細に説明したが、これらは例示に過ぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例を様々に変形、変更したものが含まれる。

また、本明細書または図面に説明した技術要素は、単独であるいは各種の組合せによって技術的有用性を発揮するものであり、出願時請求項記載の組合せに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成し得るものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

また、本明細書または図面に説明した技術要素は、単独であるいは各種の組合せによって技術的有用性を発揮するものであり、出願時請求項記載の組合せに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成し得るものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

22:コレクタ領域

24:バッファ領域

26:ドリフト領域

28:ボディ領域

32:ボディコンタクト領域

34:エミッタ領域

40:トレンチゲート

42:ゲート電極

44:ゲート絶縁膜

46:突出部

46a:第1表面

46b:第2表面

24:バッファ領域

26:ドリフト領域

28:ボディ領域

32:ボディコンタクト領域

34:エミッタ領域

40:トレンチゲート

42:ゲート電極

44:ゲート絶縁膜

46:突出部

46a:第1表面

46b:第2表面

Claims (12)

- 第1導電型の表面部半導体領域と、

第1導電型の深部半導体領域と、

表面部半導体領域と深部半導体領域を隔てている第2導電型の中間部半導体領域と、

表面部半導体領域から深部半導体領域に向けて中間部半導体領域内を伸びており、ゲート絶縁膜とそのゲート絶縁膜で被覆されているゲート電極を有しているトレンチゲートと、

一端がトレンチゲートの表面に接しているとともに、少なくとも一部が深部半導体領域内に突出している絶縁体の突出部と、を備えている半導体装置。 - 前記トレンチゲートのゲート絶縁膜は、表面部半導体領域から深部半導体領域に向けて延びているとともに相互に対向している一対の側面と、一方の前記側面から他方の前記側面まで延びている底面を有しており、

前記突出部は、前記ゲート絶縁膜の底面に接していることを特徴とする請求項1に記載の半導体装置。 - 複数の突出部が前記ゲート絶縁膜の底面に接していることを特徴とする請求項2に記載の半導体装置。

- 前記ゲート絶縁膜の底面に接している突出部と突出部の間に第2導電型の半導体領域が設けられており、その半導体領域がフローティングであることを特徴とする請求項3に記載の半導体装置。

- トレンチゲートを製造する方法であって、

半導体基板のトレンチゲート形成領域の表面の一部からドライエッチングによって第1の深さを有する第1トレンチを形成する第1工程と、

前記半導体基板の前記トレンチゲート形成領域の表面の残部からドライエッチングによって第2の深さを有する第2トレンチを形成する第2工程と、を備えており、

前記第1の深さは前記第2の深さよりも深いことを特徴とするトレンチゲートの製造方法。 - 前記第1工程では、前記トレンチゲート形成領域の周縁に沿った位置の少なくとも一部に前記第1トレンチを形成することを特徴とする請求項5のトレンチゲートの製造方法。

- トレンチゲートを製造する方法であって、

半導体基板のトレンチゲート形成領域の表面の一部からドライエッチングによって複数のトレンチを形成する第1工程と、

前記複数のトレンチ内にエッチング液を供給し、トレンチの底面から下方に向けて突出する突出トレンチをウェットエッチングによって形成する第2工程と、を備えており、

前記第1工程で形成されるトレンチの側面は第1面方位を有しており、

前記第2工程で形成される突出トレンチの側面は第2面方位を有しており、

第1側面と第2側面は、非平行であることを特徴としているトレンチゲートの製造方法。 - 前記半導体基板はシリコン基板であり、

前記第1面方位は(100)面であり、

前記第2面方位は(111)面であることを特徴とする請求項7に記載のトレンチゲートの製造方法。 - トレンチゲートを製造する方法であって、

半導体基板のトレンチゲート形成領域の表面からドライエッチングによってトレンチを形成する第1工程と、

ドライエッチングによって生成される前記半導体基板とエッチングガスが結合した揮発性物質が前記トレンチの底面に堆積する条件のドライエッチングによって、前記トレンチを更に深く形成する第2工程と、を備えていることを特徴とするトレンチゲートの製造方法。 - トレンチゲートを製造する方法であって、

半導体基板のトレンチゲート形成領域の表面の一部にマスクを形成する第1工程と、

半導体基板のトレンチゲート形成領域の表面からドライエッチングによってトレンチを形成する第2工程と、を備えており、

前記第2工程では、トレンチゲート形成領域の表面のマスクが消失した後もドライエッチングを継続することを特徴とするトレンチゲートの製造方法。 - 前記第1工程では、トレンチゲート形成領域の表面に複数のマスクを分散して形成することを特徴とする請求項10に記載のトレンチゲートの製造方法。

- 請求項5〜11のいずれか一項に記載のトレンチゲートの製造方法を備えた半導体装置の製造方法。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008156240A JP2009164558A (ja) | 2007-12-10 | 2008-06-16 | 半導体装置とその製造方法、並びにトレンチゲートの製造方法 |

| CN200880120102XA CN101897027B (zh) | 2007-12-10 | 2008-12-02 | 半导体装置及其制造方法和沟槽栅的制造方法 |

| US12/743,525 US20100276729A1 (en) | 2007-12-10 | 2008-12-02 | Semiconductor device, manufacturing method thereof, and manufacturing method of trench gate |

| EP08859002A EP2234163A4 (en) | 2007-12-10 | 2008-12-02 | SEMICONDUCTOR DEVICE AND METHOD FOR MANUFACTURING THE DEVICE, AND METHOD FOR MANUFACTURING THE TRENCH GRID |

| PCT/JP2008/071858 WO2009075200A1 (ja) | 2007-12-10 | 2008-12-02 | 半導体装置とその製造方法、並びにトレンチゲートの製造方法 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007317913 | 2007-12-10 | ||

| JP2008156240A JP2009164558A (ja) | 2007-12-10 | 2008-06-16 | 半導体装置とその製造方法、並びにトレンチゲートの製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009164558A true JP2009164558A (ja) | 2009-07-23 |

| JP2009164558A5 JP2009164558A5 (ja) | 2010-07-22 |

Family

ID=40755443

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008156240A Pending JP2009164558A (ja) | 2007-12-10 | 2008-06-16 | 半導体装置とその製造方法、並びにトレンチゲートの製造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US20100276729A1 (ja) |

| EP (1) | EP2234163A4 (ja) |

| JP (1) | JP2009164558A (ja) |

| CN (1) | CN101897027B (ja) |

| WO (1) | WO2009075200A1 (ja) |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014236088A (ja) * | 2013-05-31 | 2014-12-15 | 豊田合成株式会社 | 半導体素装置および半導体装置の製造方法 |

| JP2019071314A (ja) * | 2017-10-05 | 2019-05-09 | 国立研究開発法人産業技術総合研究所 | 半導体装置 |

| US10493057B2 (en) | 2015-09-23 | 2019-12-03 | Instituto Tecnologico Y De Estudios Superiores De Monterrey | Acetogenin molecules having antiplatelet and/or antithrombic activities, and methods and compositions thereof |

| US10575521B2 (en) | 2010-08-09 | 2020-03-03 | Instituto Technologico Y De Estudios Superiores De Monterrey | Antimicrobial, antibacterial and spore germination inhibiting activity from an avocado extract enriched in bioactive compounds |

| JP2020088343A (ja) * | 2018-11-30 | 2020-06-04 | 株式会社豊田中央研究所 | 半導体装置 |

| US10932484B2 (en) | 2016-10-19 | 2021-03-02 | Instituto Tecnologico Y De Estudios Superiores De Monterrey | Inhibitory activity of acetogenins against Listeria monocytogenes |

| JP7471267B2 (ja) | 2021-10-14 | 2024-04-19 | 富士電機株式会社 | 半導体装置 |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5472309B2 (ja) * | 2009-10-01 | 2014-04-16 | トヨタ自動車株式会社 | 半導体装置 |

| US8866222B2 (en) | 2012-03-07 | 2014-10-21 | Infineon Technologies Austria Ag | Charge compensation semiconductor device |

| US8901642B2 (en) * | 2012-03-07 | 2014-12-02 | Infineon Technologies Austria Ag | Charge compensation semiconductor device |

| CN103390650B (zh) * | 2012-05-04 | 2017-08-08 | 朱江 | 一种具有无源金属肖特基半导体装置及其制备方法 |

| JP5747891B2 (ja) * | 2012-10-09 | 2015-07-15 | トヨタ自動車株式会社 | 半導体装置 |

| DE102013207829A1 (de) * | 2012-12-27 | 2014-07-03 | Ihp Gmbh - Innovations For High Performance Microelectronics / Leibniz-Institut Für Innovative Mikroelektronik | Chip-Antenne, Elektronisches Bauelement und Herstellungsverfahren dafür |

| US8823084B2 (en) | 2012-12-31 | 2014-09-02 | Infineon Technologies Austria Ag | Semiconductor device with charge compensation structure arrangement for optimized on-state resistance and switching losses |

| JP5807653B2 (ja) * | 2013-03-26 | 2015-11-10 | トヨタ自動車株式会社 | 半導体装置の製造方法 |

| US9147763B2 (en) | 2013-09-23 | 2015-09-29 | Infineon Technologies Austria Ag | Charge-compensation semiconductor device |

| JP6453634B2 (ja) * | 2014-12-10 | 2019-01-16 | トヨタ自動車株式会社 | 半導体装置 |

| JP2016213374A (ja) * | 2015-05-12 | 2016-12-15 | 株式会社豊田中央研究所 | 半導体装置 |

| DE102019216145A1 (de) * | 2019-10-21 | 2021-04-22 | Robert Bosch Gmbh | Verfahren zum herstellen einer halbleitervorrichtung |

| CN111261713B (zh) * | 2020-03-25 | 2022-09-09 | 广东芯聚能半导体有限公司 | 沟槽型igbt器件结构 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08316479A (ja) * | 1995-03-14 | 1996-11-29 | Mitsubishi Electric Corp | 絶縁ゲート型半導体装置およびその製造方法 |

| JP2004153112A (ja) * | 2002-10-31 | 2004-05-27 | Toshiba Corp | 電力用半導体装置 |

| US7132712B2 (en) * | 2002-11-05 | 2006-11-07 | Fairchild Semiconductor Corporation | Trench structure having one or more diodes embedded therein adjacent a PN junction |

| JP2007207935A (ja) * | 2006-01-31 | 2007-08-16 | Fuji Electric Holdings Co Ltd | 炭化珪素半導体素子の製造方法 |

| JP2007317779A (ja) * | 2006-05-24 | 2007-12-06 | Toyota Motor Corp | 絶縁ゲート型半導体装置およびその製造方法 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007129259A (ja) * | 1996-08-01 | 2007-05-24 | Kansai Electric Power Co Inc:The | 絶縁ゲート半導体装置 |

| JP2005056868A (ja) * | 2001-06-04 | 2005-03-03 | Matsushita Electric Ind Co Ltd | 炭化珪素半導体装置の製造方法 |

| EP1525621B1 (en) * | 2002-05-31 | 2011-10-12 | Nxp B.V. | Method of operating a trench gate semiconductor device |

| JP2004022941A (ja) * | 2002-06-19 | 2004-01-22 | Toshiba Corp | 半導体装置 |

| CN103199017B (zh) * | 2003-12-30 | 2016-08-03 | 飞兆半导体公司 | 形成掩埋导电层方法、材料厚度控制法、形成晶体管方法 |

| JP2005276931A (ja) * | 2004-03-23 | 2005-10-06 | Toshiba Corp | 半導体装置およびその製造方法 |

| JP4491307B2 (ja) * | 2004-09-21 | 2010-06-30 | トヨタ自動車株式会社 | 半導体装置およびその製造方法 |

| JP4059510B2 (ja) * | 2004-10-22 | 2008-03-12 | 株式会社東芝 | 半導体装置及びその製造方法 |

| JP2006332591A (ja) * | 2005-04-28 | 2006-12-07 | Denso Corp | 半導体装置 |

| CN101288179B (zh) * | 2005-07-27 | 2010-05-26 | 英飞凌科技奥地利股份公司 | 具有漂移区和漂移控制区的半导体器件 |

| JP4817827B2 (ja) * | 2005-12-09 | 2011-11-16 | 株式会社東芝 | 半導体装置 |

-

2008

- 2008-06-16 JP JP2008156240A patent/JP2009164558A/ja active Pending

- 2008-12-02 WO PCT/JP2008/071858 patent/WO2009075200A1/ja active Application Filing

- 2008-12-02 CN CN200880120102XA patent/CN101897027B/zh not_active Expired - Fee Related

- 2008-12-02 EP EP08859002A patent/EP2234163A4/en not_active Withdrawn

- 2008-12-02 US US12/743,525 patent/US20100276729A1/en not_active Abandoned

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08316479A (ja) * | 1995-03-14 | 1996-11-29 | Mitsubishi Electric Corp | 絶縁ゲート型半導体装置およびその製造方法 |

| JP2004153112A (ja) * | 2002-10-31 | 2004-05-27 | Toshiba Corp | 電力用半導体装置 |

| US7132712B2 (en) * | 2002-11-05 | 2006-11-07 | Fairchild Semiconductor Corporation | Trench structure having one or more diodes embedded therein adjacent a PN junction |

| JP2007207935A (ja) * | 2006-01-31 | 2007-08-16 | Fuji Electric Holdings Co Ltd | 炭化珪素半導体素子の製造方法 |

| JP2007317779A (ja) * | 2006-05-24 | 2007-12-06 | Toyota Motor Corp | 絶縁ゲート型半導体装置およびその製造方法 |

Cited By (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10575521B2 (en) | 2010-08-09 | 2020-03-03 | Instituto Technologico Y De Estudios Superiores De Monterrey | Antimicrobial, antibacterial and spore germination inhibiting activity from an avocado extract enriched in bioactive compounds |

| US10582707B2 (en) | 2010-08-09 | 2020-03-10 | Instituto Tecnologico Y De Estudios Superiores De Monterrey | Antimicrobial antibacterial and spore germination inhibiting activity from an avocado extract enriched in bioactive compounds |

| JP2014236088A (ja) * | 2013-05-31 | 2014-12-15 | 豊田合成株式会社 | 半導体素装置および半導体装置の製造方法 |

| US10493057B2 (en) | 2015-09-23 | 2019-12-03 | Instituto Tecnologico Y De Estudios Superiores De Monterrey | Acetogenin molecules having antiplatelet and/or antithrombic activities, and methods and compositions thereof |

| US10932484B2 (en) | 2016-10-19 | 2021-03-02 | Instituto Tecnologico Y De Estudios Superiores De Monterrey | Inhibitory activity of acetogenins against Listeria monocytogenes |

| JP2019071314A (ja) * | 2017-10-05 | 2019-05-09 | 国立研究開発法人産業技術総合研究所 | 半導体装置 |

| JP2022002345A (ja) * | 2017-10-05 | 2022-01-06 | 富士電機株式会社 | 半導体装置 |

| JP7059556B2 (ja) | 2017-10-05 | 2022-04-26 | 富士電機株式会社 | 半導体装置 |

| JP2020088343A (ja) * | 2018-11-30 | 2020-06-04 | 株式会社豊田中央研究所 | 半導体装置 |

| JP7204454B2 (ja) | 2018-11-30 | 2023-01-16 | 株式会社豊田中央研究所 | 半導体装置 |

| JP7471267B2 (ja) | 2021-10-14 | 2024-04-19 | 富士電機株式会社 | 半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN101897027B (zh) | 2012-02-29 |

| EP2234163A1 (en) | 2010-09-29 |

| CN101897027A (zh) | 2010-11-24 |

| WO2009075200A1 (ja) | 2009-06-18 |

| EP2234163A4 (en) | 2012-07-04 |

| US20100276729A1 (en) | 2010-11-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2009164558A (ja) | 半導体装置とその製造方法、並びにトレンチゲートの製造方法 | |

| JP6406361B2 (ja) | 半導体装置及びその製造方法 | |

| JP4645034B2 (ja) | Iii族窒化物半導体を有する半導体素子 | |

| JP6728953B2 (ja) | 半導体装置及びその製造方法 | |

| JP5644793B2 (ja) | 半導体装置 | |

| JP5102411B2 (ja) | 半導体装置およびその製造方法 | |

| JP2008034794A (ja) | 縦型トレンチ型絶縁ゲートmos半導体装置 | |

| JP2008117881A (ja) | 半導体装置及びその製造方法 | |

| JP2019165206A (ja) | 絶縁ゲート型半導体装置及びその製造方法 | |

| JP6319508B2 (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP6616878B2 (ja) | 半導体装置 | |

| JP6563639B2 (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP2009130357A (ja) | トレンチmosfet及びその製造方法 | |

| US9954068B2 (en) | Method of forming a transistor, method of patterning a substrate, and transistor | |

| JP4929594B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| JP2010109031A (ja) | 半導体装置及びその製造方法 | |

| JP2005150352A (ja) | 炭化珪素半導体装置およびその製造方法 | |

| CN113809145B (zh) | 窄台面绝缘栅双极型晶体管器件及形成方法 | |

| JP2009212529A (ja) | Iii族窒化物半導体を有する半導体素子 | |

| JP4491307B2 (ja) | 半導体装置およびその製造方法 | |

| JP3975992B2 (ja) | 半導体装置及びその製造方法 | |

| JP2019096732A (ja) | 半導体装置 | |

| JP5394647B2 (ja) | 半導体装置 | |

| JP2021012940A (ja) | 半導体装置の製造方法 | |

| JP6539026B2 (ja) | 半導体装置及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100604 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120327 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120918 |