JP7204454B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP7204454B2 JP7204454B2 JP2018225629A JP2018225629A JP7204454B2 JP 7204454 B2 JP7204454 B2 JP 7204454B2 JP 2018225629 A JP2018225629 A JP 2018225629A JP 2018225629 A JP2018225629 A JP 2018225629A JP 7204454 B2 JP7204454 B2 JP 7204454B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- semiconductor device

- specific

- pair

- drift region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 221

- 150000001875 compounds Chemical class 0.000 claims description 71

- 210000000746 body region Anatomy 0.000 claims description 60

- 239000000758 substrate Substances 0.000 claims description 34

- 239000000463 material Substances 0.000 claims description 19

- 229910004298 SiO 2 Inorganic materials 0.000 claims description 3

- 239000012212 insulator Substances 0.000 claims description 3

- 230000004044 response Effects 0.000 claims description 2

- 238000000034 method Methods 0.000 description 35

- 238000004519 manufacturing process Methods 0.000 description 23

- 230000000052 comparative effect Effects 0.000 description 15

- 230000008569 process Effects 0.000 description 14

- 230000000694 effects Effects 0.000 description 13

- 239000010410 layer Substances 0.000 description 12

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 9

- 230000008646 thermal stress Effects 0.000 description 8

- 239000012535 impurity Substances 0.000 description 7

- 229910052814 silicon oxide Inorganic materials 0.000 description 7

- 238000001312 dry etching Methods 0.000 description 6

- 230000004048 modification Effects 0.000 description 6

- 238000012986 modification Methods 0.000 description 6

- 239000013078 crystal Substances 0.000 description 5

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 5

- 229920005591 polysilicon Polymers 0.000 description 5

- 230000005856 abnormality Effects 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 150000002500 ions Chemical class 0.000 description 3

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 2

- 238000000231 atomic layer deposition Methods 0.000 description 2

- 239000012141 concentrate Substances 0.000 description 2

- 229910002804 graphite Inorganic materials 0.000 description 2

- 239000010439 graphite Substances 0.000 description 2

- 230000007480 spreading Effects 0.000 description 2

- 238000003892 spreading Methods 0.000 description 2

- 239000002344 surface layer Substances 0.000 description 2

- 229910052681 coesite Inorganic materials 0.000 description 1

- 239000013256 coordination polymer Substances 0.000 description 1

- 229910052906 cristobalite Inorganic materials 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 230000020169 heat generation Effects 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 229910052682 stishovite Inorganic materials 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 229910052905 tridymite Inorganic materials 0.000 description 1

Images

Landscapes

- Electrodes Of Semiconductors (AREA)

- Recrystallisation Techniques (AREA)

Description

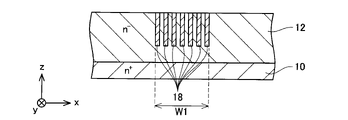

図1の要部断面図に示されるように、半導体装置1は、縦型のMOSFETである。半導体装置1は、プレーナゲート構造を有する。半導体装置1は、化合物半導体8、ゲート絶縁膜22、ゲート電極24、ソース電極26、及び、ドレイン電極28を備えている。

負荷短絡によってドレイン電極28に高い電圧が印加されると、ドレイン電極28からソース電極26に大電流が流れる。具体的には、ドレイン電極28、基板10、ドリフト領域12、JFET領域20、ボディ領域14の反転層、ソース領域16、ソース電極26という順番で電流が流れる。このような状況において、図1に示す電流集中領域40に大電流が流れる。具体的には、電流集中領域40は、JFET領域20の一部、及び、ドリフト領域12のうちJFET領域20の下方の領域である。電流集中領域40は、大電流が流れることによって発熱する。

次に、図2~図9を参照して、半導体装置1の製造方法を説明する。図2のフローチャートのステップS1において、SiCを材料とするn型の基板10の主面上に、周知のエピタキシャル成長技術を用いてn型のドリフト領域12を堆積させる(第1成長工程)。エピタキシャル成長技術の一例は、有機金属化合物気相成長法(MOCVD法)である。

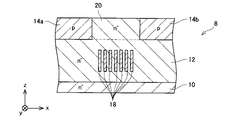

図11に、第2実施例の半導体装置201の要部断面図を示す。半導体装置201は、縦型のMOSFETであり、トレンチゲート型である。半導体装置201は、化合物半導体208、トレンチゲート220、絶縁膜225、ソース電極226、及び、ドレイン電極228を備えている。

負荷短絡によってドレイン電極228に高い電圧が印加されると、ドレイン電極228からソース電極226に大電流が流れる。具体的には、ドレイン電極228、基板210、ドリフト領域212、ボディ領域214の反転層IL、ソース領域216、ソース電極226という順番で電流が流れる。このような状況において、図11に示す電流集中領域240に大電流が流れる。具体的には、電流集中領域240は、トレンチ220Tの下端よりも下方であり、かつ、半導体装置201を垂直上方から見たときに、トレンチ220Tよりも外側の領域である。電流集中領域240は、大電流が流れることによって、発熱する。上述のように、ドリフト領域212はSiCからなる。SiCの熱伝導率は、シリコン酸化膜、ポリシリコン等よりも小さい。このため、電流集中領域240の発熱による熱は、ドリフト領域212(SiC)内を伝導する。電流集中領域240の上方には、熱伝導率が小さい材料が設けられていない。このため、半導体装置201を垂直上方から見たときに、トレンチ220Tの外側に拡散された熱は、半導体装置201の上方に放熱される。一方、トレンチ220Tには、熱伝導率が小さい材料からなるゲート電極224及びゲート絶縁膜222が形成されている。このため、半導体装置201を垂直上方から見たときに、トレンチ220Tの内側に拡散された熱は、半導体装置201の上方に放熱されない。このため、トレンチ220Tの下方が発熱し、発熱領域242となる。

次に、図12~図17を参照して、半導体装置201の製造方法を説明する。図12のフローチャートのステップS21、S22は、それぞれ、第1実施例における図2のフローチャートのステップS1、S2と同様である。これにより、図13に示すように、ドリフト領域212に複数の特定領域218が形成される。

図18に、第3実施例の半導体装置301の要部断面図を示す。第3実施例の半導体装置301は、特定領域318の構造を除いて、第1実施例の半導体装置1と同様の構造を有する。以下では、実施例間で共通する構造については、同じ符号を付して、その説明を省略する。

図19に、第4実施例の半導体装置401の要部断面図を示す。第4実施例の半導体装置401は、特定領域418の構造を除いて、第1実施例の半導体装置1と同様の構造を有する。

図20に、第5実施例の半導体装置501の要部断面図を示す。第5実施例の半導体装置501は、複数の特定領域18上にギャップGが形成されている点を除いて、第1実施例の半導体装置1と同様の構造を有する。なお、図20では、見易くするために、左端の特定領域18上のギャップにのみ符号が付されている。

Claims (7)

- 化合物半導体を有する縦型の半導体装置であって、

負荷短絡時に大電流が流れることに応じて発熱する前記化合物半導体の特定領域が、前記化合物半導体よりも線膨張係数が小さい特定材料を含み、

前記化合物半導体は、

基板と、

前記基板の上に設けられている第1導電型のドリフト領域と、

前記ドリフト領域の上に設けられており、互いに離間している第2導電型の一対のボディ領域であって、前記化合物半導体の上面に露出している前記一対のボディ領域と、

前記ドリフト領域の上であり、かつ、前記一対のボディ領域の間に設けられている前記第1導電型のJFET領域であって、前記一対のボディ領域のそれぞれに接触しており、前記化合物半導体の上面に露出している前記JFET領域と、

を備え、

前記半導体装置は、さらに、

ゲート絶縁膜を介して、前記化合物半導体の上面に設けられているゲート電極であって、前記ゲート絶縁膜を介して、前記一対のボディ領域の一部、及び、前記JFET領域に対向する前記ゲート電極を備え、

前記特定領域は、前記半導体装置を前記化合物半導体の上面の垂直上方から見たときに、前記一対のボディ領域の間に設けられており、

前記特定領域は、前記ドリフト領域内に設けられており、

前記特定領域の下端は、前記ドリフト領域の下端よりも上方に位置している、半導体装置。 - 前記特定領域は、前記一対のボディ領域の下面よりも下方側であり、かつ、前記半導体装置を前記化合物半導体の上面の垂直上方から見たときに、前記一対のボディ領域の間に設けられており、前記一対のボディ領域の下方に設けられていない、請求項1に記載の半導体装置。

- 前記ドリフト領域は、前記基板の上に設けられている第1ドリフト領域と、前記第1ドリフト領域の上に設けられている第2ドリフト領域と、を備えており、

前記一対のボディ領域及び前記JFET領域は、前記第2ドリフト領域の上に設けられており、

前記特定領域は、前記第1ドリフト領域に設けられており、

前記特定領域の上端は、前記第1ドリフト領域と前記第2ドリフト領域との間の界面と一致する、請求項1又は2に記載の半導体装置。 - 複数の前記特定領域を備え、

前記半導体装置を前記化合物半導体の上面の垂直上方から見たときに、前記複数の特定領域のそれぞれが離間している、請求項1~3のいずれか一項に記載の半導体装置。 - 前記特定材料は、導電性のSi、導電性のC、又は、導電性を有する多結晶のSiCである、請求項1~4のいずれか一項に記載の半導体装置。

- 前記特定材料は、絶縁体であるSiO2又は空気である、請求項1~5のいずれか一項に記載の半導体装置。

- 前記化合物半導体は、SiC又はGaNである、請求項1~6のいずれか一項に記載の半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2018225629A JP7204454B2 (ja) | 2018-11-30 | 2018-11-30 | 半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2018225629A JP7204454B2 (ja) | 2018-11-30 | 2018-11-30 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2020088343A JP2020088343A (ja) | 2020-06-04 |

| JP7204454B2 true JP7204454B2 (ja) | 2023-01-16 |

Family

ID=70908952

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018225629A Active JP7204454B2 (ja) | 2018-11-30 | 2018-11-30 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP7204454B2 (ja) |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007288172A (ja) | 2006-03-24 | 2007-11-01 | Hitachi Ltd | 半導体装置 |

| JP2009164558A (ja) | 2007-12-10 | 2009-07-23 | Toyota Central R&D Labs Inc | 半導体装置とその製造方法、並びにトレンチゲートの製造方法 |

| JP2012190982A (ja) | 2011-03-10 | 2012-10-04 | Toshiba Corp | 半導体装置とその製造方法 |

| JP2017041613A (ja) | 2015-08-21 | 2017-02-23 | トヨタ自動車株式会社 | 半導体装置の製造方法と半導体装置 |

-

2018

- 2018-11-30 JP JP2018225629A patent/JP7204454B2/ja active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007288172A (ja) | 2006-03-24 | 2007-11-01 | Hitachi Ltd | 半導体装置 |

| JP2009164558A (ja) | 2007-12-10 | 2009-07-23 | Toyota Central R&D Labs Inc | 半導体装置とその製造方法、並びにトレンチゲートの製造方法 |

| JP2012190982A (ja) | 2011-03-10 | 2012-10-04 | Toshiba Corp | 半導体装置とその製造方法 |

| JP2017041613A (ja) | 2015-08-21 | 2017-02-23 | トヨタ自動車株式会社 | 半導体装置の製造方法と半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2020088343A (ja) | 2020-06-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN110301034B (zh) | 碳化硅层叠基板及其制造方法 | |

| JP6109444B1 (ja) | 半導体装置 | |

| JP6120525B2 (ja) | 炭化珪素半導体装置 | |

| US20150287598A1 (en) | Semiconductor device and method for manufacturing same | |

| CN111133586B (zh) | 半导体装置 | |

| JP2017092368A (ja) | 半導体装置および半導体装置の製造方法 | |

| JP7029710B2 (ja) | 半導体装置 | |

| US9318565B2 (en) | Power semiconductor device with dual field plate arrangement and method of making | |

| JP5397289B2 (ja) | 電界効果トランジスタ | |

| CN104919594B (zh) | 制造半导体器件的方法 | |

| CN108470767A (zh) | 氮化物半导体器件 | |

| US20190074386A1 (en) | Semiconductor device | |

| JP5556863B2 (ja) | ワイドバンドギャップ半導体縦型mosfet | |

| CN108335965B (zh) | SiC-MOSFET的制造方法 | |

| JP5145694B2 (ja) | SiC半導体縦型MOSFETの製造方法。 | |

| WO2015076020A1 (ja) | 半導体装置 | |

| JP3496509B2 (ja) | 炭化珪素半導体装置の製造方法 | |

| JP7204454B2 (ja) | 半導体装置 | |

| JP5055773B2 (ja) | 半導体素子 | |

| JP2018093027A (ja) | 半導体装置 | |

| JP2009212458A (ja) | 半導体装置、電子機器およびそれらの製造方法 | |

| JP7414499B2 (ja) | 窒化物半導体装置 | |

| JP7628874B2 (ja) | 半導体装置及びその製造方法 | |

| CN120201752B (zh) | 一种半导体器件及其制作方法 | |

| CN116635984B (zh) | 半导体装置及其制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20210312 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20210712 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20220519 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20220621 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220812 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20221213 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20221228 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7204454 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |