JP2004214459A - 不揮発性磁気メモリ装置及びその製造方法 - Google Patents

不揮発性磁気メモリ装置及びその製造方法 Download PDFInfo

- Publication number

- JP2004214459A JP2004214459A JP2003000486A JP2003000486A JP2004214459A JP 2004214459 A JP2004214459 A JP 2004214459A JP 2003000486 A JP2003000486 A JP 2003000486A JP 2003000486 A JP2003000486 A JP 2003000486A JP 2004214459 A JP2004214459 A JP 2004214459A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- interlayer insulating

- insulating layer

- forming

- ferromagnetic

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Abandoned

Links

- 238000000034 method Methods 0.000 title claims description 111

- 230000005291 magnetic effect Effects 0.000 title claims description 80

- 230000015654 memory Effects 0.000 title description 14

- 230000008569 process Effects 0.000 title description 7

- 239000010410 layer Substances 0.000 claims abstract description 653

- 239000011229 interlayer Substances 0.000 claims abstract description 177

- 230000005294 ferromagnetic effect Effects 0.000 claims description 134

- 238000004519 manufacturing process Methods 0.000 claims description 74

- 239000004065 semiconductor Substances 0.000 claims description 68

- 239000000758 substrate Substances 0.000 claims description 65

- 239000004020 conductor Substances 0.000 claims description 32

- 238000000059 patterning Methods 0.000 claims description 17

- 239000010408 film Substances 0.000 description 104

- 230000005415 magnetization Effects 0.000 description 78

- 230000005290 antiferromagnetic effect Effects 0.000 description 64

- 230000004888 barrier function Effects 0.000 description 35

- 238000004544 sputter deposition Methods 0.000 description 28

- 238000005530 etching Methods 0.000 description 23

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 20

- 238000001459 lithography Methods 0.000 description 19

- 238000005229 chemical vapour deposition Methods 0.000 description 17

- 238000001020 plasma etching Methods 0.000 description 17

- 239000010949 copper Substances 0.000 description 14

- 229910052782 aluminium Inorganic materials 0.000 description 13

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 13

- 230000005641 tunneling Effects 0.000 description 13

- 229910052786 argon Inorganic materials 0.000 description 10

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 10

- 229910052721 tungsten Inorganic materials 0.000 description 10

- 239000010937 tungsten Substances 0.000 description 10

- 229910004298 SiO 2 Inorganic materials 0.000 description 9

- 239000000463 material Substances 0.000 description 8

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 8

- 229920005591 polysilicon Polymers 0.000 description 8

- 238000004380 ashing Methods 0.000 description 7

- 229910052802 copper Inorganic materials 0.000 description 7

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 7

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 6

- 229910045601 alloy Inorganic materials 0.000 description 6

- 239000000956 alloy Substances 0.000 description 6

- 239000003302 ferromagnetic material Substances 0.000 description 6

- 239000012535 impurity Substances 0.000 description 6

- 230000001590 oxidative effect Effects 0.000 description 6

- 238000005240 physical vapour deposition Methods 0.000 description 6

- 239000010936 titanium Substances 0.000 description 6

- 229910000914 Mn alloy Inorganic materials 0.000 description 5

- 229910052581 Si3N4 Inorganic materials 0.000 description 5

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 238000002955 isolation Methods 0.000 description 5

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 5

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 4

- UMVBXBACMIOFDO-UHFFFAOYSA-N [N].[Si] Chemical compound [N].[Si] UMVBXBACMIOFDO-UHFFFAOYSA-N 0.000 description 4

- 239000002885 antiferromagnetic material Substances 0.000 description 4

- 238000000231 atomic layer deposition Methods 0.000 description 4

- 239000005380 borophosphosilicate glass Substances 0.000 description 4

- 239000007789 gas Substances 0.000 description 4

- 230000004048 modification Effects 0.000 description 4

- 238000012986 modification Methods 0.000 description 4

- 229910052710 silicon Inorganic materials 0.000 description 4

- 239000010703 silicon Substances 0.000 description 4

- 229910003271 Ni-Fe Inorganic materials 0.000 description 3

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 3

- 230000008859 change Effects 0.000 description 3

- 230000008878 coupling Effects 0.000 description 3

- 238000010168 coupling process Methods 0.000 description 3

- 238000005859 coupling reaction Methods 0.000 description 3

- 230000003647 oxidation Effects 0.000 description 3

- 238000007254 oxidation reaction Methods 0.000 description 3

- 239000001301 oxygen Substances 0.000 description 3

- 229910052760 oxygen Inorganic materials 0.000 description 3

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 3

- 229910052814 silicon oxide Inorganic materials 0.000 description 3

- 229910018182 Al—Cu Inorganic materials 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 229910052736 halogen Inorganic materials 0.000 description 2

- 150000002367 halogens Chemical class 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 230000010354 integration Effects 0.000 description 2

- 230000003993 interaction Effects 0.000 description 2

- -1 magnesium nitride Chemical class 0.000 description 2

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 2

- 239000000395 magnesium oxide Substances 0.000 description 2

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 238000007747 plating Methods 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 1

- PIGFYZPCRLYGLF-UHFFFAOYSA-N Aluminum nitride Chemical compound [Al]#N PIGFYZPCRLYGLF-UHFFFAOYSA-N 0.000 description 1

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 1

- 229910020598 Co Fe Inorganic materials 0.000 description 1

- 229910002519 Co-Fe Inorganic materials 0.000 description 1

- 229910002551 Fe-Mn Inorganic materials 0.000 description 1

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 1

- 229910001030 Iron–nickel alloy Inorganic materials 0.000 description 1

- 229910016006 MoSi Inorganic materials 0.000 description 1

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 1

- 229910008599 TiW Inorganic materials 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 229910000428 cobalt oxide Inorganic materials 0.000 description 1

- IVMYJDGYRUAWML-UHFFFAOYSA-N cobalt(ii) oxide Chemical compound [Co]=O IVMYJDGYRUAWML-UHFFFAOYSA-N 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 229910001873 dinitrogen Inorganic materials 0.000 description 1

- 238000009713 electroplating Methods 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 238000007737 ion beam deposition Methods 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- SHMWNGFNWYELHA-UHFFFAOYSA-N iridium manganese Chemical compound [Mn].[Ir] SHMWNGFNWYELHA-UHFFFAOYSA-N 0.000 description 1

- DALUDRGQOYMVLD-UHFFFAOYSA-N iron manganese Chemical compound [Mn].[Fe] DALUDRGQOYMVLD-UHFFFAOYSA-N 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 230000001788 irregular Effects 0.000 description 1

- 229910052749 magnesium Inorganic materials 0.000 description 1

- 239000011777 magnesium Substances 0.000 description 1

- 238000001755 magnetron sputter deposition Methods 0.000 description 1

- ZAUUZASCMSWKGX-UHFFFAOYSA-N manganese nickel Chemical compound [Mn].[Ni] ZAUUZASCMSWKGX-UHFFFAOYSA-N 0.000 description 1

- IGOJMROYPFZEOR-UHFFFAOYSA-N manganese platinum Chemical compound [Mn].[Pt] IGOJMROYPFZEOR-UHFFFAOYSA-N 0.000 description 1

- GBZQODYDRJQFHG-UHFFFAOYSA-N manganese rhodium Chemical compound [Mn].[Rh] GBZQODYDRJQFHG-UHFFFAOYSA-N 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 229910000480 nickel oxide Inorganic materials 0.000 description 1

- 238000005121 nitriding Methods 0.000 description 1

- GNRSAWUEBMWBQH-UHFFFAOYSA-N oxonickel Chemical compound [Ni]=O GNRSAWUEBMWBQH-UHFFFAOYSA-N 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- KDLHZDBZIXYQEI-UHFFFAOYSA-N palladium Substances [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Substances [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 230000001698 pyrogenic effect Effects 0.000 description 1

- 238000005546 reactive sputtering Methods 0.000 description 1

- 229910052707 ruthenium Inorganic materials 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 238000000992 sputter etching Methods 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 229910052723 transition metal Inorganic materials 0.000 description 1

- 150000003624 transition metals Chemical class 0.000 description 1

- 238000001771 vacuum deposition Methods 0.000 description 1

- 239000002699 waste material Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B61/00—Magnetic memory devices, e.g. magnetoresistive RAM [MRAM] devices

- H10B61/20—Magnetic memory devices, e.g. magnetoresistive RAM [MRAM] devices comprising components having three or more electrodes, e.g. transistors

- H10B61/22—Magnetic memory devices, e.g. magnetoresistive RAM [MRAM] devices comprising components having three or more electrodes, e.g. transistors of the field-effect transistor [FET] type

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y10/00—Nanotechnology for information processing, storage or transmission, e.g. quantum computing or single electron logic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Nanotechnology (AREA)

- Chemical & Material Sciences (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Mathematical Physics (AREA)

- Theoretical Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Crystallography & Structural Chemistry (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Hall/Mr Elements (AREA)

- Mram Or Spin Memory Techniques (AREA)

- Semiconductor Memories (AREA)

Abstract

【解決手段】TMRタイプのMRAMは、選択用トランジスタTR、第1の接続孔23、第1の配線(書込みワード線RWL)、第1の層間絶縁層21及び第1の配線RWLを覆う第2の層間絶縁層25、第2の層間絶縁層25上に形成されたTRM素子30、第3の層間絶縁層26上に形成された第2の配線(ビット線)、及び、第2の層間絶縁層25に設けられ、第1の接続孔23と接続された第2の接続孔52を有し、TRM素子30の他端の延在部37の端面は第2の接続孔52と接している。

【選択図】 図8

Description

【発明の属する技術分野】

本発明は、不揮発性磁気メモリ装置及びその製造方法に関し、より詳しくは、TMR(Tunnel Magnetoresistance)タイプのMRAM(Magnetic Random Access Memory)と呼ばれる不揮発性磁気メモリ装置及びその製造方法に関する。

【0002】

【従来の技術】

情報通信機器、特に携帯端末等の個人用小型機器の飛躍的な普及に伴い、これらを構成するメモリやロジック等の各種半導体装置には、高集積化、高速化、低電力化等、一層の高性能化が要請されている。特に不揮発性メモリは、ユビキタス時代に必要不可欠であると考えられている。電源の消耗やトラブル、サーバーとネットワークとが何らかの障害により切断された場合でも、不揮発性メモリによって重要な情報を保存、保護することができる。また、最近の携帯機器は不要の回路ブロックをスタンバイ状態とし、出来る限り消費電力を抑えるように設計されているが、高速のワークメモリと大容量ストレージメモリを兼ねることができる不揮発性メモリが実現できれば、消費電力とメモリの無駄を無くすことができる。また、電源を投入すると瞬時に起動できる「インスタント・オン」機能も、高速、且つ、大容量の不揮発性メモリが実現できれば可能となる。

【0003】

不揮発性メモリとして、半導体材料を用いたフラッシュメモリや、強誘電体材料を用いた強誘電体型不揮発性半導体メモリ(FERAM,Ferroelectric Random Access Memory)等を挙げることができる。しかしながら、フラッシュメモリは、書込み速度がマイクロ秒のオーダーであり、書込み速度が遅いという欠点がある。一方、FERAMにおいては、書換え可能回数が1012〜1014であり、SRAMやDRAMをFERAMに置き換えるにはFERAMの書換え可能回数が十分とは云えず、また、強誘電体層の微細加工が難しいという問題が指摘されている。

【0004】

これらの欠点を有さない不揮発性メモリとして、MRAM(Magnetic Random Access Memory)と呼ばれる不揮発性磁気メモリ装置が注目されている。初期のMRAMは、GMR(Giant magnetoresistance)効果を用いたスピンバルブをベースにしたものであった。しかし、負荷のメモリセル抵抗が10〜100Ωと低いため、読み出し時のビット当たりの消費電力が大きく、大容量化が難しいという欠点があった。

【0005】

一方、TMR(Tunnel Magnetoresistance)効果を用いたMRAMは、開発初期においては、抵抗変化率が室温で1〜2%程度しかなかったが、近年、20%近くの抵抗変化率が得られるようになり、TMR効果を用いたMRAMに注目が集まっている。TMRタイプのMRAMは、構造が単純で、スケーリングも容易であり、また、磁気モーメントの回転により記録を行うために、書換え可能回数が大である。更には、アクセス時間についても非常に高速であることが予想され、既に100MHzで動作可能であると云われている。

【0006】

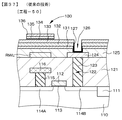

従来のTMRタイプのMRAM(以下、単に、MRAMと呼ぶ)の模式的な一部断面図を、図40に示す。このMRAMは、MOS型FETから成る選択用トランジスタTRと、トンネル磁気抵抗素子130から構成されている。

【0007】

トンネル磁気抵抗素子130は、第1の強磁性体層、トンネル絶縁膜134、第2の強磁性体層の積層構造を有する。第1の強磁性体層は、より具体的には、例えば、下から反強磁性体層132と磁化固定層133(固着層とも呼ばれる)との2層構成を有し、これらの2層の間に働く交換相互作用によって強い一方向の磁気異方性を有する。磁化方向が比較的容易に回転する第2の強磁性体層は、自由層あるいは記録層135とも呼ばれる。トンネル絶縁膜134は、記録層135と磁化固定層133との間の磁気的結合を切ると共に、トンネル電流を流すための役割を担う。MRAMとMRAMを接続するビット線BLは、第3の層間絶縁層128上に形成されている。ビット線BLと記録層135との間に設けられたトップコート膜136は、ビット線BLを構成する原子と記録層135を構成する原子の相互拡散の防止、接触抵抗の低減、及び、記録層135の酸化防止を担っている。図中、参照番号131は、反強磁性体層132と第2の層間絶縁層125との間に形成されたバリア層を示す。

【0008】

更には、トンネル磁気抵抗素子130の下方には、第2の層間絶縁層125を介して書込みワード線RWLが配置されている。尚、書込みワード線RWLの延びる方向(第1の方向)とビット線BLの延びる方向(第2の方向)とは、通常、直交している。

【0009】

一方、選択用トランジスタTRは、素子分離領域111によって囲まれたシリコン半導体基板110の部分に形成されており、第1の層間絶縁層121によって覆われている。そして、一方のソース/ドレイン領域114Bは、タングステンプラグから成る第1の接続孔123、ランディングパッド124、第2の接続孔127を介して、バリア層131、反強磁性体層132及び磁化固定層133に接続されている。即ち、第2の接続孔127は、バリア層131、反強磁性体層132及び磁化固定層133の延在部から構成されている。また、他方のソース/ドレイン領域114Aは、コンタクトホール115を介してセンス線116に接続されている。図中、参照番号112はゲート電極を示し、参照番号113はゲート絶縁膜を示す。

【0010】

MRAMアレイにあっては、ビット線BL及び書込みワード線RWLから成る格子の交点にMRAMが配置されている。

【0011】

このような構成のMRAMへのデータの書込みにおいては、ビット線BL及び書込みワード線RWLに電流を流し、その結果形成される合成磁界によって第2の強磁性体層(記録層135)の磁化の方向を変えることで、第2の強磁性体層(記録層135)に「1」又は「0」を記録する。

【0012】

一方、データの読出しは、選択用トランジスタTRをオン状態とし、ビット線BLに電流を流し、磁気抵抗効果によるトンネル電流変化をセンス線116にて検出することにより行う。記録層135と磁化固定層133の磁化方向が等しい場合、低抵抗となり(この状態を例えば「0」とする)、記録層135と磁化固定層133の磁化方向が反平行の場合、高抵抗となる(この状態を例えば「1」とする)。

【0013】

図40に示した従来のMRAMの製造方法の概要を、半導体基板等の模式的な一部断面図である図34の(A)、(B)、図35〜図40を参照して、以下、説明する。

【0014】

[工程−10]

先ず、周知の方法にて、選択用トランジスタTRとして機能するMOS型FETをシリコン半導体基板から成る半導体基板110に形成する。次いで、全面に第1の層間絶縁層の下層を形成した後、ソース/ドレイン領域114Aの上方の第1の層間絶縁層の下層にリソグラフィ技術及びRIE法に基づき開口部を形成し、次いで、開口部内を含む第1の層間絶縁層の下層上に、不純物がドーピングされたポリシリコン層をCVD法にて形成する。次いで、第1の層間絶縁層の下層上のポリシリコン層をパターニングすることで、第1の層間絶縁層の下層上にセンス線116を形成することができる。センス線116とソース/ドレイン領域114Aとは、第1の層間絶縁層の下層に形成されたコンタクトホール115を介して接続されている。その後、全面に第1の層間絶縁層の上層を形成する。尚、第1の層間絶縁層の下層と第1の層間絶縁層の上層を纏めて、以下、単に、第1の層間絶縁層121と呼ぶ。

【0015】

[工程−20]

その後、ソース/ドレイン領域114Bの上方の第1の層間絶縁層121に第1の開口部122をRIE法にて形成した後、選択用トランジスタTRのソース/ドレイン領域114Bに接続された第1の接続孔123を第1の開口部122内に形成する。

【0016】

その後、第1の層間絶縁層121上に、書込みワード線RWLを形成し、同時に、第1の接続孔123の頂面にランディングパッド124を形成する。その後、全面に第2の層間絶縁層125を形成する。こうして、図34の(A)に示す構造を得ることができる。

【0017】

[工程−30]

その後、第2の層間絶縁層125上にリソグラフィ技術に基づき、ランディングパッド124の上方に開口141が形成されたレジスト層140を形成する(図34の(B)参照)。次いで、レジスト層140をマスクとして、第2の層間絶縁層125をエッチングして、第2の層間絶縁層に第2の開口部126を形成した後、アッシング技術に基づきレジスト層140を除去する。こうして、図35に示す構造を得ることができる。次いで、良好なるコンタクトを取るため、第2の開口部126の底部に露出したランディングパッド124に対してアルゴンスパッタリング処理を施す。

【0018】

[工程−40]

その後、第2の開口部126内を含む全面に、スパッタリング法にて、バリア層131、反強磁性体層132、磁化固定層133、トンネル絶縁膜134、記録層135、及び、トップコート膜136を、順次、成膜する。第2の開口部126の側壁及び底面にも、バリア層131からトップコート膜136までを堆積させる。こうして、図36に示す構造を得ることができる。

【0019】

[工程−50]

次いで、リソグラフィ技術及びRIE法に基づき、トップコート膜136、記録層135、及び、トンネル絶縁膜134をパターニングすることで、磁化固定層133、バリア層131及び反強磁性体層132が残され、更には、バリア層131、反強磁性体層132及び磁化固定層133の延在部から構成された第2の接続孔127を得ることができる。こうして、図37に示す構造を得ることができる。

【0020】

[工程−60]

その後、磁化固定層133、反強磁性体層132及びバリア層131をパターニングし(図38参照)、全面に第3の層間絶縁層128を形成した後、第3の層間絶縁層128をCMP法にて平坦化し、トップコート膜136を露出させる(図39参照)。次いで、第3の層間絶縁層128上に、トップコート膜136と接続され、第1の方向と直交する第2の方向(図面の左右方向)に延びるビット線BLを形成する(図40参照)。尚、この際、周辺回路の配線(図示せず)、ボンディングパッド領域(図示せず)も併せて形成する。更に、全面にプラズマCVD法にてシリコン窒素膜(図示せず)を堆積し、ボンディングパッド部(図示せず)をシリコン窒素膜に開口して、MRAMの製造工程を完了させる。

【0021】

【発明が解決しようとする課題】

上述したとおり、高速・高集積化が容易という長所を有するMRAMではあるが、上述した従来のプロセスは以下に説明する問題点を有する。

【0022】

トンネル磁気抵抗素子130の下地である第2の層間絶縁層125には、数オングストローム以下の非常に高い平坦性が要求される。トンネル磁気抵抗素子130の記録層135や磁化固定層133における磁化方向は、トンネル磁気抵抗素子130の表面に平行でなければならない。然るに、第2の層間絶縁層125の表面に凹凸が存在すると、記録層135や磁化固定層133が凹凸状態となり、記録層135や磁化固定層133における磁化方向に垂直成分が発生し、トンネル磁気抵抗素子130の特性が劣化してしまうし、あるいは又、トンネル磁気抵抗素子130の特性におけるばらつきが拡大する。更には、第2の層間絶縁層125の表面に凹凸が存在すると、1nm程度と非常に薄いトンネル絶縁膜134の膜厚にもばらつきが生じ、トンネル磁気抵抗素子130の特性にばらつきが発生する。

【0023】

上述の[工程−30]において、レジスト層140を第2の層間絶縁層125上から除去する際、第2の層間絶縁層125には凹凸が生成する。更には、ランディングパッド124のアルゴンスパッタリング処理によっても、第2の層間絶縁層125には凹凸が生成する。この第2の層間絶縁層125の表面が荒れた状態を模式的に図35に示す。

【0024】

また、第2の接続孔127は、バリア層131、反強磁性体層132及び磁化固定層133の延在部から構成されている。トンネル磁気抵抗素子130を構成する各層は膜厚が薄く、各層を形成するためのスパッタリング装置は、高精度で、しかも、平坦、且つ、膜厚ばらつきを抑えるような仕様になっており、スパッタリングも室温で行われる。それ故、第2の開口部126のカバレッジが通常のスパッタリング装置を用いた場合よりも悪く、磁化固定層133、反強磁性体層132及びバリア層131に段切れが発生し易いといった問題もある。

【0025】

従って、本発明の目的は、トンネル磁気抵抗素子を構成する各種の層の平坦化を確実に達成でき、しかも、トンネル磁気抵抗素子と選択用トランジスタとを電気的に接続する接続孔に高い信頼性を付与し得る構造を有する不揮発性磁気メモリ装置、及び、その製造方法を提供することにある。

【0026】

【課題を解決するための手段】

上記の目的を達成するための本発明の不揮発性磁気メモリ装置(より具体的には、TMRタイプのMRAM)は、

(a)半導体基板に形成された選択用トランジスタ、

(b)選択用トランジスタを覆う第1の層間絶縁層、

(c)第1の層間絶縁層に設けられた第1の開口部内に形成され、選択用トランジスタと接続された第1の接続孔、

(d)第1の層間絶縁層上に形成され、第1の方向に延びる第1の配線、

(e)第1の層間絶縁層及び第1の配線を覆う第2の層間絶縁層、

(f)第2の層間絶縁層上に形成され、トンネル絶縁膜が強磁性体層で挟まれて成るトンネル磁気抵抗素子、

(g)トンネル磁気抵抗素子及び第2の層間絶縁層を覆う第3の層間絶縁層、(h)第3の層間絶縁層上に形成され、トンネル磁気抵抗素子の一端と電気的に接続され、第1の方向と異なる(例えば、直交する)第2の方向に延びる第2の配線、及び、

(i)第2の層間絶縁層に設けられた第2の開口部内に形成され、第1の接続孔と接続された第2の接続孔、

を有する不揮発性磁気メモリ装置であって、

トンネル磁気抵抗素子の他端の延在部の端面が第2の接続孔と接していることを特徴とする。

【0027】

本発明の不揮発性磁気メモリ装置において、第2の配線はトンネル磁気抵抗素子の一端と電気的に接続されているが、このような構成には、第2の配線が、トンネル磁気抵抗素子の一端と間接的に接続されている形態が包含される。

【0028】

上記の目的を達成するための本発明の第1の態様に係る不揮発性磁気メモリ装置(より具体的には、TMRタイプのMRAM)の製造方法は、本発明の不揮発性磁気メモリ装置を製造するための方法であり、

(A)半導体基板に選択用トランジスタを形成する工程と、

(B)全面に第1の層間絶縁層を形成する工程と、

(C)第1の層間絶縁層に第1の開口部を設け、該第1の開口部内に、選択用トランジスタと接続された第1の接続孔を形成する工程と、

(D)第1の方向に延びる第1の配線を、第1の層間絶縁層上に形成する工程と、

(E)全面に第2の層間絶縁層を形成する工程と、

(F)第2の層間絶縁層上に、少なくとも、第1の強磁性体層、トンネル絶縁膜、第2の強磁性体層から成る積層構造を形成する工程と、

(G)第1の接続孔の上方に位置する積層構造及び第2の層間絶縁層の部分に第2の開口部を形成する工程と、

(H)第2の開口部内を含む全面に導電体層を形成する工程と、

(I)導電体層、第2の強磁性体層及びトンネル絶縁膜をパターニングし、以て、第2の開口部内に第1の接続孔に接続された第2の接続孔を得る工程と、

(J)第1の強磁性体層をパターニングし、以て、トンネル絶縁膜が第1及び第2の強磁性体層で挟まれて成るトンネル磁気抵抗素子を得、併せて、第2の接続孔と端面が接した第1の強磁性体層の延在部を得る工程と、

(K)全面に第3の層間絶縁層を形成する工程と、

(L)第3の層間絶縁層上に、第2の強磁性体層と電気的に接続され、第1の方向と異なる(例えば、直交する)第2の方向に延びる第2の配線を形成する工程、

から成ることを特徴とする。

【0029】

本発明の第1の態様に係る不揮発性磁気メモリ装置の製造方法にあっては、第1の強磁性体層が、後述するように、例えば、下から反強磁性体層と磁化固定層から構成されている場合、前記工程(I)において、導電体層、第2の強磁性体層及びトンネル絶縁膜に加えて、磁化固定層をパターニングしてもよく、この場合には、前記工程(J)において、第1の強磁性体層をパターニングするが、具体的には、反強磁性体層をパターニングし、第2の接続孔と端面が接した第1の強磁性体層の延在部(より具体的には、反強磁性体層の延在部)を得ることができる。

【0030】

上記の目的を達成するための本発明の第2の態様に係る不揮発性磁気メモリ装置(より具体的には、TMRタイプのMRAM)の製造方法は、本発明の不揮発性磁気メモリ装置を製造するための方法であり、

(A)半導体基板に選択用トランジスタを形成する工程と、

(B)全面に第1の層間絶縁層を形成する工程と、

(C)第1の層間絶縁層に第1の開口部を設け、該第1の開口部内に、選択用トランジスタと接続された第1の接続孔を形成する工程と、

(D)第1の方向に延びる第1の配線を、第1の層間絶縁層上に形成する工程と、

(E)全面に第2の層間絶縁層を形成する工程と、

(F)第2の層間絶縁層上に、少なくとも、第1の強磁性体層、トンネル絶縁膜、第2の強磁性体層から成る積層構造を形成する工程と、

(G)第2の強磁性体層及びトンネル絶縁膜をパターニングする工程と、

(H)第1の接続孔の上方に位置する第1の強磁性体層及び第2の層間絶縁層の部分に第2の開口部を形成する工程と、

(I)第2の開口部内を含む全面に導電体層を形成する工程と、

(J)導電体層をパターニングし、以て、第2の開口部内に第1の接続孔に接続された第2の接続孔を形成する工程と、

(K)第1の強磁性体層をパターニングし、以て、トンネル絶縁膜が第1及び第2の強磁性体層で挟まれて成るトンネル磁気抵抗素子を得る工程と、

(L)全面に第3の層間絶縁層を形成する工程と、

(M)第3の層間絶縁層上に、第2の強磁性体層と電気的に接続され、第1の方向と異なる(例えば、直交する)第2の方向に延びる第2の配線を形成する工程、

から成ることを特徴とする。

【0031】

本発明の第2の態様に係る不揮発性磁気メモリ装置の製造方法にあっては、第1の強磁性体層が、後述するように、例えば、下から反強磁性体層と磁化固定層から構成されている場合、前記工程(G)において、第2の強磁性体層及びトンネル絶縁膜に加えて、磁化固定層をパターニングしてもよく、この場合には、前記工程(H)において、具体的には、第1の接続孔の上方に位置する反強磁性体層及び第2の層間絶縁層の部分に第2の開口部を形成し、前記工程(K)において、第1の強磁性体層をパターニングするが、具体的には、反強磁性体層をパターニングする。これによって、第2の接続孔と端面が接した第1の強磁性体層の延在部(より具体的には、反強磁性体層の延在部)を得ることができる。

【0032】

本発明の第2の態様に係る不揮発性磁気メモリ装置の製造方法にあっては、

前記工程(G)に引き続き、第1の強磁性体層をパターニングし、以て、トンネル絶縁膜が第1及び第2の強磁性体層で挟まれて成るトンネル磁気抵抗素子を得、且つ、第1の強磁性体層の延在部を得る工程を含み、

前記工程(H)においては、第1の接続孔の上方に位置する第1の強磁性体層の延在部及び第2の層間絶縁層の部分に第2の開口部を形成し、

前記工程(J)に引き続き、前記工程(K)を省略して、工程(L)を実行する構成とすることもできる。

【0033】

尚、このような不揮発性磁気メモリ装置の製造方法を、便宜上、本発明の第3の態様に係る不揮発性磁気メモリ装置の製造方法と呼ぶ。

【0034】

本発明の第1の態様〜第3の態様に係る不揮発性磁気メモリ装置の製造方法にあっては、第2の配線は第2の強磁性体層と電気的に接続されているが、このような構成には、第2の配線が、第2の強磁性体層と間接的に接続されている形態が包含される。

【0035】

本発明の不揮発性磁気メモリ装置、本発明の第1の態様〜第3の態様に係る不揮発性磁気メモリ装置の製造方法(以下、これらを総称して、単に、本発明と呼ぶ場合がある)において、第1の強磁性体層は、より具体的には、例えば、下から反強磁性体層と磁化固定層(固着層とも呼ばれる)との2層構成を有していることが好ましく、これによって、これらの2層の間に働く交換相互作用によって強い一方向の磁気異方性を有することができる。磁化方向が比較的容易に回転する第2の強磁性体層は、自由層あるいは記録層とも呼ばれる。トンネル絶縁膜は、第2の強磁性体層(記録層)と磁化固定層との間の磁気的結合を切ると共に、トンネル電流を流すための役割を担う。

【0036】

磁化固定層(固着層)及び第2の強磁性体層(記録層、自由層)は、例えば、遷移金属磁性元素、具体的には、ニッケル(Ni)、鉄(Fe)又はコバルト(Co)から構成された強磁性体、あるいはこれらの合金(例えば、Co−Fe、Co−Fe−Ni、Ni−Fe等)を主成分とする強磁性体から構成することができる。また、所謂ハーフメタリック強磁性体材料や、CoFe−Bといったアモルファス強磁性体材料を用いることもできる。反強磁性体層を構成する材料として、例えば、鉄−マンガン合金、ニッケル−マンガン合金、白金−マンガン合金、イリジウム−マンガン合金、ロジウム−マンガン合金、コバルト酸化物、ニッケル酸化物を挙げることができる。これらの層は、例えば、スパッタリング法、イオンビーム堆積法、真空蒸着法に例示される物理的気相成長法(PVD法)、ALD(Atomic Layer Deposition)法に代表されるCVD法にて形成することができる。

【0037】

トンネル絶縁膜を構成する絶縁材料として、アルミニウム酸化物(AlOX)、アルミニウム窒化物(AlN)、マグネシウム酸化物(MgO)、マグネシウム窒化物、シリコン酸化物、シリコン窒化物を挙げることができ、更には、Ge、NiO、CdOX、HfO2、Ta2O5、BN、ZnSを挙げることができる。トンネル絶縁膜は、例えば、スパッタリング法にて形成された金属膜を酸化若しくは窒化することにより得ることができる。より具体的には、トンネル絶縁膜を構成する絶縁材料としてアルミニウム酸化物(AlOX)を用いる場合、例えば、スパッタリング法にて形成されたアルミニウムを大気中で酸化する方法、スパッタリング法にて形成されたアルミニウムをプラズマ酸化する方法、スパッタリング法にて形成されたアルミニウムをIPCプラズマで酸化する方法、スパッタリング法にて形成されたアルミニウムを酸素中で自然酸化する方法、スパッタリング法にて形成されたアルミニウムを酸素ラジカルで酸化する方法、スパッタリング法にて形成されたアルミニウムを酸素中で自然酸化させるときに紫外線を照射する方法、アルミニウムを反応性スパッタリング法にて成膜する方法、酸化アルミニウムをスパッタリング法にて成膜する方法を例示することができる。あるいは又、トンネル絶縁膜をALD法によって形成することができる。

【0038】

第1の配線(書込みワード線)あるいは第2の配線(ビット線)は、例えば、アルミニウム、Al−Cu等のアルミニウム系合金、銅(Cu)から成り、例えば、スパッタリング法に例示されるPVD法や、化学的気相成長法(CVD法)、電解メッキ法に代表されるメッキ法にて形成することができる。また、導電体層は、例えば、アルミニウム、Al−Cu等のアルミニウム系合金、銅(Cu)、Ta、TaN、Ti、TiN、W、WN、ルテニウム(Ru)から成り、例えば、スパッタリング法に例示されるPVD法や、CVD法、メッキ法にて形成することができる。第2の接続孔は、この導電体層から構成されている。

【0039】

第1の接続孔は、不純物がドーピングされたポリシリコンや、タングステン、Ti、Pt、Pd、Cu、TiW、TiNW、WSi2、MoSi2等の高融点金属や金属シリサイドから構成することができ、CVD法や、スパッタリング法に例示されるPVD法に基づき形成することができる。

【0040】

積層構造のパターニングや選択的な除去は、例えば、反応性イオンエッチング(RIE)法やイオンミリング法にて行うことができる。また、場合によっては、所謂リフトオフ法にてパターニングを行うこともできる。

【0041】

選択用トランジスタは、例えば、周知のMIS型FETやMOS型FET、バイポーラトランジスタから構成することができる。

【0042】

各種の層間絶縁層を構成する材料として、酸化シリコン(SiO2)、窒化シリコン(SiN)、SiON、SOG、NSG、BPSG、PSG、BSG、FSG、SiOC、SiC、有機膜(所謂Low−k材料)、あるいは、LTO、Al2O3を例示することができる。

【0043】

本発明の第1の態様に係る不揮発性磁気メモリ装置の製造方法においては、工程(F)の後に工程(G)を実行するので、第2の層間絶縁層の表面に凹凸が生成することを確実に防止することができる。また、工程(H)及び工程(I)において第2の接続孔を形成するので、トンネル磁気抵抗素子と選択用トランジスタとを電気的に接続する第2の接続孔に高い信頼性を与えることができる。

【0044】

本発明の第2の態様あるいは第3の態様に係る不揮発性磁気メモリ装置の製造方法においては、工程(F)の後に工程(H)を実行するので、第2の層間絶縁層の表面に凹凸が生成することを確実に防止することができる。また、工程(I)及び工程(J)において第2の接続孔を形成するので、トンネル磁気抵抗素子と選択用トランジスタとを電気的に接続する第2の接続孔に高い信頼性を与えることができる。

【0045】

【発明の実施の形態】

以下、図面を参照して、発明の実施の形態(以下、実施の形態と略称する)に基づき本発明を説明する。

【0046】

(実施の形態1)

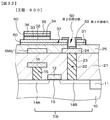

実施の形態1は、本発明の不揮発性磁気メモリ装置(以下、MRAMと称する)、及び、本発明の第1の態様に係るMRAMの製造方法に関する。実施の形態1のTMRタイプのMRAMの模式的な一部断面図を図8に示す。

【0047】

このMRAMは、選択用トランジスタTR、第1の層間絶縁層21、第1の接続孔23、第1の配線(書込みワード線RWL)、第2の層間絶縁層25、トンネル磁気抵抗素子30、第3の層間絶縁層26、第2の配線(ビット線BL)、及び、第2の接続孔52を有する。

【0048】

ここで、MOS型FETから成る選択用トランジスタTRは、シリコン半導体基板から成る半導体基板10に形成されている。より具体的には、選択用トランジスタTRは、素子分離領域11に囲まれた活性領域内に形成され、ゲート電極12、ゲート絶縁膜13、ソース/ドレイン領域14A,14Bから構成されている。例えばSiO2及びBPSGから成る第1の層間絶縁層21は、選択用トランジスタTRを覆っている。タングステンプラグから成る第1の接続孔23は、第1の層間絶縁層21に設けられた第1の開口部22内に形成されており、選択用トランジスタTRの一方のソース/ドレイン領域14Bと接続されている。第1の接続孔23は、更に、第1の層間絶縁層21上に形成されたランディングパッド24と接続されている。第1の配線(書込みワード線RWL)は銅(Cu)から成り、第2の層間絶縁層25上に形成され、第1の方向(図面の紙面垂直方向)に延びている。SiO2から成る第2の層間絶縁層25は、第1の層間絶縁層21及び書込みワード線RWLを覆っている。尚、選択用トランジスタTRの他方のソース/ドレイン領域14Aは、コンタクトホール15を介してセンス線16に接続されている。

【0049】

トンネル磁気抵抗素子30は、第2の層間絶縁層25上に形成され、下から、第1の強磁性体層、AlOXから成るトンネル絶縁膜34、Ni−Fe合金から成る第2の強磁性体層35(自由層あるいは記録層とも呼ばれる)の積層構造を有する。第1の強磁性体層は、より具体的には、下から、Fe−Mn合金から成る反強磁性体層32、Ni−Fe合金から成る磁化固定層33の2層構成を有する。この磁化固定層33は、反強磁性体層32との交換結合によって、磁化の方向がピニング(pinning)される。外部印加磁場によって、第2の強磁性体層(記録層)35の磁化の方向は、磁化固定層33に対して平行又は反平行に変えられる。反強磁性体層32と第2の層間絶縁層25との間には、窒化チタン、タンタル若しくは窒化タンタルから成るバリア層31が設けられている。尚、参照番号36は、バリア層31と同じ材料から成るトップコート膜である。トップコート膜36は、ビット線BLを構成する原子と第2の強磁性体層(記録層)35を構成する原子の相互拡散の防止、接触抵抗の低減、及び、第2の強磁性体層(記録層)35の酸化防止を担っている。

【0050】

SiO2から成る第3の層間絶縁層26は、トンネル磁気抵抗素子30、第2の層間絶縁層25、並びに、磁化固定層33、反強磁性体層32及びバリア層31の延在部37を覆っている。また、第2の配線であるビット線BLは、第3の層間絶縁層25上に形成され、トンネル磁気抵抗素子30の一端(より具体的には、第2の強磁性体層(記録層)35)と電気的に接続され、第1の方向と異なる(具体的には直交する)第2の方向(図面の左右方向)に延びている。

【0051】

Taから成る第2の接続孔52は、第2の層間絶縁層25に設けられた第2の開口部50内に形成され、第1の接続孔23と接続されている。より具体的には、第2の接続孔52は、ランディングパッド24と接している。第2の接続孔52の頂部はトップコート膜36上に形成されている。

【0052】

そして、トンネル磁気抵抗素子の他端の延在部37(より具体的には、第2の層間絶縁層25上を延在する磁化固定層33、反強磁性体層32及びバリア層31の延在部)の端面は、第2の接続孔52と接している。

【0053】

実施の形態1、あるいは、後述する実施の形態2〜実施の形態6におけるMRAMの動作、アレイ構成は、従来のMRAMの動作(書込み動作、読出し動作)、アレイ構成と基本的に同じである。

【0054】

以下、半導体基板10等の模式的な一部断面図である図1〜図8を参照して、実施の形態1のMRAMの製造方法を説明する。

【0055】

[工程−100]

先ず、選択用トランジスタTRとして機能するMOS型FETをシリコン半導体基板から成る半導体基板10に形成する。そのために、例えばトレンチ構造を有する素子分離領域11を公知の方法に基づき形成する。尚、素子分離領域は、LOCOS構造を有していてもよいし、LOCOS構造とトレンチ構造の組合せとしてもよい。その後、半導体基板10の表面を例えばパイロジェニック法により酸化し、ゲート絶縁膜13を形成する。次いで、不純物がドーピングされたポリシリコン層をCVD法にて全面に形成した後、ポリシリコン層をパターニングし、ゲート電極12を形成する。尚、ゲート電極12をポリシリコン層から構成する代わりに、ポリサイドや金属シリサイドから構成することもできる。次に、半導体基板10にイオン注入を行い、LDD構造(図示せず)を形成する。その後、全面にCVD法にてSiO2層を形成した後、このSiO2層をエッチバックすることによって、ゲート電極12の側面にゲートサイドウオール(図示せず)を形成する。次いで、半導体基板10にイオン注入を施した後、イオン注入された不純物の活性化アニール処理を行うことによって、ソース/ドレイン領域14A,14Bを形成する。

【0056】

[工程−105]

次いで、全面にSiO2から成る第1の層間絶縁層の下層をCVD法にて形成した後、化学的/機械的研磨法(CMP法)にて第1の層間絶縁層の下層を研磨する。その後、ソース/ドレイン領域14Aの上方の第1の層間絶縁層の下層にリソグラフィ技術及びRIE法に基づき開口部を形成し、次いで、開口部内を含む第1の層間絶縁層の下層上に、不純物がドーピングされたポリシリコン層をCVD法にて形成する。次いで、第1の層間絶縁層の下層上のポリシリコン層をパターニングすることで、第1の層間絶縁層の下層上にセンス線16を形成することができる。センス線16とソース/ドレイン領域14Aとは、第1の層間絶縁層の下層に形成されたコンタクトホール15を介して接続されている。その後、BPSGから成る第1の層間絶縁層の上層をCVD法にて全面に形成する。尚、BPSGから成る第1の層間絶縁層の上層の形成後、窒素ガス雰囲気中で例えば900゜C×20分間、第1の層間絶縁層の上層をリフローさせることが好ましい。更には、必要に応じて、例えばCMP法にて第1の層間絶縁層の上層の頂面を化学的及び機械的に研磨し、第1の層間絶縁層の上層を平坦化したり、レジストエッチバック法によって第1の層間絶縁層の上層を平坦化することが望ましい。尚、第1の層間絶縁層の下層と第1の層間絶縁層の上層を纏めて、以下、単に、第1の層間絶縁層21と呼ぶ。

【0057】

[工程−110]

その後、ソース/ドレイン領域14Bの上方の第1の層間絶縁層21に第1の開口部22をRIE法にて形成した後、選択用トランジスタTRのソース/ドレイン領域14Bに接続された第1の接続孔23を第1の開口部22内に形成する。第1の接続孔23の頂面は第1の層間絶縁層21の表面と略同じ平面に存在している。例えば、ブランケットタングステンCVD法にて第1の開口部22をタングステンプラグで埋め込み、第1の接続孔23を形成することができる。尚、タングステンにて第1の開口部22を埋め込む前に、Ti層及びTiN層を順に例えばマグネトロンスパッタリング法にて第1の開口部22内を含む第1の層間絶縁層21の上に形成することが好ましい。ここで、Ti層及びTiN層を形成する理由は、オーミックな低コンタクト抵抗を得ること、ブランケットタングステンCVD法における半導体基板10の損傷発生の防止、タングステンの密着性向上のためである。図面においては、Ti層及びTiN層の図示は省略している。第1の層間絶縁層21上のタングステン層、TiN層、Ti層は、CMP法にて除去してもよい。また、タングステンの代わりに、不純物がドーピングされたポリシリコンを用いることもできる。

【0058】

[工程−115]

その後、第1の層間絶縁層21上に、Cu層をスパッタリング法にて成膜し、このCu層をパターニングすることによって、第1の配線(書込みワード線RWL)及びランディングパッド24を形成する。

【0059】

尚、第1の配線(書込みワード線RWL)及びランディングパッド24を、所謂ダマシン法にて形成してもよい。即ち、第1の層間絶縁層21上に絶縁膜を形成し、第1の配線(書込みワード線RWL)及びランディングパッド24を形成すべき絶縁膜の部分に凹部を形成する。その後、厚さ20nmのTa膜、厚さ0.1μmの銅膜を、それぞれ、スパッタリング法にて成膜した後、銅メッキを行い、凹部をCu層で埋め込み、次いで、絶縁膜上のCu層、銅膜、Ta膜を、例えば、CMP法にて除去する。

【0060】

[工程−120]

その後、例えば、第1の配線(書込みワード線RWL)上において厚さが50nmとなるように、全面に、CVD法にてSiO2から成る第2の層間絶縁層25を形成する(図1参照)。この状態においては、第2の層間絶縁層25の表面は十分に平滑である。尚、必要に応じて、例えばCMP法にて第2の層間絶縁層25の平坦化処理を行ってもよい。

【0061】

[工程−125]

その後、第2の層間絶縁層25上に、少なくとも、第1の強磁性体層、トンネル絶縁膜34及び第2の強磁性体層(記録層)35から成る積層構造を形成する。

【0062】

具体的には、バリア層31、反強磁性体層32、磁化固定層33、トンネル絶縁膜34、第2の強磁性体層(記録層)35、バリア層31と同じ材料から成るトップコート膜36を、順次、PVD法で成膜する。こうして、図2に示す構造を得ることができる。トンネル絶縁膜34は、例えば、AlOXから構成されている。トンネル絶縁膜34は、膜厚が0.5nm〜5nmと非常に薄いため、ALD法によって形成し、あるいは又、スパッタリング法にてアルミニウム薄膜を成膜した後、アルミニウム薄膜をプラズマ酸化することで形成することが好ましいが、このような形成方法に限定するものではない。

【0063】

[工程−130]

次いで、リソグラフィ技術に基づき、ランディングパッド24の上方に開口41が設けられたレジスト層40をトップコート膜36上に形成する(図3参照)。その後、第1の接続孔23の上方に位置する積層構造(バリア層31からトップコート膜36までの積層構造)及び第2の層間絶縁層25の部分にRIE法にて第2の開口部50を形成した後、アッシング技術に基づきレジスト層40を除去する。こうして、図4に示す構造を得ることができる。その後、必要に応じて、第2の開口部50の底部に露出したランディングパッド24に対してアルゴンスパッタリング処理を行う。

【0064】

[工程−135]

その後、第2の開口部50内を含む全面に、Taから成る厚さ50nmの導電体層51をスパッタリング法にて形成する(図5参照)。尚、導電体層51は、例えばCVD法にて形成することもできる。

【0065】

[工程−140]

次に、リソグラフィ技術及びRIE法に基づき、導電体層51、トップコート膜36、第2の強磁性体層(記録層)35及びトンネル絶縁膜34をパターニングする。こうして、第2の開口部50内に第1の接続孔23(より具体的には、ランディングパッド24)に接続された第2の接続孔52を得ることができる(図6参照)。尚、エッチングの終点がトンネル絶縁膜34となるように、RIE条件を設定する。エッチングガスとして、Cl2、BCl3等のハロゲンの混合ガス、又は、COにNH3を添加したガス系等を用いることができる。第2の強磁性体層(記録層)35とトンネル絶縁膜34のエッチング選択比が10以上となる条件(第2の強磁性体層35のエッチング速度/トンネル絶縁膜34のエッチング速度=10/1)とするか、あるいは又、エッチング速度を落として薄いトンネル絶縁膜34中でエッチングを止めるように、エッチング条件を設定することが重要である。磁化固定層33が厚さ方向に部分的にエッチングされると、磁化固定層33の平面形状にばらつきが生じる結果、トンネル磁気抵抗素子30の特性にばらつきが発生する虞がある。

【0066】

[工程−145]

その後、第1の強磁性体層(磁化固定層33及び反強磁性体層32)、更には、バリア層31をパターニングする。これによって、トンネル絶縁膜34が第1及び第2の強磁性体層32,33,35で挟まれて成るトンネル磁気抵抗素子30を得ることができ、併せて、第2の接続孔52と端面が接した第1の強磁性体層の延在部37(磁化固定層33及び反強磁性体層32の延在部、更には、バリア層31の延在部)を得ることができる。こうして、図7に示す構造を得ることができる。

【0067】

[工程−150]

次いで、全面に、SiO2から成る厚さ0.3μmの第3の層間絶縁層26をプラズマCVD法にて形成した後、第3の層間絶縁層26をCMP法にて平坦化する。

【0068】

[工程−155]

その後、リソグラフィ技術及びエッチング技術に基づき、第3の層間絶縁層26に開口を設け、この開口内を含む第3の層間絶縁層26上に、第2の強磁性体層(記録層)35と電気的に接続され(より具体的には、導電体層51に接続され)、第1の方向と直交する第2の方向(図面の左右方向)に延びる第2の配線(ビット線BL)を、スパッタリング法、リソグラフィ技術及びエッチング技術に基づき形成する(図8参照)。尚、この際、周辺回路の配線(図示せず)、ボンディングパッド領域(図示せず)も併せて形成する。

【0069】

[工程−160]

更に、全面にプラズマCVD法にてシリコン窒素膜(図示せず)を堆積し、ボンディングパッド部(図示せず)をシリコン窒素膜に開口して、MRAMの製造工程を完了させる。

【0070】

実施の形態1においては、[工程−130]において、レジスト層40の除去の際、第2の層間絶縁層25は積層構造によって覆われているので、第2の層間絶縁層25の表面に凹凸が生成することは無い。また、必要に応じて、第2の開口部50の底部に露出したランディングパッド24に対してアルゴンスパッタリング処理を行ったときにも、第2の層間絶縁層25の表面に凹凸が生成することは無い。更には、[工程−135]及び[工程−140]において第2の接続孔52を設けるので、高い信頼性を有する第2の接続孔52を得ることができる。

【0071】

(実施の形態2)

実施の形態2は、実施の形態1のMRAMの製造方法の変形である。実施の形態2においては、前記[工程−140]と同様の工程において、導電体層51、トップコート膜36、第2の強磁性体層(記録層)35及びトンネル絶縁膜34に加えて、磁化固定層33をパターニングする。そして、前記[工程−145]と同様の工程において、第1の強磁性体層をパターニングするが、具体的には、反強磁性体層32をパターニングする。これによって、第2の接続孔52と端面が接した第1の強磁性体層の延在部37(より具体的には、反強磁性体層32の延在部)を得ることができる。

【0072】

以下、半導体基板10等の模式的な一部断面図である図9〜図11を参照して、実施の形態2のMRAMの製造方法を説明する。

【0073】

[工程−200]

先ず、実施の形態1の[工程−100]〜[工程−135]までの工程と同様の工程を実行する。

【0074】

[工程−205]

次いで、実施の形態1の[工程−140]と同様の工程において、導電体層51、トップコート膜36、第2の強磁性体層(記録層)35及びトンネル絶縁膜34に加えて、更には、磁化固定層33をパターニングする。こうして、図9に示す構造を得ることができる。尚、露出した反強磁性体層32の表面に磁化固定層33が局所的に存在しないように、磁化固定層33を若干オーバーエッチングすることが重要である。露出した反強磁性体層32の表面に磁化固定層33が局所的に存在すると、トンネル磁気抵抗素子30の特性にばらつきが発生する虞がある。

【0075】

[工程−210]

その後、実施の形態1の[工程−145]と同様の工程において、第1の強磁性体層を構成する反強磁性体層32、更には、バリア層31をパターニングする。こうして、第2の接続孔52と端面が接した第1の強磁性体層の延在部37(具体的には、反強磁性体層32、更には、バリア層31の延在部)を得ることができる(図10参照)。

【0076】

[工程−215]

次いで、実施の形態1の[工程−150]〜[工程−160]と同様の工程を実行することで、MRAMを完成させる。尚、[工程−155]と同様が完了した時点の構造を、図11に示す。

【0077】

(実施の形態3)

実施の形態3は、本発明のMRAM、及び、本発明の第2の態様に係るMRAMの製造方法に関する。実施の形態3のTMRタイプのMRAMの模式的な一部断面図を図17に示すが、トップコート膜36、第2の強磁性体層(記録層)35及びトンネル絶縁膜34の側面にサイドウオール60が形成されている点、第2の接続孔52の頂部が磁化固定層33上に形成されている点を除き、実質的に、実施の形態1にて説明したMRAMと同様の構造を有する。

【0078】

以下、半導体基板10等の模式的な一部断面図である図12〜図17を参照して、実施の形態3のMRAMの製造方法を説明する。

【0079】

[工程−300]

半導体基板10に選択用トランジスタTRを形成する工程、全面に第1の層間絶縁層21を形成する工程、第1の層間絶縁層21に第1の開口部22を設け、この第1の開口部22内に選択用トランジスタTRと接続された第1の接続孔23を形成する工程、第1の方向に延びる第1の配線(書込みワード線RWL)を第1の層間絶縁層21上に形成する工程、全面に第2の層間絶縁層25を形成する工程、第2の層間絶縁層25上に、少なくとも、第1の強磁性体層32,33、トンネル絶縁膜34、第2の強磁性体層(記録層)35から成る積層構造を形成する工程は、実質的に、実施の形態1の[工程−100]〜[工程−125]と同様とすることができるので、詳細な説明は省略する。

【0080】

[工程−305]

次いで、リソグラフィ技術に基づき、レジスト層(図示せず)をトップコート膜36上に形成した後、トップコート膜36、第2の強磁性体層(記録層)35及びトンネル絶縁膜34をパターニングし、アッシング技術に基づきレジスト層を除去する。こうして、図12に示す構造を得ることができる。尚、エッチングの終点がトンネル絶縁膜34となるように、RIE条件を設定する。エッチングガスとして、Cl2、BCl3等のハロゲンの混合ガス、又は、COにNH3を添加したガス系等を用いることができる。第2の強磁性体層(記録層)35とトンネル絶縁膜34のエッチング選択比が10以上となる条件(第2の強磁性体層35のエッチング速度/トンネル絶縁膜34のエッチング速度=10/1)とするか、あるいは又、エッチング速度を落として薄いトンネル絶縁膜34中でエッチングを止めるように、エッチング条件を設定することが重要である。磁化固定層33が厚さ方向に部分的にエッチングされると、磁化固定層33の平面形状にばらつきが生じる結果、トンネル磁気抵抗素子30の特性にばらつきが発生する虞がある。

【0081】

[工程−310]

その後、全面に、例えばSiN膜を成膜し、このSiN膜をエッチバックすることによって、トップコート膜36、第2の強磁性体層(記録層)35及びトンネル絶縁膜34の側面にサイドウオール60を形成する(図13参照)。サイドウオール60を形成することで、後の工程において、導電体層51を形成したとき、各層が導電体層51によって短絡することを確実に防止することができる。

【0082】

[工程−315]

次に、第1の接続孔23の上方(より具体的には、ランディングパッド24の上方)に位置する第1の強磁性体層(磁化固定層33及び反強磁性体層32)並びに第2の層間絶縁層25の部分に第2の開口部50を形成する。具体的には、リソグラフィ技術に基づき、ランディングパッド24の上方に開口が設けられたレジスト層(図示せず)を全面に形成する。その後、第1の接続孔23の上方に位置する第1の強磁性体層(磁化固定層33及び反強磁性体層32)、バリア層31、並びに、第2の層間絶縁層25の部分にRIE法にて第2の開口部50を形成した後、アッシング技術に基づきレジスト層を除去する。こうして、図14に示す構造を得ることができる。その後、必要に応じて、第2の開口部50の底部に露出したランディングパッド24に対してアルゴンスパッタリング処理を行う。

【0083】

[工程−320]

その後、第2の開口部50内を含む全面に(より具体的には、第2の開口部50内を含む磁化固定層33上に)、Taから成る厚さ50nmの導電体層51をスパッタリング法にて形成する。尚、導電体層51は、例えばCVD法にて形成することもできる。

【0084】

[工程−325]

次に、リソグラフィ技術及びエッチング技術に基づき、導電体層51をパターニングする。こうして、第2の開口部50内に、第1の接続孔23に接続された(より具体的には、ランディングパッド24と接する)第2の接続孔52を形成することができる(図15参照)。

【0085】

[工程−330]

その後、第1の強磁性体層(磁化固定層33及び反強磁性体層32)、更には、バリア層31をパターニングする。これによって、トンネル絶縁膜34が第1及び第2の強磁性体層32,33,35で挟まれて成るトンネル磁気抵抗素子30を得ることができ、併せて、第2の接続孔52と端面が接した第1の強磁性体層の延在部37(磁化固定層33及び反強磁性体層32の延在部、更には、バリア層31の延在部)を得ることができる。こうして、図16に示す構造を得ることができる。

【0086】

[工程−335]

その後、全面に第3の層間絶縁層26を形成する工程、第3の層間絶縁層26上に第2の強磁性体層(記録層)35と電気的に接続され、第1の方向と異なる第2の方向に延びる第2の配線(ビット線BL)を形成する工程を実行する。具体的には、実施の形態1の[工程−150]〜[工程−160]と同様の工程を実行すればよい。尚、[工程−155]と同様が完了した時点の構造を、図17に示す。

【0087】

実施の形態3においても、[工程−315]において、レジスト層の除去の際、第2の層間絶縁層25は積層構造によって覆われているので、第2の層間絶縁層25の表面に凹凸が生成することは無い。また、必要に応じて、第2の開口部50の底部に露出したランディングパッド24に対してアルゴンスパッタリング処理を行ったときにも、第2の層間絶縁層25の表面に凹凸が生成することは無い。更には、[工程−320]及び[工程−325]において第2の接続孔52を設けるので、高い信頼性を有する第2の接続孔52を得ることができる。

【0088】

(実施の形態4)

実施の形態4は、実施の形態3のMRAMの製造方法の変形である。

【0089】

実施の形態4においては、前記[工程−305]と同様の工程において、トップコート膜36、第2の強磁性体層(記録層)35及びトンネル絶縁膜34に加えて、磁化固定層33をパターニングする。そして、前記[工程−315]と同様の工程において、第1の接続孔23の上方に位置する反強磁性体層32及び第2の層間絶縁層25の部分に第2の開口部50を形成する。更には、前記[工程−320]と同様の工程においては、第2の開口部50内を含む反強磁性体層32上に導電体層51を形成し、前記[工程−325]と同様の工程において、第1の強磁性体層をパターニングするが、具体的には、反強磁性体層32をパターニングする。これによって、第2の接続孔52と端面が接した第1の強磁性体層の延在部37(より具体的には、反強磁性体層32の延在部)を得ることができる。尚、第2の接続孔52の頂部が反強磁性体層32上に形成されている点が、実施の形態3にて説明したMRAMと異なっている。

【0090】

以下、半導体基板10等の模式的な一部断面図である図18〜図23を参照して、実施の形態4のMRAMの製造方法を説明する。

【0091】

[工程−400]

先ず、実施の形態3の[工程−300]と同様の工程を実行する。

【0092】

[工程−405]

次いで、実施の形態3の[工程−305]と同様の工程において、トップコート膜36、第2の強磁性体層(記録層)35及びトンネル絶縁膜34に加えて、磁化固定層33をパターニングする。こうして、図18に示す構造を得ることができる。尚、露出した反強磁性体層32の表面に磁化固定層33が局所的に存在しないように、磁化固定層33を若干オーバーエッチングすることが重要である。露出した反強磁性体層32の表面に磁化固定層33が局所的に存在すると、トンネル磁気抵抗素子30の特性にばらつきが発生する虞がある。

【0093】

[工程−410]

その後、実施の形態3の[工程−310]と同様の工程において、トップコート膜36、第2の強磁性体層(記録層)35、トンネル絶縁膜34及び磁化固定層33の側面にサイドウオール60を形成する(図19参照)。

【0094】

[工程−415]

次に、第1の接続孔23の上方(より具体的には、ランディングパッド24の上方)に位置する第1の強磁性体層(より具体的には、反強磁性体層32)並びに第2の層間絶縁層25の部分に第2の開口部50を形成する。具体的には、リソグラフィ技術に基づき、ランディングパッド24の上方に開口が設けられたレジスト層(図示せず)を全面に形成する。その後、第1の接続孔23の上方に位置する第1の強磁性体層(具体的には、反強磁性体層32)、バリア層31及び第2の層間絶縁層25の部分にRIE法にて第2の開口部50を形成した後、アッシング技術に基づきレジスト層を除去する。こうして、図20に示す構造を得ることができる。その後、必要に応じて、第2の開口部50の底部に露出したランディングパッド24に対してアルゴンスパッタリング処理を行う。

【0095】

[工程−420]

その後、第2の開口部50内を含む全面に(より具体的には、第2の開口部50内を含む反強磁性体層32上に)、Taから成る厚さ50nmの導電体層51をスパッタリング法にて形成する。尚、導電体層51は、例えばCVD法にて形成することもできる。

【0096】

[工程−425]

次に、リソグラフィ技術及びエッチング技術に基づき、導電体層51をパターニングする。こうして、第2の開口部50内に、第1の接続孔23に接続された(より具体的には、ランディングパッド24と接する)第2の接続孔52を形成することができる(図21参照)。

【0097】

[工程−430]

その後、第1の強磁性体層(具体的には、反強磁性体層32)、更には、バリア層31をパターニングする。これによって、トンネル絶縁膜34が第1及び第2の強磁性体層32,33,35で挟まれて成るトンネル磁気抵抗素子30を得ることができ、併せて、第2の接続孔52と端面が接した第1の強磁性体層の延在部37(具体的には、反強磁性体層32の延在部、更には、バリア層31の延在部)を得ることができる。こうして、図22に示す構造を得ることができる。

【0098】

[工程−435]

その後、全面に第3の層間絶縁層26を形成する工程、第3の層間絶縁層26上に第2の強磁性体層(記録層)35と電気的に接続され、第1の方向と異なる第2の方向に延びる第2の配線(ビット線BL)を形成する工程を実行する。具体的には、実施の形態1の[工程−150]〜[工程−160]と同様の工程を実行すればよい。尚、[工程−155]と同様が完了した時点の構造を、図23に示す。

【0099】

(実施の形態5)

実施の形態5も、実施の形態3のMRAMの製造方法の変形であり、本発明の第3の態様に係るMRAMの製造方法に関する。

【0100】

実施の形態5のTMRタイプのMRAMの模式的な一部断面図を図28に示すが、トップコート膜36、第2の強磁性体層(記録層)35、トンネル絶縁膜34、磁化固定層33、反強磁性体層32及びバリア層31の側面にサイドウオール60が形成されている点、第2の接続孔52の頂部が磁化固定層33上に形成されている点を除き、実質的に、実施の形態1にて説明したMRAMと同様の構造を有する。

【0101】

実施の形態5においては、前記[工程−305]と同様の工程に引き続き、第1の強磁性体層をパターニングし、以て、トンネル絶縁膜34が第1及び第2の強磁性体層32,33,35で挟まれて成るトンネル磁気抵抗素子30を得、且つ、第1の強磁性体層の延在部37を得る工程を含む。また、前記[工程−315]と同様の工程においては、第1の接続孔23の上方に位置する第1の強磁性体層の延在部37及び第2の層間絶縁層25の部分に第2の開口部50を形成し、前記[工程−325]と同様の工程に引き続き、前記[工程−330]と同様の工程を省略して、[工程−335]と同様の工程以降の工程を実行する。実施の形態5のMRAMの製造方法にあっては、第2の接続孔52と端面が接した第1の強磁性体層の延在部37(より具体的には、磁化固定層33及び反強磁性体層32の延在部)を得ることができる。

【0102】

以下、半導体基板10等の模式的な一部断面図である図24〜図28を参照して、実施の形態5のMRAMの製造方法を説明する。

【0103】

[工程−500]

先ず、実施の形態3の[工程−300]と同様の工程を実行する。

【0104】

[工程−505]

次いで、実施の形態3の[工程−305]と同様の工程を実行する。

【0105】

[工程−510]

その後、リソグラフィ技術及びRIE法に基づき、第1の強磁性体層をパターニングし、以て、トンネル絶縁膜34が第1及び第2の強磁性体層32,33,35で挟まれて成るトンネル磁気抵抗素子30を得る。同時に、第1の強磁性体層の延在部37(具体的には、磁化固定層33、反強磁性体層32及びバリア層31の延在部)を得る。こうして、図24に示す構造を得ることができる。

【0106】

[工程−515]

次に、実施の形態3の[工程−310]と同様の工程を実行することで、トップコート膜36、第2の強磁性体層(記録層)35、トンネル絶縁膜34、磁化固定層33、反強磁性体層32及びバリア層31の側面にサイドウオール60を形成する(図25参照)。

【0107】

[工程−520]

その後、第1の接続孔23の上方(より具体的には、ランディングパッド24の上方)に位置する第1の強磁性体層(より具体的には、磁化固定層33及び反強磁性体層32)並びに第2の層間絶縁層25の部分に第2の開口部50を形成する。具体的には、リソグラフィ技術に基づき、ランディングパッド24の上方に開口が設けられたレジスト層(図示せず)を全面に形成する。その後、第1の接続孔23の上方に位置する第1の強磁性体層(磁化固定層33及び反強磁性体層32)、バリア層31並びに第2の層間絶縁層25の部分にRIE法にて第2の開口部50を形成した後、アッシング技術に基づきレジスト層を除去する。こうして、図26に示す構造を得ることができる。その後、必要に応じて、第2の開口部50の底部に露出したランディングパッド24に対してアルゴンスパッタリング処理を行う。

【0108】

[工程−525]

その後、第2の開口部50内を含む全面に(より具体的には、第2の開口部50内を含む磁化固定層33上に)、Taから成る厚さ50nmの導電体層51をスパッタリング法にて形成する。尚、導電体層51は、例えばCVD法にて形成することもできる。

【0109】

[工程−530]

次に、リソグラフィ技術及びエッチング技術に基づき、導電体層51をパターニングする。こうして、第2の開口部50内に、第1の接続孔23に接続された(より具体的には、ランディングパッド24と接する)第2の接続孔52を形成することができる(図27参照)。

【0110】

[工程−535]

その後、全面に第3の層間絶縁層26を形成する工程、第3の層間絶縁層26上に第2の強磁性体層(記録層)35と電気的に接続され、第1の方向と異なる第2の方向に延びる第2の配線(ビット線BL)を形成する工程を実行する。具体的には、実施の形態1の[工程−150]〜[工程−160]と同様の工程を実行すればよい。尚、[工程−155]と同様が完了した時点の構造を、図28に示す。

【0111】

実施の形態5においても、[工程−520]において第2の開口部50を形成する際、第2の層間絶縁層25は第1の強磁性体層によって覆われているので、第2の層間絶縁層25の表面に凹凸が生成することは無い。また、必要に応じて、第2の開口部50の底部に露出したランディングパッド24に対してアルゴンスパッタリング処理を行ったときにも、第2の層間絶縁層25の表面に凹凸が生成することは無い。更には、[工程−525]及び[工程−530]において第2の接続孔52を設けるので、高い信頼性を有する第2の接続孔52を得ることができる。

【0112】

(実施の形態6)

実施の形態6は、実施の形態5のMRAMの製造方法の変形である。

【0113】

実施の形態6においては、前記[工程−505]と同様の工程において、トップコート膜36、第2の強磁性体層(記録層)35及びトンネル絶縁膜34に加えて、磁化固定層33をパターニングする。そして、前記[工程−520]と同様の工程において、第1の接続孔23の上方に位置する反強磁性体層32及び第2の層間絶縁層25の部分に第2の開口部50を形成する。更には、前記[工程−525]と同様の工程においては、第2の開口部50内を含む反強磁性体層32上に導電体層51を形成する。実施の形態6のMRAMの製造方法にあっては、第2の接続孔52と端面が接した第1の強磁性体層の延在部37(より具体的には、反強磁性体層32の延在部)を得ることができる。尚、第2の接続孔52の頂部が反強磁性体層32上に形成されている点が、実施の形態5にて説明したMRAMと異なっている。

【0114】

以下、半導体基板10等の模式的な一部断面図である図29〜図33を参照して、実施の形態6のMRAMの製造方法を説明する。

【0115】

[工程−600]

先ず、実施の形態3の[工程−300]と同様の工程を実行する。

【0116】

[工程−605]

次いで、実施の形態3の[工程−305]と同様の工程において、トップコート膜36、第2の強磁性体層(記録層)35及びトンネル絶縁膜34に加えて、磁化固定層33をパターニングする。尚、露出した反強磁性体層32の表面に磁化固定層33が局所的に存在しないように、磁化固定層33を若干オーバーエッチングすることが重要である。露出した反強磁性体層32の表面に磁化固定層33が局所的に存在すると、トンネル磁気抵抗素子30の特性にばらつきが発生する虞がある。

【0117】

[工程−610]

その後、リソグラフィ技術及びRIE法に基づき、第1の強磁性体層(より具体的には、磁化固定層33)をパターニングし、以て、トンネル絶縁膜34が第1及び第2の強磁性体層32,33,35で挟まれて成るトンネル磁気抵抗素子30を得る。同時に、第1の強磁性体層の延在部37(具体的には、反強磁性体層32及びバリア層31の延在部)を得る。こうして、図29に示す構造を得ることができる。

【0118】

[工程−615]

次に、実施の形態3の[工程−310]と同様の工程を実行することで、トップコート膜36、第2の強磁性体層(記録層)35、トンネル絶縁膜34、磁化固定層33、反強磁性体層32及びバリア層31の側面にサイドウオール60を形成する(図30参照)。

【0119】

[工程−620]

その後、第1の接続孔23の上方(より具体的には、ランディングパッド24の上方)に位置する第1の強磁性体層(より具体的には、反強磁性体層32)並びに第2の層間絶縁層25の部分に第2の開口部50を形成する。具体的には、リソグラフィ技術に基づき、ランディングパッド24の上方に開口が設けられたレジスト層(図示せず)を全面に形成する。その後、第1の接続孔23の上方に位置する第1の強磁性体層(具体的には、反強磁性体層32)、バリア層31並びに第2の層間絶縁層25の部分にRIE法にて第2の開口部50を形成した後、アッシング技術に基づきレジスト層を除去する。こうして、図31に示す構造を得ることができる。その後、必要に応じて、第2の開口部50の底部に露出したランディングパッド24に対してアルゴンスパッタリング処理を行う。

【0120】

[工程−625]

その後、第2の開口部50内を含む全面に(より具体的には、第2の開口部50内を含む反強磁性体層32上に)、Taから成る厚さ50nmの導電体層51をスパッタリング法にて形成する。尚、導電体層51は、例えばCVD法にて形成することもできる。

【0121】

[工程−630]

次に、リソグラフィ技術及びエッチング技術に基づき、導電体層51をパターニングする。こうして、第2の開口部50内に、第1の接続孔23に接続された(より具体的には、ランディングパッド24と接する)第2の接続孔52を形成することができる(図32参照)。

【0122】

[工程−635]

その後、全面に第3の層間絶縁層26を形成する工程、第3の層間絶縁層26上に第2の強磁性体層(記録層)35と電気的に接続され、第1の方向と異なる第2の方向に延びる第2の配線(ビット線BL)を形成する工程を実行する。具体的には、実施の形態1の[工程−150]〜[工程−160]と同様の工程を実行すればよい。尚、[工程−155]と同様が完了した時点の構造を、図33に示す。

【0123】

以上、本発明を、発明の実施の形態に基づき説明したが、本発明はこれらに限定されるものではない。発明の実施の形態にて説明した各層を構成する材料、各層を形成する方法、MRAMの構造等は例示であり、適宜変更することができる。

【0124】

トンネル絶縁膜34が第1及び第2の強磁性体層32,33,35で挟まれて成るトンネル磁気抵抗素子30を形成する際、トンネル磁気抵抗素子30の平面形状を、対向する2辺が第1の方向と平行な矩形としてもよいし、対向する2辺が第1の方向と平行な菱形や平行四辺形としてもよい。後者の場合、残りの対向する2辺が第2の方向と平行ではなくなり、第2の強磁性体層(記録層)35の磁化方向の反転を高速化することができる。

【0125】

【発明の効果】

本発明においては、トンネル磁気抵抗素子30の下地に相当する第2の層間絶縁層の表面は、積層構造を形成した後、実質的に何の処理も施されないが故に、第2の層間絶縁層の表面を非常に平坦な状態に保持することができる。また、トンネル磁気抵抗素子30の引き出し配線に相当する反強磁性体層32の延在部、あるいは、反強磁性体層32と磁化固定層33との延在部の端面と、第2の接続孔の側壁とが接触した構造を有するが故に、第2の開口部におけるカバレッジ部の段切れといった問題が発生することもなく、安定した低抵抗の第2の接続孔を得ることができる。以上の結果として、トンネル磁気抵抗素子の特性におけるばらつきを抑制することができるし、高い信頼性及び特性安定性を有する不揮発性磁気メモリ装置を製造することができる。

【図面の簡単な説明】

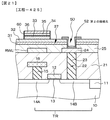

【図1】図1は、発明の実施の形態1のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図2】図2は、図1に引き続き、発明の実施の形態1のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図3】図3は、図2に引き続き、発明の実施の形態1のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図4】図4は、図3に引き続き、発明の実施の形態1のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図5】図5は、図4に引き続き、発明の実施の形態1のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図6】図6は、図5に引き続き、発明の実施の形態1のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図7】図7は、図6に引き続き、発明の実施の形態1のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図8】図8は、図7に引き続き、発明の実施の形態1のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

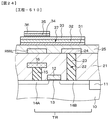

【図9】図9は、発明の実施の形態2のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図10】図10は、図9に引き続き、発明の実施の形態2のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図11】図11は、図10に引き続き、発明の実施の形態2のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

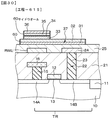

【図12】図12は、発明の実施の形態3のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図13】図13は、図12に引き続き、発明の実施の形態3のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図14】図14は、図13に引き続き、発明の実施の形態3のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図15】図15は、図14に引き続き、発明の実施の形態3のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図16】図16は、図15に引き続き、発明の実施の形態3のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図17】図17は、図16に引き続き、発明の実施の形態3のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

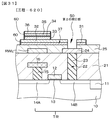

【図18】図18は、発明の実施の形態4のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図19】図19は、図18に引き続き、発明の実施の形態4のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図20】図20は、図19に引き続き、発明の実施の形態4のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図21】図21は、図20に引き続き、発明の実施の形態4のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図22】図22は、図21に引き続き、発明の実施の形態4のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図23】図23は、図22に引き続き、発明の実施の形態4のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図24】図24は、発明の実施の形態5のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図25】図25は、図24に引き続き、発明の実施の形態5のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図26】図26は、図25に引き続き、発明の実施の形態5のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図27】図27は、図26に引き続き、発明の実施の形態5のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図28】図28は、図27に引き続き、発明の実施の形態5のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図29】図29は、発明の実施の形態6のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図30】図30は、図29に引き続き、発明の実施の形態6のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図31】図31は、図30に引き続き、発明の実施の形態6のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図32】図32は、図31に引き続き、発明の実施の形態6のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図33】図33は、図32に引き続き、発明の実施の形態6のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図34】図34の(A)及び(B)は、従来のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図35】図35は、図34(B)に引き続き、従来のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図36】図36は、図35に引き続き、従来のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図37】図37は、図36に引き続き、従来のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図38】図38は、図37に引き続き、従来のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図39】図39は、図38に引き続き、従来のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【図40】図40は、図39に引き続き、従来のMRAMタイプの不揮発性磁気メモリ装置の製造方法を説明するための、半導体基板等の模式的な一部断面図である。

【符号の説明】

TR・・・選択用トランジスタ、RWL・・・第1の配線(書込みワード線)、BL・・・第2の配線(ビット線)、10・・・半導体基板、11・・・素子分離領域、12・・・ゲート電極、13・・・ゲート絶縁膜、14A,14B・・・ソース/ドレイン領域、15・・・コンタクトホール、16・・・センス線、21・・・第1の層間絶縁層、22・・・第1の開口部、23・・・第1の接続孔、24・・・ランディングパッド、25・・・第2の層間絶縁層、26・・・第3の層間絶縁層、30・・・トンネル磁気抵抗素子、31・・・バリア層、32・・・反強磁性体層、33・・・磁化固定層、34・・・トンネル絶縁膜、35・・・第2の強磁性体層(記録層)、36・・・トップコート膜、37・・・延在部、40・・・レジスト層、41・・・開口、50・・・第2の開口部、51・・・導電材料層、52・・・第2の接続孔、60・・・・・・サイドウオール

Claims (4)

- (a)半導体基板に形成された選択用トランジスタ、

(b)選択用トランジスタを覆う第1の層間絶縁層、

(c)第1の層間絶縁層に設けられた第1の開口部内に形成され、選択用トランジスタと接続された第1の接続孔、

(d)第1の層間絶縁層上に形成され、第1の方向に延びる第1の配線、

(e)第1の層間絶縁層及び第1の配線を覆う第2の層間絶縁層、

(f)第2の層間絶縁層上に形成され、トンネル絶縁膜が強磁性体層で挟まれて成るトンネル磁気抵抗素子、

(g)トンネル磁気抵抗素子及び第2の層間絶縁層を覆う第3の層間絶縁層、(h)第3の層間絶縁層上に形成され、トンネル磁気抵抗素子の一端と電気的に接続され、第1の方向と異なる第2の方向に延びる第2の配線、及び、

(i)第2の層間絶縁層に設けられた第2の開口部内に形成され、第1の接続孔と接続された第2の接続孔、

を有する不揮発性磁気メモリ装置であって、

トンネル磁気抵抗素子の他端の延在部の端面が第2の接続孔と接していることを特徴とする不揮発性磁気メモリ装置。 - (A)半導体基板に選択用トランジスタを形成する工程と、

(B)全面に第1の層間絶縁層を形成する工程と、

(C)第1の層間絶縁層に第1の開口部を設け、該第1の開口部内に、選択用トランジスタと接続された第1の接続孔を形成する工程と、

(D)第1の方向に延びる第1の配線を、第1の層間絶縁層上に形成する工程と、

(E)全面に第2の層間絶縁層を形成する工程と、

(F)第2の層間絶縁層上に、少なくとも、第1の強磁性体層、トンネル絶縁膜、第2の強磁性体層から成る積層構造を形成する工程と、

(G)第1の接続孔の上方に位置する積層構造及び第2の層間絶縁層の部分に第2の開口部を形成する工程と、

(H)第2の開口部内を含む全面に導電体層を形成する工程と、

(I)導電体層、第2の強磁性体層及びトンネル絶縁膜をパターニングし、以て、第2の開口部内に第1の接続孔に接続された第2の接続孔を得る工程と、

(J)第1の強磁性体層をパターニングし、以て、トンネル絶縁膜が第1及び第2の強磁性体層で挟まれて成るトンネル磁気抵抗素子を得、併せて、第2の接続孔と端面が接した第1の強磁性体層の延在部を得る工程と、

(K)全面に第3の層間絶縁層を形成する工程と、

(L)第3の層間絶縁層上に、第2の強磁性体層と電気的に接続され、第1の方向と異なる第2の方向に延びる第2の配線を形成する工程、

から成ることを特徴とする不揮発性磁気メモリ装置の製造方法。 - (A)半導体基板に選択用トランジスタを形成する工程と、

(B)全面に第1の層間絶縁層を形成する工程と、

(C)第1の層間絶縁層に第1の開口部を設け、該第1の開口部内に、選択用トランジスタと接続された第1の接続孔を形成する工程と、

(D)第1の方向に延びる第1の配線を、第1の層間絶縁層上に形成する工程と、

(E)全面に第2の層間絶縁層を形成する工程と、

(F)第2の層間絶縁層上に、少なくとも、第1の強磁性体層、トンネル絶縁膜、第2の強磁性体層から成る積層構造を形成する工程と、

(G)第2の強磁性体層及びトンネル絶縁膜をパターニングする工程と、

(H)第1の接続孔の上方に位置する第1の強磁性体層及び第2の層間絶縁層の部分に第2の開口部を形成する工程と、

(I)第2の開口部内を含む全面に導電体層を形成する工程と、

(J)導電体層をパターニングし、以て、第2の開口部内に第1の接続孔に接続された第2の接続孔を形成する工程と、

(K)第1の強磁性体層をパターニングし、以て、トンネル絶縁膜が第1及び第2の強磁性体層で挟まれて成るトンネル磁気抵抗素子を得る工程と、

(L)全面に第3の層間絶縁層を形成する工程と、

(M)第3の層間絶縁層上に、第2の強磁性体層と電気的に接続され、第1の方向と異なる第2の方向に延びる第2の配線を形成する工程、

から成ることを特徴とする不揮発性磁気メモリ装置の製造方法。 - 前記工程(G)に引き続き、第1の強磁性体層をパターニングし、以て、トンネル絶縁膜が第1及び第2の強磁性体層で挟まれて成るトンネル磁気抵抗素子を得、且つ、第1の強磁性体層の延在部を得る工程を含み、

前記工程(H)においては、第1の接続孔の上方に位置する第1の強磁性体層の延在部及び第2の層間絶縁層の部分に第2の開口部を形成し、

前記工程(J)に引き続き、前記工程(K)を省略して、工程(L)を実行することを特徴とする請求項3に記載の不揮発性磁気メモリ装置の製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003000486A JP2004214459A (ja) | 2003-01-06 | 2003-01-06 | 不揮発性磁気メモリ装置及びその製造方法 |

| TW092135571A TWI239008B (en) | 2003-01-06 | 2003-12-16 | Non-volatile magnetic memory and manufacturing method thereof |

| US10/750,263 US6982446B2 (en) | 2003-01-06 | 2003-12-31 | Nonvolatile magnetic memory device and manufacturing method thereof |

| US11/237,138 US7271010B2 (en) | 2003-01-06 | 2005-09-28 | Nonvolatile magnetic memory device and manufacturing method thereof |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003000486A JP2004214459A (ja) | 2003-01-06 | 2003-01-06 | 不揮発性磁気メモリ装置及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004214459A true JP2004214459A (ja) | 2004-07-29 |

| JP2004214459A5 JP2004214459A5 (ja) | 2005-03-17 |

Family

ID=32818781

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003000486A Abandoned JP2004214459A (ja) | 2003-01-06 | 2003-01-06 | 不揮発性磁気メモリ装置及びその製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US6982446B2 (ja) |

| JP (1) | JP2004214459A (ja) |

| TW (1) | TWI239008B (ja) |

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006086322A (ja) * | 2004-09-16 | 2006-03-30 | Renesas Technology Corp | 磁気抵抗記憶素子およびその製造方法 |

| JP2006165031A (ja) * | 2004-12-02 | 2006-06-22 | Ulvac Japan Ltd | トンネル接合素子の製造方法およびその製造装置 |

| WO2006070803A1 (ja) * | 2004-12-28 | 2006-07-06 | Nec Corporation | 磁気ランダムアクセスメモリ及びその製造方法 |

| KR100626390B1 (ko) | 2005-02-07 | 2006-09-20 | 삼성전자주식회사 | 자기 메모리 소자 및 그 형성 방법 |

| KR100761541B1 (ko) * | 2004-12-31 | 2007-09-27 | 매그나칩 반도체 유한회사 | 압력 센서의 제조 방법 |

| JP2008512875A (ja) * | 2004-09-09 | 2008-04-24 | ティーガル コーポレイション | ストップ−オン−アルミニウム処理を含むウェーハ処理のためのシステム及び方法 |

| JP2012160671A (ja) * | 2011-02-02 | 2012-08-23 | Toshiba Corp | 磁気ランダムアクセスメモリ及びその製造方法 |

| JP2014090109A (ja) * | 2012-10-31 | 2014-05-15 | Hitachi High-Technologies Corp | 磁気抵抗素子の製造方法 |

| US8941197B2 (en) | 2007-02-27 | 2015-01-27 | Kabushiki Kaisha Toshiba | Magnetic random access memory |

| JP2017157874A (ja) * | 2017-06-19 | 2017-09-07 | 株式会社日立ハイテクノロジーズ | 磁気抵抗素子の製造方法、及び磁気抵抗素子 |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4567963B2 (ja) * | 2003-12-05 | 2010-10-27 | ルネサスエレクトロニクス株式会社 | 半導体集積回路装置 |

| KR100657897B1 (ko) * | 2004-08-21 | 2006-12-14 | 삼성전자주식회사 | 전압 제어층을 포함하는 메모리 소자 |

| KR100719345B1 (ko) * | 2005-04-18 | 2007-05-17 | 삼성전자주식회사 | 자기 기억 장치의 형성 방법 |

| DE102005047482A1 (de) * | 2005-10-04 | 2007-04-12 | Infineon Technologies Ag | Magnetoresistives Sensormodul und Verfahren zum Herstellen desselben |

| US7608538B2 (en) * | 2007-01-05 | 2009-10-27 | International Business Machines Corporation | Formation of vertical devices by electroplating |

| JP4384196B2 (ja) * | 2007-03-26 | 2009-12-16 | 株式会社東芝 | スピンfet、磁気抵抗効果素子及びスピンメモリ |

| US7939188B2 (en) * | 2008-10-27 | 2011-05-10 | Seagate Technology Llc | Magnetic stack design |

| US9041146B2 (en) * | 2013-03-15 | 2015-05-26 | Intel Corporation | Logic chip including embedded magnetic tunnel junctions |

| KR102099191B1 (ko) | 2013-03-15 | 2020-05-15 | 인텔 코포레이션 | 내장된 자기 터널 접합을 포함하는 로직 칩 |

| US9373663B2 (en) * | 2013-09-20 | 2016-06-21 | Avalanche Technology, Inc. | Landing pad in peripheral circuit for magnetic random access memory (MRAM) |

| US10495771B2 (en) * | 2015-10-27 | 2019-12-03 | Schlumberger Technology Corporation | Method and system for processing dipole anisotropy |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000294743A (ja) | 1999-04-01 | 2000-10-20 | Matsushita Electronics Industry Corp | 強誘電体メモリ装置 |

| US6611405B1 (en) * | 1999-09-16 | 2003-08-26 | Kabushiki Kaisha Toshiba | Magnetoresistive element and magnetic memory device |

| US6473336B2 (en) * | 1999-12-16 | 2002-10-29 | Kabushiki Kaisha Toshiba | Magnetic memory device |

| JP2001298161A (ja) | 2000-04-12 | 2001-10-26 | Sony Corp | 不揮発性半導体記憶装置およびその製造方法 |

| JP4309075B2 (ja) * | 2000-07-27 | 2009-08-05 | 株式会社東芝 | 磁気記憶装置 |

| US6587370B2 (en) * | 2000-11-01 | 2003-07-01 | Canon Kabushiki Kaisha | Magnetic memory and information recording and reproducing method therefor |

| JP2002334574A (ja) | 2001-05-02 | 2002-11-22 | Canon Inc | 不揮発性メモリの駆動方法及び不揮発性メモリ |

| KR100442959B1 (ko) * | 2001-05-22 | 2004-08-04 | 주식회사 하이닉스반도체 | 마그네틱 램 및 그 형성방법 |

| KR100403313B1 (ko) * | 2001-05-22 | 2003-10-30 | 주식회사 하이닉스반도체 | 바이폴라 접합 트랜지스터를 이용한 마그네틱 램 및 그형성방법 |

| US7262064B2 (en) * | 2001-10-12 | 2007-08-28 | Sony Corporation | Magnetoresistive effect element, magnetic memory element magnetic memory device and manufacturing methods thereof |

| KR100457159B1 (ko) * | 2001-12-26 | 2004-11-16 | 주식회사 하이닉스반도체 | 마그네틱 램 |

| JP2004119478A (ja) * | 2002-09-24 | 2004-04-15 | Renesas Technology Corp | 半導体記憶装置、不揮発性記憶装置および磁気記憶装置 |

-

2003

- 2003-01-06 JP JP2003000486A patent/JP2004214459A/ja not_active Abandoned

- 2003-12-16 TW TW092135571A patent/TWI239008B/zh not_active IP Right Cessation

- 2003-12-31 US US10/750,263 patent/US6982446B2/en not_active Expired - Fee Related

-

2005

- 2005-09-28 US US11/237,138 patent/US7271010B2/en not_active Expired - Fee Related

Cited By (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008512875A (ja) * | 2004-09-09 | 2008-04-24 | ティーガル コーポレイション | ストップ−オン−アルミニウム処理を含むウェーハ処理のためのシステム及び方法 |

| JP2006086322A (ja) * | 2004-09-16 | 2006-03-30 | Renesas Technology Corp | 磁気抵抗記憶素子およびその製造方法 |

| JP2006165031A (ja) * | 2004-12-02 | 2006-06-22 | Ulvac Japan Ltd | トンネル接合素子の製造方法およびその製造装置 |

| JPWO2006070803A1 (ja) * | 2004-12-28 | 2008-06-12 | 日本電気株式会社 | 磁気ランダムアクセスメモリ及びその製造方法 |

| WO2006070803A1 (ja) * | 2004-12-28 | 2006-07-06 | Nec Corporation | 磁気ランダムアクセスメモリ及びその製造方法 |

| KR100761541B1 (ko) * | 2004-12-31 | 2007-09-27 | 매그나칩 반도체 유한회사 | 압력 센서의 제조 방법 |

| KR100626390B1 (ko) | 2005-02-07 | 2006-09-20 | 삼성전자주식회사 | 자기 메모리 소자 및 그 형성 방법 |

| US7645619B2 (en) | 2005-02-07 | 2010-01-12 | Samsung Electronics Co., Ltd. | Magnetic random access memory device and method of forming the same |

| US8941197B2 (en) | 2007-02-27 | 2015-01-27 | Kabushiki Kaisha Toshiba | Magnetic random access memory |

| US9263666B2 (en) | 2007-02-27 | 2016-02-16 | Kabushiki Kaisha Toshiba | Magnetic random access memory |

| JP2012160671A (ja) * | 2011-02-02 | 2012-08-23 | Toshiba Corp | 磁気ランダムアクセスメモリ及びその製造方法 |

| US9076720B2 (en) | 2011-02-02 | 2015-07-07 | Kabushiki Kaisha Toshiba | Magnetic random access memory and a method of fabricating the same |

| JP2014090109A (ja) * | 2012-10-31 | 2014-05-15 | Hitachi High-Technologies Corp | 磁気抵抗素子の製造方法 |

| JP2017157874A (ja) * | 2017-06-19 | 2017-09-07 | 株式会社日立ハイテクノロジーズ | 磁気抵抗素子の製造方法、及び磁気抵抗素子 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20060023561A1 (en) | 2006-02-02 |

| US7271010B2 (en) | 2007-09-18 |

| TW200426840A (en) | 2004-12-01 |

| TWI239008B (en) | 2005-09-01 |

| US20040157427A1 (en) | 2004-08-12 |

| US6982446B2 (en) | 2006-01-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7271010B2 (en) | Nonvolatile magnetic memory device and manufacturing method thereof | |

| JP4952725B2 (ja) | 不揮発性磁気メモリ装置 | |

| US7005715B2 (en) | Magnetic storage device and method of fabricating the same | |

| US20050270828A1 (en) | Magnetic memory device and manufacturing method thereof | |

| JP2003324187A (ja) | 磁気メモリ装置の製造方法および磁気メモリ装置 | |

| US6958503B2 (en) | Nonvolatile magnetic memory device | |

| EP1484767A2 (en) | Magnetic memory apparatus and method of manufacturing magnetic memory apparatus | |

| JP2008282940A (ja) | 磁気記憶装置の製造方法 | |

| JP4590862B2 (ja) | 磁気メモリ装置及びその製造方法 | |

| JP2009290050A (ja) | 磁気抵抗効果素子及びその製造方法 | |

| JP5277629B2 (ja) | 磁気抵抗効果を有するメモリ素子及びその製造方法、並びに、不揮発性磁気メモリ装置 | |

| TW202316580A (zh) | 半導體元件及其製作方法 | |

| JP2008021816A (ja) | 不揮発性磁気記憶装置の製造方法 | |

| JP2003218324A (ja) | 磁気記憶装置およびその製造方法 | |

| JP2003086773A (ja) | 磁気メモリ装置およびその製造方法 | |

| JP4678144B2 (ja) | フォトマスク | |

| JP2003282836A (ja) | 磁気メモリ装置およびその製造方法 | |

| JP2004235512A (ja) | 磁気記憶装置およびその製造方法 | |

| JP5327293B2 (ja) | 不揮発性磁気メモリ装置 | |

| JP2005243764A (ja) | 磁気記憶装置の製造方法 | |

| JP2005056976A (ja) | 磁気メモリ装置及びその製造方法 | |

| JP2005175374A (ja) | 磁気メモリ装置及びその製造方法 | |

| JP2006059869A (ja) | トグルモード書込型不揮発性磁気メモリ装置 | |

| JP4899377B2 (ja) | 不揮発性磁気記憶装置の製造方法 | |

| US20240365677A1 (en) | Semiconductor device and method of fabricating the same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040421 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040421 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060908 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20061003 |

|

| A762 | Written abandonment of application |

Free format text: JAPANESE INTERMEDIATE CODE: A762 Effective date: 20061017 |