-

Die

Erfindung betrifft ein Datenmodulationsgerät, ein Datenmodulationsverfahren,

ein Datendemodulationsgerät,

ein Datendemodulationsverfahren sowie ein Medium zur Bereitstellung

von Daten. Die Erfindung betrifft insbesondere ein Gerät und ein

Verfahren zum Modulieren von Daten für das Übertragen der Daten oder das

Aufzeichnen der Daten auf einem Aufzeichnungsmedium, ferner ein

Gerät und

ein Verfahren zum Demodulieren von Daten, die moduliert wurden,

sowie ein Medium für

die Benutzung bei der Übertragung

oder Aufzeichnung von Daten, die moduliert wurden.

-

Modulierte

Daten werden über

einen vorbestimmten Übertragungspfad übertragen

oder auf einem Aufzeichnungsmedium, z.B. einer Magnetplatte, einer

optischen Platte oder einer magneto-optischen Platte aufgezeichnet.

Eines dieser Datenmodulationsverfahren ist die Blockkodierung. Bei

der Blockkodierung wird eine Datenzeile in Blöcke oder Einheiten unterteilt,

die jeweils aus m × i

Bits bestehen. (Diese Dateneinheiten werden im folgenden als "Datenwörter" bezeichnet). Die

Datenwörter

werden nach einem geeigneten Kodiergesetz zu Codewörtern moduliert,

die jeweils aus n × i

Bits bestehen. Jedes Codewort hat eine feste Länge, wenn i den Wert Eins (1)

hat. Es hat eine variable Länge,

wenn der Wert i aus mehreren Werten ausgewählt werden kann. Das heißt, das

Codewort hat eine variable Länge,

wenn für

i einer der Werte aus dem Bereich von 1 bis imax (dem größten Wert

für i)

ausgewählt

wird. Der durch die Blockkodierung erzeugte Code ist ein variabler

Längencode

(d, k; m, n; r).

-

Der

Wert i wird als "Zwangslänge" bezeichnet, und

der Wert imax wird als "maximale" Zwangslänge r bezeichnet.

Der minimale Lauf d bezeichnet die kleinste Zahl von Einsen (1en),

die in einer Codereihe enthalten sein können. Der maximale Lauf k bezeichnet

die größte Zahl

von Einsen (1en), die in einer Codereihe enthalten sein können.

-

Um

variable Längencodes,

die in der oben beschriebenen Weise erzeugt werden, auf einer Compaktdisk,

einer Minidisk oder dgl. aufzuzeichnen, können die variablen Längencodes

einer NRZI-(Non Return to Zero Inverted)-Modulation unterzogen werden.

Bei der NRZI-Modulation wird der variable Längencode bei jeder Eins (1)

invertiert und bei jeder Null (0) nicht invertiert. Die der NRZI-Modulation

unterzogenen variablen Längencodes

(im folgenden als "Pegelcodes" bezeichnet) werden

auf der Platte aufgezeichnet.

-

Die

inverse NRZI-Modulation, bei der ein Pegelcode geändert wird,

wenn "1" in "0" invertiert wird oder "0" in "1" invertiert wird,

so daß er

zu einer Flanke wird, kann an variablen Längencodes durchgeführt werden. In

diesem Fall läßt sich

eine Codereihe gewinnen, die mit den originalen EFM-Codes oder RLL-(1-7)-Codes identisch

ist. Diese inversen NRZI-Codes werden als "Flankencodes" bezeichnet.

-

Das

minimale Intervall von invertierenden Pegelcodes sei Tmin, und das

maximale Intervall von invertierenden Pegelcodes sei Tmax. Um Daten

mit hoher Dichte in Richtung der Lineargeschwindigkeit aufzuzeichnen,

sollte das minimale Code-Invertierungsintervall Tmin lang sein.

Das heißt,

der minimale Lauf d sollte groß sein.

Um Taktsignale zu reproduzieren sollte das maximale Code-Invertierungsintervall

Tmax kurz sein. Mit anderen Worten, der maximale Lauf k sollte klein

sein. Im Hinblick hierauf werden verschiedene Datenmodulationsverfahren

vorgeschlagen.

-

Ein

Beispiel ist das als RLL (1-7) bekannte Datenmodulationsverfahren,

das für

die Aufzeichnung von Daten auf einer Magnetplatte, einer magneto-optischen

Platte oder dgl. benutzt wird. Der Parameter für dieses Datenmodulationsverfahren

ist (1,7; 2,3; 2). Das minimale Code-Invertierungsintervall Tmin

ist 2T oder (1+1)T. Dieses minimale Code-Invertierungsintervall

Tmin beträgt

1,33T Daten, d.h. (m/n) × Tmin

= (2/3) × 2.

Die als (k+1)T gegebene maximale Code-Invertierungsperiode Tmax

ist gleich 8 oder (7+1)T = 2/3 × 8T

Daten = 5,33T Daten. Die Breite Tw des Detektierungsfensters, die

als (m/n)T gegeben ist, ist gleich 0,67 (= 2/3)T Daten.

-

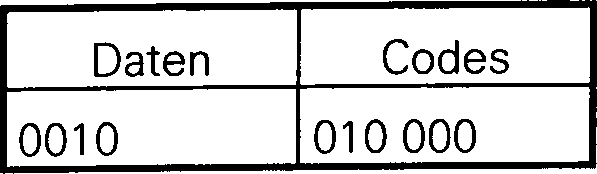

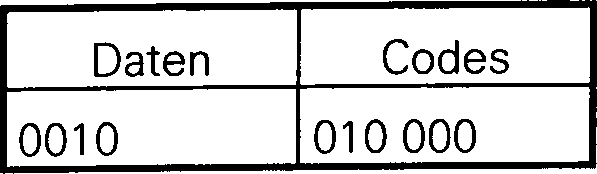

Die

Umwandlungstabelle für

RLL-(1-7)-Codes ist z.B. die folgende Tabelle 1: Tabelle

1: RLL(1,7; 2,3; 2)

-

Das

in der Umwandlungstabelle benutzte Symbol x ist gleich "1", wenn das nächste Kanalbit gleich "0" ist, und gleich "0",

wenn das nächste

Kanalbit gleich "1" ist. Die maximale

Zwangslänge

r ist gleich 2.

-

In

der Kanalbitreihe, die nach dem RLL-(1-7)-Verfahren moduliert wurde,

tritt in dem Intervall Tmin 2T am häufigsten auf, 3T tritt weniger

häufig

auf als 2T und 4T tritt weniger häufig auf als 3T. Wenn Flankendatenposten

wie 2T oder 3T mit großer

Häufigkeit

auftreten, hilft dies bei der Reproduktion der Taktsignale. Wenn 2T

kontinuierlich auftritt, besteht hingegen die Gefahr, daß seine

Aufzeichnungswellenform deformiert wird. (Die Wellenform des Ausgangssignals

von 2T ist klein und kann leicht durch Defokussierung oder tangentiales Kippen

beeinflußt

werden). Außerdem

besteht die Gefahr, daß kleinsten

Marken, die mit hoher linearer Dichte kontinuierlich aufgezeichnet

sind, durch äußere Störungen,

wie Rauschen, beeinflußt

werden, was in den reproduzierten Daten Fehler verursacht,.

-

Die

Anmelderin hat in der japanischen Patentanmeldung Nr. 9-133379 vorgeschlagen,

zu verhindern, daß Tmin

häufiger

als in einer vorgeschriebenen Anzahl auftritt. Die Umwandlungstabelle

für RLL-(1-7)-Codes für die Benutzung

bei diesem vorgeschlagenen Verfahren ist z.B. die folgende Tabelle

2.

-

Tabelle

2: RML(1,7; 2,3; 3)

-

Das

in dieser Umwandlungstabelle benutzte Symbol x ist gleich "1", wenn das nächste Kanalbit "0" ist, und gleich "0",

wenn das nächste

Kanalbit "1" ist Die maximale

Zwangslänge

r ist gleich 2.

-

Bei

der Umwandlung mit Hilfe der Tabelle 2 wird auf die nächsten vier

Datenposten Bezug genommen, wenn die Datenzeile den Wert "10" hat, und ein Code "100 000 010" zur Verhinderung

der Wiederholung des minimalen Laufs d ist dann gegeben, wenn die

Datenzeile mit sechs Bits gleich "100110" wird. Der minimale Lauf d kann in dem

durch diese Umwandlung gewonnenen Code höchstens sechs Mal wiederholt

werden.

-

Um

Daten auf einem Aufzeichnungsmedium aufzeichnen oder Daten in einer

speziellen Weise zu übertragen,

werden die Daten in Codes moduliert, die auf dem Medium aufgezeichnet

oder in der speziellen Weise übertragen

werden können.

Die modulierten Codes können

eine Gleichstromkomponente enthalten. Wenn dies der Fall ist, besteht

die Gefahr, daß verschiedene

Fehlersignale, wie das Spurfehlersignal oder die Servosteuerung

in einem Plattenlaufwerk sich ändern

oder Jitter enthalten. Deshalb sollten die modulierten Codes keine

Gleichstromkomponente enthalten.

-

Die

oben erwähnten

RLL-Codes mit variabler Länge,

in denen der minimale Lauf d gleich 1 ist (d = 1) und die Umwandlungsraten

m und n gleich 2 bzw. gleich 3 sind (m = 2, n = 3), werden keiner

digitalen Summenwert-Steuerung (DSV-Steuerung) unterzogen. Bei der

DSV-Steuerung wird

der Absolutwert der Gesamtsumme (DSV) der Codes verringert, wenn

die Kanalbitreihe NRZI-moduliert (d.h. in Pegelcodes umgewandelt) wird

und die "1"-Bits der Kette (Datensymbole),

d.h. +1-Codes, addiert werden, während

die "0"-Bits der Kette, d.h. –1-Codes

addiert werden. Der DSV kann dazu dienen, die Gleichstromkomponente

in der Codereihe abzuschätzen.

Die Verkleinerung des Absolutwerts des DSV bedeutet eine Verringerung

der Gleichstromkomponente in der Codereihe.

-

In

den meisten Fällen

werden 2 × (d+1)

Bits als DSV-Steuerbits verwendet. Falls d = 1, werden vier Bits,

d.h. 2 × (1+1)

Bits als DSV-Bits benutzt. In diesem Fall können der minimale Lauf und

der maximale Lauf beibehalten werden, und es kann eine perfekte

DSV-Steuerung erreicht werden, um Codes innerhalb gegebener Intervalle

zu invertieren und nicht zu invertieren.

-

Die

DSV-Steuerbits sind grundsätzlich

jedoch redundante Bits. Im Hinblick auf die Effizienz von invertierenden

Codes ist es deshalb wünschenswert,

die Zahl der DSV-Steuerbits so weit wie möglich zu reduzieren.

-

Alternativ

können

1 × (d+1)

Bits als DSV-Steuerbits benutzt werden. Wenn dies der Fall ist,

werden zwei DSV-Bits, d.h. 1 × (1+1)

Bits, benutzt. In diesem Fall kann ebenfalls eine perfekte DSV-Steuerung

erreicht werden, um innerhalb gegebener Intervalle Codes zu invertieren

und Codes nicht zu invertieren. Trotzdem wächst der maximale Lauf auf

(k+2), obwohl der minimale Lauf beibehalten werden kann. Der minimale

Lauf muß unbedingt

als aufgezeichneter Code gesichert werden, während der maximale Lauf als

solcher nicht gesichert werden muß. In einigen Fällen gibt

es Formate, in denen ein Muster, das den maximalen Lauf verletzt, als

Synchronisiersignal benutzt wird (EFM-plus der DVD hat einen maximalen

Lauf von 11T, der auf 14T vergrößert werden

kann, um ein spezifisches Format zu benutzen).

-

Eine

Tabelle von 1,7PP-(Parity preserve Prohibit rmtr)-Codes ist als

Tabelle verfügbar,

die eine effizientere DSV-Steuerung ermöglicht, während die Grundfunktion der

in Tabelle 2 dargestellten RML-Codes beibehalten wird. Die 1,7PP-Codes

sind modulierte Codes, in denen der minimale Lauf gleich 1 (d =

1) und der maximale Lauf gleich 7 (k = 7) ist. In jedem 1,7PP-Code

wird verhindert, daß der

minimale Lauf sich wiederholt, und den Elementen, die Datenwörtern und

Codewörtern

entsprechen, wird eine Regel zugeordnet.

-

Die

Umwandlungstabelle für

1,7PP-Codes, die von der Anmelderin in der japanischen Patentanmeldung

Nr. 10-150280 vorgeschlagen wird, ist z.B. die Folgende: Tabelle

3: 1,7PP(1,7; 2,3; 4)

-

In

der Tabelle 3 ist der minimale Lauf gleich 1 (d = 1) und der maximale

Lauf gleich 7 (k = 7). Unter den in dieser Umwandlungstabelle dargestellten

Elementen gibt es unsichere Codes. In Abhängigkeit von der der Datenzeile

unmittelbar vorangehenden Codewortreihe ist ein unsicherer Code

entweder "000" oder "101", wenn zwei Bits

der umzuwandelnden Datenzeile (11) sind. Falls ein Kanalbit der

unmittelbar vorangehenden Codewortreihe gleich "1" ist,

werden die zwei Bits (11) in "000" umgewandelt, um

den minimalen Lauf zu sichern. Falls ein Kanalbit der unmittelbar

vorangehenden Codewortreihe gleich "0" ist,

werden die zwei Bits in "101" umgewandelt, um

den maximalen Lauf zu sichern.

-

Die

Umwandlungstabelle von Tabelle 3 ist eine Tabelle mit variabler

Längenstruktur.

Das heißt,

ein Code, der mit der Zwangslänge

i = 1 umgewandelt werden soll, besteht aus drei Datenposten, also

weniger als den vier benötigten

Datenposten [2^(m × i)

= 2^(2 × 1)

= 4]. Das heißt

unter den umzuwandelnden Datenzeilen gibt es eine Datenzeile, die

nicht mit der Zwangslänge

i umgewandelt werden kann. Nach alledem muß für die Benutzung der Tabelle

3 als Umwandlungstabelle oder zur Umwandlung aller Datenzeilen die

Zwangslänge

i gleich 3 angewendet werden.

-

Die

Umwandlungstabelle von Tabelle 3 enthält Ersatzcodes, die die Zahl

der Wiederholungen des minimalen Laufs einschränken. Die Datenzeile (110 111)

wird z.B. durch "001

000 000" ersetzt,

wenn die nachfolgende Codewortreihe gleich "010" ist.

Falls die Codewortreihe eine andere als "010" ist,

wird die Datenzeile in "*0*010*0*" umgewandelt. Die

nach der Datenumwandlung gewonnene Codewortreihe ist bezüglich der Zahl

der Wiederholungen des minimalen Laufs begrenzt. Der minimale Lauf

kann höchstens

sechs Mal wiederholt werden.

-

Die

Umwandlungstabelle von Tabelle 2 basiert auf dem Umwandlungsgesetz,

bei dem dann, wenn die Zahl der "1

en" in den Elementen

einer Datenzeile und die Zahl der "1 en" in

einer umzuwandelnden Codewortreihe durch 2 geteilt wird, die Reste

einander gleich sind, nämlich

entweder "1" oder "0". Die Elemente (000 001) einer Datenzeile

entsprechen z.B. einer Codewortreihe "010 100 100". Die Datenzeile hat eine "1", während

die Codewortreihe drei "1

en" hat. Wenn die

Zahl der "1 en" in der Datenzeile

und die Zahl "1

en" in der Codewortreihe

nun durch 2 geteilt wird, ergibt sich der gleiche Rest, nämlich "1". Es werde noch ein anderes Beispiel

betrachtet. Die Elemente (000 000) einer Datenzeile entsprechen

einer Codewortreihe "010

100 000". Die Datenzeile

hat keine "1", während die

Codewortreihe zwei "1

en" hat. Wenn die

Zahl der "1 en" in der Datenzeile

und die Zahl der "1

en" in der Codewortreihe

durch 2 geteilt werden, haben sie den gleichen Rest, nämlich "0".

-

In

der Umwandlungstabelle von Tabelle 3 ist die maximale Zwangslänge r gleich

4 (r = 4). Der Umwandlungscode, in welchem i = 4 ist, hat einen

Ersatzcode, um den maximalen Lauf k von 7 (k = 7) zu erreichen.

-

Eine

Datenzeile kann nach der Umwandlungstabelle von Tabelle 3 moduliert

werden, um dadurch in vorbestimmten Intervallen eine DSV-Steuerung

auf die Kanalbitreihe auszuüben,

wie dies bisher praktiziert wurde. Die Beziehung zwischen der Datenzeile

und der umgewandelten Codewortreihe kann jedoch auch für eine hocheffiziente

DSV-Steuerung benutzt werden.

-

Wie

oben erwähnt

wurde, kann die Umwandlungstabelle eine solche sein, die auf dem

Umwandlungsgesetz basiert, bei dem dann, wenn die Zahl der "1 en" in den Elementen

an der Datenzeile und die Zahl "1 en" in einer umzuwandelnden

Codewortreihe durch 2 geteilt werden, die Reste gleich sind, nämlich entweder "1" oder "0".

Wenn dies der Fall ist, ist das Einfügen eines DSV-Steuerbits "1" in die Kanalbitreihe, das "Umwandlung" anzeigt, oder eines

DSV-Steuerbits "0", das "Nichtumwandlung" anzeigt, äquivalent

zum Einfügen eines

DSV-Steuerbits "1" in einer Datenbitreihe, um die Datenbitreihe

umzuwandeln, bzw. zum Einfügen

eines DSV-Steuerbits "0" in die Datenbitreihe,

um die Datenbitreihe nicht umzuwandeln Es sei angenommen, daß in der

Tabelle 3 drei Bits "001" umgewandelt werden

sollen. Um am Ende dieser Bitreihe ein DSV-Steuerbit einzufügen, wird

die Datenreihe als (001-x) dargestellt, worin x ein Bit, entweder

0 oder 1, bedeutet. Falls x gleich "0" ist, ändert sich

die Umwandlungstabelle von Tabelle 3 folgendermaßen:

-

Falls

x gleich "1" ist, ändert sich

die Umwandlungstabelle von Tabelle 3 folgendermaßen:

-

Die

Codewortreihe kann einer NRZI-Modulation unterworfen werden. Man

erhält

dann die folgenden Pegelcodes:

-

Die

letzten drei Bits jedes Pegelcodes sind offensichtlich zu den letzten

drei Bits des anderen Pegelcodes invers. Dies bedeutet, daß die DSV-Steuerung

an der Datenzeile vorgenommen werden kann, indem für das DSV-Steuerbit

x entweder "1" oder "0" gewählt

wird.

-

Im

Hinblick auf die auf die DSV-Steuerung zurückzuführende Redundanz bedeutet die

Durchführung der

DSV-Steuerung an einem Bit, daß diese

Steuerung an 1,5 Bit durchzuführen

ist. Dies liegt daran, daß in Tabelle

3 die Umwandlungsraten m und n in der Kanalbitreihe gleich 2 bzw.

3 sind (m = 2, n = 3). Für

die DSV-Steuerung in einer RLL-(107)-Tabelle, wie der Tabelle 1,

ist die DSV-Steuerung in der Kanalbitreihe durchzuführen. Um

den mini malen Lauf zu sichern, sind wenigstens zwei Kanalbits erforderlich,

wie dies oben angegeben wurde. Deshalb wird die Redundanz größer.

-

In

der Umwandlungstabelle von Tabelle 3 kann die DSV-Steuerung in einer

Datenzeile durchgeführt werden.

Deshalb ist eine effiziente DSV-Steuerung möglich. Da die Zahl der Wiederholungen

des minimalen Laufs eingeschränkt

ist, ist es außerdem

möglich,

Codes zu erzeugen, die mit hoher Dichte aufgezeichnet und wiedergegeben

werden.

-

Für den praktischen

Einsatz der Umwandlungstabelle von Tabelle 3 muß ein Synchronisiersignal verwendet

werden, um den Start der Daten zu identifizieren, bevor die Codereihe

reproduziert wird. Das Synchronisiersignal sollte ein Muster haben,

welches das Synchronisiersignal von jedem anderen Signal unterscheidet.

In einigen Fällen

müssen

mehrere Synchronisiersignale benutzt werden. Wenn dies der Fall

ist, sollten die Synchronisiersignale Muster haben, die voneinander

unterschieden werden können.

-

Um

Daten mit hoher Dichte auf einem Aufzeichnungsmedium, wie einer

Magnetplatte, einer magneto-optischen Platte oder einer optischen

Platte, aufzuzeichnen oder von ihm wiederzugeben, ist es, wie oben beschrieben,

notwendig, als Modulationscode einen Code zu wählen, der den minimalen Lauf

1 (d = 1) hat, um die Verzerrung der Daten bei der Aufzeichnung

und Wiedergabe zu minimieren und dadurch die Erzeugung von Fehlern

zu verhindern, und ein geeignetes Synchronisiersignal zu benutzen,

wenn als Code, der für

die Datenaufzeichnung und -wedergabe mit hoher Dichte geeignet ist,

1,7PP-Codes ausgewählt

werden.

-

EP-A-0

577 402 beschreibt einen Synchronisationsdetektor zum Detektieren

von Synchronisiersignalen, die in Hochfrequenzsignale eingebettet

sind, wobei dieser Detektor eine Zähleinrichtung zum Zählen der Zahl

der Kanaltakte zwischen benachbarten extrahierten Flanken des HF-Signals

aufweist, sowie eine Halteeinrichtung zum Halten des vorherigen

Zählwerts

der Kanaltakte. Synchronisiersignale werden detektiert, indem die

Ausgangssignale der Zähleinrichtung

und der Halteeinrichtung mit einem Rahmen-Synchronisiersignal und

einem Fehlerkorrektur-Synchronisiersignal verglichen werden. EP-A-0

577 402 beschreibt ferner, daß Muster,

die in mit variabler Länge

kodierten Signalen niemals auftreten, als Rahmen-Synchronisiersignale benutzt werden,

und sowohl der maximale Abstand Tmax zwischen Magnetisierungsübergängen als

auch der minimale Abstand Tmin zwischen Magnetisierungsübergängen (die

den maximalen bzw. minimalen Lauflängen entsprechen) von den Synchronisiersignalen

erfüllt

sein müssen.

-

EP-A-0

597 443 beschreibt ein Modulationsverfahren, bei dem in vorbestimmten

Intervallen ein Muster mit vorgegebener Länge in eine Sequenz von Daten

eingefügt

wird, die entwe der mit fester Länge

oder mit variabler Länge

kodiert sind, wobei die eingefügten

Muster für

die Steuerung des digitalen Summenwerts (DSV) der modulierten kodierten

Daten benutzt und so ausgewählt

werden, daß der

Redundanzpegel reduziert wird. EP-A-0 597 443 beschreibt auch, daß in Abhängigkeit

von den Einfügungspositionen

der Muster die maximale Lauflänge

des variablen Längencodes

nicht erfüllt

werden kann. In diesem Fall werden die Muster auf der Basis von

(d+1) Bits vor und hinter der Mustereinfügung festgelegt, wobei d der

minimale Lauf des Codes ist.

-

EP-A-0

779 623 beschreibt ein Übertragungsverfahren,

das einen variablen Längencode

benutzt. Das Synchronisiersignal enthält ein Bitmuster, das den maximalen

Lauf verletzt. Vor und hinter dem Synchronisiersignal werden Bitmuster

eingefügt,

die jeweils eine Lauflänge

haben, die größer ist

als der minimale Lauf.

-

Die

vorliegende Erfindung entstand im Hinblick auf die vorangehenden

Ausführungen.

Das Ziel der Erfindung besteht darin, ein zuverlässigeres Muster für ein Synchronisiersignal

zur Verfügung

zu stellen.

-

Nach

einem ersten Aspekt der Erfindung ist ein Datenmodulationsgerät vorgesehen

zum Modulieren von Daten mit einer Basisdatenlänge von m Bits in Daten mit

einer Basislänge

von n Bits mittels eines variablen Längencodes (d,k; m,n; r), wobei

das Gerät

aufweist: eine Modulationseinrichtung zum Erzeugen einer Codefolge

und eine Synchronisiersignal-Addiereinrichtung zum Hinzufügen eines

Synchronisiersignals zu der Codefolge, wobei das Synchronisiersignal

ein Muster hat, das einen maximalen Lauf verletzt, und zum Einfügen eines

einem minimalen Lauf entsprechenden Signals vor dem Synchronisiersignal.

-

Nach

einem zweiten Aspekt sieht die Erfindung ein Datendemodulationsgerät vor zum

Demodulieren eines variablen Längencodes

(d,k; m,n; r) mit einer Basiscodelänge von n Bits in Daten mit

einer Basisdatenlänge

von m Bits, wobei das Gerät

aufweist: eine Synchronisiersignal-Detektoreinrichtung, die so betreibbar ist,

daß sie

in einer Codefolge ein Signal detektiert, das einem minimalen Lauf

entspricht, gefolgt von einem Synchronisiersignal mit einem Muster,

das einen maximalen Lauf verletzt.

-

Weitere

Aspekte der Erfindung umfassen ein Modulationsverfahren, ein Demodulationsverfahren

und ein Datenmedium mit Programmbefehlen zur Implementierung des

Modulationsverfahrens oder des Demodulationsverfahrens gemäß der Erfindung.

Diese weiteren Aspekte sind in den anliegenden Ansprüchen definiert.

-

1 zeigt

ein Blockdiagramm eines Datenmodulationsgeräts nach einem Ausführungsbeispiel

der Erfindung,

-

2 zeigt

ein Blockdiagramm eines anderen Ausführungsbeispiels der Erfindung,

-

3 zeigt

ein Blockdiagramm eines Datendemodulationsgeräts nach einem Ausführungsbeispiel

der Erfindung.

-

Im

folgenden werden Ausführungsbeispiele

der Erfindung beschrieben. Um klarzustellen, welche in einem Anspruch

beschriebenen Mittel welchen in den einzelnen Ausführungsbeispielen

benutzten Komponenten entsprechen, sind die Bezugszeichen, die die

Mittel bezeichnen, in Klammern hinter der beschriebenen Komponente

angegeben. Die Benutzung dieser Bezugszeichen soll die Mittel jedoch

nicht auf die betreffende Komponente einschränken.

-

Das

Datenmodulationsgerät

gemäß der Erfindung

umfaßt

eine Synchronisiersignal-Addiereinrichtung (z.B. die SYNC-Bit-Einfügungsstufe 14 in 1),

die dazu dient, ein Synchronisiersignal zu dem in einer Codereihe

enthaltenen minimalen Lauf hinzuzufügen. Das Synchronisiersignal

hat ein Muster, das den maximalen Lauf verletzt.

-

Das

Datendemodulationsgerät

gemäß der Erfindung

besitzt eine Synchronisiersignal-Detektoreinrichtung (z.B. die SYNC/SyncID-Identifizierstufe 33 von 3),

die dazu dient, nach der Detektierung des minimalen Laufs ein Synchronisiersignal

aus der Codereihe zu detektieren. Dieses Synchronisiersignal hat

ein Muster, das den maximalen Lauf verletzt.

-

Die

Muster der in Tabelle 3 dargestellten Synchronisiersignale haben

die folgenden Eigenschaften, die in Tabelle 4 dargestellt sind.

- (1) (Tmax + 1) – (Tmax + 1), so daß sich 9T-9T

ergibt. Ein Muster, das den maximalen Lauf verletzt, wird zweimal

kontinuierlich erzeugt, wodurch die Detektierungsfähigkeit

vergrößert wird.

- (2) Der Wert 2T wird angewendet, bevor sich 9T-9T ergibt, so

daß die

Erzeugung von Tmax verhindert wird, unabhängig davon, welche Datenzeile

moduliert wurde. Mit anderen Worten, es wird ein kurzer Lauf eingefügt, so daß in der

Kombination der modulierten Datenzeile und des Datenpostens, der

dem einzufügenden Synchronisiersignal

unmittelbar vorangeht, kein Muster 8T-9T-9T auftreten kann. Es sei

angenommen, daß ein

Muster 8T-9T-9T auftritt. In diesem Fall ist der Detektierungsabstand

zwischen der ersten Hälfte

dieses Musters, d.h. 8T-9T, und dem detektierten Muster 9T-9T gleich 1, wodurch

die Möglichkeit

vergrößert wird, daß die Detektierungsfähigkeit

abnimmt und Detektierungsfehler verursacht. Um dies zu verhindern,

wird 2T eingefügt

Alternativ können

zu dem gleichen Zweck 3T oder 4T vor dem 9T-9T eingefügt wer den.

Falls 3T oder 4T eingefügt

werden, nimmt jedoch die Redundanz zu. Somit wird höchste Effizienz

erreicht, wenn 2T eingefügt

wird.

- (3) Vor 2T-9T-9T werden zwei Bits angeordnet, die als Koppelbits

benutzt werden. Dies macht es möglich, an

jeder gewünschten

Position ein Synchronisiersignal anzufügen und die Daten an der Position

zu beenden, an der das Synchronisiersignal eingefügt wird.

-

-

Es

sei angenommen, daß die

Umwandlungstabelle von Tabelle 3 eine Codewortreihe (d.h. eine Kette von

Kanalbits) erzeugt. Um ein Synchronisiersignal an einer gewünschten

Position in der Codewortreihe einzufügen, kann, falls erforderlich,

eine Abschlußtabelle

benutzt werden, um an der gewünschten

Position einen Code zu beenden, der mittels der Umwandlungstabelle

von Tabelle 3 erzeugt wurde und der ein Code mit variabler Länge ist.

-

Um

in dem Fall von Tabelle 3 an irgendeiner gewünschten Position ein Synchronisiersignal

einzufügen,

wird an der Verbindung zweier benachbarter Codewortreihen ein Verbindungsmuster

hinzugefügt,

um sowohl den minimalen Lauf d als auch den maximalen Lauf k zu

sichern. Zwischen den beiden benachbarten Codewortreihen wird ein

Synchronisiersignalmuster eingefügt.

(Das Verbindungsmuster kann als Teil des Synchronisiersignalmusters

betrachtet werden). Das so eingefügte oder gegebene Synchronisiersignalmuster

besteht aus 24 Bits, die durch die Umwandlungsraten (m = 2 und n

= 3) geteilt werden können,

wobei keine Reste zurückbleiben.

Genauer gesagt, ist das Synchronisiersignalmuster: "#01 010 000 000 010

000 000 010". Das erste

Bit # ist das Koppelbit, das entweder "0" oder "1" ist. Das zweite Kanalbit ist "0", um den minimalen Lauf zu sichern.

Das dritte und vierte Kanalbit definieren 2T. Von dem fünften Kanalbit

und folgenden werden zwei aufeinanderfolgende 9Ts definiert, das

als Synchronisiersignalmuster benutzt wird, wobei k = 8. Das heißt, zwischen "1" und "1" erscheinen

aufeinanderfolgend acht "0en". Dieses Muster wird

zweimal wiederholt. Das letzte Kanalbit dieses Synchronisiersignalmusters, "1", bestimmt den maximalen Lauf. Das letzte

Bit des Synchronisiersignalmusters ist ein Koppelbit "0". Das letzte Bit dient dazu, den minimalen

Lauf, d = 1, unabhängig

davon, was für

ein Bit auf dieses Bit folgt, zu sichern.

-

Im

folgenden werden die Abschlußtabelle

und das Koppelbit # in dem Synchronisiersignalmuster beschrieben.

Die Abschlußtabelle

ist, wie in Tabelle 4 dargestellt, folgende:

00 000

0000

010 100

-

Die

Abschlußtabelle

muß benutzt

werden, wenn weniger als vier Umwandlungscodes, die keine Ersatzcodes

zum Begrenzen der Fortsetzung der minimalen Läufe sind, die Zwangslängen definieren.

Wie aus Tabelle 3 ersichtlich ist, gibt es drei Umwandlungscodes,

wenn die Zwangslänge

gleich 1 ist, i = 1. Deshalb muß die

Abschlußtabelle

benutzt werden. Wenn die Zwangslänge

gleich 2 ist, i = 2, gibt es ebenfalls drei Umwandlungscodes, und

die Abschlußtabelle

muß benutzt

werden. Wenn die Zwangslänge

gleich 3 ist, i = 3, gibt es fünf

Codes, von denen einer ein Ersatzcode und die anderen vier Umwandlungscodes

sind. Da eine erforderliche Zahl von Codes vorhanden ist, wird ein

Abschluß durchgeführt. Wenn

die Zwangslänge

gleich 4 ist, i = 4, sind alle Umwandlungscodes Ersatzcodes, und

es braucht kein Abschluß berücksichtigt

zu werden. Deshalb sind der Abschlußtabelle (00), d.h. die Zwangslänge i =

1, und (0000), d.h. die Zwangslänge

i = 2, gegeben.

-

Das

Koppelbit "#" des Synchronisiersignals

ist gegeben, um den Fall, in dem ein Abschluß benutzt wird, von dem Fall

zu unterscheiden, in dem keine Abschlußtabelle benutzt wird. Genauer

gesagt, das erste Kanalbit "#" des Synchronisierkanalmusters

ist "1", wenn ein Abschlußcode benutzt

wird. Andernfalls ist dieses Bit gleich "0".

Somit kann das Koppelbit "#" bei der Demodulation

von Codes den Fall, in dem eine Abschlußtabelle benutzt wird, zuverlässig von

dem Fall unterscheiden, in dem keine Abschlußtabelle benutzt wird.

-

Das

Synchronisiersignalmuster ist durch (23 + 1) Kanalbits definiert

und kann deshalb zuverlässig

detektiert werden. Falls zwei oder mehr Typen von Synchronisiersignalen

erforderlich sind, reichen (23 + 1) Kanalbits nicht aus, um diese

Typen von Synchronisiersignalen zur Verfügung zu stellen.

-

Somit

müssen

zu den oben erwähnten

24 Kanalbits sechs Bits hinzugefügt

werden, so daß 30

Kanalbits benutzt werden, die Synchronisiersignale unterschiedlicher

Art erzeugen. Die verschiedenen Arten von Synchronisiersignalen

werden im folgenden beschrieben.

-

Die

zwei oder mehr Arten von Synchronisiersignalmustern in den Umwandlungstabellen

3 und 4 sind so definiert, wie dies in der Tabelle 5 dargestellt

ist. In jedem Synchronisiersignalmuster wird der minimale Lauf gesichert,

und der minimale Lauf kann nicht mehr als sechs Mal wiederholt werden,

wie dies in Tabelle 3 dargestellt ist. Jedes Synchronisiersignalmuster

ist so gewählt,

daß der

maximale Lauf nicht außerhalb

des Synchronisiersignal-Detektierungsmusters

erzeugt wird. Diese Synchronisiersignalmuster sind in der gleichen Weise

zu einer Datenzeile verbunden, wie dies in Tabelle 4 dargestellt

ist.

-

-

Wie

Tabelle 5 zeigt, stehen 15 Arten von Synchronisiersignalmustern

zur Verfügung,

die verschiedenen Gesetzen entsprechen, wenn 30 Bits als Synchronisiersignal-Bits

benutzt werden. Aus diesen Synchronisiersignalmustern können die

folgenden verschiedenen Synchronisiersignalmuster bestimmt werden,

wie dies weiter unten erläutert

wird.

-

Das

heißt,

es können

sieben Synchronisiersignalmuster ausgewählt werden, von denen zwei

beliebige benachbarte einen Abstand von 2 oder mehr haben.

-

-

Der "Abstand von 2 oder

mehr" bedeutet,

daß die

zwei Synchronisiersignalmuster sich in zwei oder mehr Bits voneinander

unterscheiden, wenn die Synchronisiersignalmuster detektiert werden

(die reproduzierten Daten bilden einen Pegelcode). Die in Tabelle

6 dargestellten Synchronisiersignalmuster sind diejenigen, die diese

Bedingung in den letzten sechs Bits erfüllen. Die in Tabelle 6 dargestellten

Muster sind dann effektiv, wenn viele Arten von Synchronisiersignalen

benötigt

werden.

-

Die

folgenden drei Synchronisiersignalmuster können als gleichstromfreie Synchronisiersignalmuster ausgewählt werden.

-

-

Das

Wort "gleichstromfrei" bedeutet, daß 30 Kanalbits

des Synchronisiersignalmusters einen DSV-Wert von Null haben. Die

in Tabelle 7 dargestellten Synchronisiersignalmuster sind gleichstromfrei

und haben jeweils einen Abstand von 2 oder mehr von dem benachbarten

Muster.

-

Die

folgenden drei Synchronisiersignalmuster können ausgewählt werden, um einen Satz zu

bilden, in dem das letzte Bit jedes Synchronisiersignalmusters entweder "0" oder "1" sein

kann.

-

-

In

dem Satz von Synchronisiersignalmustern, in dem das letzte Bit jedes

Synchronisiersignalmusters entweder "0" oder "1" sein kann, dient das letzte Kanalbit

jedes Musters zur Durchführung

einer Gleichstromsteuerung in der nächsten umgewandelten Datenzeile.

In dem Synchronisiersignalteil kann eine effiziente DSV-Steuerung

erreicht werden. Das Datenmodulationsgerät führt die DSV-Steuerung durch,

indem sie für das

letzte Bit jedes Synchronisiersignalmusters von Tabelle 8 in Abhängigkeit

von dem DSV-Wert der folgenden Datenzeile entweder "1" oder "0" wählt. Die

drei Arten von Synchronisiersignalmustern sind unabhängig von

dem Wert des letzten Bits des Musters festgelegt.

-

Anhand

der Zeichnungen wird nun ein Ausführungsbeispiel des Datenmodulationsgeräts gemäß der Erfindung

beschrieben. Dieses Ausführungsbeispiel

ist ein Datenmodulationsgerät,

das eine Datenzeile in einen variablen Längencode (d,k; m,n; r) = (1,7;

2,3; 4) umwandelt.

-

1 zeigt

das Blockdiagramm eines Datenmodulationsgeräts nach einem Ausführungsbeispiel

der Erfindung, das in vorgeschriebenen Intervallen Synchronisiersignale

einfügt.

Die DSV-Bit-Festlegungs-/-Einfügungsstufe

nimmt in vorgegebenen Intervallen eine DSV-Steuerung in einer Datenzeile

vor, bestimmt ein DSV-Steuerbit "1" oder "0" und fügt das DSV-Steuerbit in den

vorgeschriebenen Intervallen ein. Die Datenzeile wird einer Modulationsstufe 12 und

einer SYNC/Sync-ID-Festlegungsstufe 13 zugeführt. Die

Modulationsstufe 12 moduliert die Datenzeile, in die die

DSV-Steuerbits eingefügt

sind, indem sie eine Codereihe erzeugt. Die Codereihe wird an eine

SYNC-Bit-Einfügungsstufe 14 ausgegeben.

Die SYNC/Sync-ID-Festlegungsstufe 13 bestimmt

das Muster der Synchronisiersignale, die in den vorgeschriebenen

Intervallen in die Datenzeile eingefügt werden. Die Daten, die das

so festgelegte Muster repräsentieren,

werden der SYNC-Bit-Einfügungsstufe 14 zugeführt.

-

Die

SYNC-Bit-Einfügungsstufe 14 fügt die durch

die SYNC/Sync-ID-Festlegungsstufe 13 festgelegten Synchronisiersignale

in die von der Modulationsstufe 12 gelieferte Codereihe

ein. Die Codereihe, die nun die Synchronisiersignale enthält, wird

einer NRZI-Modulationsstufe 15 zugeführt. Die NRZI-Modulationsstufe 15 unterzieht

die von der SYNC-Bit-Einfügungsstufe 14 gelieferte

Codereihe einer NRZI-Modulation, indem sie diese in eine Kette von

Aufzeichnungswellenformen umwandelt. Das heißt, die NRZI-Modulationsstufe 15 gibt eine

Kette von Aufzeichnungswellenformen aus. Die Zeitsteuerstufe 16 erzeugt

ein Zeitsteuersignal. Das Zeitsteuersignal wird der DSV-Bit-Festlegungs-/-Einfügungsstufe 11,

der Modulationsstufe 12, der SYNC/Sync-ID-Festlegungsstufe 13,

der SYNC-Bit-Einfügungsstufe 14 und

der NRZI-Modulationsstufe 15 zugeführt und steuert so das Betriebs-Timing

dieser Stufen.

-

Die

SYNC/Sync-ID-Festlegungsstufe 13 setzt die ersten 24 Codes

des 30-Codeworts, d.h. das Synchronisiersignalmuster von Tabelle

3, auf "x01 010

000 000 010 000 000 010".

Der Wert "x" wird in Abhängigkeit

von der dem eingefügten

Synchronisiersignal unmittelbar vor angehenden Kette der umgewandelten

Codes bestimmt. Wenn die unmittelbar vorhergehende Datenumwandlung

mittels einer Abschlußtabelle

durchgeführt

wurde, wird "x" auf "1" gesetzt (x = 1). Andernfalls wird "x" auf "0" gesetzt

(x = 0). Das heißt, "x" ist einem eingefügten Synchronisiersignal äquivalent

und hat einen solchen Wert, daß sowohl

der minimale Lauf als auch der maximale Lauf gesichert werden.

-

Die

SYNC-Bit-Einfügungsstufe 14 fügt das Synchronisiersignal

in die Codereihe ein, wobei dieses Synchronisiersignal ein solches

ist, das von der SYNC/Sync-ID-Festlegungsstufe 13 in der oben beschriebenen

Weise festgelegt wurde. Nachdem das Synchronisiersignal in die Codereihe

eingefügt

wurde, beginnt der Prozeß am

Kopf der Umwandlungstabelle.

-

Im

folgenden wird die Arbeitsweise des vorliegenden Ausführungsbeispiels

erläutert.

-

Die

DSV-Steuerung wird in der Datenzeile in den vorgeschriebenen Intervallen

ausgeführt,

und in den vorgeschriebenen Intervallen werden Synchronisiersignale

in die Datenzeile eingefügt.

Die DSV-Bit-Festlegungs-/-Einfügungsstufe 11 akkumuliert

die DSV-Werte bis zu einer bestimmten Position und berechnet einen DSV-Wert

für das

nächste

Intervall. Dann wählt

die Stufe 11 ein DSV-Steuerbit "1" oder "0" aus, das die Summe des akkumulierten

DSV-Werts und den DSV-Wert für

das nächste

Intervall kleiner macht. Die Stufe 11 fügt das ausgewählte DSV-Steuerbit

in die Datenzeile ein. Der DSV-Wert kann nicht aus der Datenzeile

allein bestimmt werden. Deshalb benutzt die DSV-Bit-Festlegungs-/-Einfügungsstufe 11 die

Umwandlungstabelle, wobei sie aus der Datenzeile eine Codewortreihe

erzeugt. Die Stufe 11 ermittelt den DSV-Wert auf der Basis

der Codewortreihe.

-

Die

Bitreihe mit dem eingefügten

DSV-Wert wird von der Modulationsstufe 12 auf der Basis

der Umwandlungstabelle moduliert (oder umgewandelt). Die Modulationsstufe 12 speichert

Daten, die die Intervalle von Synchronisiersignalen repräsentieren.

Sie moduliert die Bitreihe bis zu einem Bit in der Nähe eines

Synchronisiersignals. Falls die Bitreihe nicht mit Hilfe der gewöhnlichen

Umwandlungstabelle umgewandelt werden kann, d.h. wenn die Abschlußtabelle

von Tabelle 4 benutzt werden muß,

werden an die SYNC/Sync-ID-Festlegungsstufe 13 Daten ausgegeben,

die diese Tatsache anzeigen.

-

Die

SYNC/Sync-ID-Festlegungsstufe 13 speichert Daten, die die

Synchronisiersignalintervalle repräsentieren, und legt den Wert

des ersten Bits des Synchronisiersignals, d.h. des Koppelbits aus

dem Zustand heraus fest, der bestand; bevor das Synchronisiersignal

eingefügt

wurde. Falls die Bitreihe mit Hilfe der normalen Umwandlungstabelle

umgewandelt wird, wird das Koppelbit auf "0" gesetzt.

Falls die Bitreihe nicht mit Hilfe der normalen Umwandlungstabelle

umgewandelt werden kann und deshalb die Abschlußtabelle benutzt werden muß, bezieht

sich die SYNC/Sync-ID-Festlegungsstufe 13 auf die Abschlußtabelle

und setzt das erste Bit des Synchronisiersignals, d.h. das Koppelbit,

auf "1".

-

Auf

diese Weise werden die ersten 24 Bits des Synchronisiersignals festgelegt.

Die verbleibenden sechs Bits werden auf Werte gesetzt und als Sync-ID-Bits

des Synchronisiersignals benutzt. Die Sync-ID-Bits können eines

von sieben Synchronisiersignalmustern annehmen, wie sie z.B. in

Tabelle 6 dargestellt sind. In jedem dieser Synchronisiersignalmuster

haben zwei benachbarte Bits einen Abstand 2 voneinander.

-

Die

Synchronisiersignale werden in der oben beschriebenen Weise festgelegt.

Die SYNC-Bit-Einfügungsstufe 14 fügt die Synchronisiersignale

in die Codereihe ein. Die Synchronisiersignale können mit Hilfe der in der SYNC/Sync-ID-Festlegungsstufe 13 gespeicherten

Abschlußtabelle

festgelegt werden. In diesem Fall werden die Synchronisiersignale,

die jeweils den aus der Abschlußtabelle

gewonnenen Wert enthalten, mit Hilfe der SYNC-Bit-Einfügungsstufe 14 in

die Codereihe eingefügt.

-

Zuletzt

wandelt die NRZI-Modulationsstufe 15 die Kanalbitreihe,

die einer DSV-Steuerung unterzogen wurde und Synchronisiersignale

enthält,

in einen Aufzeichnungscode um.

-

2 zeigt

ein Blockdiagramm eines anderen Ausführungsbeispiels der Erfindung.

Wie bereits in Verbindung mit dem ersten Ausführungsbeispiel erläutert wurde,

muß die

Modulation und die NRZI-Modulation durchgeführt werden, um einen DSV-Wert

zu berechnen. Jedes Synchronisiersignal muß der DSV-Steuerung und somit

der NRZI-Modulation unterzogen werden. Im Hinblick hierauf kann

das Datenmodulationsgerät

den in 2 dargestellten Aufbau haben.

-

In

dem Datenmodulationsgerät

von 2 fügt

die Steuerbit-Einfügungsstufe 21 für jede vorgeschriebene

Bitzahl ein DSV-Steuerbit in die Datenzeile ein. Die Datenzeile,

die nun die DSV-Steuerbits enthält,

wird der Modulationsstufe 12 zugeführt. Die Bits mit dieser vorgeschriebenen

Anzahl enthalten Synchronisiersignale. Deshalb braucht die Steuerbit-Einfügungsstufe 21 nicht

nur eine spezifische Anzahl von Bits einzufügen (sie kann vielmehr zwei

oder mehr spezifische Zahlen von Bits einfügen). Die Modulationsstufe 12 wandelt

die aus der Steuerbit-Einfügungsstufe 21 zugeführte Datenzeile

um, indem sie eine Kanalbitreihe erzeugt. Falls die Datenzeile in

der Modulationsstufe 12 nicht unmittelbar vor einem Synchronisiersignal

umgewandelt werden kann, liefert die Stufe 12 ein Signal

an eine SYNC/-Sync-ID-Einfügungsstufe 22,

das anzeigt, daß die

Abschlußtabelle

benutzt werden soll.

-

Die

SYNC/Sync-ID-Einfügungsstufe 22 fügt in vorgeschriebenen

Intervallen ein Synchronisiersignal in das modulierte Codewort ein.

Die SYNC/Sync-ID-Einfügungsstufe 22 enthält ei ne

Abschlußtabelle.

Wann immer dies nötig

ist, benutzt die Stufe 22 die Abschlußtabelle, indem sie eine Modulation

durchführt

und 30 Bits des Synchronisiersignalmusters in die Kanalbitreihe

einfügt.

Die Codewortreihe, die das Synchronisiersignal und das DSV-Steuerbit

enthält,

wird von der NRZI-Modulationsstufe 15 in Pegelcodes umgewandelt.

Eine DSV-Bit-/SYNC-Festlegungsstufe 23 berechnet aus der

ihr zugeführten

Pegelcodereihe einen DSV-Wert. Gleichzeitig

legt die Stufe 53 das Muster des Synchronisiersignals fest.

Das Ausgangssignal der DSV-Bit-/SYNC-Festlegungsstufe 23 ist

eine Kette von Aufzeichnungscodes und mit dem Ausgangssignal des Datenmodulationsgeräts von 1 identisch.

Die Zeitsteuerstufe 16 erzeugt ein Zeitsteuersignal. Das

Zeitsteuersignal wird der Steuerbit-Einfügungsstufe 21, der

Modulationsstufe 12, der SYNC/Sync-ID-Einfügungsstufe 22,

der NRZI-Modulationsstufe 15 und

der DSV-Bit-/SYNC-Festlegungsstufe 23 zugeführt. Das

Zeitsteuersignal steuert das Betriebs-Timing dieser Stufen.

-

Als

Nächstes

wird die Arbeitsweise des Datenmodulationsgeräts von 2 erläutert. Die

Steuerbit-Einfügungsstufe 21 erzeugt

aus der eingegebenen Datenzeile zwei Bitreihen. In die erste Bitreihe

werden in vorbestimmten Intervallen DSV-Steuerbits "1" eingefügt. In die zweite Bitreihe

werden in vorbestimmten Intervallen DSV-Steuerbits "0" eingefügt. Diese Bitreihen werden

von der Modulationsstufe 12 moduliert. Die Modulationsstufe 12 enthält eine

Umwandlungstabelle. Die SYNC/Sync-ID-Einfügungsstufe 22 fügt in die

von der Modulationsstufe 12 modulierten Signale Synchronisiersignale

ein. Die SYNC/Sync-ID-Einfügungsstufe 22 enthält eine

Abschlußtabelle

und wandelt die abgeschlossene Datenzeile in eine Codewortreihe

um, um Synchronisiersignale einzufügen. Die Codewortreihe wird

von der NRZI-Modulationsstufe 15 in Pegelcodes umgewandelt.

Dabei werden in der Kanalbitreihe keine DSV-Steuerbits festgelegt,

und es existieren zwei Typen von Pegelcodereihen. Die DSV-Bit-/SYNC-Festlegungsstufe 23 berechnet

den DSV-Wert jeder Pegelcodereihe und wählt aus diejenige Kanalbitreihe,

die die akkumulierten DSV-Werte blockiert, und legt diese fest.

Bei dieser Gelegenheit werden die Synchronisiersignalmuster festgelegt.

Die so festgelegte Codewortreihe (eine Kette von Kanalbits) wird

als Datenzeile ausgegeben, die der DSV-Steuerung unterzogen wurde.

-

Es

wird nun anhand der anliegenden Zeichnungen ein Datendemodulationsgerät beschrieben,

das ein Ausführungsbeispiel

der vorliegenden Erfindung darstellt. Dieses Ausführungsbeispiel

ist ein Datendemodulationsgerät,

das eine mit einem variablen Längencode

(d,k; m,n;) = (1,7; 2,3; 4) modulierte Datenzeile demoduliert.

-

3 zeigt

ein Blockdiagramm eines Datendemodulationsgeräts zum Demodulieren von reproduzierten

Daten, die Synchronisiersignale enthalten. Eine Komparator-/inverse

NRZI-Stufe 31 vergleicht die über einen Übertragungspfad übertragenen

Signale oder die von einem Aufzeichnungsmedium reproduzierten Signale

und unterzieht die Signale einer inversen NRZI-Modulation (und wandelt

sie dadurch in Flankensignale um). Die Flankensignale oder digitalen

Signale werden einer Demodulationsstufe 32 und einer SYNC/Sync-ID-Erkennungsstufe 33 zugeführt. Die

Stufe 32 demoduliert die digitalen Signale nach einer Demodulationstabelle

(d.h. einer inversen Umwandlungstabelle) und gibt die Signale an

eine SYNC-Bit-Extrahierstufe 34 aus.

Die SYNC/Sync-ID-Erkennungsstufe 33 detektiert die in vorbestimmten

Intervallen eingefügten Synchronisiersignale

(Sync). Falls eine inverse Umwandlungs-Abschlußtabelle, die eine der Abschlußtabellen bildet,

benutzt wird, unmittelbar bevor die Synchronisiersignale detektiert

werden, liefert die Stufe 33 die Daten, die diese Tatsache

anzeigen, an die Demodulationsstufe 32. Die SYNC/Sync-ID-Erkennungsstufe 33 erkennt eine

Sync-ID auf der Basis der letzten sechs Bits des Synchronisiersignals.

Die SYNC-Bit-Extrahierstufe 34 extrahiert

das Synchronisiersignal. Eine DSV-Bit-Extrahierstufe 35 entfernt

DSV-Steuerbits aus der demodulierten Datenzeile, die in vorgegebenen

Intervallen in die Datenzeile eingefügt wurden. Somit gibt die DSV-Bit-Extrahierstufe 35 die

anfängliche

Datenzeile aus. Ein Puffer 36 speichert die von der DSV-Bit-Extrahierstufe 35 zugeführten seriellen

Daten temporär

und gibt sie mit einer vorgeschriebenen Übertragungsrate aus. Eine Zeitsteuerstufe 37 erzeugt

ein Zeitsteuersignal. Das Zeitsteuersignal wird der Komparator-/inversen NRZI-Stufe 31,

der Demodulationsstufe 32, der SYNC/Sync-ID-Erkennungsstufe 33,

der SYNC-Bit-Extrahierstufe 34, der DSV-Bit-Extrahierstufe 35 und

dem Puffer 36 zugeführt.

Das Zeitsteuersignal steuert das Betriebs-Timing dieser Komponenten.

-

Die

SYNC/Sync-ID-Erkennungsstufe 33 bestimmt aus dem für die Synchronisiersignale

spezifischen Muster die Position von Synchronisiersignalen. Da die

Synchronisiersignale in vorgeschriebenen Intervallen eingefügt sind,

kann die Stufe 35 ihre Position durch Abzählen der

Intervalle bestimmen. Sobald die Positionen der Synchronisiersignale

bestimmt sind, wird die Demodulation nicht nur an den Daten unmittelbar

vor einem Synchronisiersignal sondern auch an der Abschlußtabelle

durchgeführt.

Unmittelbar nach einem Synchronisiersignal wird keine Abschlußtabelle

benötigt,

und die Daten können

mit Hilfe der gewöhnlichen

Umwandlungstabelle von Tabelle 3 demoduliert werden.

-

Nachdem

die Daten unmittelbar vor dem Synchronisiersignal in der oben beschriebenen

Weise demoduliert wurden, entfernt die SYNC-Bit-Extrahierstufe 34 die

Bits eines vorgeschriebenen Synchronisiersignals. Deshalb ist die

SYNC-Bit-Extrahierstufe 34 mit der Demodulationsstufe 32 kompatibel.

-

Im

folgenden wird die Arbeitsweise des Datendemodulationsgeräts beschrieben.

-

Die über den Übertragungspfad übertragenen

Signale oder die von dem Aufzeichnungsmedium reproduzierten Signale

werden der Komparator-/inversen NRZI-Stufe 31 zugeführt. Die

Signale werden verglichen und in inverse NRZI-Codes umgewandelt

(Codes, in denen eine Flanke anzeigt). Diese Codes oder digitalen Signale

werden der Demodulationsstufe 32 und der SYNC/Sync-ID-Erkennungsstufe 33 zugeführt.

-

Die

Demodulationsstufe 32 demoduliert die digitalen Signale

nach Maßgabe

der inversen Umwandlungstabelle von Tabelle 3. Die Demodulationsstufe 32 enthält die inverse

Umwandlungstabelle von Tabelle 3, benötigt jedoch keine inverse Umwandlungstabelle

für den

Abschluß.

Im vorliegenden Fall kann die inverse Umwandlung nicht an einem

Abschnitt unmittelbar vor einem eingefügten Synchronisiersignal durchgeführt werden.

Die SYNC/-Sync-ID-Erkennungsstufe 33 führt trotzdem

die inverse Umwandlung durch. Die SYNC/-Sync-ID-Erkennungsstufe 33 liefert

die detektierten Synchronisiersignale an die Demodulationsstufe 32.

Die Demodulationsstufe 32 startet die Demodulation synchron

mit den Synchronisiersignalen.

-

Die

SYNC/Sync-ID-Erkennungsstufe 33 detektiert "x01 010 000 000 010

000 000 010", das

2T-9T-9T, d.h. das gegebene Synchronisiersignalmuster, repräsentiert.

Dieses Synchronisiersignalmuster enthält 9T, das ein Spezifikum für das Synchronisiersignalmuster

ist. Aus irgendeiner anderen Kette von Datencodewörtern würde dieses

Synchronisiersignalmuster nicht detektiert. Sobald die SYNC/Sync-ID-Erkennungsstufe 33 ein Synchronisiersignalmuster

detektiert hat, können

die in den vorgeschriebenen Intervallen eingefügten Synchronisiersignale mit

Hilfe eines internen Zählers

oder dgl. detektiert werden.

-

Die

SYNC/Sync-ID-Erkennungsstufe 33 enthält eine inverse Umwandlungs-Abschlußtabelle,

die eine der Abschlußtabellen

ist. Sie demoduliert die Codewörter,

die unmittelbar vor jedem Synchronisiersignal erzeugt werden, nach

der Abschlußtabelle.

Die Ergebnisse der so durchgeführten

Demodulation werden der Demodulationsstufe 32 zugeführt. Nach

allem genügt

es, eine inverse Umwandlungstabelle entweder in der Demodulationsstufe 32 oder

in der SYNC/Sync-ID-Erkennungsstufe 33 vorzusehen.

-

Die

SYNC/Sync-ID-Erkennungsstufe 33 erkennt die zwei oder mehr

Synchronisiersignale, die auf das 2T-9T-9T folgen, das ein Synchronisiersignalmuster

darstellt. Für

jedes Synchronisiersignal wird ein Muster ausgewählt, das leicht detektiert

werden kann.

-

Die

SYNC-Bit-Extrahierschaltung 34 entfernt aus jedem Synchronisiersignal

30 Bits. Außerdem

entfernt die DSV-Bit-Extrahierstufe 35 DSV-Steuerbits,

die in vorgeschriebenen Intervallen eingefügt sind.

-

Ein

Beispiel für

die inverse Umwandlungstabelle ist in der unten dargestellten Tabelle

9 angegeben. Ein Beispiel für

die inverse Abschluß-Umwandlungstabelle

ist in der unten dargestellten Tabelle 10 angegeben.

-

1,7PP(d,k;

m,n; r) 0 (1,7; 2,3; 4) r = 4 Tabelle

9: Inverse Umwandlungstabelle

-

Tabelle

10: Inverse Umwandlungstabelle

-

Der

minimale Lauf d = 1 kann gesichert werden, indem Synchronisiersignale

festgelegt und in der oben beschriebenen Weise eingefügt werden.

Die Zahl, wie oft der minimale Lauf wiederholt werden kann, bleibt

auf sechs begrenzt. Außerhalb

des Synchronisiersignals wird kein Lauf erzeugt, der größer ist

als der maximale Lauf k = 7. Falls 9T, wobei k = 8 in dem Synchronisiersignal

zwei Mal kontinuierlich wiederholt wird, wird das Synchronisiersignal

leichter detektiert. Ein solches Synchronisiersignal, wie es in

Tabelle 6 dargestellt ist, besitzt sieben Typen von Synchronisiersignal-IDs

und zwei beliebige einander benachbarte Bits in ihm haben einen

Abstand von 2 voneinander. Somit können die IDs dieses Synchronisiersignals

leicht detektiert werden. Neben diesen Eigenschaften besteht die

Möglichkeit, daß die DSV-Steuerung

an den Datenbits durchgeführt wird,

so daß eine

DSV-Steuerung mit hoher Effizienz möglich ist.

-

Die

Umwandlungstabelle besitzt Ersatzcodes mit variabler Länge, die

jeweils einen minimalen Lauf d von 1 (d = 1), einen maximalen Lauf

k von 7 (k = 7), eine Umwandlungsrate m/n von 2/3 haben und die

jeweils die Zahl der Male beschränken,

wie oft der minimale Lauf wiederholt werden kann. Die Umwandlungstabelle basiert

auf dem Gesetz, daß dann,

wenn die Zahl von "1

en" in den Elementen

der Umwandlungstabelle und die Zahl von "1 en" in

einer umzuwandelnden Codewortreihe durch 2 geteilt werden, die Reste

gleich sind, nämlich

entweder "1" oder "0". Wenn ein Synchronisiersignal an einer

vorgeschriebenen Position in der Umwandlungstabelle eingefügt wird,

nimmt das Synchronisiersignal ein eindeutiges Muster an, ohne daß die begrenzte

Anzahl von Malen, wie oft der minimale Lauf und der maximale Lauf

wiederholt werden können,

geändert

wird, und wird leicht detektiert. Deshalb kann das Synchronisiersignal

leicht und stabil detektiert werden. Da die Datenzeile mit Sicherheit

an einer Position endet, an der ein Synchronisiersignal eingefügt ist,

können die

Daten vor und hinter dem Synchronisiersignal leichter kontrolliert

werden, während

sie demoduliert werden. Dies trägt

zu einer stabilen Datendemodulation bei.

-

Das

Datenmedium zur Bereitstellung des Computerprogramms für den oben

beschriebenen Prozeß kann

eine Magnetplatte, eine CD-ROM, ein Festkörperspeicher oder dgl. sein.

Darüber

hinaus kann das Computerprogramm mit Hilfe eines Kommunikationsmediums,

wie eines Netzwerks oder eines Kommunikationssatelliten bereitgestellt

werden.

-

In

dem Datenmodulationsgerät,

dem Datenmodulationsverfahren und dem Datenmedium gemäß der Erfindung

wird zu einer Codereihe nach dem Hinzufügen des minimalen Laufs ein

Synchronisiersignal hinzugefügt.

Das Synchronisiersignal hat ein Muster, das den maximalen Lauf verletzt,

d.h. das Synchronisiersignal erhält

ein zuverlässiges

Muster.

-

In

dem Datendemodulationsgerät,

dem Datendemodulationsverfahren und dem Datenmedium gemäß der Erfindung

wird aus einer Codereihe nach dem Detektieren des minimalen Laufs

ein Synchronisiersignal detektiert. Das Synchronisiersignal hat

ein Muster das den maximalen Lauf verletzt. Deshalb kann ein Synchronisiersignal

zuverlässig

detektiert werden.