CN105262483B - Cdr电路和半导体装置 - Google Patents

Cdr电路和半导体装置 Download PDFInfo

- Publication number

- CN105262483B CN105262483B CN201510410326.6A CN201510410326A CN105262483B CN 105262483 B CN105262483 B CN 105262483B CN 201510410326 A CN201510410326 A CN 201510410326A CN 105262483 B CN105262483 B CN 105262483B

- Authority

- CN

- China

- Prior art keywords

- frequency

- circuit

- phase

- pulling

- synchronization loop

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 11

- 230000010355 oscillation Effects 0.000 claims abstract description 114

- 230000009471 action Effects 0.000 claims abstract description 12

- 238000012937 correction Methods 0.000 claims description 162

- 238000000034 method Methods 0.000 claims description 26

- 238000012545 processing Methods 0.000 claims description 22

- 230000004044 response Effects 0.000 claims description 22

- 230000008569 process Effects 0.000 claims description 17

- 230000001360 synchronised effect Effects 0.000 claims description 17

- 230000008859 change Effects 0.000 abstract description 16

- 230000006870 function Effects 0.000 description 15

- 238000001514 detection method Methods 0.000 description 10

- 239000004973 liquid crystal related substance Substances 0.000 description 9

- 238000010586 diagram Methods 0.000 description 6

- 230000005540 biological transmission Effects 0.000 description 5

- 230000000694 effects Effects 0.000 description 4

- 230000004043 responsiveness Effects 0.000 description 4

- 238000005070 sampling Methods 0.000 description 4

- 238000011084 recovery Methods 0.000 description 3

- 230000009467 reduction Effects 0.000 description 3

- 230000003247 decreasing effect Effects 0.000 description 2

- 230000003111 delayed effect Effects 0.000 description 2

- 238000009825 accumulation Methods 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000013481 data capture Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000001172 regenerating effect Effects 0.000 description 1

- 239000000758 substrate Substances 0.000 description 1

- 238000012549 training Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/0004—Initialisation of the receiver

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/07—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop using several loops, e.g. for redundant clock signal generation

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/0807—Details of the phase-locked loop concerning mainly a recovery circuit for the reference signal

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/081—Details of the phase-locked loop provided with an additional controlled phase shifter

- H03L7/0812—Details of the phase-locked loop provided with an additional controlled phase shifter and where no voltage or current controlled oscillator is used

- H03L7/0814—Details of the phase-locked loop provided with an additional controlled phase shifter and where no voltage or current controlled oscillator is used the phase shifting device being digitally controlled

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/10—Details of the phase-locked loop for assuring initial synchronisation or for broadening the capture range

- H03L7/107—Details of the phase-locked loop for assuring initial synchronisation or for broadening the capture range using a variable transfer function for the loop, e.g. low pass filter having a variable bandwidth

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/10—Details of the phase-locked loop for assuring initial synchronisation or for broadening the capture range

- H03L7/107—Details of the phase-locked loop for assuring initial synchronisation or for broadening the capture range using a variable transfer function for the loop, e.g. low pass filter having a variable bandwidth

- H03L7/1075—Details of the phase-locked loop for assuring initial synchronisation or for broadening the capture range using a variable transfer function for the loop, e.g. low pass filter having a variable bandwidth by changing characteristics of the loop filter, e.g. changing the gain, changing the bandwidth

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/0016—Arrangements for synchronising receiver with transmitter correction of synchronization errors

- H04L7/002—Arrangements for synchronising receiver with transmitter correction of synchronization errors correction by interpolation

- H04L7/0025—Arrangements for synchronising receiver with transmitter correction of synchronization errors correction by interpolation interpolation of clock signal

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/02—Speed or phase control by the received code signals, the signals containing no special synchronisation information

- H04L7/033—Speed or phase control by the received code signals, the signals containing no special synchronisation information using the transitions of the received signal to control the phase of the synchronising-signal-generating means, e.g. using a phase-locked loop

Abstract

公开了CDR电路和半导体装置。即使由于温度变化等而在CDR电路的振荡电路产生不期望的频率变动,也不重新进行使用输入数据样式的频率牵引动作,使得能够进行振荡时钟信号相对于输入数据的同步化。在CDR电路设置在利用相位同步环路电路的对于通过频率同步环路电路完成频率牵引后的频率完成相位牵引之后或者在相位牵引动作中具有小的环路增益而更新牵引完成的振荡频率的电路。由于具有小的环路增益来更新完成了牵引的振荡频率,因此成为能够即使在相位牵引动作中也在没有相位同步环路不期望地进行振荡的情况下对频率同步环路电路中的振荡电路的频率变动进行校正。

Description

技术领域

本发明涉及具备根据在数据列嵌入有时钟信号的数据来再生时钟信号的功能的时钟/数据/恢复(CDR)电路,例如涉及适用于使用了CDR电路的数据输入接口电路而有效的技术。

背景技术

近年来,由于被使用于智能手机、平板终端的显示器的高细致化,发送设备与接收设备间的接口的高速化正在发展。以往,发送设备将时钟与数据一同送出、接收设备按照该时钟取入数据的源同步方式被使用得多。但是,在源同步方式中,时钟与数据间的偏移成为对高速化的妨碍,最近开始使用将时钟嵌入于数据来进行发送的所谓嵌入时钟方式。

嵌入时钟方式的接收需要作为把时钟和数据分离的功能的CDR(Clock DataRecovery:时钟数据恢复)电路,该CDR电路的性能对被嵌入有该CDR电路的设备及进一步地设备的应用系统整体的性能带来大的影响。

作为关于CDR电路进行了记载的文献的例子,有专利文献1。在专利文献1中,生成用于从被串行传输的数据信号抽出数据的时钟信号并进行输出的时钟/数据/恢复电路具有用于使用规定的基准时钟信号来使时钟信号锁定于期望的频率的频率同步环路以及用于在时钟信号的频率锁定状态下使时钟信号与数据信号相位同步的相位同步环路。在频率同步环路的动作中进行参照时钟信号与所生成的时钟信号的频率比较,锁定与该比较结果相应的频率的时钟信号频率,频率锁定的时钟信号的相位通过使相位同步环路进行动作而与输入数据的相位同步化。

在如专利文献1那样提供参照时钟并使用该参照时钟进行频率牵引(频率锁定)的情况下,在不要求长时间的连续接收的情况下,在频率锁定后将振荡电路的设定固定。但是,在需要长时间的连续接收的情况下,还存在即使在频率锁定后也以参照时钟继续维持锁定状态的情况。

CDR之中也有不提供参照时钟的CDR。在该情况下,在接收设备侧使时钟信号在初期进行自振荡以检测输入数据的边缘,由此对输入数据的频率进行上述时钟信号的配合,锁定频率。频率锁定后将振荡电路的设定固定。在锁定振荡频率之后,成为使用相位同步环路修正微小的相位的定时误差。

现有技术文献。

专利文献。

专利文献1:特开2012-44446号公报。

发明内容

发明要解决的课题

本发明人关于CDR电路进行了以下研究。在CDR电路中可知,在根据发送数据再生时钟信号,按该时钟信号接收数据的情况下,如果是短时间的数据接收,则按不使用参照时钟而进行频率锁定来进行数据接收的方法没有问题,但是在进行长时间连续接收的情况下,由于温度变化、电源电压的变动,振荡电路的振荡频率变动,产生频率锁定偏离的可能性、即在相位校正中变得不能使时钟信号与接收数据同步的风险,存在变得不能进行接收数据的再生的可能性。

在这样的情况下,成为向发送设备发出频率的再锁定请求(频率牵引的再请求)并暂时停止数据发送,在该期间重新进行频率锁定。然而,如果为了重新进行频率牵引动作而暂时停止数据发送,则导致数据传输效率下降。

本发明的目的在于即使由于温度变化等而在CDR电路的振荡电路产生不期望的频率变动,也不重新进行使用输入数据样式的频率牵引动作,使得能够进行振荡时钟信号相对于输入数据的同步化。

本发明的所述以及其它目的和新颖的特征将根据本说明书的记述以及随附附图而变得明了。

用于解决课题的方案

如果简单地说明本申请中所公开的发明中的代表性的发明的概要则为按下述那样。

即,在CDR电路设置如下的电路:该电路在利用相位同步环路电路的对于通过频率同步环路电路完成频率牵引的频率完成了相位牵引之后或者在相位牵引动作中,具有小的环路增益(使环路带宽窄)而更新完成了牵引的振荡频率。由于具有小的环路增益来更新完成了牵引的振荡频率,因此成为能够即使是在相位牵引动作中,也在相位同步环路没有不期望地进行振荡的情况下对频率同步环路电路中的振荡电路的频率变动进行校正。

发明的效果

简单地说明通过本申请中所公开的发明中的代表性的发明所得到的效果,则为按下述那样。

即,即使由于温度变化等而在振荡电路产生不期望的频率变动,也不重新进行使用输入数据样式的频率牵引动作,能够使得能够进行振荡时钟信号相对于输入数据的同步化。

附图说明

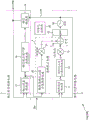

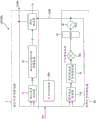

图1是例示第一实施方式的CDR电路的框图。

图2是例示在将图1的CDR电路适用于数据接口的情况下的系统结构的框图。

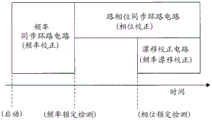

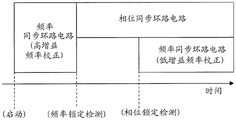

图3是例示利用图1的同步化控制部的对于CDR电路的基本的控制方式的定时图。

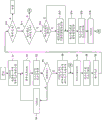

图4是例示图1的CDR电路的动作流程的流程图。

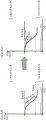

图5是示出对于放置了VCO的振荡时钟信号的频率漂移的情况进行频率校正的情况的说明图。

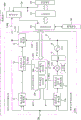

图6是例示第二实施方式的CDR电路的框图。

图7是例示在将图6的CDR电路适用于数据接口的情况下的系统结构的框图。

图8是例示利用图6的同步化控制部的对于CDR电路的基本的控制方式的定时图。

图9是例示图6的CDR电路的动作流程的流程图。

图10是作为第三实施方式例示液晶驱动器作为在外部接口电路具备CDR电路的半导体装置的框图。

具体实施方式

1. 实施方式的概要

首先,关于本申请中所公开的发明的代表性的な实施方式说明概要。在关于代表性的实施方式的概要说明中附加括号进行参照的附图中的参照标记只不过例示包括在附有该参照标记的结构要素的概念中的要素。

[1]<对频率牵引后的振荡电路的频率变动进行校正的漂移校正>

CDR电路(1)具有:频率同步环路电路(2),使振荡电路(16)的振荡时钟信号(CLKf)的频率与输入数据(Din)的频率同步;相位同步环路电路(3),输入所述振荡时钟信号而输出与所述输入数据的相位同步的相位同步时钟信号b(CLKfp);以及漂移校正电路(4),设为在利用所述频率同步环路电路的频率牵引之后的利用所述相位同步环路电路的相位牵引动作中或者相位牵引完成后,基于所述输入数据与所述相位同步时钟信号的相位差来运算校正值,与所述频率同步环路电路相比具有更小的环路增益而能够利用所述校正值对所述振荡电路的振荡频率进行校正。

由此,通过与频率同步环路电路相比具有更小的环路增益的漂移校正电路对完成了牵引的振荡频率进行校正。换言之,小的环路增益等效于使环路带宽窄,因此能够相对于振荡电路的频率变动而延迟负反馈控制的响应。因而,成为能够即使是在相位牵引动作中,也在相位同步环路没有不期望地进行振荡的情况下对频率同步环路电路中的振荡电路的频率变动进行校正。即使由于温度变化等而在振荡电路产生不期望的频率变动,也不重新进行使用输入数据样式的频率牵引动作,能够使得能够进行振荡时钟信号相对于输入数据的同步化。

[2]<降低环路增益而将基于相位误差的校正值与频率控制数据相加>

在项1中,所述漂移校正电路基于利用所述相位同步环路电路检测出的相位误差来运算频率校正值,与所述频率同步环路电路相比具有更小的环路增益而将所述校正值与所述频率同步环路电路的频率控制数据相加。

由此,能够将校正值容易地反映到频率同步环路电路。

[3]<将频率牵引对象固定样式化>

在项2中,所述频率同步环路电路对于输入数据的特定的固定样式进行频率牵引动作。所述相位同步环路电路对于输入数据的任意样式进行相位牵引。

由此,能够有助于频率同步环路电路的简单化和低消耗电力,以此为前提,在漂移校正电路中,沿用用于与频率牵引完成后的任意样式对应的相位牵引的相位误差检测功能来对频率牵引完成后的任意样式进行校正值的运算成为可能。

[4]<频率变动校正的控制>

在项2中,具有控制部(22),该控制部(22)管理以下控制:响应于所述频率同步环路电路中的频率牵引完成的通知而对所述相位同步环路电路指示相位牵引动作的开始,响应于相位牵引的完成通知而对所述漂移校正电路指示所述校正值的运算,在运算出的所述校正值达到了规定值时,与所述频率同步环路电路相比具有更小的环路增益而将所述校正值与所述频率同步环路电路的频率控制数据相加,以对所述相位同步环路电路再次指示相位牵引动作的开始。

由此,使用与频率同步环路电路相比具有更小的环路增益的漂移校正电路来在相位牵引完成状态下对完成了牵引的振荡频率进行校正,因此成为能够未然地防止相位同步环路变得不稳定的风险而校正振荡频率的变动。

[5]<频率牵引后的频率同步环路的增益下降>

CDR电路(1A)具有:频率同步环路电路(2A),使振荡电路(16)的振荡时钟信号(CLKf)的频率与输入数据(Din)的频率同步;以及相位同步环路电路(3),输入所述振荡时钟信号来输出与所述输入数据的相位同步的相位同步时钟信号(CLKfp)。所述频率同步环路电路与频率牵引后的所述相位同步环路电路的相位牵引动作并行地或者在该相位牵引动作完成后,在环路增益被切换得小的状态下进行频率牵引动作。

由此,由于在把完成了牵引的频率同步环路电路的环路增益切换为小的环路增益的状态下进行频率牵引动作,因此成为能够即使是在相位牵引动作中,也在相位同步环路没有不期望地进行振荡的情况下,对频率同步环路电路中的振荡电路的频率变动进行校正。即使由于温度变化等而在振荡电路产生不期望的频率变动,也不重新进行使用输入数据样式的频率牵引动作,能够使得能够进行振荡时钟信号相对于输入数据的同步化。

[6]<可变增益电路>

在项5中,所述频率同步环路电路具有能够可变地切换环路增益的可变增益电路(13A)。

由此,能够简单地进行频率同步环路电路的环路增益的切换。

[7]<把任意样式设为频率牵引对象>

在项5中,所述频率同步环路电路对于输入数据的任意样式进行频率牵引动作。所述相位同步环路电路对于输入数据的任意样式进行相位同步。

由此,与利用特定的固定样式进行频率牵引动作的情况相比,虽然频率同步环路电路的结构变得复杂,但是不要求新设置如所述漂移校正电路那样的新的环路电路,能够利用频率同步环路电路的环路增益的切换来应对振荡频率的校正。

[8]<频率变动校正的控制>

在项6中,具有控制部(22A),该控制部(22A)进行如下控制:响应于所述频率同步环路电路中的频率牵引完成的通知来对所述相位同步环路电路指示相位牵引动作的开始,并且响应于相位牵引的完成通知来把所述频率同步环路电路的环路增益切换得小而指示频率牵引动作的开始,在频率牵引完成后再次对相位同步环路电路指示相位牵引动作的开始。

由此,由于使用切换为小的环路增益的频率同步环路电路来在相位牵引完成状态下对完成了牵引的振荡电路的振荡频率进行校正,因此成为能够未然地防止相位同步环路变得不稳定的风险而校正振荡频率的变动。

[9]<向半导体装置的接口电路的适用>

半导体装置(106)包括外部接口电路(101、102、102A)以及对供给至所述外部接口电路的数据进行处理的处理电路(104),所述外部接口电路具备项1的CDR电路(1、1A)作为输入所述数据的电路。

由此,能够有助于半导体装置中的所谓时钟嵌入型的数据接口的可靠性提高。

[10]<显示驱动设备>

在项9中,所述处理电路输入被供给至所述CDR电路的图像数据,把与输入的图像数据相应的灰度电压与显示定时同步地按像素单位进行输出。

由此,即使在作为影像输出接口的标准的显示器端口等中起因于温度变化、电源电压变动而振荡频率变动,也能够防止由此引起的输入数据的取入错误的发生。

[11]<频率牵引后的振荡电路的频率变动的校正>

CDR电路包括同步化电路(2、3、4、2A),该同步化电路(2、3、4、2A)形成使振荡电路(16)的振荡时钟信号(CLKf)的频率与输入数据(Din)的频率同步的频率同步环路以及输入所述振荡时钟信号来生成与所述输入数据的相位同步的相位同步时钟信号(CLKfp)的相位同步环路。同步化电路具有电路(20、21、14、13A),该电路(20、21、14、13A)对于利用所述频率同步环路的完成了频率牵引的频率,在利用相位同步环路的相位牵引动作中或相位牵引完成后,与所述频率同步环路相比具有更小的环路增益而对牵引完成的振荡频率进行更新。

由此,由于与频率同步环路相比具有更小的环路增益而对完成了牵引的振荡频率进行更新,因此成为能够即使是在相位牵引动作中,也在相位同步环路没有不期望地进行振荡的情况下对频率同步环路中的振荡电路的频率变动进行校正。即使由于温度变化等而在振荡电路产生了不期望的频率变动,也不重新进行使用输入数据样式的频率牵引动作,能够使得能够进行振荡时钟信号相对于输入数据的同步化。

[12]<校正用频率同步环路>

在项11中,所述进行更新的电路是设为如下的漂移校正电路(4),在利用所述频率同步环路的频率牵引后的利用所述相位同步环路的相位牵引动作中或者相位牵引完成后,基于所述输入数据与所述相位同步时钟信号的相位差来运算校正值,与所述频率同步环路相比具有更小的环路增益而能够利用所述校正值对所述振荡电路的振荡频率变动进行校正。

由此,即使是在通过所述频率同步环路对于输入数据的特定的固定样式进行频率牵引动作从而谋求频率同步环路的简单化和低消耗电力的情况下,在漂移校正中对于频率牵引完成后的任意样式进行校正值的运算也成为可能。

[13]<频率变动校正的控制>

在项12中,具有控制部(22),该控制部(22)管理如下控制:响应于所述频率同步环路中的频率牵引完成的通知而对所述相位同步环路指示相位牵引动作的开始,响应于相位牵引的完成通知而对所述漂移校正电路指示所述校正值的运算,在运算出的所述校正值达到了规定值时,与所述频率同步环路相比具有更小的环路增益而将所述校正值与所述频率同步环路的频率控制数据相加,以对所述相位同步环路再次指示相位牵引动作的开始。

由此,由于使用与频率同步环路相比具有更小的环路增益的漂移校正电路来在相位牵引完成状态下对完成了牵引的振荡频率进行校正,因此成为能够未然地防止相位同步环路变得不稳定的风险而校正振荡频率的变动。

[14]<频率牵引后的频率同步环路的增益下降>

在项11中,所述进行更新的电路是被配置在所述频率同步环路电路中并能够可变地切换环路增益的可变增益电路(13A)。所述可变增益电路与频率牵引后的所述相位同步环路的相位牵引动作并行地将环路增益切换得小或者在该相位牵引动作的完成后将环路增益切换得小。

由此,如果所述频率同步环路电路能够对于输入数据的任意样式进行频率牵引,则能够不新设置所述漂移校正电路那样的新的环路电路,利用频率同步环路的环路增益的切换来应对振荡频率的校正。

[15]<频率变动校正的控制>

在项14中,具有控制部(22A),该控制部(22A)进行如下控制:响应于所述频率同步环路中的频率牵引完成的通知而对所述相位同步环路指示相位牵引动作的开始,并且响应于相位牵引的完成通知而将所述频率同步环路的环路增益切换得小并指示频率牵引动作的开始,在频率牵引完成后再次对相位同步环路指示相位牵引动作的开始。

由此,由于在相位牵引完成状态下使用切换为小的环路增益的频率同步环路来对完成了牵引的振荡电路的振荡频率进行校正,因此成为能够未然地防止相位同步环路变得不稳定的风险而对振荡频率的变动进行校正。

2. 实施方式的详情

进一步详述实施方式。

<第一实施方式>

对作为第一实施方式使用了漂移校正电路1的CDR电路的例子进行说明。

在图1例示了第一实施方式的CDR电路。在同一图示出的CDR电路1具有频率同步环路电路2、相位同步环路电路3、漂移校正电路4以及同步化控制部22。

频率同步环路电路2使振荡电路(VCO)16的振荡时钟信号CLKf的频率与输入数据Din的频率同步。例如具有具体地例示的频率误差检测器11、频率校正值计算保持电路12、增益电路13、加法器14、将数字信号转换为模拟信号的DA转换器(DAC)15以及由电压控制振荡器(VCO)构成的振荡电路16,利用振荡电路16进行振荡的时钟信号CLKf被反馈给频率误差检测器11,作为整体构成负反馈环路。关于各个电路,只要采用公知的电路即可。例如频率误差检测器11能够利用计数器按每规定间隔对1、0反复那样的固定样式的输入数据Din和振荡时钟信号CLKf间的各个的边缘变化进行计数,根据双方的计数值之差来检测频率误差。频率校正值计算保持电路12具有对频率误差进行积分来削减该积分值的短周期的信号性分量的数字滤波功能以及保持利用该数字滤波功能所生成的信号代码的数据锁存功能等。

利用增益电路13对被保持在频率校正值计算保持电路12的数据提供必要的环路增益,通过加法器14并由DAC 15转换为模拟电压信号。频率校正计算保持电路12和增益电路13也能够通过数字滤波器来一体地构成。

VCO 16具有变容二极管,按与通过施加于变容二极管的模拟电压信号而产生的静电电容的变化相应的振荡频率来输出时钟信号CLKf。当考虑频率同步环路电路2的时钟信号CLKf的频率牵引动作(使时钟信号CLKf的频率与输入数据Din的频率一致的动作)时,在增益电路13设定得到必要的负反馈响应性所需要的比较大(高)的环路增益。高的环路增益等效于使环路带宽宽,能够加快对于VCO 16的振荡频率变动的响应性。

相位同步环路电路3输入所述振荡时钟信号CLKf以生成与输入数据Din的相位同步的时钟信号CLKfp(相位同步时钟信号CLKfp)。例如,具有具体地例示的相位误差检测器17、相位校正值计算保持电路18以及相位插值器19,由相位插值器19校正的时钟信号CLKfp被反馈给相位误差检测器17,作为整体构成负反馈环路。关于各个电路,采用公知的电路即可。例如相位误差检测器17能够通过输出与相位差相应的电压(相位差电压)的所谓的数字相位比较器构成。相位校正值计算保持电路18具有对相位差电压进行积分来削减该积分值的短周期的信号性成分的数字滤波功能以及保持通过该数字滤波功能生成的信号代码的数据锁存功能等。

相位插值器19与被保持于相位校正值计算保持电路18的信号代码相应地调整时钟信号CLKf的相位超前/滞后来输出时钟信号CLKfp,进行要使时钟信号CLKfp的相位与输入数据Din的边缘的定时同步而最适化的相位牵引。

漂移校正电路4是设为如下的漂移校正电路:在利用所述频率同步环路电路2的频率牵引后的利用所述相位同步环路电路3的相位牵引动作中或者在相位牵引完成后,基于所述输入数据Din与所述时钟信号CLKfp的相位差来运算校正值,与所述频率同步环路电路2相比具有更小的环路增益而能够利用所述校正值校正所述振荡电路16的振荡频率。例如,由具体地例示的频率漂移校正值计算保持电路20、与所述增益电路13相比增益低的增益电路21以及加法器14构成。频率漂移校正值计算保持电路20具有削减对于积分值的短周期的信号性分量的数字滤波功能以及判别利用该数字滤波功能生成的积分值是否超过规定的阈值并保持超过时的积分值的代码数据的数据锁存功能等,所述积分值是对来自相位误差检测器17的相位差电压进行积分得到的。

利用增益电路21对被保持在频率漂移校正值计算保持电路20的代码数据提供比较低的环路增益,并将其供给至加法器14。此时,经由增益电路13对加法器14供给用于得到完成了频率牵引的时钟信号CLKf的频率的信号代码,把使环路增益低的增益电路21的输出相加到使环路增益高的增益电路13的输出,由此时钟信号CLKf的频率与增益电路13的输出相应地变化。此外,频率漂移校正值计算保持电路20和低增益电路21也能够通过数字滤波器一体地构成。

对于时钟信号CLKf的频率的由漂移校正电路4所致的变化以对由温度变化所致的时钟信号CLK的变动量进行补偿为目的的变化,频率漂移校正值计算保持电路20所输出的代码数据的大小以及增益电路21所提供的环路增益是为了对应该目的而决定的。总之,使低增益电路21的输出对于VCO 16的频率变动的响应性延迟。

例如,当CDR电路的连续动作时间变长时,由于温度变化而VCO 16的输出频率漂移。在漂移量小的期间,可利用相位同步环路电路3的相位校正进行时钟信号CLKfp的修正,但是当变大则不能完全校正,即频率锁定偏离。如在图5例示的那样,如果当前设为随着温度变化而VCO16的频率降低,则在不进行校正的情况下,VCO 16的振荡频率按原样地降低下去,并在某个时点频率锁定偏离。漂移校正电路4是当VCO 16的振荡频率降低到某个任意的值时校正向DAC 15的供给数据以使得不会成为该任意的值以下的漂移校正电路。由此,使得暂且牵引的时钟信号CLKf的频率锁定不偏移。

在图2例示了将图1的CDR电路1适用于数据接口的情况下的系统结构,特别是示出了CDR电路1中的同步化控制部22的具体例子。

在图2例示的系统成为:主机装置100连接于由控制接口101、数据接口102、处理控制器103以及处理电路104构成的设备,控制接口101输入主机装置100发出的命令,数据接口102输入主机装置100输出的数据,处理控制器103对命令进行解读,处理控制器103按照解读结果使处理电路104对输入数据进行处理。

数据接口102通过CDR电路1和采样电路5构成为所谓的时钟嵌入型的接口。采样电路5与由CDR电路1生成的时钟信号CLKfp同步地取入输入数据Din并提供给处理控制器103。

同步化控制部22对利用频率锁定检测器23的频率牵引(频率锁定)、利用相位锁定检测器24的相位送牵引(相位锁定)以及利用漂移校正电路4的频率校正的各动作进行控制。φ1是频率误差检测器11的动作指示信号,φ2是频率锁定的完成通知信号,φ3是对于相位误差检测器17的检测动作的指示信号,φ4是相位锁定的完成通知信号,φ5是对于频率漂移校正值计算保持电路20的动作的指示信号。

同步化控制部22对利用频率锁定检测器23的频率牵引(频率锁定)、利用相位锁定检测器24的相位送牵引(相位锁定)以及利用漂移校正电路4的频率校正的各动作进行控制。

在图3例示有利用同步化控制部22的对于CDR电路1的基本控制方式。最初开始利用频率锁定检测器23的频率校正动作、即时钟信号CLKf的频率牵引(频率锁定)动作。使用于该动作的输入数据Din在本实施方式中被限制为具有1、0反复那样的特定的数据样式。由此,当检测出频率锁定时,本次开始利用相位锁定检测器24的相位校正动作、即相位送牵引(相位锁定)动作。最初的相位牵引动作也可以与频率牵引动作同样地使用特定样式的输入数据Din,还可以使用不同的训练样式。在通过相位校正动作检测出相位锁定之后,开始利用漂移校正电路4的频率漂移校正。利用漂移校正电路4的对时钟信号CLKf的频率校正可以与相位锁定后的相位校正动作并行地进行,也可以在相位锁定后停止了相位校正动作的状态下进行。

在图4例示有CDR电路1的动作流程。首先,当按照来自主机装置100的命令,处理控制器103对CDR电路1提供活性化(ON)的指示时,同步化控制部22启动VCO 16,按照信号φ1使频率误差检测器11进行动作等,由此设为能够使频率同步环路电路2进行动作,开始数据Din的输入(S1)。由此,通过频率误差检测器11来检测输入数据Din与VCO 16的振荡时钟信号CLKf的频率之间的误差(S2),基于检测出的误差,频率校正值计算保持电路12计算校正值并进行保持(S3),判别振荡频率CLKf是否已锁定(S4),如果未锁定,则将该校正值反映给VCO 16(S5)。重复进行S2~S5的处理直到判别出频率锁定为止。当判别出时钟信号CLKf的频率锁定时,将VCO 16的设定被固定,通过信号φ2来结束利用频率同步环路电路2的频率误差检测,本次启动相位同步环路电路3(S6),通过信号φ3开始利用相位误差检测器17的相位误差检测(S7)。由此,基于输入数据Din与时钟信号CLKfp的相位差,由相位校正值计算保持电路18计算校正值,将计算出的校正值进行保持(S8)。通过被保持的校正值来对被输入的时钟信号CLKf的相位进行校正,并将其反映给时钟信号CLKfp(S9)。

之后,判别输入数据Din的全部是否被接收完成(S10),如果并未完成,则判别时钟信号CLKfp的相位是否与输入数据Din的相位一致而相位锁定、或者是否已经完成了相位锁定(S11),如果并未锁定或未完成锁定,则返回步骤S7,重复进行步骤S7~S11的处理直到相位锁定为止。此外,在至少经过了频率锁定完成的预测时间的规定的定时,输入数据Din从频带牵引用的特定的固定样式变化为本来的通信数据。

在通过相位同步环路电路3进行相位锁定时,通过信号φ4将其通知给同步化控制部22。如果该通知是初次的相位锁定的通知(S12),则同步化控制部22利用信号φ5启动频率漂移校正值计算保持电路20(S13),输入相位误差检测器17的输出(S14),基于相位变动超过阈值时的相位差的累积来运算用于对振荡电路16的频率漂移进行校正的校正值,并对其进行保持(S15)。通过所保持的校正值对振荡电路16的振荡频率进行校正(S16)。

在对时钟信号CLKf的频率进行校正之后,使相位同步环路电路3和漂移电路4同时启动,使进行相位校正的处理S7~S11和校正振荡频率的处理S14~S16并行地进行。频率漂移校正电路4一旦启动就保持启动的状态,如图3所示那样在启动之后与相位同步环路电路并行地进行动作。即,虽然在流程图中为了使作图简单而像是串行地进行漂移校正和相位校正那样进行了图示,但是实际上在进行了漂移校正之后的相位校正时,漂移校正电路也进行动作。漂移校正电路4由于响应慢,因此成为在相位校正充分收敛之后再次使漂移校正值变化。重复用于相位校正的处理S7~S11以及利用漂移校正电路4的对于频率漂移的VCO 16的振荡频率的校正处理S14~S16,直到接收完成为止。

根据第一实施方式,起到以下的作用效果。

(1)由于在相位牵引完成之后,通过与频率同步环路电路2相比具有更小的环路增益的漂移校正电路4来对VCO 16的振荡频率进行校正,因此成为能够即使是在相位牵引动作中也在相位同步环路没有不期望地进行振荡的情况下校正频率同步环路电路中的振荡电路的频率变动。即使由于温度变化等而在振荡电路VCO 16产生不期望的频率变动,也不重新进行使用输入数据Din的特定样式的频率牵引动作,能够使得能够进行振荡时钟信号CLKf对于输入数据Din的同步化。

(2)漂移校正电路4基于由所述相位同步环路电路3检测出的相位误差来运算频率校正值,与频率同步环路电路2相比具有更小的环路增益而利用加法器14把该校正值与频率同步环路电路2的频率控制数据相加,因此能够将校正值容易地反映到频率同步环路电路2。

(3)所述相位同步环路电路3必须对输入数据的任意样式进行相位牵引,这是不言而喻的,但是关于在其前级进行的频率牵引,并非一定不需要与其同样地能够对任意的样式进行频率牵引。在这一点上,第一实施方式中的频率检测器11把1、0反复那样的特定的固定样式作为频率牵引对象而谋求频率同步环路电路2的简单化以及低消耗电力。以此为前提,漂移校正电路4能够沿用与频率牵引完成后的任意样式对应的相位误差检测器17的误差检测功能来进行频率漂移的运算。

(4)如在图4的流程图中说明的那样,在第一实施方式中,使用与频率同步环路电路2相比具有更小的环路增益的漂移校正电路4来在相位牵引完成状态下对完成了频率牵引的振荡频率进行校正,因此能够通过利用漂移校正电路4的频率校正来未然地防止相位同步环路电路3进行过度的负反馈控制并且相位同步环路变得不稳定的风险,并校正振荡频率的变动。

<第二实施方式>

作为第二实施方式说明使用了漂移校正电路的CDR电路的例子。

在图6例示有第二实施方式的CDR电路1A。在同一图示出的CDR电路1A具有频率同步环路电路2A和相位同步环路电路3。不使用如在图1的第一实施方式中采用的那样的跨相位同步环路电路3和频率同步环路电路2的漂移校正电路4。在第二实施方式中,通过设为能够使频率同步环路电路2A的环路增益可变,从而对于VCO 16的频率漂移的频率校正也利用频率同步环路电路2A进行。

说明第二实施方式的CDR电路1A的具体例子。与图1之间的不同点为代替漂移校正电路4而采用的频率同步环路电路2A的结构。即,频率检测11A不只是1、0反复那样的特定的固定样式,还使得能够对于任意的样式检测频率误差,与频率误差检测器11相比电路规模变大。是为了应对必须对各种输入样式进行频率牵引的用途。虽然关于具体的电路结构省略图示,但是采用使用了计数器等的公知的电路结构即可。除此之外,频率同步环路电路2A代替固定增益电路3而采用能够可变地切换由频率校正值计算保持电路12所保持的对于校正值的环路增益的可变增益电路13A,由于不使用漂移校正电路4,因此设为不使用加法器14。在该频率同步环路电路2A中紧接着启动之后的频率牵引动作中对可变增益电路13A设定高的环路增益,使得能够具有比较高的响应性地来将利用频率误差检测器11A的误差反映到VCO 16的振荡频率。在频率牵引后的相位牵引完成之后,对可变增益电路13A设定低的环路增益,使得能够具有比较低的响应性地来将利用频率误差检测器11A的误差反映到VCO16的振荡频率。只要能够对由温度变化等所致的VCO 16的振荡频率变动(频率下降)沿对其进行补偿的方向校正频率就是足够的,这是因为相反地如果稍有变动就敏感地响应则相位同步会偏离,时钟信号CLKfp的频率变得不稳定。该情形与第一实施方式相同。同步化控制部20A进行与振荡时钟的同步动作相应的频率同步环路电路中的环路增益的切换控制,并且与上述同样地进行频率同步环路电路的控制和相位同步环路电路3的控制。此外,对实现与图1同样的功能的电路块附加与其相同的参照标记并省略其详细说明。

在图7例示将图6的CDR电路1A适用于数据接口的情况下的系统结构。在图7所例示的系统成为:主机装置100连接于由控制接口101、数据接口102A、处理控制器103以及处理电路104构成的设备,控制接口101输入主机装置100发出的命令,数据接口102A输入主机装置100所输出的数据,处理控制器103对命令进行解读,处理控制器103按照解读结果使处理电路104对输入数据进行处理。

数据接口102A通过CDR电路1A和采样电路5构成为所谓的时钟嵌入型的接口。采样电路5与由CDR电路1A生成的时钟信号CLKfp同步地取入输入数据Din并提供给处理控制器103。

CDR电路1A中的同步化控制部22A具有频率锁定检测器23A和相位锁定检测器24A。同步化控制部22A对利用频率锁定检测器23A的频率牵引(频率锁定)、利用相位锁定检测器24的相位牵引(相位锁定)以及环路增益的切换进行控制。φ11是频率误差检测器11A的动作指示信号,φ12是频率锁定的完成通知信号,φ13是对于相位误差检测器17的检测动作的指示信号,φ14是相位锁定的完成通知信号,φ15是对于可变增益电路13A的环路增益的切换信号。对具有与图2相同功能的电路块附加相同的参照标记并省略其详细说明。

在图8例示有利用同步化控制部22A的对于CDR电路1A的基本的控制方式。最初开始利用频率锁定检测器23A的频率校正动作、即时钟信号CLKf的频率牵引(频率锁定)动作。使用于该动作的输入数据Din与第一实施方式不同,具有任意的数据样式。由此,当检测出频率锁定时,本次开始利用相位锁定检测器24A的相位校正动作、即相位送牵引(相位锁定)动作。相位牵引动作也与频率牵引动作同样地对于具有任意的样式的输入数据Din进行。当通过相位校正动作检测出相位锁定时,相位锁定检测器24A将可变增益电路13A的环路增益切换得低,频率同步环路电路2A具有低的环路增益来对VCO16的振荡时钟信号校正变动。利用该低环路增益下的频率同步环路电路2A的对VCO 16的漂移校正在最初的相位锁定之后进行,在最初的相位锁定之后与相位同步环路电路3的相位校正动作并行地进行漂移校正。或者,也可以在相位同步环路电路3启动时同时启动频率同步环路电路2A。

在图9例示有CDR电路1A的动作流程。首先,当按照来自主机装置100的命令,处理控制器103对CDR电路1A提供活性化(ON)的指示时,同步化控制部22A启动VCO 16,通过信号φ1使频率误差检测器11A进行动作等,从而设为能够使频率同步环路电路2A进行动作,开始数据Din的输入(S21)。由此,由频率误差检测器11A检测输入数据Din与VCO 16的振荡时钟信号CLKf的频率之间的误差(S22),基于检测出的误差,频率校正值计算保持电路12计算校正值并进行保持(S23),判别振荡频率CLKf是否已锁定(S24),如果未锁定,则将该校正值反映给VCO 16(S25)。重复进行S22~S25的处理直到判别出频率锁定为止。当判别出时钟信号CLKf的频率锁定时,将VCO 16的设定固定,通过信号φ2结束利用频率同步环路电路2A的频率误差检测,本次启动相位同步环路电路3(S26),通过信号φ3开始利用相位误差检测器17的相位误差检测(S27),基于输入数据Din与时钟信号CLKfp的相位差,由相位校正值计算保持电路18计算校正值,并保持计算出的校正值(S28)。通过所保持的校正值来校正时钟信号CLKf的相位,将其反映到时钟信号CLKfp(S29)。

之后,判别输入数据Din的全部是否被接收完成(S30),如果并未接收完成,则判别时钟信号CLKfp的相位是否与输入数据Din的相位一致而相位锁定、或者是否已经完成相位锁定(S31),如果并未锁定或未完成锁定,则返回步骤S27,重复步骤S27~S31的处理直到相位锁定为止。关于接收完成判断由处理控制器103进行。

在由相位同步环路电路3进行相位锁定时,通过信号φ4将其通知给同步化控制部22A。如果该通知是初次的相位锁定的通知(S32),则同步化控制部22A利用信号φ15对于频率同步环路电路2A启动频率漂移校正模式(S33)。即,利用信号φ15将可变增益电路13A的环路增益从高增益切换为低增益来使频率同步环路电路2A进行动作。由此,频率校正值计算保持电路12输入由频率误差检测器11A检测出的频率误差(S34),基于所输入的误差,频率校正值计算保持电路12运算用于校正振荡电路16的频率漂移的校正值,并对其进行保持(S35)。关于所保持的校正值,利用低环路增益校正振荡电路16的振荡频率(S36)。

在校正了时钟信号CLKf的频率之后,再次使用相位同步环路电路3进行用于相位校正的处理S27~S31,在相位校正之后再次进行校正VCO 16的频率漂移的处理S34~S36。重复进行这些处理直到接收完成为止。

根据第二实施方式,起到以下的作用效果。

(1)由于在把完成了牵引的频率同步环路电路2A的环路增益切换为小的环路增益的状态下进行频率牵引动作,因此成为能够即使是在相位牵引动作中也在没有相位同步环路不期望地进行振荡的情况下,校正频率同步环路电路2A中的VCO 16的频率变动。即使由于温度变化等而在VCO 16产生不期望的频率变动,也不重新进行使用了输入数据样式的频率牵引动作,能够使得能够进行对于输入数据的时钟信号CLKf的同步化。

(2)频率同步环路电路2A能够通过可变增益电路13A来简单地进行频率同步环路的环路增益的切换。

(3)频率同步环路电路2A对于输入数据Din的任意样式进行频率牵引动作,因此与如第一实施方式那样的按固定样式进行频率牵引动作的情况相比,虽然频率同步环路电路2A的结构变为复杂化,但是不要求新设置漂移校正电路4那样的新的环路电路,能够应对VCO 16的频率漂移。

(4)使用切换为小的环路增益的频率同步环路电路2A在相位牵引完成状态下对完成了牵引的VCO 16的振荡频率进行校正,因此能够未然地防止相位同步环路变得不稳定的风险,能够校正VCO 16的频率漂移。

<第三实施方式>

作为第三实施方式,在图10例示有液晶驱动器作为在外部接口电路具备CDR电路的半导体装置。液晶驱动器(LCD驱动器)106与形成于玻璃基板上的液晶显示器(LCD_DSP)120和电源电路121一起构成LCD模块(或者LCD面板)108。

液晶驱动器(LCD驱动器)106具有控制接口101和输入图像数据的数据接口102(102A)作为与主机装置(HST)100连接的外部接口电路。从主机装置100经由控制接口电路101供给命令,经由数据接口102(102A)供给显示数据。在数据接口102(102A)适用CDR电路1(1A),构成所谓的时钟嵌入型的数据接口。作为对供给至控制接口101的命令和供给至数据接口102(102A)的图像数据进行处理的处理电路106,具有作为处理控制器的显示控制器103、存储器110、灰度电压控制器111、源极驱动器112以及栅极控制驱动器113。显示控制器103使用所供给的命令的解读结果和命令参数来对内部进行控制,并且将供给的显示数据保存到存储器110。灰度电压控制器111生成多个灰度电压,按照与显示定时同步地从存储器110提供的以显示线为单位的显示数据来按像素单位选择灰度电压并提供到源极驱动器112。显示控制器103在显示动作中使用栅极控制驱动器113来按每一显示帧与水平扫描期间同步地依次选择驱动液晶显示器120的栅极线。另外,显示控制器103与水平扫描期间同步地从存储器110将一个栅极线的量的显示数据(显示线数据)输送到灰度电压控制器111,使用所输送的显示线数据来按该数据的像素单位选择灰度电压。所选择的灰度电压被供给至构成源极驱动器112的多个驱动放大器。多个驱动放大器按显示线数据单位并联地驱动液晶显示器120的多个源极线。

由于在数据接口102(102A)适用上述CDR电路1(1A),因此能够提高LCD驱动器106中的所谓时钟嵌入型的数据接口的可靠性。即使产生由VCO 16的温度上升所致的振荡频率下降,也能够通过VCO 16的振荡时钟信号CLKf的频率校正来校正其变动量。在该校正时,不要求停止输入数据Din的输入来从频率牵引重新进行时钟同步。

虽然以上基于实施方式具体说明了由本发明人作出的发明,但是本发明是被不限定于此的发明,能够在不脱离其宗旨的范围内进行各种变更,这是不言而喻的。

本发明不限定于LCD驱动器,能够具备时钟嵌入型的接口而广泛地适用于半导体装置、系统。频率同步环路电路和相位同步环路电路的结构不限定于上述实施方式而能够适当地进行变更。环路增益的设定、切换不限定于上述实施方式,能够使用数字滤波器等各种手段进行。

附图标记的说明

1、1A:CDR电路;2、2A:频率同步环路电路;3:相位同步环路电路;4:漂移校正电路;Din:输入数据;11、11A:频率误差检测器;12:频率校正值计算保持电路;13、13A:增益电路;14:加法电路;15:DA转换器(DAC);16:振荡电路(VCO);CLKf:频率同步环路电路的振荡时钟信号;CLKfp:从相位同步环路电路输出的时钟信号;17:相位误差检测电路;18:相位校正值计算保持电路;19:相位插值器;20:频率漂移校正值计算保持电路;21:低环路增益的增益电路;22:同步化控制部;101:控制接口;102、102A:数据接口;103:处理控制器;104:处理电路;106:液晶驱动器(LCD驱动器);108:LCD模块(或者LCD面板);100:主机装置(HST);110:存储器;111:灰度电压控制器;112:源极驱动器;113:栅极控制驱动器;120:液晶显示器(LCD_DSP)。

Claims (15)

1.一种CDR电路,具有:

频率同步环路电路,使振荡电路的振荡时钟信号的频率与输入数据的频率同步;

相位同步环路电路,输入所述振荡时钟信号而输出与所述输入数据的相位同步的相位同步时钟信号;以及

漂移校正电路,设为在利用所述频率同步环路电路的频率牵引之后的利用所述相位同步环路电路的相位牵引动作中或者在相位牵引完成后,基于所述输入数据与所述相位同步时钟信号的相位差来运算校正值,与所述频率同步环路电路相比具有更小的环路增益而能够利用所述校正值对所述振荡电路的振荡频率进行校正。

2.根据权利要求1所述的CDR电路,

所述漂移校正电路基于利用所述相位同步环路电路检测出的相位误差来运算频率校正值,与所述频率同步环路电路相比具有更小的环路增益而将所述校正值与所述频率同步环路电路的频率控制数据相加。

3.根据权利要求2所述的CDR电路,

所述频率同步环路电路对于输入数据的特定的固定样式进行频率牵引动作,

所述相位同步环路电路对于输入数据的任意样式进行相位牵引。

4.根据权利要求2所述的CDR电路,

具有控制部,该控制部管理以下控制:响应于所述频率同步环路电路中的频率牵引完成的通知而对所述相位同步环路电路指示相位牵引动作的开始,响应于相位牵引的完成通知而对所述漂移校正电路指示所述频率校正值的运算,在运算出的所述校正值达到了规定值时,与所述频率同步环路电路相比具有更小的环路增益而将所述校正值与所述频率同步环路电路的频率控制数据相加,以对所述相位同步环路电路再次指示相位牵引动作的开始。

5.一种CDR电路,具有:

频率同步环路电路,使振荡电路的振荡时钟信号的频率与输入数据的频率同步;以及

相位同步环路电路,输入所述振荡时钟信号而输出与所述输入数据的相位同步的相位同步时钟信号,

所述频率同步环路电路与频率牵引后的所述相位同步环路电路的相位牵引动作并行地或者在该相位牵引动作完成之后,在环路增益被切换得小的状态下进行频率牵引动作。

6.根据权利要求5所述的CDR电路,

所述频率同步环路电路具有能够可变地切换环路增益的可变增益电路。

7.根据权利要求5所述的CDR电路,

所述频率同步环路电路对于输入数据的任意样式进行频率牵引动作,

所述相位同步环路电路对于输入数据的任意样式进行相位同步。

8.根据权利要求6所述的CDR电路,

具有控制部,该控制部进行如下控制:响应于所述频率同步环路电路中的频率牵引完成的通知来对所述相位同步环路电路指示相位牵引动作的开始,并且响应于相位牵引的完成通知来把所述频率同步环路电路的环路增益切换得小而指示频率牵引动作的开始,在频率牵引完成之后再次对相位同步环路电路指示相位牵引动作的开始。

9.一种半导体装置,包括外部接口电路以及对供给至所述外部接口电路的数据进行处理的处理电路,所述外部接口电路具备根据权利要求1所述的CDR电路作为输入所述数据的电路。

10.根据权利要求9所述的半导体装置,

所述处理电路输入被供给至所述CDR电路的图像数据,把与输入的图像数据相应的灰度电压与显示定时同步地按像素单位进行输出。

11.一种CDR电路,包括同步化电路,该同步化电路形成使振荡电路的振荡时钟信号的频率与输入数据的频率同步的频率同步环路以及输入所述振荡时钟信号来生成与所述输入数据的相位同步的相位同步时钟信号的相位同步环路,在该CDR电路中,

所述同步化电路具有如下电路:该电路在利用相位同步环路的相位牵引动作中或者相位牵引完成之后,对于利用所述频率同步环路电路的完成了频率牵引的频率,与所述频率同步环路相比具有更小的环路增益来更新牵引完成的振荡频率。

12.根据权利要求11所述的CDR电路,

更新振荡频率的电路是设为如下的漂移校正电路:在利用所述频率同步环路的频率牵引之后的利用所述相位同步环路的相位牵引动作中或者在相位牵引完成后,基于所述输入数据与所述相位同步时钟信号的相位差来运算校正值,与所述频率同步环路相比具有更小的环路增益而能够利用所述校正值对所述振荡电路的振荡频率变动进行校正。

13.根据权利要求12所述的CDR电路,

具有控制部,该控制部管理如下控制:响应于所述频率同步环路电路中的频率牵引完成的通知而对所述相位同步环路电路指示相位牵引动作的开始,响应于相位牵引的完成通知而对所述漂移校正电路指示所述频率校正值的运算,在运算出的所述频率校正值达到了规定值时,降低环路增益而将该频率校正值与所述频率同步环路电路的频率控制数据相加来再次对所述相位同步环路电路指示相位牵引动作的开始。

14.根据权利要求11所述的CDR电路,

更新振荡频率的电路是被配置在所述频率同步环路电路中并能够可变地切换环路增益的可变增益电路,

所述可变增益电路与频率牵引后的所述相位同步环路电路的相位牵引动作并行地将环路增益切换得小或者在该相位牵引动作的完成后将环路增益切换得小。

15.根据权利要求14所述的CDR电路,

具有控制部,该控制部进行如下控制:响应于所述频率同步环路电路中的频率牵引完成的通知而对所述相位同步环路电路指示相位牵引动作的开始,并且响应于相位牵引的完成通知而将环路增益切换得小而对所述频率同步环路电路指示频率牵引动作的开始,在频率牵引完成后再次对相位同步环路电路指示相位牵引动作的开始。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014-144119 | 2014-07-14 | ||

| JP2014144119A JP6430738B2 (ja) | 2014-07-14 | 2014-07-14 | Cdr回路及び半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN105262483A CN105262483A (zh) | 2016-01-20 |

| CN105262483B true CN105262483B (zh) | 2020-12-11 |

Family

ID=55068387

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201510410326.6A Active CN105262483B (zh) | 2014-07-14 | 2015-07-14 | Cdr电路和半导体装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US9413517B2 (zh) |

| JP (1) | JP6430738B2 (zh) |

| CN (1) | CN105262483B (zh) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2016021629A (ja) * | 2014-07-14 | 2016-02-04 | シナプティクス・ディスプレイ・デバイス合同会社 | Cdr回路及び半導体装置 |

| JP6536347B2 (ja) * | 2015-10-20 | 2019-07-03 | 富士通株式会社 | 周波数検出方法 |

| US9843439B2 (en) * | 2016-01-27 | 2017-12-12 | Ciena Corporation | System and method for managing holdover |

| US10348414B2 (en) * | 2016-06-30 | 2019-07-09 | Avago Technologies International Sales Pte. Limited | Clock-and-data recovery (CDR) circuitry for performing automatic rate negotiation |

| KR102480913B1 (ko) | 2016-07-11 | 2022-12-26 | 삼성전자주식회사 | 데이터를 전송하기 위한 방법 및 그 전자 장치 |

| CN107800427B (zh) * | 2016-09-05 | 2021-04-06 | 创意电子股份有限公司 | 时脉数据回复模块 |

| CN106712768A (zh) * | 2016-12-12 | 2017-05-24 | 深圳市紫光同创电子有限公司 | 一种去毛刺频率锁定电路 |

| KR102633143B1 (ko) * | 2016-12-23 | 2024-02-02 | 삼성전자주식회사 | 무선 채널 분류를 기초로 디지털 루프 필터 이득을 조절하는 자동 주파수 제어기, 상기 자동 주파수 제어기를 포함하는 무선 통신 장치, 자동 주파수 제어 방법 및 무선 통신 방법 |

| CN107682007B (zh) * | 2017-09-22 | 2021-01-15 | 哈尔滨工业大学 | 基于双环路的快锁定低抖动的时钟数据恢复电路 |

| CN107911113B (zh) * | 2017-10-31 | 2021-01-12 | 北京集创北方科技股份有限公司 | 时钟数据恢复电路及其环路带宽调节方法、处理器 |

| CN108199710B (zh) * | 2017-12-25 | 2021-06-29 | 深圳市紫光同创电子有限公司 | 一种振荡器校正电路及振荡器校正方法 |

| US11349485B2 (en) * | 2019-01-28 | 2022-05-31 | Mediatek Inc. | Clock and data recovery and associated signal processing method |

| CN111435827B (zh) * | 2020-01-14 | 2023-11-28 | 珠海市杰理科技股份有限公司 | 一种快速起振电路、方法、晶体振荡器以及集成芯片 |

| US11038602B1 (en) | 2020-02-05 | 2021-06-15 | Credo Technology Group Limited | On-chip jitter evaluation for SerDes |

| US10992501B1 (en) | 2020-03-31 | 2021-04-27 | Credo Technology Group Limited | Eye monitor for parallelized digital equalizers |

| KR20210129327A (ko) * | 2020-04-20 | 2021-10-28 | 주식회사 엘엑스세미콘 | 데이터구동장치 및 이의 구동 방법 |

| US10892763B1 (en) * | 2020-05-14 | 2021-01-12 | Credo Technology Group Limited | Second-order clock recovery using three feedback paths |

| US11855648B2 (en) | 2022-01-14 | 2023-12-26 | Samsung Display Co., Ltd. | Clock pattern detection and correction |

| CN115985221B (zh) * | 2023-03-21 | 2023-07-21 | 深圳通锐微电子技术有限公司 | 源极驱动器、频宽调整方法和显示面板 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62253224A (ja) * | 1986-01-14 | 1987-11-05 | Toshiba Corp | 位相同期回路 |

| JPH01293718A (ja) * | 1988-05-20 | 1989-11-27 | Hitachi Ltd | 位相同期回路 |

| JP2005006187A (ja) * | 2003-06-13 | 2005-01-06 | Renesas Technology Corp | Pll回路 |

| CN102820886A (zh) * | 2012-08-10 | 2012-12-12 | 硅谷数模半导体(北京)有限公司 | 信号检测方法、装置和具有该装置的pll和cdr系统 |

| JP2013005144A (ja) * | 2011-06-15 | 2013-01-07 | Renesas Electronics Corp | シリアル−パラレル変換回路、クロックデータリカバリ回路、表示装置用駆動回路及びシリアル−パラレル変換方法 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08331118A (ja) * | 1995-06-02 | 1996-12-13 | Yupiteru Ind Co Ltd | デジタル無線電話装置の基準クロック再生方法及び装置 |

| JP2000243042A (ja) * | 1999-02-19 | 2000-09-08 | Matsushita Electric Ind Co Ltd | クロックリカバリ装置 |

| JP2002198805A (ja) * | 2000-12-22 | 2002-07-12 | Asahi Kasei Microsystems Kk | Pll回路 |

| US6753711B2 (en) * | 2002-06-26 | 2004-06-22 | Comtech Ef Data | Digital summing phase-lock loop circuit with sideband control and method therefor |

| NZ524537A (en) * | 2003-03-04 | 2005-08-26 | Tait Electronics Ltd | Improvements relating to frequency and/or phase lock loops |

| US6803827B1 (en) * | 2003-04-09 | 2004-10-12 | Analog Devices, Inc. | Frequency acquisition system |

| JP3939715B2 (ja) * | 2004-08-20 | 2007-07-04 | 日本テキサス・インスツルメンツ株式会社 | 位相同期ループ回路 |

| JP4106069B2 (ja) * | 2004-08-27 | 2008-06-25 | 松下電器産業株式会社 | Pll周波数シンセサイザ |

| US7932784B1 (en) * | 2005-03-17 | 2011-04-26 | Rf Micro Devices, Inc. | Frequency and phase locked loop synthesizer |

| TWI346460B (en) * | 2006-10-31 | 2011-08-01 | Realtek Semiconductor Corp | A clock and data recovery circuit and a method for adjusting loop bandwidth used thereby |

| US20090108891A1 (en) * | 2007-10-26 | 2009-04-30 | Matsushita Electric Industrial Co., Ltd. | Bandwidth control in a mostly-digital pll/fll |

| JP2012044446A (ja) | 2010-08-19 | 2012-03-01 | Renesas Electronics Corp | クロックデータリカバリ回路 |

| JP2012049863A (ja) * | 2010-08-27 | 2012-03-08 | Renesas Electronics Corp | 半導体装置 |

-

2014

- 2014-07-14 JP JP2014144119A patent/JP6430738B2/ja active Active

-

2015

- 2015-07-09 US US14/795,494 patent/US9413517B2/en active Active

- 2015-07-14 CN CN201510410326.6A patent/CN105262483B/zh active Active

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62253224A (ja) * | 1986-01-14 | 1987-11-05 | Toshiba Corp | 位相同期回路 |

| JPH01293718A (ja) * | 1988-05-20 | 1989-11-27 | Hitachi Ltd | 位相同期回路 |

| JP2005006187A (ja) * | 2003-06-13 | 2005-01-06 | Renesas Technology Corp | Pll回路 |

| JP2013005144A (ja) * | 2011-06-15 | 2013-01-07 | Renesas Electronics Corp | シリアル−パラレル変換回路、クロックデータリカバリ回路、表示装置用駆動回路及びシリアル−パラレル変換方法 |

| CN102820886A (zh) * | 2012-08-10 | 2012-12-12 | 硅谷数模半导体(北京)有限公司 | 信号检测方法、装置和具有该装置的pll和cdr系统 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20160013929A1 (en) | 2016-01-14 |

| JP6430738B2 (ja) | 2018-11-28 |

| US9413517B2 (en) | 2016-08-09 |

| JP2016021628A (ja) | 2016-02-04 |

| CN105262483A (zh) | 2016-01-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN105262483B (zh) | Cdr电路和半导体装置 | |

| KR101743455B1 (ko) | 데이터 수신 장치 | |

| CN101098220B (zh) | 一种基于数字锁相环的时钟同步方法及其系统 | |

| US7679453B2 (en) | Phase-locked loop capable of dynamically adjusting phase of output signal according to detection result of phase/frequency detector, and method thereof | |

| US7366271B2 (en) | Clock and data recovery device coping with variable data rates | |

| TWI449341B (zh) | 訊號傳輸系統以及訊號傳輸方法 | |

| CN102629878B (zh) | 用于发射器或接收器的信号发生器、发射器和接收器 | |

| US8923468B2 (en) | Clock and data recovery circuit selectively configured to operate in one of a plurality of stages and related method thereof | |

| US9147376B2 (en) | Display device and method | |

| KR20140109131A (ko) | 이미지 데이터를 압축/압축해제할 수 있는 디스플레이 인터페이스, 이의 동작 방법, 및 이를 포함하는 디스플레이 장치 | |

| KR20080044977A (ko) | 위상 동기 루프 및 위상 동기 루프의 동작 방법 | |

| US11728815B2 (en) | Semiconductor device | |

| KR102655530B1 (ko) | 스트림 클럭 생성 장치 및 이를 포함하는 임베디드 디스플레이포트 시스템 | |

| CN105306049A (zh) | Cdr电路和半导体装置 | |

| US11424746B1 (en) | Reference-less clock and data recovery device and method | |

| US10483989B2 (en) | Phase-locked loop, phase-locking method, and communication unit | |

| JP2010081513A (ja) | 信号処理装置及び信号処理方法 | |

| JP2010081512A (ja) | 信号処理装置及び信号処理方法 | |

| US11646862B2 (en) | Reception device and transmission and reception system | |

| CN109818614B (zh) | 时序控制方法、时序控制芯片和显示装置 | |

| US7295821B2 (en) | Multiple base station automatic frequency control architecture in wireless communication system | |

| US20080151117A1 (en) | Horizontal synchronous circuit, display device, and clock adjusting method | |

| EP1265365A2 (en) | Frequency synchronous apparatus and frequency synchronous control method | |

| CN109391262B (zh) | 时钟恢复装置及方法 | |

| CN114978159A (zh) | Cdr控制环路频率校正方法、装置、环路和接收器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| CB02 | Change of applicant information |

Address after: Tokyo, Japan, Japan Applicant after: Sin Knapp Dick J Japan Contract Society Address before: Tokyo, Japan, Japan Applicant before: Xin Napudikesi display contract commercial firm |

|

| COR | Change of bibliographic data | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| GR01 | Patent grant | ||

| GR01 | Patent grant |