WO2015114802A1 - 半導体集積回路装置および電源システム - Google Patents

半導体集積回路装置および電源システム Download PDFInfo

- Publication number

- WO2015114802A1 WO2015114802A1 PCT/JP2014/052286 JP2014052286W WO2015114802A1 WO 2015114802 A1 WO2015114802 A1 WO 2015114802A1 JP 2014052286 W JP2014052286 W JP 2014052286W WO 2015114802 A1 WO2015114802 A1 WO 2015114802A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- voltage

- mosfet

- input electrode

- gate electrode

- integrated circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of DC power input into DC power output

- H02M3/02—Conversion of DC power input into DC power output without intermediate conversion into AC

- H02M3/04—Conversion of DC power input into DC power output without intermediate conversion into AC by static converters

- H02M3/10—Conversion of DC power input into DC power output without intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M3/145—Conversion of DC power input into DC power output without intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal

- H02M3/155—Conversion of DC power input into DC power output without intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only

- H02M3/156—Conversion of DC power input into DC power output without intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only with automatic control of output voltage or current, e.g. switching regulators

- H02M3/158—Conversion of DC power input into DC power output without intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only with automatic control of output voltage or current, e.g. switching regulators including plural semiconductor devices as final control devices for a single load

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of DC power input into DC power output

- H02M3/02—Conversion of DC power input into DC power output without intermediate conversion into AC

- H02M3/04—Conversion of DC power input into DC power output without intermediate conversion into AC by static converters

- H02M3/10—Conversion of DC power input into DC power output without intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M3/145—Conversion of DC power input into DC power output without intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal

- H02M3/155—Conversion of DC power input into DC power output without intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only

- H02M3/156—Conversion of DC power input into DC power output without intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only with automatic control of output voltage or current, e.g. switching regulators

- H02M3/158—Conversion of DC power input into DC power output without intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only with automatic control of output voltage or current, e.g. switching regulators including plural semiconductor devices as final control devices for a single load

- H02M3/1588—Conversion of DC power input into DC power output without intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only with automatic control of output voltage or current, e.g. switching regulators including plural semiconductor devices as final control devices for a single load comprising at least one synchronous rectifier element

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/08—Circuits specially adapted for the generation of control voltages for semiconductor devices incorporated in static converters

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/06—Modifications for ensuring a fully conducting state

- H03K17/063—Modifications for ensuring a fully conducting state in field-effect transistor switches

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/0003—Details of control, feedback or regulation circuits

- H02M1/0009—Devices or circuits for detecting current in a converter

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/0003—Details of control, feedback or regulation circuits

- H02M1/0032—Control circuits allowing low power mode operation, e.g. in standby mode

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/0048—Circuits or arrangements for reducing losses

- H02M1/0054—Transistor switching losses

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K2217/00—Indexing scheme related to electronic switching or gating, i.e. not by contact-making or -breaking covered by H03K17/00

- H03K2217/0036—Means reducing energy consumption

-

- H10W72/926—

-

- H10W90/753—

-

- H10W90/766—

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02B—CLIMATE CHANGE MITIGATION TECHNOLOGIES RELATED TO BUILDINGS, e.g. HOUSING, HOUSE APPLIANCES OR RELATED END-USER APPLICATIONS

- Y02B70/00—Technologies for an efficient end-user side electric power management and consumption

- Y02B70/10—Technologies improving the efficiency by using switched-mode power supplies [SMPS], i.e. efficient power electronics conversion e.g. power factor correction or reduction of losses in power supplies or efficient standby modes

Definitions

- the present invention relates to a semiconductor integrated circuit device and a power supply system, for example, a semiconductor integrated circuit device used for converting a voltage and a power supply system using the semiconductor integrated circuit device.

- a power supply system that converts a DC voltage having a predetermined voltage value into a DC voltage having a voltage value different from the predetermined voltage value is known as a so-called DC / DC converter.

- DC / DC converters are used in various electronic devices.

- An example of the electronic device is a computer.

- a power supply voltage supplied to a microprocessor hereinafter referred to as a CPU

- a DC / DC converter is formed by a DC / DC converter.

- a power supply system such as a DC / DC converter has a coil and a plurality of switch elements that periodically change the direction of current flowing through the coil.

- Each of the plurality of switch elements is constituted by a transistor such as a field effect transistor (hereinafter referred to as MOSFET).

- MOSFET field effect transistor

- FIG. 1D shows a MOSFET structure in which a first gate electrode 10 and a second gate electrode 12 are stacked vertically.

- a MOSFET in which a gate electrode 26 (hereinafter referred to as a first gate electrode) and a gate electrode 30 (hereinafter referred to as a second gate electrode) are stacked vertically. The structure of is shown.

- the first gate electrode and the second gate electrode are stacked in the vertical direction, thereby achieving high integration as taught in Patent Document 1, for example. It is possible to reduce the capacitance between the second gate electrode and the drain region of the MOSFET while maintaining it. As a result, the high frequency characteristics of the MOSFET can be improved. By improving the high frequency characteristics, the loss of the DC / DC converter is reduced and the efficiency can be improved. Improvement of the efficiency of the DC / DC converter is an important matter because it leads to reduction of power consumption in an electronic device using the DC / DC converter, for example.

- Patent Documents 1 and 2 were examined.

- Patent Document 1 shows that the first gate electrode of the MOSFET is set to a predetermined positive voltage and an input signal is supplied to the second gate electrode.

- Patent Document 2 shows that the first gate electrode is connected to the source of the MOSFET.

- the inventors of the present application have studied that if the voltage supplied to the first gate electrode is changed to a positive voltage or a negative voltage with respect to the voltage supplied to the source of the MOSFET, the characteristics (on-resistance) of the MOSFET Value, capacity value) was found to change. The present invention has been made based on this finding.

- An object of the present invention is to provide a power supply system capable of improving efficiency and a semiconductor integrated circuit device used therefor.

- a semiconductor integrated circuit device includes a first voltage terminal, a second voltage terminal, an output terminal, a first MOSFET connected between the first voltage terminal and the output terminal, a second voltage terminal, and an output terminal. And a second MOSFET connected between the first and second MOSFETs.

- the first MOSFET has a first input electrode, a drain, and a source

- the second MOSFET is disposed closer to the drain than the first input electrode, the drain, the source, and the first input electrode.

- a second input electrode is disposed closer to the drain than the first input electrode, the drain, the source, and the first input electrode.

- An input signal for complementarily turning on / off the first MOSFET and the second MOSFET is supplied to each first input electrode of the first MOSFET and the second MOSFET. Thereby, a current is alternately supplied from the first voltage terminal and the second voltage terminal to the output terminal.

- the second MOSFET a negative voltage is supplied to the second input electrode disposed on the drain side of the first input electrode with respect to the voltage at the source of the second MOSFET.

- the parasitic capacitance generated between the first input electrode and the drain.

- the first MOSFET and the second MOSFET are complementarily turned on / off, but during the transition time from on to off or off to on, between the first voltage terminal and the second voltage terminal and between the first voltage terminal and the output terminal.

- a current flows between the second voltage terminal and the output terminal.

- the second input electrode and the first input electrode of the second MOSFET are embedded in the stacked first semiconductor region and third semiconductor region, respectively. Formed by layers.

- the first semiconductor region forms the drain of the second MOSFET

- the third semiconductor region forms the source of the second MOSFET.

- the second input electrode is disposed closer to the drain side of the second MOSFET than the first input electrode. Further, since they are stacked, high integration is possible. In this case, a channel of the second MOSFET is generated in the second semiconductor region interposed between the first semiconductor region and the third semiconductor region.

- the semiconductor integrated circuit device selectively supplies a positive voltage and a negative voltage to the second input electrode of the second MOSFET with respect to the voltage at the source of the second MOSFET. It comprises. By supplying a positive voltage with respect to the voltage at the source to the second input electrode of the second MOSFET, it is possible to reduce the on-resistance when the second MOSFET is turned on. By reducing the on-resistance of the second MOSFET, it is possible to reduce the loss in the second MOSFET.

- the loss can be reduced by reducing the transient time and the loss by reducing the on-resistance. It becomes possible to select.

- the selection circuit is supplied with the voltage supplied to the second input electrode in synchronization with the timing at which the second MOSFET is turned on / off according to the input signal supplied to the first input electrode. Select the polarity. Accordingly, it is possible to reduce the loss by reducing the transient time and the loss by reducing the on-resistance in accordance with the on / off of the second MOSFET.

- the semiconductor integrated circuit device includes a detection circuit that detects whether or not the current flowing through the output terminal exceeds a predetermined current value.

- the selection circuit changes the polarity of the voltage supplied to the second input electrode. This makes it possible to select between reducing the loss by reducing the transient time and reducing the loss by reducing the on-resistance according to the value of the load current required by the load coupled to the output terminal. .

- an appropriate voltage polarity for reducing the loss is selected according to the magnitude of the load current. As a result, the loss can be reduced according to the magnitude of the load current.

- the load current changes according to the load state at that time. Therefore, it is possible to select an appropriate means for reducing loss (transient time reduction and on-resistance reduction) according to the load.

- a semiconductor integrated circuit device includes: a first voltage terminal; a second voltage terminal; an output terminal; and a first MOSFET coupled between the first voltage terminal and the output terminal. And a second MOSFET coupled between the output terminal and the second voltage terminal.

- each of the first MOSFET and the second MOSFET includes a first input electrode, a drain, a source, and a second input electrode disposed on the drain side of the first input electrode.

- the first MOSFET and the second MOSFET are complementarily turned on / off by the input signal. By being turned on / off in a complementary manner, current is alternately supplied from the first voltage terminal and the second voltage terminal to the output terminal. The value of the current flowing through the output terminal varies depending on the load current required by the load coupled to the output terminal.

- the semiconductor integrated circuit device further includes a detection circuit that detects a value of a current flowing through the output terminal, and different voltages are applied to the second input electrodes of the first MOSFET and the second MOSFET in response to a detection signal from the detection circuit.

- a supply control circuit is provided.

- the loss is reduced by shortening the transient time in each of the first MOSFET and the second MOSFET, and the loss is reduced or the increase is suppressed by suppressing the on-resistance or suppressing the increase. It will be. As a result, it is possible to reduce the loss of the semiconductor integrated circuit device according to the load, and it is possible to improve the efficiency.

- the control circuit when the current flowing through the output terminal exceeds a predetermined current value, applies a positive voltage to the second gate electrode of each of the first MOSFET and the second MOSFET with respect to the voltage at each source. Supply sex voltage.

- a negative voltage is supplied to the second gate electrode of each of the first MOSFET and the second MOSFET with respect to the voltage at each source.

- the power supply system includes a semiconductor integrated circuit device and a coil element.

- One end of the coil element is coupled to the output terminal of the semiconductor integrated circuit device, and the direction of the current supplied from the output terminal to the coil element changes periodically.

- the semiconductor integrated circuit device has any one of the means (1) to (6) for solving as described above in ⁇ Semiconductor integrated circuit device viewpoint>.

- any of the means (1) to (6) for solving this problem it is possible to reduce the loss of the semiconductor integrated circuit device, so that the loss of the power supply system can be reduced and the efficiency can be improved. Is possible.

- a device for example, a CPU supplied with power by the power supply system is regarded as a load.

- the current demanded by the load (load current) varies depending on the operation status of the device regarded as a load.

- the ratio between the loss caused by the transient time and the loss caused by the on-resistance in the loss in the semiconductor integrated circuit device is heavy (heavy load), and the load current It was found that the load was different from that when the load was light (light load) and the load current was relatively low. According to the study of the present inventor, as the load current increases, the ratio of loss generated by the on-resistance increases.

- the load current is detected by the detection circuit, and in response to the detection signal, the selection circuit (means (5)) or the control circuit (means (6))

- the voltage supplied to the second input electrode of the MOSFET (the second MOSFET in the means (5), the first MOSFET and the second MOSFET in the means (6)) is selected.

- the selection circuit or the control circuit selects a voltage having a polarity such that the voltage supplied to the second input electrode of the MOSFET is more positive than the voltage at the source of the MOSFET. This reduces the loss that occurs during heavy loads.

- the selection circuit or the control circuit selects a voltage having a polarity that is more negative than the voltage at the source of the MOSFET and supplies it to the second input electrode of the MOSFET. Thereby, the loss at the time of light load is reduced.

- the loss can be reduced by items that are effective for reduction (loss reduction by shortening the transient time, loss reduction by reducing on-resistance). As a result, it is possible to reduce the loss of the power supply system according to the load.

- the above-described first input electrode corresponds to, for example, the second gate electrode of Patent Document 1

- the above-described second input electrode corresponds to the first gate electrode.

- the loss in the transient time is also referred to as switching loss

- the loss due to the on-resistance is also referred to as conduction loss.

- FIG. 10 is a block diagram showing a main configuration of a semiconductor integrated circuit device according to a third embodiment.

- A) And (B) is a wave form diagram which shows operation

- FIG. 10 is a block diagram showing a configuration of a main part of a semiconductor integrated circuit device according to a fourth embodiment.

- (A) to (D) are waveform diagrams showing the operation of the semiconductor integrated circuit device according to the fourth embodiment.

- (A) to (F) are explanatory diagrams for explaining the operation of the semiconductor integrated circuit device according to the fourth embodiment.

- FIG. 10 is a characteristic diagram illustrating characteristics of the semiconductor integrated circuit device according to the fourth embodiment.

- (A) to (F) are explanatory diagrams for explaining the operation of the semiconductor integrated circuit device according to the first embodiment.

- (A) to (F) are explanatory diagrams for explaining the operation of the semiconductor integrated circuit device according to the first embodiment.

- 4 is a characteristic diagram showing characteristics of the semiconductor integrated circuit device according to the first embodiment.

- FIG. 10 is a characteristic diagram illustrating characteristics of the semiconductor integrated circuit device according to the second embodiment.

- (A) And (B) is the block diagram and waveform diagram which show the principal part structure of the semiconductor integrated circuit device concerning Embodiment 5.

- FIG. (A) to (E) are explanatory diagrams for explaining the operation of the semiconductor integrated circuit device according to the fifth embodiment.

- FIG. 10 is a characteristic diagram illustrating characteristics of the semiconductor integrated circuit device according to the fifth embodiment.

- (A) And (B) is a principal part structure and operation

- FIG. 20 is a characteristic diagram illustrating characteristics of the semiconductor integrated circuit device according to the sixth embodiment.

- (A) And (B) is the block diagram and waveform diagram which show the principal part structure of the semiconductor integrated circuit device concerning Embodiment 7.

- FIG. (A) to (E) are explanatory diagrams for explaining the operation of the semiconductor integrated circuit device according to the seventh embodiment.

- FIG. 20 is a characteristic diagram illustrating characteristics of the semiconductor integrated circuit device according to the seventh embodiment.

- FIG. 10 is a waveform diagram showing waveforms of main parts of a semiconductor integrated circuit device according to an eighth embodiment.

- FIG. 20 is a characteristic diagram illustrating characteristics of the semiconductor integrated circuit device according to the eighth embodiment.

- FIG. 10 is a block diagram illustrating a configuration of a semiconductor integrated circuit device according to a ninth embodiment.

- FIG. 29 is a block diagram showing a second modification of the semiconductor integrated circuit device according to the ninth embodiment.

- FIG. 29 is a block diagram showing a third modification of the semiconductor integrated circuit device according to the ninth embodiment.

- FIG. 10 is a block diagram showing a configuration of a semiconductor integrated circuit device according to a tenth embodiment.

- FIG. 20 is a circuit diagram showing a configuration of a main part of a semiconductor integrated circuit device according to a tenth embodiment.

- (A) to (E) are waveform diagrams showing the operation of the semiconductor integrated circuit device according to the tenth embodiment.

- FIG. 20 is a block diagram showing a configuration of a semiconductor integrated circuit device according to an eleventh embodiment.

- FIG. 20 is a circuit diagram showing a configuration of main parts of a semiconductor integrated circuit device according to an eleventh embodiment.

- (A) to (E) are waveform diagrams showing the operation of the semiconductor integrated circuit device according to the eleventh embodiment.

- (A) And (B) is the schematic diagram and top view which show the relationship between a semiconductor integrated circuit device, a package, and a power supply system.

- A) And (B) is the top view and sectional drawing of MOSFET which have a 1st gate electrode and a 2nd gate electrode. It is explanatory drawing for demonstrating the loss of a semiconductor integrated circuit device.

- FIG. 1 is a block diagram showing a configuration of a semiconductor integrated circuit device and a power supply system according to an embodiment.

- (A) to (G) are waveform diagrams showing the operation of the semiconductor integrated circuit device according to the embodiment.

- FIG. 40 is a block diagram showing the configuration of the power supply system.

- reference numeral 4000 denotes a power supply system

- reference numeral 4001 denotes a load coupled to the power supply system 4000. Since the load 4001 can be regarded as a current source equivalently, the load 4001 is shown as a symbol of a current source in the figure, but as described above, for example, the CPU corresponds to the load.

- the power supply system 4000 is not particularly limited, but includes a control semiconductor integrated circuit device 4007, a coil element 4008, a smoothing capacitor 4008, a boot capacitor 4009, and a plurality of semiconductor chips 4004 to 4006 sealed in one package 4002. It has.

- the plurality of semiconductor chips sealed in one package 4002 are a high-side MOSFET 4005, a low-side MOSFET 4006, a high-side MOSFET 4005, and a driver 4003 that drives the low-side MOSFET 4006. That is, the high-side MOSFET 4005, the low-side MOSFET 4006, and the driver 4003 are formed on separate semiconductor chips. These three semiconductor chips will be described later with reference to FIGS. 36A and 36B, but are sealed in one package. Since the package is mounted as a unit on, for example, a printed circuit board, the package 4002 is referred to as a semiconductor integrated circuit device in this specification. Therefore, in the following description, 4002 is described as a semiconductor integrated circuit device.

- the voltage supplied to the drain of the MOSFET 4005 has a higher potential than the voltage supplied to the source of the MOSFET 4006. Therefore, the MOSFET 4005 is referred to as a high side MOSFET, and the MOSFET 4006 is referred to as a low side MOSFET.

- each of T1 to T6 is a terminal provided in the semiconductor integrated circuit device 4002.

- the semiconductor integrated circuit device 4002 is provided with a plurality of terminals. In FIG. 40, only main terminals are shown as terminals T1 to T6. For example, a terminal to which an input signal from the control semiconductor integrated circuit device 4007 is transmitted is omitted in FIG.

- the terminal T1 is an output terminal that outputs the output signal VSWH of the semiconductor integrated circuit device 4002

- the terminal T2 is a voltage terminal that supplies the ground voltage PGND to the low-side MOSFET 4006, and the terminal T3 is a voltage terminal that supplies the ground voltage CGND to the driver. is there.

- the terminal T4 is a voltage terminal for supplying the power supply voltage VCIN to the control circuit 4004.

- the terminal T5 is a voltage terminal for supplying the power supply voltage BOOT corresponding to the voltage of the output signal VSWH to the driver.

- the terminal T6 is connected to the high side MOSFET 4005. A voltage terminal for supplying the input voltage VIN.

- each of the high-side MOSFET 4005 and the low-side MOSFET 4006 is an N-channel MOSFET, and will be described later with reference to FIGS. 37A and 37B. It has a first gate electrode G1, a second gate electrode G2 corresponding to a second input electrode, a source S and a drain D.

- the second input electrode (second gate electrode) G2 is disposed closer to the drain D than the first input electrode (first gate electrode) G1, and the MOSFET is arranged according to the voltage supplied to the first gate electrode G1. Turn on or off (on / off).

- the second input electrode (second gate electrode) G2 of each of the high-side MOSFET 4005 and the low-side MOSFET 4006 has a positive polarity voltage or A negative polarity voltage is supplied.

- FIG. 40 in the high-side MOSFET 4005 and the low-side MOSFET 4006, a parasitic diode formed between the semiconductor region where these MOSFETs are formed and the semiconductor region corresponding to the drain is shown as DD.

- the back gates of these MOSFETs are connected to the source. Since the connection destination of the second gate electrode G2 of each of the high-side MOSFET 4005 and the low-side MOSFET 4006 will be described later in each embodiment, the connection destination of the second gate electrode G2 is not clearly shown in FIG.

- the high-side MOSFET 4005 has a source / drain path connected in series between the voltage terminal T6 and the output terminal T1, and the first gate electrode G1 is connected to the output terminal T7 of the driver 4003.

- the low-side MOSFET 4006 has a source / drain path connected in series between the output terminal T1 and the voltage terminal T2, and the first gate electrode G1 is connected to the output terminal T9 of the driver 4003.

- the ground voltage PGND is supplied to the voltage terminal T2

- a positive voltage higher than the ground voltage PGND is supplied to the voltage terminal T6 as the input voltage VIN. Therefore, here, it is assumed that the drain D of the high-side MOSFET 4005 is connected to the voltage terminal T6 and the source S is connected to the output terminal T1. Similarly, it is assumed that the drain D of the low-side MOSFET 4006 is connected to the output terminal T1, and the source S is connected to the voltage terminal T2.

- the high side MOSFET 4005 receives the output signal (drive signal) GH output from the output terminal T7 of the driver 4003 as an input signal at the first gate electrode G1. Further, the low-side MOSFET 4006 receives the output signal (drive signal) GL output from the output terminal T9 of the driver 4003 as an input signal at the first gate electrode G1.

- the driver 4003 changes the voltages of the drive signals GH and GL so that the high-side MOSFET 4005 and the low-side MOSFET 4006 are turned on / off complementarily.

- the high-side MOSFET 4005 and the low-side MOSFET 4006 are complementarily turned on / off by the drive signals GH and GL, and accordingly, the voltage terminal VIN or the via the source / drain path of the high-side MOSFET 4005 or the low-side MOSFET 4006.

- the voltage terminal PGND is electrically connected to the output terminal T1.

- the voltage formed at one end of the coil element 4008 is supplied to the boot capacitor element 4010.

- the boot capacitive element 4010 forms a voltage BOOT having a voltage value higher than the voltage value at the output terminal T1 by periodically changing the voltage at one end of the coil element 4008, and supplies the voltage BOOT to the voltage terminal T5.

- the driver 4003 includes drive circuits 4011 and 4012 and a control circuit 4004.

- the drive circuit 4011 uses the voltage from the voltage terminal T8 as a reference voltage, the voltage BOOT from the voltage terminal T5 as a power supply voltage, and outputs a signal according to the output signal f from the control circuit 4004 as the drive signal GH.

- the drive circuit 4011 drives the drive signal GH based on the voltage at the source S of the high-side MOSFET 4005, in other words, the voltage at the output terminal T1. Is output. Therefore, the voltage of the drive signal GH changes between, for example, a reference voltage (voltage at the voltage terminal T8) and the voltage BOOT.

- the drive circuit 4012 operates using the voltage at the voltage terminal T10 as a reference voltage and the power supply voltage VCIN supplied to the voltage terminal T4 as a power supply voltage.

- the drive circuit 4012 uses the ground voltage PGND and the voltage VCIN as power supply voltages, and outputs the drive signal GL according to the output signal c from the control circuit 4004. Output to the first gate electrode G1 of the low-side MOSFET 4006 via the output terminal T9.

- the control circuit 4004 operates using the ground voltage CGND supplied to the voltage terminal T3, the voltage VCIN supplied to the voltage terminal T4, and the voltage BOOT supplied to the voltage terminal T5 as operation power supplies.

- the control circuit 4004 has control terminals T11 and T12, and forms output signals f and c according to a pulse width control signal PWM (input signal a) supplied from the control semiconductor integrated circuit device 4007 to the control terminal T11. .

- a control signal DISBL # for instructing whether or not to operate the control circuit 4004 is supplied to the control terminal T12.

- the power supply voltage VCIN is supplied to the control terminal T12 via the resistance element 4022.

- the control circuit 4004 Since the power supply voltage VCIN is at a high level, the control signal DISBL # is at a high level, and the control circuit 4004 forms output signals g and c according to the pulse width control signal PWM supplied to the control terminal T11. On the other hand, when the control signal DISBL # is set to the low level, the control circuit 4004 enters a non-operating state. Thereby, the power supply system 4000 can be controlled to be in an operating state or a non-operating state by the control signal DISBL #.

- the ground voltage CGND supplied to the voltage terminal T3 of the control circuit 4004 is substantially the same voltage (ground voltage GND) as the ground voltage PGND supplied to the voltage terminal T2 connected to the source S of the low-side MOSFET 4006.

- the low-side MOSFET 4006 operates by electrically separating the voltage terminal T3 that supplies the ground voltage to the control circuit 4004 and the voltage terminal T2 that supplies the ground voltage to the source S of the low-side MOSFET 4006. It is possible to prevent the fluctuation of the ground voltage PGND caused by this from being transmitted to the control circuit 4004.

- the voltage value of the voltage BOOT supplied to the voltage terminal T5 is set higher than the power supply voltage VCIN supplied to the voltage terminal T4.

- the control circuit 4004 is configured such that the high level of the output signal f of the control circuit 4004 becomes the voltage BOOT. As a result, the output signal f having the voltage BOOT that is higher than the power supply voltage VCIN is input to the drive circuit 4011.

- the input voltage VIN is, for example, 12V

- the power supply voltage VCIN for the driver 4003 is, for example, 5V.

- each of the drive circuits 4011 and 4012 functions as a buffer circuit. Therefore, the drive circuit 4012 supplies the output signal c from the control circuit 4004 to the first gate electrode G1 of the low-side MOSFET 4006.

- the voltage of the drive signal GL supplied to the first gate electrode G1 of the low-side MOSFET 4006 transitions between the power supply voltage VCIN and the ground voltage.

- the drive circuit 4011 supplies the output signal f from the control circuit 4004 to the first gate electrode G1 of the high-side MOSFET 4005.

- the drive circuit 4011 is supplied with the voltage BOOT as the power supply voltage, and the high level voltage of the output signal f becomes the voltage BOOT. Therefore, the voltage of the drive signal GH supplied to the first gate electrode G1 of the high side MOSFET 4005 transitions between the voltage BOOT and the voltage VSWH at the voltage terminal T8 (voltage at the source of the high side MOSFET).

- loss due to the threshold voltage of the high side MOSFET 4005 is reduced.

- the output voltage Vout output from the output terminal T13 of the power supply system 4000 is supplied to the control semiconductor integrated circuit device 4007.

- the control semiconductor integrated circuit device 4007 forms a pulse width control signal PWM (input signal a) according to the voltage value of the output voltage Vout. That is, the pulse width control signal PWM having a pulse width (for example, a period during which the output voltage Vout is high) is formed.

- the control circuit 4004 in this embodiment includes level shifters 4013 and 4014, an input logic circuit 4018, AND circuits 4016 and 4017, a NOR circuit 4014, an inverter circuit 4020, a low voltage detection circuit 4021, and an overlap prevention circuit 4015.

- the voltage BOOT described above is supplied to the level shifter 4013, and the high level of the output signal f output from the level shifter 4013 is set to the voltage value of the voltage BOOT.

- the overlap prevention circuit 4015 is provided with a voltage conversion circuit that converts the high-level voltage value of the output signal f into an appropriate value.

- the AND circuit 4016 is a three-input AND circuit having one inverting input terminal and two non-inverting input terminals

- the AND circuit 4017 has two inverting input terminals and one non-inverting input terminal. It is a 3-input AND circuit having an inverting input terminal.

- the inverting input terminal is a terminal that inverts the signal supplied to the terminal and supplies it to the AND circuit

- the non-inverting terminal is a terminal that supplies the signal supplied to the terminal as it is to the AND circuit.

- inverter 4020 has a hysteresis function in order to prevent malfunction due to noise.

- the input logic circuit 4018 has a plurality of functions, but description thereof is omitted here.

- the pulse width control signal PWM (input signal a) output from the control semiconductor integrated circuit device 4007 is input to the input logic circuit 4018 via the control terminal T11.

- the output signal b of the input logic circuit 4018 is supplied to the inverting input terminal of the AND circuit 4017 and the non-inverting input terminal of the AND circuit 4016.

- the output signals of the NOR circuit 4019 are supplied to the non-inverting input terminals of the AND circuits 4016 and 4017, respectively.

- a control signal DISBL # is supplied to one input terminal of the NOR circuit 4019 via an inverter 4019, and a power supply voltage VCIN is supplied to the other input terminal via a low voltage detection circuit 4021.

- the power supply voltage VCIN is input to the low voltage detection circuit 4021.

- a high level output signal is formed and supplied to the NOR circuit 4019.

- the NOR circuit 4019 forms a low level output signal.

- each of the AND circuits 4016 and 4017 transmits the output signal b of the input logic circuit 4018 and / or the output signals d and g of the overlap prevention circuit 4015 to its output. No longer. As a result, the control circuit 4004 becomes inoperative.

- each of the AND circuits 4016 and 4017 transmits the output signal b of the input logic circuit 4018 and / or the output signals d and g of the overlap prevention circuit 4015 to its output, and the control circuit 4004 It becomes an operation state.

- the output signal d of the overlap prevention circuit 4015 is supplied to the inverting input terminal of the AND circuit 4016, and the output signal g of the overlap prevention circuit 4015 is supplied to the inverting input terminal of the AND circuit 4017.

- the output signal e of the AND circuit 4016 is input to the drive circuit 4011 as the output signal f of the control circuit 4004 via the level shifter 4013.

- the output signal f is input to the overlap prevention circuit 4015.

- the output signal c of the AND circuit 4017 is input to the drive circuit 4012 as an output signal of the control circuit 4004.

- the output signal c is level-shifted to a desired voltage value by the level shifter 4014 and supplied to the overlap prevention circuit 4015.

- the overlap prevention circuit 4015 is a circuit for preventing the high-side MOSFET 4005 and the low-side MOSFET 4006 from being turned on simultaneously. At the same time, in order to prevent the on-state from being turned on, the output signals c and f are received, and the high levels of the output signals d and g that do not overlap in time are formed.

- Such a circuit can be configured by using a plurality of logic circuits and delay circuits, for example.

- 41 (A) to 41 (G) are waveform diagrams of the signals (output signals and control signals) a to g described above.

- the horizontal axis indicates time

- the vertical axis indicates voltage.

- FIG. 41A is a waveform diagram of a pulse width control signal PWM (denoted as a in the figure) output from the control semiconductor integrated circuit device 4007.

- PWM pulse width control signal

- FIG. 41A is a waveform diagram of a pulse width control signal PWM (denoted as a in the figure) output from the control semiconductor integrated circuit device 4007.

- the control semiconductor integrated circuit device 4007 changes the pulse width (high-level period) in the pulse width control signal PWM, and outputs the output voltage. Control is performed so that the voltage value of Vout becomes a predetermined value.

- a so-called PWM control method is employed.

- the pulse width control signal PWM (a) changes from the low level to the high level at time t1.

- the input logic circuit 4018 changes the output signal b from the low level to the high level at time t2 after a predetermined delay time (FIG. 41B).

- the AND circuit 4017 changes the output signal c to low level at time t2 when the output signal b supplied to the inverting input terminal changes to high level (FIG. 41C).

- the drive circuit 4012 forms the low-level drive signal GL and supplies it to the first gate electrode G1 of the low-side MOSFET 4006.

- the drive circuit 4012 functions as a buffer, the drive signal GL and the output signal c are synchronized with each other. Therefore, it can be considered that the waveform of the drive signal GL is shown in FIG. 41C, and in FIG. 41C, the reference sign GL meaning the drive signal GL is shown as (GL). ing.

- the overlap prevention circuit 4015 receives a change (change from high level to low level) of the output signal c via the level shifter 4014. When this change is received, at time t3 after a predetermined delay time, the overlap prevention circuit 4015 changes the output signal d from the high level to the low level (FIG. 41D). Since the output signal d is supplied to the inverting input terminal of the AND circuit 4016, when the output signal d changes to the low level, the AND circuit 4016 changes the output signal e from the low level to the high level at time t3. (FIG. 41E).

- the level shifter 4013 In response to the change of the output signal e of the AND circuit 4016 from the low level to the high level, the level shifter 4013 forms the high-level output signal f. Since the voltage BOOT is supplied as the operating voltage to the level shifter 4013, the high level of the output signal f becomes the voltage value of the voltage BOOT. This output signal f is supplied to the first gate electrode G1 of the high-side MOSFET 4005 through the drive circuit 4011 that functions as a buffer. The drive circuit 4011 uses the voltage BOOT and the voltage VSWH at the voltage terminal T8 as operating voltages.

- the high level voltage value of the drive signal GH supplied from the drive circuit 4011 to the first gate electrode G1 of the high side MOSFET 4005 is the voltage BOOT

- the low level voltage value of the drive signal GH is the voltage VSWH. Since the output signal f and the drive signal GH are synchronized, FIG. 41 (F) shows that the output signal f and the output signal GH change to high level (voltage BOOT) at time t4. Yes.

- the overlap prevention circuit 4015 changes the output signal g from low level to high level at time t5 after a predetermined time (FIG. 41 (G)).

- the drive signal GL of the drive circuit 4012 changes from the high level to the low level at time t2.

- the drive signal GH of the drive circuit 4011 changes from the low level (VSWH) to the high level (BOOT). Accordingly, at time t2, the low-side MOSFET 4006 starts to transition to the off state, and at time t4, the high-side MOSFET 4005 starts to transition to the on state.

- the input voltage VIN is supplied to the output terminal T1 through the high-side MOSFET 4005, and is supplied to one end of the coil element 4008 and one end of the boot capacitor 4010.

- a current is supplied from the voltage terminal T6 to one end of the coil element 4008 via the output terminal T1.

- the pulse width control signal PWM (a in FIG. 41A) changes from the high level to the low level (FIG. 41A).

- the input logic circuit 4018 changes the output signal b from the high level to the low level at time t7 after a predetermined time (FIG. 41 (b)).

- the output signal e of the AND circuit 4016 changes to the low level at time t7 (FIG. 41 (e)).

- the level shifter 4013 changes the output signal f from the high level (voltage BOOT) to the low level.

- the drive circuit 4011 changes the drive signal GH from the high level (BOOT) to the low level (VSWH) (time t8 in FIG. 41F).

- the overlap prevention circuit 4015 changes the output signal g from the high level to the low level at time t9 after a predetermined time in response to the change to the low level ( FIG. 41 (G)).

- the low level is supplied to the two inverting input terminals of the AND circuit 4017, and the output signal c of the AND circuit 4017 changes from the low level to the high level (time t9 in FIG. 41C). ).

- This output signal c is buffered by the drive circuit 4012 and supplied to the first gate electrode G1 of the low-side MOSFET 4006 as the drive signal GL.

- the overlap prevention circuit 4015 changes the output signal d from the low level to the high level after a lapse of a predetermined time after the output signal c changes to the high level. (Time t10 in FIG. 41D).

- the drive signal GH supplied to the first gate electrode G1 of the high-side MOSFET 4005 transitions to the low level (VSWH), and at time t9 after time t8, the first gate of the low-side MOSFET 4006.

- the drive signal GL supplied to the electrode G1 transitions to a low level. That is, it is possible to prevent a period in which the high-side MOSFET 4005 and the low-side MOSFET 4006 are turned on at the same time.

- the low-side MOSFET 4006 transitions to the on state.

- the output terminal T1 is connected to the voltage terminal T2 via the low-side MOSFET 4006.

- a current flows from one end of the coil element 4008 toward the voltage terminal T2 via the output terminal T1.

- the control semiconductor integrated circuit device 4007 controls the pulse width of the pulse width control signal PWM according to the voltage value of the output voltage Vout so that the generated voltage value of the output voltage Vout becomes a predetermined value.

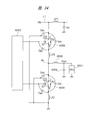

- FIG. 37A is a schematic plan view showing the layout of the low-side MOSFET 4006 in the semiconductor chip.

- FIG. 37B is a schematic cross-sectional view showing a cross section of the low-side MOSFET 4006 when viewed along B-B ′ in FIG.

- reference numeral 3700 denotes a semiconductor chip.

- two MOSFETs are formed in the semiconductor chip 3700, and the source S, drain D, first gate electrode G1, and second gate electrode G2 of each of the two MOSFETs are formed. Are connected to each other to form one low-side MOSFET 4006.

- 3701 is the source electrode of each of the two MOSFETs

- 3702 is the second gate electrode G2, 3703 of each of the two MOSFETs

- the drain electrode of the low-side MOSFET 4006 is the back surface of the semiconductor chip 3700.

- the source electrode 3701 is formed so as to cover a part of the second gate electrode 3702.

- the drive signal GL is supplied to the second gate electrode 3702 using the region of the second gate electrode 3702 that is not covered with the source electrode 3702.

- reference numeral 3704 denotes an N ⁇ type (first conductivity type) semiconductor region which functions as the drain D of the low-side MOSFET 4006.

- Reference numeral 3705 denotes a P ⁇ -type (second conductivity type) semiconductor region, which is a semiconductor region where a MOSFET channel is formed.

- Reference numeral 3706 denotes an N + type (first conductivity type) semiconductor region which functions as the source S of the MOSFET.

- a semiconductor region 3705 is stacked on the main surface of the semiconductor region 3704, and a semiconductor region 3706 is stacked on the main surface of the semiconductor region 3705. As shown in the figure, grooves are formed in the semiconductor regions 3704, 3705 and 3706.

- a metal layer 3708 is formed in the groove of the semiconductor region 3704 with the insulating layer 3707 interposed therebetween.

- a metal layer 3709 is formed in the trenches of the semiconductor regions 3704 and 3705 with the insulating layer 3707 interposed therebetween so as to overlap with the metal layer 3708.

- the metal layer 3709 constitutes the first gate electrode G1 described above, and the metal layer 3708 constitutes the second gate electrode G2 described above.

- the part of the insulating layer 3707 sandwiched between the metal layer 3709 functioning as the first gate electrode G1 and the semiconductor region 3705 can be understood as a gate insulating film of the low-side MOSFET 4006.

- the metal layer 3709 constituting the first gate electrode G1 overlaps with the semiconductor region 3706 functioning as the source S and the semiconductor region 3704 functioning as the drain D in the vertical direction of the groove.

- the metal layer 3708 functioning as the second gate electrode G2 is embedded in the semiconductor region 3704 functioning as the drain D in the vertical direction of the trench. In other words, the second gate electrode G2 is disposed closer to the drain D than the first gate electrode G1 in the longitudinal direction of the trench.

- reference numeral 3701 denotes a source electrode, which is electrically connected to a semiconductor region 3706 functioning as a source S. Note that the source electrode 3701 is also electrically connected to a semiconductor region 3705 where a channel is formed. As a result, the source S and the back gate of the low-side MOSFET 4006 are electrically connected to the source electrode 3701.

- the metal layer 3709 functioning as the first gate electrode G1 is connected to the connection pad 3703 shown in FIG.

- Reference numeral 3710 denotes a drain electrode provided on the back surface of the semiconductor chip 3700.

- Crss indicates the first gate-drain capacitance that is formed between the first gate electrode G1 and the drain D.

- the high-side MOSFET 4005 it is possible to reduce the capacitance Crss between the first gate and the drain by changing the polarity of the voltage supplied to the second gate electrode G2 (based on the voltage at the source). In addition, the on-resistance can be reduced.

- the low-side MOSFET 4006 (FIG. 40) is larger in size than the high-side MOSFET 4005 in order to flow the current from the coil element 4008 to the ground voltage PGND and lower the voltage at the output terminal T1. Has been increased. Therefore, reduction of the first gate-drain capacitance Crss and the on-resistance in the low-side MOSFET 4006 is particularly effective.

- FIG. 1A is a circuit diagram showing a configuration of a main part of the semiconductor integrated circuit device 4002 according to the first embodiment.

- FIG. 1B is a waveform diagram showing voltage waveforms in the semiconductor integrated circuit device 4002 shown in FIG.

- FIG. 1A shows a low-side MOSFET 4006 and a drive circuit 4012 in the semiconductor integrated circuit device 4002 shown in FIG.

- a portion not shown in FIG. 1A has the same configuration as that of the semiconductor integrated circuit device 4002 shown in FIG.

- the first gate electrode G1 of the low-side MOSFET 4006 is connected to the output terminal T9 of the driver 4003, its source and back gate are connected to the voltage terminal T2, and its drain is the semiconductor integrated circuit device 4002. Are connected to the output terminal T1.

- the driver 4003 includes a drive circuit 4012 that drives the low-side MOSFET 4006, and a drive signal GL from the drive circuit is supplied to the first gate electrode G1 of the low-side MOSFET 4006 via the output terminal T9.

- the driver 4003 includes a control terminal T14 and a second gate electrode control circuit 1001 connected to the control terminal T14.

- the control terminal T14 is connected to the second gate electrode G2 of the low-side MOSFET 4006, and the second gate control signal UL formed by the second gate electrode control circuit 1001 is supplied to the second gate electrode of the low-side MOSFET 4006 via the control terminal T14. Supplied to G2.

- the second gate electrode control circuit 1001 includes a variable voltage source 1004 as an example in FIG.

- Variable voltage source 1004 generates a positive voltage with respect to ground voltage CGND.

- the generated voltage value is variable.

- the ground voltage CGND is the ground voltage GND substantially the same as the ground voltage PGND. Therefore, the second gate electrode control circuit 1001 forms a second gate control signal UL that has a positive polarity with respect to the source of the low-side MOSFET 4006 and changes its voltage value.

- FIG. 1C is a circuit diagram showing an example of the second gate electrode control circuit 1000 that forms the second gate control signal UL having a positive voltage.

- FIG. 1D is a circuit diagram showing an example of the second gate electrode control circuit 1000 that forms the second gate control signal UL having a negative voltage.

- FIG. 1B is a waveform diagram showing a voltage waveform of the second gate control signal UL formed by the second gate electrode control circuit 1000 shown in FIG.

- a positive voltage means a positive voltage

- a negative voltage means a negative voltage.

- reference numeral 1002 denotes an N-channel MOSFET

- reference numerals 1003 and 1004 denote resistance elements

- reference numeral 1005 denotes a differential amplifier circuit

- reference numeral 1006 denotes a variable voltage source.

- Resistance elements 1003 and 1004 are connected in series between the control terminal T14 and the ground voltage CGND, and a divided voltage is taken out from a connection node between the resistance elements 1003 and 1004.

- the extracted divided voltage is supplied to the inverting input ( ⁇ ) of the differential amplifier circuit 1005, and the variable voltage from the variable voltage source 1006 is supplied to the non-inverting input (+) of the differential amplifier circuit 1005. .

- the output signal of the differential amplifier circuit 1005 is supplied with the power supply voltage VCIN at its drain, and its back gate and drain are supplied to the gate of the MOSFET 1002 connected to the control terminal T14.

- the differential amplifier circuit 1005 controls the MOSFT 1002 so that the voltage difference between the divided voltage determined by the resistance ratio between the resistance element 1003 and the resistance element 1004 and the variable voltage from the variable voltage source 1006 decreases. .

- a voltage corresponding to the variable voltage from the variable voltage source 1006 is formed as the second gate control signal UL and supplied to the second gate electrode G2 of the low-side MOSFET 4006.

- the value of the on-resistance of the low-side MOSFET 4006 can be adjusted by changing the value of the variable voltage of the variable voltage source 1006.

- the second gate electrode control circuit 1000 that forms the second gate control signal UL having a negative voltage will be described with reference to FIGS. 1D and 1B.

- the second gate electrode control circuit 1000 includes a P-channel MOSFET 1007, an N-channel MOSFET 1008, an oscillation circuit 1013, capacitive elements 1009 and 1012, and diode elements 1010 and 1011.

- the source / drain paths of the P-channel MOSFET 1007 and the N-channel MOSFET 1008 are connected in series between the power supply voltage VCIN and the ground voltage CGND. Further, the oscillation output from the oscillation circuit 1013 is supplied to each gate electrode. That is, the P-channel MOSFET 1007 and the N-channel MOSFET 1008 constitute a CMOS inverter, and the oscillation output of the oscillation circuit 1013 is input to the inverter. An output of the inverter (a connection node between the MOSFET 1007 and the MOSFET 1008) is connected to the cathode of the diode element 1010 and the anode of the diode element 1011 through the capacitor element 1009.

- the anode of the diode element 1010 is connected to one end of the capacitor element 1012 and the control terminal. Connected to T14.

- the cathode of the diode element 1011 and the other end of the capacitor element 1012 are connected to the ground voltage CGND.

- the inverters (MOSFETs 1007 and 1008) periodically charge and discharge the capacitive element 1009. That is, when the MOSFET 1007 is turned on, the MOSFET 1007, the capacitor element 1009, and the diode element 1011 form a charging path, and the capacitor element 1009 is charged. On the other hand, when the MOSFET 1008 is turned on, the MOSFET 1008, the capacitor element 1009, the diode element 1010, and the capacitor element 1012 form a discharge path. When the discharge path is configured, charge dispersion is performed between the capacitive elements 1009 and 1012, and the voltage at the control terminal T14 becomes a negative voltage (negative voltage) than the ground voltage CGND. This negative voltage is supplied to the second gate electrode G2 of the low-side MOSFET 4006 as the second gate control signal UL.

- FIG. 1B shows the voltage waveform of the voltage at the source of the low-side MOSFET 4006 (referred to as source voltage (GND) in the figure) and the second gate control signal UL.

- the horizontal axis is time, and the vertical axis is voltage.

- the source S and back gate of the low-side MOSFET 4006 are connected to a voltage terminal T2 to which a ground voltage PGND is supplied. Therefore, the voltage at the source S of the low-side MOSFET 4006 is the ground voltage PGND (denoted as GND in the figure).

- the second gate electrode control circuit 1000 shown in FIG. 1D forms a negative voltage with respect to the ground voltage CGND.

- the signal UL is lower than the voltage at the source S of the low-side MOSFET 4006. In other words, when the voltage at the source S is used as a reference, the voltage is negative.

- the first gate-drain capacitance Crss can be reduced, and the low-side MOSFET 4006 is turned off from on.

- transition time the transition time for transition from OFF to ON.

- the power consumption (loss) in the low-side MOSFET 4006 can be reduced, and as a result, the semiconductor integrated circuit device 4002 can be reduced in loss.

- the second gate electrode control circuit 1000 generates the second gate control signal UL having a positive voltage or a negative voltage with respect to the voltage at the source S.

- the second gate electrode G2 when the low-side MOSFET 4006 makes a transition according to the drive signal GL supplied to the first gate electrode G1, and in either the on state or the off state, the second gate electrode G2 The second gate control signal UL having a positive or negative voltage is constantly supplied.

- the second gate control signal UL having a negative voltage is supplied to the second gate electrode G2

- the first gate-drain capacitance Crss decreases, but the MOSFET is turned on. It turns out that resistance increases.

- the second gate control signal UL having a positive voltage is supplied to the second gate electrode G2

- the on-resistance of the MOSFET decreases, but the first gate-drain capacitance Crss increases. There was found. For this reason, when the second gate control signal UL having a positive or negative voltage is constantly supplied to the second gate electrode G2 of the MOSFET, the loss may increase.

- the inventor of the present application examined a loss caused by the on-resistance of the MOSFET, that is, a conduction loss, and a loss caused when the MOSFET is turned from on to off or turned on from off, that is, a switching loss.

- the study was conducted on the semiconductor integrated circuit device 4002 used in the power supply system 4000, and the type and ratio of loss in the semiconductor integrated circuit device 4002 were examined.

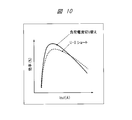

- FIG. 38 is a characteristic diagram showing a loss in the semiconductor integrated circuit device 4002.

- FIG. 38 shows three measurement results.

- a characteristic graph showing the relationship between the output current (load current) Iout (A) flowing through the output terminal T1 (FIG. 40) and the efficiency (%) of the semiconductor integrated circuit device 4002 is shown. Yes.

- the horizontal axis represents the output current

- the vertical axis represents the ratio (output power / input power) between the input power and the output power of the semiconductor integrated circuit device 4002.

- the load current (output current) Iout increases. This is because the current required by the load increases as the load becomes heavier.

- the efficiency increases when the load current Iout is relatively low, and decreases as the load current Iout increases.

- the load current (output current) Iout is equal to or less than the predetermined current value i2

- the load current (output current) Iout exceeds the predetermined current value i2.

- the type and ratio of loss were determined for light load and heavy load.

- the type and ratio of loss when the load current Iout is a current value i1 equal to or less than a predetermined current value i2 at light load is shown as “loss breakdown at light load”.

- the type and ratio of loss when the load current Iout exceeds the predetermined current value i2 when the load is heavy are shown as “loss breakdown under heavy load”. ing.

- each of “loss breakdown at light load” and “loss breakdown at heavy load” is represented by a stacked bar.

- the item of accumulation represents the type of loss.

- switching loss hereinafter also referred to as SW loss

- conduction loss hereinafter also referred to as conduction loss

- others are types of loss.

- the loss represented by others represents a loss in a logic circuit in the semiconductor integrated circuit device 4002, for example, the driver 4003.

- SW loss and conduction loss are losses in the high-side MOSFET 4005 and the low-side MOSFET 4006, and will be described with reference to FIGS. 39A and 39B.

- FIG. 39A and FIG. 39B are explanatory diagrams for explaining the SW loss and the conduction loss.

- FIG. 39A schematically shows a change in the source-drain voltage VDS, a change in the drain current IDS, and a loss P when the low-side MOSFET 4006 (high-side MOSFET 4005) transitions from off to on. ing.

- the relationship between the voltage of the second gate control signal UL supplied to the second gate electrode G2 and the first gate-drain capacitance Crss is shown as a characteristic graph.

- the horizontal axis indicates the voltage of the second gate control signal UL (in the figure, indicated as UL voltage), and the vertical axis indicates the capacitance value of the first gate-drain capacitance Crss.

- SW loss ie, switching loss P

- switching loss P is a loss that occurs when a low-side MOSFET (high-side MOSFET) transitions from off to on (or from on to off).

- VDS voltage

- IDS current

- the first gate-drain capacitance Crss is the voltage value of the second gate control signal UL supplied to the second gate electrode G2, as shown in the characteristic graph shown in the lower side of FIG. Can be reduced by reducing the negative electrode property.

- the change in the source-drain voltage VDS and the drain current IDS can be accelerated, the transition time can be shortened, and the switching loss P can be reduced. It becomes possible.

- the conduction loss is a loss proportional to the product of the on-resistance (Ron) of the low-side MOSFET (high-side MOSFET) and the square of the drain current IDS (IDS 2 ). It is.

- a characteristic graph showing the relationship between the voltage (UL voltage) of the second gate control signal UL and the on-resistance is shown on the lower side of FIG. 39B.

- the horizontal axis indicates the voltage of the second gate control signal UL

- the vertical axis indicates the on-resistance value of the low-side MOSFET (high-side MOSFET).

- the voltage (UL voltage) of the second gate control signal supplied to the second gate electrode G2 is changed from the negative voltage to the positive voltage.

- the on-resistance Ron of the low-side MOSFET (high-side MOSFET) decreases.

- the ratio of “SW loss” is higher than the losses of “conduction loss” and “other” at light load.

- the ratio of “conduction loss” is the loss of “SW loss” and “other” at heavy load.

- the ratio of “conduction loss” to the loss of the semiconductor integrated circuit device increases. That is, the ratio between the conduction loss and the switching loss in the loss of the semiconductor integrated circuit device varies depending on the load. When the load is heavy, the ratio of conduction loss is high, and when the load is light, the ratio of switching loss is high.

- both the switching loss and the conduction loss described above can be reduced.

- FIG. 2A is a block diagram showing a main configuration of the driver 4003 in the semiconductor integrated circuit device 4002 according to the second embodiment.

- a second gate electrode control circuit 1000 is shown.

- the configuration of the second gate electrode control circuit 1000 shown in FIG. 1A is changed to the configuration shown in FIG. 2A in the second embodiment.

- 2A shows the control terminal T14 of the driver 4003 and the second gate electrode control circuit 1000, and the low-side MOSFET 4006 and the drive circuit 4012 shown in FIG. 1A are omitted.

- the second gate electrode control circuit 1000 shown in FIG. 2A is provided in the driver 4003 shown in FIG.

- the second gate electrode control circuit 1000 includes a positive voltage regulator 2000, a negative voltage regulator 2001, a level shifter 2003, a selection circuit 2002, and a second gate electrode drive control circuit 2004.

- Positive voltage regulator 2000 generates a positive voltage Vpos with respect to ground voltage PGND

- negative voltage regulator 2001 generates a negative voltage Vneg with respect to ground voltage PGND.

- the generated positive voltage Vpos and negative voltage Vneg are supplied to the level shifter 2003 and the selection circuit 2002.

- the second gate electrode drive control circuit 2004 receives the drive signal GL output from the drive circuit 4012 (FIG. 40), forms a control signal synchronized with the drive signal GL, and supplies it to the level shifter 2003.

- the level shifter 2003 receives the control signal formed by the second gate electrode drive control circuit 2004, shifts the high level and low level of the received control signal to voltages adapted to the positive voltage Vpos and the negative voltage Vneg, A control signal whose voltage is shifted is supplied to the selection circuit 2002.

- the selection circuit 2002 selects either the positive voltage Vpos or the negative voltage Vneg according to the voltage (high level / low level) of the supplied control signal, and selects the selected voltage (positive voltage Vpos or negative voltage Vneg). Is output to the terminal T14 as the second gate control signal UL. As shown in FIG. 1A, the terminal T14 is connected to the second gate electrode G2 of the low-side MOSFET 4006. Here, the control signal supplied from the level shifter 2003 to the selection circuit 2002 is synchronized with the drive signal GL output from the drive circuit 4012.

- the voltage of the second gate control signal UL supplied to the second gate electrode G2 of the low-side MOSFET 4006 becomes a negative voltage Vneg or a positive voltage Vpos in synchronization with the drive signal GL for turning on / off the low-side MOSFET 4006. .

- FIG. 2B shows a circuit configuration example of the selection circuit 2002, the level shifter 2003, and the second gate electrode drive control circuit 2004 described above.

- the second gate electrode drive control circuit 2004 has three inverters connected in parallel between the power supply voltage VCIN and the ground voltage CGND.

- the inverter includes a P-channel MOSFET 2009 (2008, 2007) and an N-channel type. This is a CMOS type inverter composed of MOSFETs 2015 (2014, 2013).

- the input of the inverter is connected to the output of the inverter at the previous stage and cascaded, and the drive signal GL from the drive circuit 4012 (FIG.

- the second gate electrode drive control circuit 2004 shown in FIG. 2B supplies a signal obtained by inverting the phase of the drive signal GL to the level shifter 2003 as a control signal.

- the level shifter 2003 includes an N-channel MOSFET 2012 that receives a control signal from the second gate electrode drive control circuit 2004, and a load element 2016.

- the drain of the N-channel MOSFET 2012 has a positive voltage via the load element 2016. Connected to Vpos.

- the source of the N-channel MOSFET 2012 is connected to the ground voltage CGND.

- a control signal that changes between the positive voltage Vpos and the ground voltage CGND is output from the connection node between the load element 2016 and the N-channel MOSFET 2012. That is, the control signal with the voltage shifted is output from the level shifter 2003.

- the source of the N-channel MOSFET 2012 is connected to the ground voltage CGND, but it may be connected to the negative voltage Vneg.

- the selection circuit 2002 includes two inverters connected in parallel between a positive voltage Vpos and a negative voltage Vneg, and the inverter includes an N-channel MOSFET 2011 (2010) and a P-channel MOSFET 2006 (2005). It is a CMOS inverter configured. The input of the inverter is connected to the output of the previous inverter and cascaded. The control signal from the level shifter 2003 is supplied to the input of the first stage inverter (2011, 2006), and the output of the last stage inverter (2010, 2005) is connected to the control terminal T14. Each inverter in the selection circuit 2002 operates using the positive voltage Vpos and the negative voltage Vneg as power supply voltages. Therefore, the inverter at the final stage selects the positive voltage Vpos or the negative voltage Vneg according to the control signal from the level shifter 2003, and outputs it to the control terminal T14.

- the positive voltage regulator 2000 and the negative voltage regulator 2001 can take various configurations.

- the circuits shown in FIGS. 1C and 1D can be used.

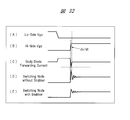

- FIGS. 3A to 3D are operation waveform diagrams of the semiconductor integrated circuit device 4002 having the second gate electrode control circuit 1000 shown in FIGS. 2A and 2B. Next, the operation of the semiconductor integrated circuit device 4002 according to Embodiment 2 will be described with reference to FIGS. 1A, 2A, 3A to 3D, and FIG.

- the horizontal axis indicates time

- the vertical axis indicates voltage

- a period (a) indicates a period in which the high-side MOSFET 4005 is on and a low-side MOSFET 4006 is off

- a period (b) indicates a period in which the high-side MOSFET 4005 is off and the low-side MOSFET 4006 is on. Yes.

- the high-side MOSFET 4005 and the low-side MOSFET 4006 are turned on / off complementarily by the drive signals GH and GL.

- FIG. 3A shows the waveform of the output voltage VSWH at the output terminal T1 of the semiconductor integrated circuit device 4002, and FIG. 3B shows the waveform of the drive signal GH from the drive circuit 4011 (FIG. 40).

- FIG. 3C shows the waveform of the drive signal GL from the drive circuit 4012 (FIG. 40).

- FIG. 3D shows the waveform of the second gate control signal UL output from the second gate electrode control circuit 1000 shown in FIG.

- the voltage of the second gate control signal UL transitions between the positive voltage Vpos and the negative voltage Vneg in synchronization with the drive signal GL.

- the source S of the low-side MOSFET 4006 is connected to a voltage terminal T2 (FIG. 1A, FIG. 40) for ground voltage. Therefore, as shown in FIG. 3D, the voltage of the second gate control signal UL is a positive voltage (positive voltage) based on the voltage at the source S of the low-side MOSFET 4006 (source voltage (GND)). Voltage Vpos) or negative voltage (negative voltage Vneg).

- Vpos positive voltage

- Vneg negative voltage

- the second gate electrode control circuit 1000 when the drive signal GL supplied to the first gate electrode G1 of the low-side MOSFET 4006 changes to a high level, in synchronization with this change, The second gate electrode control circuit 1000 outputs the positive voltage Vpos as the second gate control signal UL. On the other hand, when the drive signal GL changes to the low level, in synchronization with this change, the second gate electrode control circuit 1000 outputs the negative voltage Vneg as the second gate control signal UL.

- the drive signal GL which is the output of the drive circuit 4012, changes from the high level to the low level. Since the drive signal GL is supplied to the first gate electrode G1 of the low-side MOSFET 4006, the low-side MOSFET 4006 transitions from on to off.

- the voltage of the second gate control signal UL output from the second gate electrode control circuit 1000 changes to the negative voltage Vneg at time t1. Since the second gate electrode control signal UL is supplied to the second gate electrode G2 of the low-side MOSFET 4006, the first gate / drain of the low-side MOSFET 4006 changes when the second gate electrode control signal UL changes to the negative voltage Vneg.

- the interspace capacitance Crss is reduced. As a result, the low-side MOSFET 4006 transitions from on to off quickly, and the transition time is shortened.

- the drive signal GH that is the output signal of the drive circuit 4011 changes from the low level to the high level at time t2 after a predetermined time (dead time period) has elapsed. Change. Since the drive signal GH is supplied to the first gate electrode G1 of the high-side MOSFET 4005, the high-side MOSFET 4005 changes from off to on. As a result, the voltage of the output voltage VSWH at the output terminal T1 rises.

- both the high-side MOSFET 4005 and the low-side MOSFET 4006 are off, but the voltage VSWH at the output terminal T14 decreases. This is due to the switching loss that occurs during the period in which the low-side MOSFET 4006 transitions from on to off. In the second embodiment, since the transition period can be shortened, the switching loss can be reduced.

- the drive signal GH changes from the high level to the low level.

- the high-side MOSFET 4005 transitions from on to off.