KR900007757B1 - 반도체장치 및 그 제조방법 - Google Patents

반도체장치 및 그 제조방법 Download PDFInfo

- Publication number

- KR900007757B1 KR900007757B1 KR1019860010041A KR860010041A KR900007757B1 KR 900007757 B1 KR900007757 B1 KR 900007757B1 KR 1019860010041 A KR1019860010041 A KR 1019860010041A KR 860010041 A KR860010041 A KR 860010041A KR 900007757 B1 KR900007757 B1 KR 900007757B1

- Authority

- KR

- South Korea

- Prior art keywords

- film

- hole

- wiring

- insulating film

- semiconductor device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

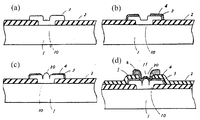

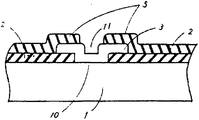

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/01—Manufacture or treatment

- H10W20/031—Manufacture or treatment of conductive parts of the interconnections

- H10W20/056—Manufacture or treatment of conductive parts of the interconnections by filling conductive material into holes, grooves or trenches

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/60—Formation of materials, e.g. in the shape of layers or pillars of insulating materials

- H10P14/63—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by the formation processes

- H10P14/6302—Non-deposition formation processes

- H10P14/6304—Formation by oxidation, e.g. oxidation of the substrate

- H10P14/6314—Formation by oxidation, e.g. oxidation of the substrate of a metallic layer

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/01—Manufacture or treatment

- H10W20/031—Manufacture or treatment of conductive parts of the interconnections

- H10W20/032—Manufacture or treatment of conductive parts of the interconnections of conductive barrier, adhesion or liner layers

- H10W20/038—Manufacture or treatment of conductive parts of the interconnections of conductive barrier, adhesion or liner layers covering conductive structures

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/01—Manufacture or treatment

- H10W20/031—Manufacture or treatment of conductive parts of the interconnections

- H10W20/062—Manufacture or treatment of conductive parts of the interconnections by smoothing of conductive parts, e.g. by planarisation

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/01—Manufacture or treatment

- H10W20/031—Manufacture or treatment of conductive parts of the interconnections

- H10W20/064—Manufacture or treatment of conductive parts of the interconnections by modifying the conductivity of conductive parts, e.g. by alloying

- H10W20/065—Manufacture or treatment of conductive parts of the interconnections by modifying the conductivity of conductive parts, e.g. by alloying by making at least a portion of the conductive part non-conductive, e.g. by oxidation

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/01—Manufacture or treatment

- H10W20/071—Manufacture or treatment of dielectric parts thereof

- H10W20/081—Manufacture or treatment of dielectric parts thereof by forming openings in the dielectric parts

- H10W20/089—Manufacture or treatment of dielectric parts thereof by forming openings in the dielectric parts using processes for implementing desired shapes or dispositions of the openings, e.g. double patterning

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Electrodes Of Semiconductors (AREA)

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP61037785A JPS62194644A (ja) | 1986-02-20 | 1986-02-20 | 半導体装置およびその製造方法 |

| JP37785 | 1986-02-20 | ||

| JP61-37785 | 1986-02-20 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR870008388A KR870008388A (ko) | 1987-09-26 |

| KR900007757B1 true KR900007757B1 (ko) | 1990-10-19 |

Family

ID=12507140

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019860010041A Expired KR900007757B1 (ko) | 1986-02-20 | 1986-11-27 | 반도체장치 및 그 제조방법 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US4884120A (enExample) |

| JP (1) | JPS62194644A (enExample) |

| KR (1) | KR900007757B1 (enExample) |

| DE (1) | DE3705152A1 (enExample) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6482547A (en) * | 1987-09-24 | 1989-03-28 | Tadahiro Omi | Semiconductor device |

| US5252382A (en) * | 1991-09-03 | 1993-10-12 | Cornell Research Foundation, Inc. | Interconnect structures having patterned interfaces to minimize stress migration and related electromigration damages |

| DE4140330C1 (enExample) * | 1991-12-06 | 1993-03-18 | Texas Instruments Deutschland Gmbh, 8050 Freising, De | |

| US5371047A (en) * | 1992-10-30 | 1994-12-06 | International Business Machines Corporation | Chip interconnection having a breathable etch stop layer |

| US5783483A (en) * | 1993-02-24 | 1998-07-21 | Intel Corporation | Method of fabricating a barrier against metal diffusion |

| US5897376A (en) * | 1993-09-20 | 1999-04-27 | Seiko Instruments Inc. | Method of manufacturing a semiconductor device having a reflection reducing film |

| US5439731A (en) * | 1994-03-11 | 1995-08-08 | Cornell Research Goundation, Inc. | Interconnect structures containing blocked segments to minimize stress migration and electromigration damage |

| JPH09205185A (ja) | 1996-01-26 | 1997-08-05 | Mitsubishi Electric Corp | 半導体装置および半導体装置の製造方法 |

| EP4541394A3 (en) | 2016-10-21 | 2025-07-09 | Sanofi-Aventis Deutschland GmbH | Liquid medicament administration device |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3866311A (en) * | 1971-06-14 | 1975-02-18 | Nat Semiconductor Corp | Method of providing electrically isolated overlapping metallic conductors |

| DE3109801A1 (de) * | 1981-03-13 | 1982-09-30 | Siemens AG, 1000 Berlin und 8000 München | Verfahren zum herstellen von halbleiterbauelementen |

| JPS5955037A (ja) * | 1982-09-24 | 1984-03-29 | Hitachi Ltd | 半導体装置 |

| GB8316477D0 (en) * | 1983-06-16 | 1983-07-20 | Plessey Co Plc | Producing layered structure |

| JPS60234346A (ja) * | 1984-05-07 | 1985-11-21 | Nec Corp | 半導体装置 |

| JPS61280638A (ja) * | 1985-06-06 | 1986-12-11 | Toshiba Corp | 半導体装置の製造方法 |

| US4707457A (en) * | 1986-04-03 | 1987-11-17 | Advanced Micro Devices, Inc. | Method for making improved contact for integrated circuit structure |

| JP3480738B2 (ja) * | 1992-06-23 | 2003-12-22 | 株式会社東芝 | 情報処理装置における表示方法及び情報処理装置 |

-

1986

- 1986-02-20 JP JP61037785A patent/JPS62194644A/ja active Pending

- 1986-11-27 KR KR1019860010041A patent/KR900007757B1/ko not_active Expired

-

1987

- 1987-02-18 DE DE19873705152 patent/DE3705152A1/de active Granted

- 1987-02-20 US US07/016,787 patent/US4884120A/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| DE3705152A1 (de) | 1987-08-27 |

| KR870008388A (ko) | 1987-09-26 |

| JPS62194644A (ja) | 1987-08-27 |

| US4884120A (en) | 1989-11-28 |

| DE3705152C2 (enExample) | 1989-07-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US5017510A (en) | Method of making a scalable fuse link element | |

| JPH0613470A (ja) | 半導体装置およびその製造方法 | |

| KR100206676B1 (ko) | 도트 패턴이 없는 다중층 배선 구조를 갖는 반도체 집적 회로 장치 및 그 제조 공정 | |

| KR19980028939A (ko) | 게이트전극의 제조방법 및 그에 따라 제조된 게이트 구조 | |

| KR900007757B1 (ko) | 반도체장치 및 그 제조방법 | |

| US4728627A (en) | Method of making multilayered interconnects using hillock studs formed by sintering | |

| US5229645A (en) | Semiconductor device and manufacturing method thereof | |

| KR100274974B1 (ko) | 반도체소자의금속배선층제조방법 | |

| JP2555755B2 (ja) | 半導体装置およびその製造方法 | |

| JP2005085884A (ja) | 半導体装置およびその製造方法 | |

| JPS62137853A (ja) | 多層配線の形成方法 | |

| KR100418920B1 (ko) | 반도체소자의배선형성방법 | |

| KR920010126B1 (ko) | 반도체 소자의 다층금속배선 공정방법 | |

| KR950002954B1 (ko) | 필라반대형상 평탄화를 이용한 다층배선의 반도체 장치의 제조방법 | |

| KR960011816B1 (ko) | 반도체소자의 캐패시터 및 그의 제조방법 | |

| KR0126102B1 (ko) | 반도체 소자의 금속막간 절연 방법 | |

| KR0154190B1 (ko) | 반도체 소자의 텅스텐-플러그 형성방법 | |

| KR100223284B1 (ko) | 반도체 소자의 금속배선 형성방법 | |

| KR0179707B1 (ko) | 반도체 장치의 다층 배선구조 및 그 제조방법 | |

| KR950011554B1 (ko) | 다층금속배선형성방법 | |

| KR100216730B1 (ko) | 반도체 금속막 식각공정 | |

| KR100257768B1 (ko) | 반도체 장치의 금속배선 형성방법 | |

| KR100228278B1 (ko) | 반도체 장치의 제조 방법 | |

| JP4986721B2 (ja) | 半導体装置およびその製造方法 | |

| JPS61203654A (ja) | 半導体装置及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| PA0109 | Patent application |

St.27 status event code: A-0-1-A10-A12-nap-PA0109 |

|

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| R17-X000 | Change to representative recorded |

St.27 status event code: A-3-3-R10-R17-oth-X000 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| G160 | Decision to publish patent application | ||

| PG1605 | Publication of application before grant of patent |

St.27 status event code: A-2-2-Q10-Q13-nap-PG1605 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U11-oth-PR1002 Fee payment year number: 1 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 4 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 5 |

|

| FPAY | Annual fee payment |

Payment date: 19951018 Year of fee payment: 6 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 6 |

|

| LAPS | Lapse due to unpaid annual fee | ||

| PC1903 | Unpaid annual fee |

St.27 status event code: A-4-4-U10-U13-oth-PC1903 Not in force date: 19961020 Payment event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE |

|

| PC1903 | Unpaid annual fee |

St.27 status event code: N-4-6-H10-H13-oth-PC1903 Ip right cessation event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE Not in force date: 19961020 |

|

| R17-X000 | Change to representative recorded |

St.27 status event code: A-5-5-R10-R17-oth-X000 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |