KR20150050390A - 반도체 장치 - Google Patents

반도체 장치 Download PDFInfo

- Publication number

- KR20150050390A KR20150050390A KR1020140145107A KR20140145107A KR20150050390A KR 20150050390 A KR20150050390 A KR 20150050390A KR 1020140145107 A KR1020140145107 A KR 1020140145107A KR 20140145107 A KR20140145107 A KR 20140145107A KR 20150050390 A KR20150050390 A KR 20150050390A

- Authority

- KR

- South Korea

- Prior art keywords

- layer

- wiring

- metal

- resistance element

- layers

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 239000004065 semiconductor Substances 0.000 title claims description 63

- 229910052751 metal Inorganic materials 0.000 claims abstract description 546

- 239000002184 metal Substances 0.000 claims abstract description 546

- 239000000758 substrate Substances 0.000 claims abstract description 47

- 239000010408 film Substances 0.000 claims description 371

- 238000000034 method Methods 0.000 claims description 51

- 230000001681 protective effect Effects 0.000 claims description 11

- 239000010409 thin film Substances 0.000 claims description 8

- 239000003990 capacitor Substances 0.000 claims description 7

- 238000009413 insulation Methods 0.000 claims description 2

- 239000010410 layer Substances 0.000 description 1166

- 238000004519 manufacturing process Methods 0.000 description 82

- 239000011229 interlayer Substances 0.000 description 29

- 238000002161 passivation Methods 0.000 description 27

- 230000008569 process Effects 0.000 description 21

- 230000004048 modification Effects 0.000 description 14

- 238000012986 modification Methods 0.000 description 14

- 230000000052 comparative effect Effects 0.000 description 11

- 230000000694 effects Effects 0.000 description 10

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 8

- 238000005229 chemical vapour deposition Methods 0.000 description 8

- 102100031476 Cytochrome P450 1A1 Human genes 0.000 description 7

- 102100026533 Cytochrome P450 1A2 Human genes 0.000 description 7

- 101000941690 Homo sapiens Cytochrome P450 1A1 Proteins 0.000 description 7

- 101000855342 Homo sapiens Cytochrome P450 1A2 Proteins 0.000 description 7

- 238000001312 dry etching Methods 0.000 description 6

- 238000000206 photolithography Methods 0.000 description 6

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 5

- 229910052814 silicon oxide Inorganic materials 0.000 description 5

- 229910052782 aluminium Inorganic materials 0.000 description 4

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 4

- 238000005530 etching Methods 0.000 description 4

- 101710201952 Photosystem II 22 kDa protein, chloroplastic Proteins 0.000 description 3

- 102100021941 Sorcin Human genes 0.000 description 3

- 101000741271 Sorghum bicolor Phosphoenolpyruvate carboxylase 1 Proteins 0.000 description 3

- 230000015572 biosynthetic process Effects 0.000 description 3

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 3

- 238000005498 polishing Methods 0.000 description 3

- 238000004544 sputter deposition Methods 0.000 description 3

- 229910018182 Al—Cu Inorganic materials 0.000 description 2

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 229910052723 transition metal Inorganic materials 0.000 description 2

- 150000003624 transition metals Chemical class 0.000 description 2

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 239000010937 tungsten Substances 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 230000003667 anti-reflective effect Effects 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 229910052755 nonmetal Inorganic materials 0.000 description 1

- 150000002843 nonmetals Chemical class 0.000 description 1

- 230000010355 oscillation Effects 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 238000012858 packaging process Methods 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 230000000149 penetrating effect Effects 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 239000003223 protective agent Substances 0.000 description 1

- 239000005368 silicate glass Substances 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 239000002344 surface layer Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

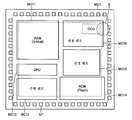

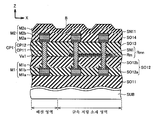

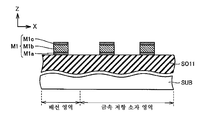

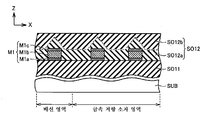

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/5228—Resistive arrangements or effects of, or between, wiring layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/40—Resistors

- H10D1/47—Resistors having no potential barriers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/201—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of only components covered by H10D1/00 or H10D8/00, e.g. RLC circuits

- H10D84/204—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of only components covered by H10D1/00 or H10D8/00, e.g. RLC circuits of combinations of diodes or capacitors or resistors

- H10D84/209—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of only components covered by H10D1/00 or H10D8/00, e.g. RLC circuits of combinations of diodes or capacitors or resistors of only resistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0555—Shape

- H01L2224/05552—Shape in top view

- H01L2224/05554—Shape in top view being square

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/53204—Conductive materials

- H01L23/53209—Conductive materials based on metals, e.g. alloys, metal silicides

- H01L23/53214—Conductive materials based on metals, e.g. alloys, metal silicides the principal metal being aluminium

- H01L23/53223—Additional layers associated with aluminium layers, e.g. adhesion, barrier, cladding layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/53204—Conductive materials

- H01L23/53209—Conductive materials based on metals, e.g. alloys, metal silicides

- H01L23/53257—Conductive materials based on metals, e.g. alloys, metal silicides the principal metal being a refractory metal

- H01L23/53266—Additional layers associated with refractory-metal layers, e.g. adhesion, barrier, cladding layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/40—Resistors

- H10D1/47—Resistors having no potential barriers

- H10D1/474—Resistors having no potential barriers comprising refractory metals, transition metals, noble metals, metal compounds or metal alloys, e.g. silicides

Landscapes

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Semiconductor Integrated Circuits (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013225212A JP6396653B2 (ja) | 2013-10-30 | 2013-10-30 | 半導体装置 |

| JPJP-P-2013-225212 | 2013-10-30 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20150050390A true KR20150050390A (ko) | 2015-05-08 |

Family

ID=51799005

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020140145107A Withdrawn KR20150050390A (ko) | 2013-10-30 | 2014-10-24 | 반도체 장치 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US9881868B2 (enExample) |

| EP (1) | EP2869343A3 (enExample) |

| JP (1) | JP6396653B2 (enExample) |

| KR (1) | KR20150050390A (enExample) |

| CN (1) | CN104600052A (enExample) |

| TW (1) | TWI643299B (enExample) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2016181710A1 (ja) * | 2015-05-13 | 2016-11-17 | 株式会社村田製作所 | 薄膜デバイス |

| DE102016104507A1 (de) * | 2016-03-11 | 2017-09-14 | Infineon Technologies Ag | Halbleiterbauelemente und ein Verfahren zum Bilden eines Halbleiterbauelements |

| WO2018008068A1 (ja) * | 2016-07-04 | 2018-01-11 | 三菱電機株式会社 | 半導体装置の製造方法 |

| US10164002B2 (en) * | 2016-11-29 | 2018-12-25 | Taiwan Semiconductor Manufacturing Company Ltd. | Semiconductor device and layout method |

| JP6800815B2 (ja) * | 2017-06-27 | 2020-12-16 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP7340948B2 (ja) * | 2018-09-05 | 2023-09-08 | ローム株式会社 | 電子部品 |

| US12438080B2 (en) * | 2018-09-28 | 2025-10-07 | Intel Corporation | And process for a precision resistor |

| KR102816786B1 (ko) | 2019-06-21 | 2025-06-05 | 삼성전자주식회사 | 수직형 메모리 장치 |

| WO2021177071A1 (ja) * | 2020-03-03 | 2021-09-10 | ローム株式会社 | 電子部品 |

| JP2023160005A (ja) * | 2022-04-21 | 2023-11-02 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06140396A (ja) * | 1992-10-23 | 1994-05-20 | Yamaha Corp | 半導体装置とその製法 |

| JP2001015599A (ja) * | 1999-06-30 | 2001-01-19 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP3715502B2 (ja) | 2000-03-14 | 2005-11-09 | 株式会社東芝 | 半導体装置及びその製造方法 |

| US6709918B1 (en) * | 2002-12-02 | 2004-03-23 | Chartered Semiconductor Manufacturing Ltd. | Method for making a metal-insulator-metal (MIM) capacitor and metal resistor for a copper back-end-of-line (BEOL) technology |

| JP2004303908A (ja) * | 2003-03-31 | 2004-10-28 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| KR100524963B1 (ko) * | 2003-05-14 | 2005-10-31 | 삼성전자주식회사 | 금속 배선 및 금속 저항을 포함하는 반도체 소자 및 그제조 방법 |

| DE10341059B4 (de) * | 2003-09-05 | 2007-05-31 | Infineon Technologies Ag | Integrierte Schaltungsanordnung mit Kondensator und Herstellungsverfahren |

| JP2005158803A (ja) * | 2003-11-20 | 2005-06-16 | Seiko Epson Corp | 半導体装置および半導体装置の製造方法 |

| JP4446771B2 (ja) * | 2004-03-23 | 2010-04-07 | 株式会社リコー | 半導体装置 |

| US7005379B2 (en) * | 2004-04-08 | 2006-02-28 | Micron Technology, Inc. | Semiconductor processing methods for forming electrical contacts |

| JP2005347466A (ja) * | 2004-06-02 | 2005-12-15 | Renesas Technology Corp | 半導体装置及び半導体装置の製造方法 |

| KR100735521B1 (ko) * | 2005-10-19 | 2007-07-04 | 삼성전자주식회사 | 반도체 소자 및 그 제조 방법 |

| JP2008130918A (ja) | 2006-11-22 | 2008-06-05 | Denso Corp | 半導体装置及び半導体装置の製造方法 |

| EP2351378B1 (en) * | 2008-11-26 | 2020-08-19 | Thin Film Electronics ASA | Random delay generation for thin-film transistor based circuits |

| JP5601566B2 (ja) | 2010-01-28 | 2014-10-08 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| JP2011253898A (ja) * | 2010-06-01 | 2011-12-15 | Nippon Telegr & Teleph Corp <Ntt> | 半導体装置及び製造方法 |

| JP2012119383A (ja) * | 2010-11-29 | 2012-06-21 | Renesas Electronics Corp | 半導体装置およびその製造方法 |

| US8860181B2 (en) * | 2012-03-07 | 2014-10-14 | United Microelectronics Corp. | Thin film resistor structure |

-

2013

- 2013-10-30 JP JP2013225212A patent/JP6396653B2/ja active Active

-

2014

- 2014-10-17 US US14/516,806 patent/US9881868B2/en active Active

- 2014-10-22 TW TW103136519A patent/TWI643299B/zh active

- 2014-10-24 KR KR1020140145107A patent/KR20150050390A/ko not_active Withdrawn

- 2014-10-24 EP EP14190281.7A patent/EP2869343A3/en not_active Withdrawn

- 2014-10-30 CN CN201410598459.6A patent/CN104600052A/zh active Pending

-

2017

- 2017-09-06 US US15/696,395 patent/US20170365553A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| US20170365553A1 (en) | 2017-12-21 |

| US20150115410A1 (en) | 2015-04-30 |

| JP6396653B2 (ja) | 2018-09-26 |

| TW201523822A (zh) | 2015-06-16 |

| JP2015088585A (ja) | 2015-05-07 |

| EP2869343A2 (en) | 2015-05-06 |

| TWI643299B (zh) | 2018-12-01 |

| US9881868B2 (en) | 2018-01-30 |

| CN104600052A (zh) | 2015-05-06 |

| EP2869343A3 (en) | 2015-09-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20150050390A (ko) | 반도체 장치 | |

| JP6075114B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| US10102972B2 (en) | Method of forming capacitor structure | |

| JP4577687B2 (ja) | 半導体装置 | |

| JP5329068B2 (ja) | 半導体装置 | |

| US8618634B2 (en) | Semiconductor device manufacturing method and semiconductor device | |

| JP5601566B2 (ja) | 半導体装置およびその製造方法 | |

| JP6120528B2 (ja) | 半導体装置およびその製造方法 | |

| US9240439B2 (en) | Semiconductor device and method for manufacturing semiconductor device | |

| KR20100104448A (ko) | 커패시터 구조물 및 그 제조 방법 | |

| US7675175B2 (en) | Semiconductor device having isolated pockets of insulation in conductive seal ring | |

| US20200051874A1 (en) | Dummy element and method of examining defect of resistive element | |

| JP5521422B2 (ja) | 半導体装置 | |

| JP2017212299A (ja) | 半導体装置およびその製造方法 | |

| JP2020065075A (ja) | 半導体装置 | |

| JP2018186285A (ja) | 半導体装置 | |

| JP2017208419A (ja) | 半導体装置およびその製造方法 | |

| JP2006120896A (ja) | 半導体ウエハ、半導体装置および半導体装置の製造方法 | |

| JP5553923B2 (ja) | 半導体装置 | |

| TWI741005B (zh) | 半導體裝置及其製造方法 | |

| JP5722651B2 (ja) | 半導体装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0109 | Patent application |

Patent event code: PA01091R01D Comment text: Patent Application Patent event date: 20141024 |

|

| PG1501 | Laying open of application | ||

| PC1203 | Withdrawal of no request for examination | ||

| WITN | Application deemed withdrawn, e.g. because no request for examination was filed or no examination fee was paid |