KR20100069595A - Soi 기판의 제작 방법, 반도체 장치의 제작 방법 - Google Patents

Soi 기판의 제작 방법, 반도체 장치의 제작 방법 Download PDFInfo

- Publication number

- KR20100069595A KR20100069595A KR1020090123832A KR20090123832A KR20100069595A KR 20100069595 A KR20100069595 A KR 20100069595A KR 1020090123832 A KR1020090123832 A KR 1020090123832A KR 20090123832 A KR20090123832 A KR 20090123832A KR 20100069595 A KR20100069595 A KR 20100069595A

- Authority

- KR

- South Korea

- Prior art keywords

- laser light

- single crystal

- substrate

- crystal semiconductor

- semiconductor layer

- Prior art date

Links

- 239000000758 substrate Substances 0.000 title claims abstract description 228

- 239000004065 semiconductor Substances 0.000 title claims abstract description 221

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 48

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims abstract description 134

- 239000001301 oxygen Substances 0.000 claims abstract description 134

- 229910052760 oxygen Inorganic materials 0.000 claims abstract description 134

- 239000013078 crystal Substances 0.000 claims abstract description 131

- 238000000034 method Methods 0.000 claims abstract description 93

- 238000010438 heat treatment Methods 0.000 claims abstract description 53

- 238000002844 melting Methods 0.000 claims abstract description 25

- 230000008018 melting Effects 0.000 claims abstract description 25

- 239000012298 atmosphere Substances 0.000 claims description 80

- 230000001678 irradiating effect Effects 0.000 claims description 27

- 239000007789 gas Substances 0.000 claims description 22

- 238000000926 separation method Methods 0.000 claims description 20

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 claims description 19

- 229910000040 hydrogen fluoride Inorganic materials 0.000 claims description 19

- 230000001603 reducing effect Effects 0.000 claims description 15

- 230000006698 induction Effects 0.000 claims description 12

- 238000005530 etching Methods 0.000 claims description 11

- 238000009792 diffusion process Methods 0.000 abstract description 52

- 238000009413 insulation Methods 0.000 abstract description 3

- 239000010408 film Substances 0.000 description 225

- 239000010410 layer Substances 0.000 description 191

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 50

- 229910052710 silicon Inorganic materials 0.000 description 50

- 239000010703 silicon Substances 0.000 description 50

- 239000000523 sample Substances 0.000 description 37

- 150000002500 ions Chemical class 0.000 description 32

- 239000001257 hydrogen Substances 0.000 description 27

- 229910052739 hydrogen Inorganic materials 0.000 description 27

- 239000011229 interlayer Substances 0.000 description 26

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 23

- 239000012535 impurity Substances 0.000 description 22

- 229910052581 Si3N4 Inorganic materials 0.000 description 19

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 19

- 229910052734 helium Inorganic materials 0.000 description 18

- 239000001307 helium Substances 0.000 description 18

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 18

- 150000002431 hydrogen Chemical class 0.000 description 17

- 229910052814 silicon oxide Inorganic materials 0.000 description 17

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 14

- 239000007787 solid Substances 0.000 description 13

- 230000000694 effects Effects 0.000 description 12

- 239000000463 material Substances 0.000 description 12

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 11

- 229910052751 metal Inorganic materials 0.000 description 11

- 239000002184 metal Substances 0.000 description 11

- 238000004458 analytical method Methods 0.000 description 9

- 230000015572 biosynthetic process Effects 0.000 description 9

- 238000005259 measurement Methods 0.000 description 9

- 239000004020 conductor Substances 0.000 description 8

- 238000001556 precipitation Methods 0.000 description 8

- 230000008569 process Effects 0.000 description 8

- 230000001737 promoting effect Effects 0.000 description 8

- 229910052785 arsenic Inorganic materials 0.000 description 7

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 7

- 229910052757 nitrogen Inorganic materials 0.000 description 7

- 238000006722 reduction reaction Methods 0.000 description 7

- 239000013074 reference sample Substances 0.000 description 7

- 239000002356 single layer Substances 0.000 description 7

- 230000003746 surface roughness Effects 0.000 description 7

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 6

- 238000001994 activation Methods 0.000 description 6

- 229910052782 aluminium Inorganic materials 0.000 description 6

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 6

- 239000011521 glass Substances 0.000 description 6

- 230000003647 oxidation Effects 0.000 description 6

- 238000007254 oxidation reaction Methods 0.000 description 6

- 229910052698 phosphorus Inorganic materials 0.000 description 6

- 239000011574 phosphorus Substances 0.000 description 6

- 239000010453 quartz Substances 0.000 description 6

- 230000009467 reduction Effects 0.000 description 6

- 229910021332 silicide Inorganic materials 0.000 description 6

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 6

- 238000001816 cooling Methods 0.000 description 5

- 229910052736 halogen Inorganic materials 0.000 description 5

- XMBWDFGMSWQBCA-UHFFFAOYSA-N hydrogen iodide Chemical compound I XMBWDFGMSWQBCA-UHFFFAOYSA-N 0.000 description 5

- 229910000043 hydrogen iodide Inorganic materials 0.000 description 5

- 238000005304 joining Methods 0.000 description 5

- 238000004381 surface treatment Methods 0.000 description 5

- 229910052721 tungsten Inorganic materials 0.000 description 5

- 239000010937 tungsten Substances 0.000 description 5

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 4

- 229910052796 boron Inorganic materials 0.000 description 4

- 150000002367 halogens Chemical class 0.000 description 4

- 239000011261 inert gas Substances 0.000 description 4

- 238000005468 ion implantation Methods 0.000 description 4

- 150000004767 nitrides Chemical class 0.000 description 4

- 238000009832 plasma treatment Methods 0.000 description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 3

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 3

- 230000001133 acceleration Effects 0.000 description 3

- 125000004429 atom Chemical group 0.000 description 3

- 230000008901 benefit Effects 0.000 description 3

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 3

- 238000005336 cracking Methods 0.000 description 3

- 229910052750 molybdenum Inorganic materials 0.000 description 3

- 239000011733 molybdenum Substances 0.000 description 3

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 3

- 230000001681 protective effect Effects 0.000 description 3

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 3

- 229910052719 titanium Inorganic materials 0.000 description 3

- 239000010936 titanium Substances 0.000 description 3

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 3

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 2

- UGFAIRIUMAVXCW-UHFFFAOYSA-N Carbon monoxide Chemical compound [O+]#[C-] UGFAIRIUMAVXCW-UHFFFAOYSA-N 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 2

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 2

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- 239000004642 Polyimide Substances 0.000 description 2

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 2

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 2

- 230000004913 activation Effects 0.000 description 2

- 229910052799 carbon Inorganic materials 0.000 description 2

- 229910002091 carbon monoxide Inorganic materials 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 238000011109 contamination Methods 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 2

- 238000000635 electron micrograph Methods 0.000 description 2

- 229910052732 germanium Inorganic materials 0.000 description 2

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 2

- 238000005247 gettering Methods 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 239000010931 gold Substances 0.000 description 2

- 150000002363 hafnium compounds Chemical class 0.000 description 2

- 229910000041 hydrogen chloride Inorganic materials 0.000 description 2

- IXCSERBJSXMMFS-UHFFFAOYSA-N hydrogen chloride Substances Cl.Cl IXCSERBJSXMMFS-UHFFFAOYSA-N 0.000 description 2

- -1 hydrogen ions Chemical class 0.000 description 2

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 2

- 238000010884 ion-beam technique Methods 0.000 description 2

- 238000003475 lamination Methods 0.000 description 2

- 238000002156 mixing Methods 0.000 description 2

- 239000012788 optical film Substances 0.000 description 2

- 230000001590 oxidative effect Effects 0.000 description 2

- 229920001721 polyimide Polymers 0.000 description 2

- 229920000642 polymer Polymers 0.000 description 2

- 229910000077 silane Inorganic materials 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- 239000000243 solution Substances 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- 229910001220 stainless steel Inorganic materials 0.000 description 2

- 239000010935 stainless steel Substances 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- ZCYVEMRRCGMTRW-UHFFFAOYSA-N 7553-56-2 Chemical compound [I] ZCYVEMRRCGMTRW-UHFFFAOYSA-N 0.000 description 1

- VHUUQVKOLVNVRT-UHFFFAOYSA-N Ammonium hydroxide Chemical compound [NH4+].[OH-] VHUUQVKOLVNVRT-UHFFFAOYSA-N 0.000 description 1

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 1

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 1

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 1

- 229910021529 ammonia Inorganic materials 0.000 description 1

- 235000011114 ammonium hydroxide Nutrition 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000007795 chemical reaction product Substances 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 150000004820 halides Chemical class 0.000 description 1

- 229910001385 heavy metal Inorganic materials 0.000 description 1

- 238000002513 implantation Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 238000010348 incorporation Methods 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 239000011630 iodine Substances 0.000 description 1

- 229910052740 iodine Inorganic materials 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 239000000155 melt Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 239000011259 mixed solution Substances 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- 239000012466 permeate Substances 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 238000007517 polishing process Methods 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 238000003825 pressing Methods 0.000 description 1

- 239000000047 product Substances 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 239000002994 raw material Substances 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 238000004335 scaling law Methods 0.000 description 1

- 229910052708 sodium Inorganic materials 0.000 description 1

- 239000011734 sodium Substances 0.000 description 1

- 238000005728 strengthening Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76251—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques

- H01L21/76254—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques with separation/delamination along an ion implanted layer, e.g. Smart-cut, Unibond

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02587—Structure

- H01L21/0259—Microstructure

- H01L21/02598—Microstructure monocrystalline

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/268—Bombardment with radiation with high-energy radiation using electromagnetic radiation, e.g. laser radiation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/324—Thermal treatment for modifying the properties of semiconductor bodies, e.g. annealing, sintering

Abstract

SOI 기판의 단결정 반도체층 중의 산소 농도를 저감시키는 방법이 제공된다.

단결정 반도체층을 용융 상태로 함으로써 산소의 외방 확산이 촉진된다. 구체적으로는 베이스 기판 위에 형성된 산소를 함유한 접합층과, 상기 산소를 함유한 접합층 위에 형성된 단결정 반도체층을 갖는 SOI 구조를 형성하고, 상기 베이스 기판의 온도를 500℃ 이상의 온도이며 상기 베이스 기판의 융점보다 낮은 온도로 가열한 상태에서 레이저 광의 조사에 의하여 상기 단결정 반도체층을 부분 용융시킴으로써 SOI 기판이 제작된다.

부분 용융, 레이저 조사, 기판 가열, 단결정 반도체, 에치 백

Description

기술 분야는 SOI(Silicon on Insulator) 구조에 관련된 분야이다.

트랜지스터를 형성하는 방법으로서 실리콘 웨이퍼를 사용하는 방법, 절연 표면을 갖는 기판 위에 형성된 비단결정 반도체층을 형성하는 방법, 절연 표면에 형성된 얇은 단결정 반도체층을 갖는 기판(SOI 기판)을 사용하는 방법 등이 알려져 있다.

특히, SOI 기판을 사용하여 형성한 트랜지스터는 다른 방법을 사용하여 형성한 트랜지스터보다 성능을 높게 할 수 있다.

여기서, SOI 기판의 제작 방법으로서 스마트 컷(등록 상표)법이 알려져 있다.

스마트 컷법이란, 대략 이하의 공정을 거쳐 SOI 기판을 제작하는 방법이다.

우선, 실리콘 웨이퍼에 수소 이온을 조사하여 상기 실리콘 웨이퍼의 표면으로부터 소정의 깊이에 취화 영역(미소 기포층, 분리층, 박리층 등이라고도 함)을 형성한다.

다음에, 상기 실리콘 웨이퍼의 표면에 접합층으로서 기능하는 절연층을 형성한다.

다음에, 상기 접합층과 베이스 기판을 접합하여 가열 처리함으로써, 상기 미소 기포층에 균열을 생기게 함으로써 상기 실리콘 웨이퍼의 일부분을 분리시켜, 상기 실리콘 웨이퍼의 일부분으로 이루어진 단결정 반도체층을 상기 베이스 기판 위에 형성한다.

그리고, 상술한 바와 같은 SOI 기판의 제작 방법을 개시한 문헌으로서는 특허 문헌 1을 참조한다.

[특허 문헌 1]특개2008-277789호 공보

실리콘 중에 다량의 산소가 함유되어 있으면 산소 석출이라는 현상이 발생할 경우가 있다.

그리고, 산소 석출에는 오염 금속 불순물을 게터링하는 장점과, 트랜지스터의 성능을 악화시키는 결점이 있다.

실리콘 웨이퍼를 사용하여 트랜지스터를 형성하는 경우는, 표면으로부터 깊은 개소(수㎛ 내지 수십㎛ 정도의 깊이)에서 산소 석출을 발생시키고, 표면으로부터 얕은 개소(수십㎚ 내지 수백㎚)에서는 산소 석출을 발생시키지 않음으로써, 산소 석출의 결점을 회피하고 장점을 살릴 수 있다.

그러나, SOI 기판은 단결정 반도체층의 막 두께가 얇기 때문에(수십㎚ 내지 수백㎚의 막 두께), 산소 석출이 발생하면 트랜지스터의 성능을 악화시킨다는 결점을 회피하기 어렵다.

따라서, SOI 기판에 있어서는, 산소 석출을 극력 방지하기 위하여 실리콘 중의 산소 농도가 낮은 것이 바람직하다.

상술한 내용을 감안하여 단결정 반도체층 중의 산소 농도를 저감시킨 SOI 기판의 제작 방법을 이하에 개시한다.

또한, SOI 기판을 사용하여 형성한 반도체 장치 및 그 제작 방법도 이하에 개시한다.

또한, 이하에 개시하는 SOI 기판을 사용하여 형성하는 반도체 장치 및 그 제 작 방법에는 각각의 특유의 과제를 해결하는 것이 있다.

따라서, 상기 특유의 과제를 해결하는 방법이 산소 농도를 감소시킨 SOI 기판 외의 SOI 기판을 사용하여 제작한 반도체 장치에도 적용할 수 있다는 것을 부언한다.

용융 상태는 고상 상태보다 산소의 확산 계수가 높다. 따라서, 베이스 기판과, 베이스 기판 위에 형성된 절연층(접합층)과, 절연층(접합층) 위에 형성된 단결정 반도체층을 갖는 SOI 구조에 있어서, 단결정 반도체층(실리콘을 주성분으로 하는 단결정 반도체층)을 용융 상태로 함으로써 단결정 반도체층 중의 산소의 외방 확산을 촉진할 수 있다.

따라서, SOI 구조의 단결정 반도체층에 레이저 광을 조사하여 단결정 반도체층을 용융시킴으로써 산소의 확산 계수가 높은 상태로 할 수 있으므로, 산소의 외방 확산을 촉진할 수 있다.

그리고, 산소의 외방 확산이 촉진되면, 단결정 반도체층 중의 산소 농도는 감소되기 때문이다.

또한, 베이스 기판을 가열한 상태에서 레이저 광을 조사하면 더 바람직하다.

즉, 베이스 기판을 가열한 상태에서 레이저 광을 조사하면 단결정 반도체층도 가열된다.

그리고, 단결정 반도체층을 가열한 상태에서 레이저 광을 조사하면 용융된 단결정 반도체층의 냉각 속도가 저하되기 때문에, 단결정 반도체층의 용융 시간을 길게 할 수 있다.

단결정 반도체층의 용융 시간이 길어지면, 산소의 확산 계수가 높은 용융 상태의 유지 시간이 길어지기 때문에 산소의 외방 확산을 더 촉진할 수 있다.

따라서, 베이스 기판을 가열한 상태에서 레이저 광을 조사함으로써, 레이저 광 조사에 의한 산소의 외방 확산의 촉진 효과를 촉진할 수 있기 때문에 바람직하다.

또한, 베이스 기판의 온도가 500℃ 이상이면 베이스 기판을 가열하지 않는 경우와 비교하여 산소를 저감할 수 있다.

그리고, 베이스 기판의 온도가 높으면 높을수록 용융 상태의 반도체의 냉각 속도를 느리게 할 수 있으므로 베이스 기판의 온도는 높은 것이 바람직하다.

또한, 단결정 반도체층과 접촉되는 절연층이 산소를 함유한 절연막(열 산화막, 산화실리콘막, 질화산화실리콘막, 산화질화실리콘막, 산화알루미늄막, 질화산화알루미늄막, 산화질화알루미늄막 등)으로 이루어지는 경우, 용융 상태의 반도체가 산소를 함유한 절연막과 접촉되면 산소를 함유한 절연막 중의 산소가 용융 상태의 반도체 중에 확산되어 버리는 문제가 생긴다. 또한, 질화산화막이란, 산소 농도보다 질소 농도가 높은 막이고, 산화질화막이란, 산소 농도보다 질소 농도가 낮은 막이다.

따라서, 단결정 반도체층과 접촉되는 절연층이 산소를 함유한 절연층인 경우는 단결정 반도체층의 바닥 부분이 고상 상태가 되는 에너지 밀도로 레이저 광을 조사하는 것이 바람직하다.

즉, 레이저 광을 조사함으로써 단결정 반도체층을 부분 용융하는 것이 바람직하다.

부분 용융이란, 단결정 반도체층의 바닥 부분이 고상 상태가 되고, 상기 바닥 부분보다 위의 영역이 용융 상태가 되는 것을 가리킨다.

왜냐하면, 레이저 광을 조사함으로써 단결정 반도체층을 부분 용융시킴으로써 용융 상태의 반도체와 비교하여 산소의 확산 계수가 낮은 고상 상태의 반도체를 용융 상태의 반도체와 산소를 함유한 절연막 사이에 개재시킬 수 있으므로, 산소를 함유한 절연막 중의 산소가 용융 상태의 반도체 중에 확산되어 버리는 것을 방지할 수 있기 때문이다.

또한, 하지의 산소가 용융 상태의 반도체 중에 확산되는 문제는 베이스 기판에 단결정 반도체층을 직접 접합하는 경우에 있어서, 베이스 기판이 유리 기판, 석영 기판 등의 산소를 함유한 기판인 경우에도 생기는 문제다.

또한, 산소를 함유한 절연막(열 산화막, 산화실리콘막, 질화산화실리콘막, 산화질화실리콘막, 산화알루미늄막, 질화산화알루미늄막, 산화질화알루미늄막 등) 중 산화알루미늄막, 질화산화알루미늄막, 산화질화알루미늄막 등과 비교하여 산화실리콘막, 질화산화실리콘막, 산화질화실리콘막 등은 열 전도율이 낮다.

한편, 본 발명자들이 계산 과학에 의거하여 계산을 행한 결과에 의하면, 단결정 반도체층의 열 확산은 하지 측으로 우선적으로 생기기 쉬운 것이 알려져 있다.

따라서, 단결정 반도체층의 하지 측에 열 전도율이 낮은 물질을 배치함으로 써 하지 측으로 열이 확산되는 것을 억제할 수 있으므로, 단결정 반도체층의 냉각 속도를 느리게 할 수 있다.

따라서, 용융 상태의 유지 시간을 길게 하는 관점에서 보면, 산소를 함유한 절연막으로서는 열 산화막, 산화실리콘막, 질화산화실리콘막, 산화질화실리콘막 등이 열 전도율이 낮으므로 바람직하다고 할 수 있다.

또한, 실리콘 웨이퍼보다 유리 기판, 석영 기판 등이 열 전도율이 낮으므로, 용융 상태를 길게 유지하는 관점에서 보면, 베이스 기판으로서 유리 기판, 석영 기판 등이 바람직하다.

베이스 기판의 가열 수단으로서 램프 가열, 유도 가열 등의 수단을 사용하는 경우는 램프 가열, 유도 가열 등이 가능한 베이스 기판을 선택하는 것이 바람직하다. 또한, 접촉 가열을 사용하여도 좋다.

또한, 레이저 광의 조사 분위기를 감압 분위기(기압이 10-3Pa 이하의 분위기)로 함으로써 분위기 중에서 산소가 혼입되는 것을 방지할 수 있으므로 바람직하다.

또한, 레이저 광의 조사 분위기를 환원 분위기(수소를 함유한 분위기, 일산화탄소를 함유한 분위기, 요오드화 수소를 함유한 분위기 등)로 함으로써 환원 반응이 일어나므로 산소의 외방 확산을 촉진할 수 있어 바람직하다.

또한, 감압 분위기 또 환원 분위기로 하면 산소 저감 효과가 더 높아지므로 바람직하다.

또한, 단결정 반도체층 중의 산소량이 증대되는 원인은 산소 농도가 정밀하게 제어되지 않고 가격이 저렴한 단결정 반도체 기판(실리콘 웨이퍼 등)을 사용하거나, 질량 분리하지 않는 이온 도핑법을 사용하여 수소, 헬륨 등을 첨가하는 일 등이 생각된다.

따라서, 산소의 외방 확산을 촉진시키는 방법은 산소 농도가 정밀하게 제어되지 않고 가격이 저렴한 단결정 반도체 기판(실리콘 웨이퍼 등)을 사용한 경우, 질량 분리하지 않는 이온 도핑법을 사용하여 수소, 헬륨 등을 첨가한 경우 등에 특히 유효하다.

한편, 이온 도핑법은 이온 주입법과 비교하면, 질량 분리하지 않으므로 장치에 질량 분리기가 필요 없다.

질량 분리기를 사용하면, 이온 빔을 만곡시킬 필요가 있어 이온 빔의 단면적을 크게 하기 어렵다. 또한, 질량 분리기를 사용하면, 이온 전류가 감소되기 때문에 면적이 좁은 영역에 밖에 이온을 조사할 수 없는 한편, 이온 도핑법은 질량 분리하지 않고 이온을 조사하므로 큰 이온 전류를 사용할 수 있어 대면적의 기판에 이온을 조사할 수 있다.

또한, 이온 도핑법을 사용하여 수소 가스를 원료로 하여 도핑하면, 피조사물에 대하여 H+ 이온, H2 + 이온, H3 + 이온 중 H3 + 이온을 많이 조사할 수 있다.

그리고, H3 +은 H+나 H로 분리하여 피조사물 내에 도입되기 때문에, 피조사물 에 대하여 H+, H2 +를 조사하는 경우와 비교하여 수소, 헬륨 등의 혼입 효율을 향상시킬 수 있다.

취화 영역에 수소, 헬륨 등이 많이 도입될수록 단결정 반도체 기판이 더 확실하게 분리되기 때문에, 수소, 헬륨 등의 도입 효율이 향상되는 것을 바람직하다.

또한, 이온 도핑법을 사용하면, 면적이 넓은 영역에 이온을 조사할 수 있으므로, 면적이 작은 기판을 복수개 동시에 처리할 수도 있다.

그러나, 이온 도핑법은 질량 분리하지 않고 수소, 헬륨 등을 피처리물에 첨가하는 방법이므로, 도핑 분위기 중의 수소, 헬륨 등 외의 불순물도 피처리물에 첨가되어 버린다.

즉, 이온 도핑법으로 피처리물에 수소를 도핑할 때, 도핑 분위기 중에 존재하는 산소도 피처리물에 도핑되기 때문에 피처리물 중의 산소 농도가 상승되어 버린다.

따라서, 산소의 외방 확산을 촉진시키는 방법은 산소 농도가 정밀하게 제어되지 않고 가격이 저렴한 단결정 반도체 기판(실리콘 웨이퍼 등)을 사용한 경우, 질량 분리하지 않는 이온 도핑법으로 수소, 헬륨 등을 첨가한 경우 등에 특히 유효하다고 할 수 있다.

물론, 산소 석출을 방지하는 관점에서 보면, 산소 농도가 정밀하게 제어되고 가격이 비싼 단결정 반도체 기판(실리콘 웨이퍼 등)을 사용한 경우, 질량 분리를 행하는 이온 주입법으로 수소, 헬륨 등을 첨가하는 경우 등이라도 산소의 외방 확 산을 촉진시키는 방법을 적용하는 것이 바람직한 것은 말할 것도 없다.

즉, 베이스 기판과, 상기 베이스 기판 위에 형성된 산소를 함유한 접합층과, 상기 산소를 함유한 접합층 위에 형성된 단결정 반도체층을 갖는 SOI 구조를 형성하고, 상기 베이스 기판을 500℃ 이상의 온도이고 상기 베이스 기판의 융점보다 낮은 온도로 가열한 상태에서 레이저 광의 조사에 의하여 상기 단결정 반도체층을 부분 용융시킴으로써 SOI 기판을 제작하는 것이 바람직하다.

또한, 상기 레이저 광의 조사 분위기는 감압 분위기인 것이 바람직하다.

또한, 상기 레이저 광의 조사 분위기는 환원 가스를 함유하는 것이 바람직하다.

또한, 상기 레이저 광의 조사 분위기는 불화 수소 가스를 함유하는 것이 바람직하다.

또한, 상기 레이저 광의 조사 분위기에 불화 수소 가스를 함유시키는 경우에 있어서, 상기 SOI 구조의 형성 후이고 상기 레이저 광을 조사하기 전에, 불화 수소 가스를 함유시킨 분위기 내에 상기 SOI 구조를 노출시키면 바람직하다.

또한, 상기 레이저 광을 조사할 때, 상기 베이스 기판을 광 조사 또는 유도 가열에 의하여 가열하면 바람직하다.

또한, 질량 분리하지 않는 이온 도핑법을 사용하여 단결정 반도체 기판에 취화 영역을 형성한 후, 상기 취화 영역을 가열 처리함으로써 상기 단결정 반도체 기판의 일부분을 분리하여 상기 단결정 반도체층을 형성한 경우에 특히 유효적이다.

또한, 상기 단결정 반도체층이 Cz법(초크랄스키(Czochralski)법)을 사용하여 형성된 벌크 실리콘으로 형성된 것이면 특히 유효적이다.

또한, 산소 농도를 저감한 SOI 기판을 사용하여 반도체 소자(트랜지스터 등)를 형성하면, 수율이 좋고 또 고성능의 반도체 장치를 제작할 수 있으므로 바람직하다.

SOI 기판의 단결정 반도체층에 레이저 광을 조사함으로써 산소의 확산 계수가 높은 용융 상태의 반도체를 형성할 수 있으므로, 반도체 중의 산소의 외방 확산이 일어나 단결정 반도체층 중의 산소를 저감할 수 있다.

또한, SOI 기판의 베이스 기판을 가열한 상태에서 레이저 광을 조사하면, 레이저 광의 조사에 의한 산소의 외방 확산의 촉진 효과를 촉진할 수 있게 되므로 바람직하다.

또한, 단결정 반도체층과 접촉되는 절연막이 산소를 함유한 절연막인 경우는 단결정 반도체층의 바닥 부분이 고상 상태가 되는 에너지 밀도로 레이저 광을 조사하면, 산소를 함유한 절연막 중의 산소가 용융 상태의 반도체 중에 확산되어 버리는 것을 방지할 수 있으므로 바람직하다.

또한, 레이저 광의 조사 분위기를 감압 분위기 또는 환원 분위기로 함으로써 산소의 저감 효과를 촉진할 수 있다.

또한, 산소의 외방 확산을 촉진시키는 방법은 산소 농도가 정밀하게 제어되지 않고 가격이 저렴한 단결정 반도체 기판(실리콘 웨이퍼 등)을 사용한 경우, 질량 분리하지 않는 이온 도핑법을 사용하여 수소, 헬륨 등을 첨가한 경우 등에 특히 유효하다고 할 수 있다.

실시형태에 대하여 이하 설명한다.

다만, 본 발명의 형태 및 상세한 사항은 발명의 취지에서 벗어남이 없이 다양하게 변경될 수 있다는 것은 당업자라면 용이하게 이해할 수 있다.

따라서, 본 발명의 범위는 이하에 제시하는 실시형태의 기재 내용에 한정하여 해석되는 것은 아니다.

또한, 이하에 설명하는 구성에 있어서, 동일 부분 또는 같은 기능을 갖는 부분에는 동일한 부호를 상이한 도면간에서 공통적으로 사용하고, 그 반복 설명은 생략한다.

또한, 이하의 실시형태는 몇 개의 실시형태를 적절히 조합하여 실시할 수 있다.

또한, 이하에 개시하는 SOI 기판을 사용하여 형성하는 반도체 장치 및 그 제작 방법에는 각각의 특유의 과제를 해결하는 것이 있다.

따라서, 상기 특유의 과제를 해결하는 기술은 상기 기술에 의한 작용 효과가 손실되지 않으면, 이하의 실시형태에 기재된 다른 기술과 당연히 조합하여 실시할 수 있다.

(실시형태 1)

본 실시형태에서는 SOI 기판의 제작 방법의 일례에 대하여 설명한다.

우선, 단결정 반도체 기판(11)을 준비한다(도 1a 참조).

단결정 반도체 기판(11)은 실리콘을 주성분으로 하는 기판을 사용할 수 있다.

실리콘을 주성분으로 하는 기판으로서는, 실리콘 웨이퍼, 게르마늄이 첨가된 실리콘 웨이퍼 등을 사용할 수 있다.

또한, 실리콘을 주성분으로 하는 기판은 게르마늄 외의 불순물이 첨가된 경우라도 실리콘이 주성분이라면 어느 기판이라도 사용할 수 있다.

또한, 실리콘을 주성분으로 하는 기판에는, 도너 원소, 억셉터 원소 등의 저항 값을 제어하기 위한 불순물 원소가 첨가되어도 좋다.

다음에, 단결정 반도체 기판(11)에 접합층(12)을 형성한다(도 1b 참조).

또한, 접합층(12)은 노출된 표면이 평활성을 갖고, 또 단결정 반도체 기판(11)과 접촉되는 면이 절연성을 갖는 것이면 어느 층이라도 사용할 수 있다.

따라서, 접합층(12)은 단층 구조와 적층 구조의 어느 쪽이라도 좋다.

접합층(12)으로서는, 단결정 반도체 기판(11)의 표면 또는 베이스 기판의 표면을 열 산화한 열 산화막, CVD법, 스퍼터링법 등으로 형성한 산화실리콘막, 질화실리콘막, 산화질화실리콘막, 질화산화실리콘막 등을 사용할 수 있다.

특히, 단결정 반도체 기판(11)의 표면 또는 베이스 기판의 표면을 열 산화한 열 산화막을 형성하는 경우, 할로겐화물(염화수소 등)을 포함한 분위기 중에서 열 산화를 행하면 열 산화막에 할로겐을 첨가할 수 있다.

또한, 할로겐은 금속 불순물 등을 게터링할 효과가 있다.

또한, 접합층으로서 열 산화막을 사용하는 경우는 단결정 반도체 기판(11)의 표면, 이면, 및 측면에 열 산화막이 형성된다.

한편, 접합층으로서 CVD법, 스퍼터링법 등으로 형성한 막을 사용하는 경우는 적어도 표면에 접합층을 형성하면 좋다.

할로겐이 함유된 열 산화막은 나트륨 등의 가동 이온을 게터링할 수 있으므로 바람직하다.

또한, 접합층(12)을 적층 구조로 하는 경우는 상기 재료에 추가하여 금속막을 사용하여도 좋다.

노출된 표면이 평활성을 갖는 이유는 접합층과 접촉되는 베이스 기판의 표면의 접합을 강하게 하기 위해서이다.

또한, 원자간 힘 현미경(AFM)으로 측정한 경우의 평균 면 거칠기(Ra)가 0.50㎚ 이하인 것이 바람직하다(더 바람직하게는 평균 면 거칠기가 0.35㎚ 이하(더 바람직하게는 평균 면 거칠기가 0.20㎚ 이하)).

다만, 평균 면 거칠기는 하지의 평활성의 영향을 받기 때문에 접합층(12)을 적층 구조로 하는 경우는 접합층(12)이 노출된 표면의 평균 면 거칠기(Ra)가 0.50㎚ 이하가 되도록 적층 구조를 형성하는 것이 바람직하다(더 바람직하게는 평균 면 거칠기가 0.35㎚ 이하(더 바람직하게는 평균 면 거칠기가 0.20㎚ 이하)).

또한, 테트라에톡시실란(TEOS) 등의 유기 실란 재료를 사용하여 형성한 산화실리콘막은 성막시에 중간 반응 생성물이 하지의 표면을 재빠르게 이동한 후에 막이 형성되기 때문에, 적층 구조의 접합층의 표면을 평활화할 수 있다.

따라서, 접합층(12)의 최상층은 유기 실란 재료를 사용하여 형성한 산화실리 콘막으로 하면 평활성이 향상되기 때문에 바람직하다.

단결정 반도체 기판(11)과 접촉되는 면이 절연성을 갖는 이유는 단결정 반도체 기판(11)과 접촉되는 면이 도전성을 가지면 반도체와 도전성의 표면이 접촉되어 트랜지스터에 리크가 발생되기 때문이다.

또한, 베이스 기판의 표면이 평활성 또 절연성을 가지면 접합층을 형성하지 않아도 좋다.

다음에, 단결정 반도체 기판(11)에 소정의 원소를 첨가하여 제 1 영역(11a)과 제 2 영역(11b) 사이에 취화 영역(11c)(미소 기포층, 분리층, 박리층 등이라고도 함)을 형성한다(도 1c 참조).

또한, 취화 영역의 형성은 접합층을 형성하기 전에 행하여도 좋다.

다만, 취화 영역의 형성시에 반도체층이 노출되면, 이온의 주입시 또는 도핑시에 반도체층이 거칠어진다.

따라서, 취화 영역의 형성시에는 산화실리콘막, 질화실리콘막, 산화질화실리콘막, 질화산화실리콘막 등의 보호막을 형성해 두는 것이 바람직하다.

따라서, 접합층을 형성한 후에 취화 영역을 형성하는 경우는 접합층이 보호막으로서 기능한다.

한편, 접합층을 형성하기 전에 취화 영역을 형성하는 경우는 보호막을 형성하고 나서 취화 영역을 형성하면 바람직하다.

다만, 접합층이 400℃ 이상으로 가열되는 공정에서 형성되면, 접합층 형성시에 단결정 반도체 기판에 균열이 생길 우려가 있으므로, 취화 영역은 접합층을 형 성한 후에 형성하는 것이 바람직하다.

특히, 열 산화는 보통 800℃ 이상의 온도로 행해지기 때문에, 접합층을 형성하기 전에 취화 영역을 형성하면, 접합층 형성시에 단결정 반도체 기판에 균열이 생기는 것을 피할 수 없다.

따라서, 특히, 접합층으로서 열 산화막을 형성하는 경우는 취화 영역은 접합층을 형성한 후에 형성하는 것이 바람직하다.

소정의 원소로서는 수소, 헬륨 등을 사용할 수 있다.

수소, 헬륨 등의 첨가 방법으로서는, 질량 분리를 행하는 이온 주입법, 질량 분리를 행하지 않는 이온 도핑법 등을 사용할 수 있다.

또한, 이온 도핑법은 질량 분리를 행하지 않고 수소, 헬륨 등을 피처리물에 첨가하는 방법이므로, 도핑 분위기 중의 수소, 헬륨 등 외의 불순물도 피처리물에 첨가되어 버린다.

즉, 이온 도핑법으로 피처리물에 수소 등을 첨가할 때, 도핑 분위기 중에 존재하는 산소도 피처리물에 첨가되기 때문에, 피처리물 중의 산소 농도가 상승되어 버린다.

따라서, 산소의 외방 확산을 촉진시키는 방법은 이온 도핑법으로 혼입되어 버린 산소를 제거하는 의미에서 유효하다고 할 수 있다.

또한, 단결정 반도체 기판 자체에 산소가 어느 정도 함유되어 있으므로, 질량 분리를 행하는 이온 주입법을 행한 경우라도 산소의 외방 확산을 촉진시키는 방법을 사용하는 가치는 당연히 있다(특히, Cz법(초크랄스키법)을 사용하여 단결정 실리콘의 잉곳을 형성한 경우는 석영 도가니로부터 잉곳으로 산소가 혼입되는 것을 회피할 수 없음)

다음에, 접합층(12)의 표면을 베이스 기판(13)에 접합하여 가열한다(도 2a 및 도 2b 참조).

또한, 접합하기 전에, 2개의 접합 면의 접합을 강화하기 위하여 적어도 2개의 접합 면 중 어느 한쪽에 대하여 친수화 또는 활성화를 위한 표면 처리를 행하는 것이 바람직하다.

친수화를 위한 표면 처리로서는, 오존수, 암모니아 과수(암모니아수와 과산화수소수의 혼합 용액) 등에 의한 표면 처리를 사용할 수 있다.

활성화를 위한 표면 처리로서는, 산소 플라즈마 처리, 질소 플라즈마 처리, 희 가스 플라즈마 처리(특히, 아르곤 플라즈마 처리) 등에 의한 표면 처리를 사용할 수 있다.

접합층(12)의 표면을 베이스 기판에 접합하면, 접합층의 표면 및 베이스 기판의 표면이 평활성을 갖기 때문에 접합이 생긴다(도 2a 참조).

또한, 접합 후에 가열함으로써 취화 영역에 형성된 미소한 공동의 체적 변화가 일어나 취화 영역을 따라 균열이 생겨 제 1 영역(11a)과 제 2 영역(11b)을 분리할 수 있다(도 2b 참조).

베이스 기판으로서는, 실리콘 웨이퍼, 유리 기판, 석영 기판, 금속 기판(스테인리스 기판 등)을 사용할 수 있다.

취화 영역을 따라 균열을 생기게 하기 위한 가열의 온도는 400℃ 이상의 온 도로 행하면 좋다.

또한, 취화 영역을 따라 균열을 생기게 하기 위한 가열을 행하기 전에, 가열(200℃ 이상 400℃ 미만) 또는 가압을 행하여 접합을 강화시켜 두어도 좋다. 가열 및 가압을 행하여도 좋다.

제 2 영역(11b) 측에 잔존된 취화 영역(11c)은 고농도로 수소, 헬륨 등이 첨가되므로 결함이 많다.

그래서, 접합 후에 제 2 영역(11b; 단결정 반도체층)의 표면을 에칭하여 취화 영역(11c)을 제거하는 것이 바람직하다(도 3a 참조).

에칭 방법으로서는 레지스트 마스크를 형성하지 않고 에칭하는 방법(에치 백), CMP법(Chemical Mechanical Polishing) 등을 사용하여 표면을 연마하는 방법 등을 사용하는 것이 바람직하다.

다만, 공정수를 삭감하기 위하여 취화 영역(11c)을 제거하는 공정을 생략하여도 좋다.

또한, 취화 영역(11c)에 균열을 생기게 하여 분리하기 때문에 취화 영역(11c)의 표면에는 요철이 형성된다(도 3a 참조).

그리고, 에치 백을 행한 경우는 취화 영역(11c)의 표면의 요철 형상이 반영되어 남아 버린다(도 3b 참조).

그래서, 레이저 광을 주사시키면서 조사하여 단결정 반도체층을 용융시킴으로써 표면의 평탄성을 향상시킬 수 있다.

또한, 에치 백 후의 제 2 영역(11b; 단결정 반도체층)의 막 두께의 평균 값 이 100㎚보다 얇게 되면, 레이저 광을 조사한 후, 표면의 골 부분에 구멍이 생길 확률이 높아진다(도 3c의 파선(81 내지 83) 참조).

100㎚이라는 값은 에치 백 후의 제 2 영역(11b; 단결정 반도체층)의 막 두께의 평균 값을 10㎚씩 바꾼 샘플을 준비하고, 각각의 샘플에 레이저 광을 조사한 후, 현미경 관찰을 행함으로써 도출한 값이다.

현미경 관찰의 결과에 의거하면, 에치 백 후의 제 2 영역(11b; 단결정 반도체층)의 막 두께의 평균 값이 100㎚보다 작은 샘플은 구멍의 개수가 급격하게 증가되었다.

또한, 막 두께의 평균 값은 광학적인 막 두께 측정기(제품명: 나노 스펙)를 사용하여 단결정 반도체층 위의 복수의 개소를 측정하고, 복수의 개소의 측정 결과의 평균 값을 사용하여 산출하였다.

따라서, 에치 백 후의 제 2 영역(11b; 단결정 반도체층)의 막 두께의 평균 값이 100㎚ 이상이 되도록 수소, 헬륨 등의 첨가 및 에치 백을 행하면 바람직하다.

또한, 수소, 헬륨 등을 첨가할 때의 가속 전압을 조정함으로써 취화 영역(11c)의 형성 위치를 조정할 수 있으므로, 에치 백 전의 막 두께는 수소, 헬륨 등을 첨가할 때의 가속 전압을 조정함으로써 설정하면 좋다.

그리고, 에치 백 후의 막 두께는 에칭 레이트를 고려하여 원하는 막 두께가 될 때까지 제 2 영역(11b; 단결정 반도체층)을 에칭함으로써 조정할 수 있다.

다음에, 레이저 광(14)을 조사한 영역을 용융시키면서 주사하여 산소의 외방 확산을 행한다(도 4a 참조).

레이저 광의 조사 영역은 적어도 반도체 소자(트랜지스터 등)를 형성하는 영역이라면 좋다. 단결정 반도체층 전체 면에 레이저 광을 조사하여도 좋다.

레이저 광(14)의 종류로서는, 단결정 반도체층에 흡수되는 파장의 레이저 광이면 어느 레이저 광이라도 사용할 수 있다(예를 들어, 엑시머 레이저 광, YAG 레이저 광, YVO4 레이저 광 등).

레이저 광(14)의 조사 영역의 형상도 어느 형상이라도 좋다(예를 들어, 스폿 형상, 선 형상, 면 형상 등).

또한, 레이저 광의 조사 영역의 형상이 면 형상이고, 원하는 영역을 한번에 용융시킬 수 있으면 레이저 광을 주사하지 않아도 좋다.

또한, 펄스 레이저 광을 주사하면서 조사하는 경우는 충분히 가열하기 위하여 조사 영역을 중첩하여 주사하면 바람직하다(특히, 하나의 위치에 펄스 레이저 광이 평균하여 5회 내지 50회 조사되도록 펄스 레이저 광을 주사하면 바람직함).

산소의 외방 확산을 행하는 공정은 표면의 평탄성을 향상시키는 공정과 동시에 행하여도 좋고, 따로 행하여도 좋다(표면의 평탄성의 향상을 다른 공정에서 행하는 경우도 레이저 광(14)과 같은 종류의 레이저 광을 적용할 수 있음).

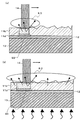

도 4a에서는, 산소의 외방 확산을 행하는 공정과 표면의 평탄성을 향상시키는 공정을 동시에 행한다.

레이저 광(14)이 조사된 개소는 용융 상태의 반도체(11d)가 된다.

용융 상태의 반도체(11d)는 고상 상태의 반도체보다 산소의 확산 계수가 높 아지고, 또 레이저 광(14)의 조사에 의하여 온도가 상승되어 산소의 외방 확산이 촉진된다(도 4a의 파선(80) 참조).

여기서, 접합층(12)이 산소를 함유한 절연막인 경우, 용융 상태의 반도체가 산소를 함유한 절연막과 접촉되면, 산소를 함유한 절연막 중의 산소가 용융 상태인 반도체 중에 확산되어 버리는 문제가 생긴다.

따라서, 단결정 반도체층과 접촉되는 절연막이 산소를 함유한 절연막의 경우는 단결정 반도체층의 바닥 부분이 고상 상태가 되는 에너지 밀도로 레이저 광을 조사하는 것이 바람직하다(도 4a 파선(90) 참조).

즉, 레이저 광을 조사함으로써 단결정 반도체층을 부분 용융시키는 것이 바람직하다.

부분 용융이란, 단결정 반도체층의 바닥 부분이 고상 상태가 되고, 상기 바닥 부분보다 위의 영역이 용융 상태가 되는 것을 가리킨다.

왜냐하면, 레이저 광을 조사하여 단결정 반도체층을 부분 용융함으로써 용융 상태의 반도체와 비교하여 산소의 확산 계수가 낮은 고상 상태의 반도체를 용융 상태의 반도체와 산소를 함유한 절연막 사이에 개재시킬 수 있으므로, 산소를 함유한 절연막 중의 산소가 용융 상태의 반도체 중에 확산되어 버리는 것을 방지할 수 있기 때문이다.

또한, 하지에 함유된 산소가 용융 상태의 반도체 중에 확산되는 문제는 베이스 기판에 단결정 반도체층을 직접 접착하는 경우에 있어서, 베이스 기판이 유리 기판, 석영 기판 등의 산소를 함유한 기판인 경우에도 생기는 문제다.

여기서, 결정 반도체층의 바닥 부분이 고상 상태가 되는 에너지 밀도의 결정 방법에 대하여 설명한다.

우선, 미리 에너지 밀도를 변화시켜 레이저 광을 조사한 SOI 기판으로 이루어진 복수의 샘플을 준비한다.

다음에, 복수의 샘플에 대하여, 반도체층의 단면의 전자 현미경 사진의 관찰, 반도체층의 SIMS 분석(2차 이온 질량 분석) 등을 행한다.

예를 들어, 반도체층의 단면의 전자 현미경 사진의 관찰을 행하면, 반도체층의 결정화 상태로부터 용융한 깊이를 판단할 수 있다.

또한, 용융 상태와 고상 상태의 경계에 불순물(탄소, 질소, 산소 등)이 모이기 쉬우므로, SIMS 분석을 하면 불순물 농도가 높은 피크의 위치가 용융 상태와 고상 상태의 경계인 것을 판단할 수 있다.

따라서, 원하는 깊이까지 용융하고자 하는 경우는 미리 복수의 샘플을 형성하여 측정을 해 둠으로써 적절한 에너지 밀도를 결정할 수 있다.

물론, 에너지 밀도의 결정 방법이 예시한 방법에 한정되지 않는 것은 말할 것도 없다.

또한, 도 4a에서는 베이스 기판(13)을 가열하지 않고 레이저 광을 조사하였지만, 도 4b와 같이 베이스 기판(13)을 가열하면서 레이저 광을 조사하면 바람직하다.

즉, 베이스 기판을 가열한 상태에서 레이저 광을 조사하면 단결정 반도체층도 가열된다.

그리고, 단결정 반도체층이 가열된 상태가 되면, 용융된 단결정 반도체층의 냉각 속도가 완화되기 때문에, 단결정 반도체층의 용융 시간을 길게 할 수 있다.

단결정 반도체층의 용융 시간이 길어지면, 산소의 확산 계수가 높은 용융 상태의 유지 시간이 길어지기 때문에, 산소의 외방 확산을 더 촉진할 수 있다.

따라서, SOI 기판의 베이스 기판을 가열한 상태에서 레이저 광을 조사하는 것은 레이저 광을 조사함으로써 산소의 외방 확산의 촉진 효과를 촉진할 수 있게 되므로 바람직하다.

베이스 기판의 온도가 500℃ 이상이면 베이스 기판을 가열하지 않는 경우와 비교하여 산소를 저감할 수 있다.

그리고, 베이스 기판의 온도가 높으면 높을수록 용융 상태의 반도체의 냉각 속도를 느리게 할 수 있으므로, 베이스 기판의 온도는 높을수록 바람직하다.

또한, 반도체층은 고상 상태라도 온도가 높으면 약간의 산소의 외방 확산이 생기므로, 산소의 외방 확산이 더 촉진된다고 할 수 있다(도 4b의 파선(80) 참조).

다만, 베이스 기판의 온도가 베이스 기판의 융점 이상이 되면 베이스 기판이 녹아 버린다.

또한, 베이스 기판의 온도가 베이스 기판의 변형점 온도 이상이 되면 베이스 기판이 변형되어 버린다.

따라서, 베이스 기판의 온도 범위의 상한 값은 베이스 기판의 융점보다 낮은 온도, 또는, 베이스 기판의 변형점 온도보다 낮은 온도 중에서 선택하는 것이 바람직하다.

다만, 단결정 반도체층이 실리콘인 경우, 실리콘의 융점은 약 1414℃이므로, 베이스 기판의 내열 온도(융점, 변형점 온도 등)가 1414℃ 이상이라도 베이스 기판의 온도는 1414℃보다 낮은 온도로 할 필요가 있다(즉, 베이스 기판의 온도 범위의 상한 값은 단결정 반도체층의 융점 미만의 온도라고 할 수 있음).

또한, 베이스 기판의 온도 범위의 상한 값은 600℃ 이하(또는 600℃ 미만), 650℃ 이하(또는 650℃ 미만), 700℃ 이하(또는 700℃ 미만), 750℃ 이하(또는 750℃ 미만), 800℃ 이하(또는 800℃ 미만), 850℃ 이하(또는 850℃ 미만), 900℃ 이하(또는 900℃ 미만), 950℃ 이하(또는 950℃ 미만), 1000℃ 이하(또는 1000℃ 미만), 1050℃ 이하(또는 1050℃ 미만), 1100℃ 이하(또는 1100℃ 미만), 1150℃ 이하(또는 1150℃ 미만), 1200℃ 이하(또는 1200℃ 미만), 1250℃ 이하(또는 1250℃ 미만), 1300℃ 이하(또는 1300℃ 미만), 1350℃ 이하(또는 1350℃ 미만), 1400℃ 이하(또는 1400℃ 미만) 중에서 선택하여도 좋다. 또한, X℃ 미만이란, X℃보다 낮은 온도를 가리킨다(X는 임의의 수임).

또한, 베이스 기판의 온도 범위의 하한 값은 500℃ 이상(또는 500℃ 초과), 550℃ 이상(또는 550℃ 초과), 600℃ 이상(또는 600℃ 초과), 650℃ 이상(또는 650℃ 초과), 700℃ 이상(또는 700℃ 초과), 750℃ 이상(또는 750℃ 초과), 800℃ 이상(또는 800℃ 초과), 850℃ 이상(또는 850℃ 초과), 900℃ 이상(또는 900℃ 초과), 950℃ 이상(또는 950℃ 초과), 1000℃ 이상(또는 1000℃ 초과), 1050℃ 이상(또는 1050℃ 초과), 1100℃ 이상(또는 1100℃ 초과), 1150℃ 이상(또는 1150℃ 초과), 1200℃ 이상(또는 1200℃ 초과), 1250℃ 이상(또는 1250℃ 초과), 1300℃ 이상 (또는 1300℃ 초과), 1350℃ 이상(또는 1350℃ 초과) 중에서 선택하여도 좋다. 또한, X℃ 초과란, X℃보다 높은 온도를 가리킨다(X는 임의의 수임).

다만, 베이스 기판의 온도 범위의 상한 값은 베이스 기판의 온도 범위의 하한 값보다 큰 것으로 한다.

베이스 기판의 가열 수단으로서는 접촉 가열, 광 조사에 의한 가열, 유도 가열 등의 수단이 있다.

접촉 가열은 기판을 배치하는 스테이지 등을 가열하여 스테이지 등과 접촉되는 기판을 가열하는 수단이다.

따라서, 접촉 가열을 사용하면 베이스 기판이 어느 종류의 기판이라도 가열할 수 있다.

한편, 광 조사에 의한 가열은 기판에 흡수되는 파장의 광을 기판에 조사하여 기판을 발열시키는 수단이다.

따라서, 광 조사에 의한 가열을 사용하는 경우는 베이스 기판의 종류와 광 파장의 선택이 필수적이다.

광 조사에 의한 가열로서는, 예를 들어, 베이스 기판을 실리콘을 주성분으로 하는 기판으로 하고, 광을 실리콘에 흡수되는 광(레이저 광, 램프 광(텅스텐 할로겐 램프 등) 등)으로 하는 방법 등이 있다.

레이저 광(제 2 레이저 광으로 함)은 산소 확산을 위한 레이저 광(14(제 1 레이저 광))과 같은 것을 사용할 수 있다. 예를 들어, 베이스 기판을 용융시키지 않는 에너지 밀도로 베이스 기판 측으로부터 조사한다.

이 경우, 제 1 레이저 광을 단결정 반도체층 측으로부터 조사하고 제 2 레이저 광을 베이스 기판 측으로부터 조사함과 함께, 제 1 레이저 광의 조사 영역의 일부분과 제 2 레이저 광의 조사 영역의 일부분이 중첩되도록 한다. 또한, 제 1 레이저 광의 파장과 제 2 레이저 광의 파장이 상이하면 제 2 레이저 광을 단결정 반도체층 측으로부터 조사하여도 처리할 수 있다.

또한, 제 1 레이저 광과 제 2 레이저 광의 주사 방향이 같은 방향을 향하도록 주사한다.

또한, 제 2 레이저 광은 여열(余熱)용이므로, 제 2 레이저 광의 조사 영역의 면적이 제 1 레이저 광의 조사 영역의 면적보다 크게 되도록 하면 바람직하다.

제 2 레이저 광의 조사 영역의 면적이 제 1 레이저 광의 조사 영역의 면적보다 크게 되도록 함으로써, 여열 범위를 광범위하게 할 수 있으므로, 용융 상태를 유지할 수 있는 영역을 광범위하게 할 수 있기 때문이다.

또한, 제 2 레이저 광은 단결정 반도체층과 비교하여 매우 두꺼운 베이스 기판을 조사하는 것이다.

따라서, 제 2 레이저 광에는 제 1 레이저 광보다 파장이 긴 레이저 광을 사용하는 것이 바람직하다.

레이저 광의 파장이 길면, 피조사물 표면으로부터 깊은 위치까지 레이저 광이 조사되기 때문이다.

유도 가열은 교류 자장 중에 도체를 놓고, 도체에 와 전류(eddy current)를 발생시켜 도체를 발열시키는 방법이다.

따라서, 유도 가열이 가능한 베이스 기판은 와 전류가 흐르기 쉬운 도체인 것이 바람직하다.

와 전류가 흐르기 쉬운 것은 어느 정도 저항이 높은 도체이므로, 유도 가열을 사용하는 경우는 베이스 기판으로서 실리콘 웨이퍼, 철 기판, 스테인리스 기판 등을 사용하는 것이 바람직하다.

접촉 가열은 베이스 기판이 원하는 온도에 도달될 때까지 시간이 걸리기 때문에, 베이스 기판이 원하는 온도에 도달될 때까지 시간이 짧은 광 조사에 의한 가열, 유도 가열 등을 사용하면 처리 시간을 단축할 수 있다. 또한, 유도 가열로 도체를 가열하고, 도체로부터의 열 전도를 이용한 가열 방법을 사용하여도 좋다.

또한, 레이저 광의 조사 분위기를 불활성 기체 분위기(질소, 희 가스 등)로 함으로써 분위기 중으로부터 산소가 혼입되는 것을 방지할 수 있어 바람직하다.

또한, 레이저 광의 조사 분위기를 감압 분위기(기압이 10-3Pa 이하의 분위기)로 함으로써, 분위기 중으로부터 산소가 혼입되는 것을 방지할 수 있어 바람직하다.

또한, 레이저 광의 조사 분위기를 환원 분위기(수소를 함유한 분위기, 일산화탄소를 함유한 분위기, 요오드화 수소를 함유한 분위기 등(환원 가스만이라도 좋고, 환원 가스와 불활성 기체의 혼합 가스라도 좋음))으로 함으로써 환원 반응이 생기므로, 산소의 외방 확산을 촉진할 수 있어 바람직하다.

즉, 레이저 광의 조사 분위기에 환원 가스를 포함시키면 바람직하다.

특히, 요오드화 수소를 함유한 분위기는 환원 작용이 있는 동시에 할로겐인 요오드에 의하여 중금속 등의 오염을 제거할 수 있어 바람직하다.

또한, 감압 분위기 또 불활성 기체 분위기, 또는 감압 분위기 또 환원 분위기로 하면, 산소 저감 효과가 더 높아지므로 바람직하다.

또한, 레이저 광을 조사하기 전에 불화 수소 용액을 사용하여 반도체층의 자연 산화막을 제거해 두는 것이 바람직하다.

자연 산화막은 불균일하게 형성되기 때문에, 자연 산화막이 존재하면 레이저 광을 조사한 후의 반도체막의 결정 상태에 불균일이 생기기 때문이다. 또한, 산소가 자연 산화막으로부터 반도체층으로 확산되는 것을 방지하기 위해서이다.

한편, 공정수를 삭감하기 위하여, 불화 수소 용액을 사용하는 대신에, 감압 분위기, 환원 분위기, 또는 감압 분위기 또 환원 분위기 등의 분위기에 불화 수소를 함유시켜도 좋다.

또한, 대기 분위기, 불활성 기체 분위기(희 가스, 질소 등)에 불화 수소를 함유시켜도 좋다.

물론, 불화 수소 분위기만이라도 좋다.

즉, 레이저 광의 조사 분위기에 불화 수소 가스를 포함시키면 바람직하다.

불화 수소는 산화실리콘막을 제거하는 작용이 있기 때문에, 반도체층 표면의 자연 산화막을 제거하면서 레이저 광을 조사할 수 있어 바람직하다.

특히, 불화 수소를 함유한 분위기 중에 잠시 SOI 기판을 노출한 직후에 연속적으로 레이저 광을 조사하면, 자연 산화막을 확실히 제거한 후 레이저 광을 조사 할 수 있어 바람직하다(연속적으로 레이저 광을 조사하므로 공정수도 삭감할 수 있음).

또한, 요오드화 수소, 불화 수소 등은 금속을 침식하기 쉬우므로, 요오드화 수소, 불화 수소 등을 분위기에 도입할 때는, 레이저 광의 조사를 행하는 처리실 내의 내벽, 스테이지 등을 사파이어, 다이아몬드 라이크 카본 등으로 코팅해 두면 바람직하다.

또한, 레이저 광의 조사 분위기의 온도를 높게 하면, 용융 상태의 유지 시간이 길어져 바람직하다.

베이스 기판의 가열 온도가 500℃ 이상인 경우에 산소 저감의 효과가 있는 것을 고려하면, 레이저 광의 조사 분위기의 온도도 500℃ 이상인 것이 바람직하다.

또한, 레이저 광의 조사 분위기의 온도 범위의 상한 값은 600℃ 이하(또는 600℃ 미만), 650℃ 이하(또는 650℃ 미만), 700℃ 이하(또는 700℃ 미만), 750℃ 이하(또는 750℃ 미만), 800℃ 이하(또는 800℃ 미만), 850℃ 이하(또는 850℃ 미만), 900℃ 이하(또는 900℃ 미만), 950℃ 이하(또는 950℃ 미만), 1000℃ 이하(또는 1000℃ 미만), 1050℃ 이하(또는 1050℃ 미만), 1100℃ 이하(또는 1100℃ 미만), 1150℃ 이하(또는 1150℃ 미만), 1200℃ 이하(또는 1200℃ 미만), 1250℃ 이하(또는 1250℃ 미만), 1300℃ 이하(또는 1300℃ 미만), 1350℃ 이하(또는 1350℃ 미만), 1400℃ 이하(또는 1400℃ 미만) 중에서 선택하여도 좋다. 또한, X℃ 미만이란, X℃보다 낮은 온도를 가리킨다(X는 임의의 수임).

또한, 레이저 광의 조사 분위기의 온도 범위의 하한 값은 500℃ 이상(또는 500℃ 초과), 550℃ 이상(또는 550℃ 초과), 650℃ 이상(또는 650℃ 초과), 600℃ 이상(또는 600℃ 초과), 650℃ 이상(또는 650℃ 초과), 700℃ 이상(또는 700℃ 초과), 750℃ 이상(또는 750℃ 초과), 800℃ 이상(또는 800℃ 초과), 850℃ 이상(또는 850℃ 초과), 900℃ 이상(또는 900℃ 초과), 950℃ 이상(또는 950℃ 초과), 1000℃ 이상(또는 1000℃ 초과), 1050℃ 이상(또는 1050℃ 초과), 1100℃ 이상(또는 1100℃ 초과), 1150℃ 이상(또는 1150℃ 초과), 1200℃ 이상(또는 1200℃ 초과), 1250℃ 이상(또는 1250℃ 초과), 1300℃ 이상(또는 1300℃ 초과), 1350℃ 이상(또는 1350℃ 초과) 중에서 선택하여도 좋다. 또한, X℃ 초과란, X℃보다 높은 온도를 가리킨다(X는 임의의 수임).

다만, 레이저 광의 조사 분위기의 온도 범위의 상한 값은 레이저 광의 조사 분위기의 온도 범위의 하한 값보다 큰 것으로 한다.

상술한 바와 같이, 산소를 저감시킨 SOI 기판을 형성할 수 있다.

또한, 레이저 광의 조사는 구멍이 발생되는 것을 회피하기 위하여 단결정 반도체층의 막 두께의 평균 값이 100㎚ 이상의 상태에서 행하는 것이 바람직하다.

그러나, 축척 법칙(scaling law)에 따르면, 단결정 반도체층의 막 두께가 얇으면 얇을수록 트랜지스터의 특성이 상승되는 것이 알려져 있다.

따라서, 단결정 반도체층의 막 두께를 100㎚보다 얇게 하고 싶은 경우에는 100㎚ 이상의 막 두께로 레이저 광을 조사하고, 레이저 광을 조사한 후에 막 두께를 100㎚보다 얇게 하기 위한 박막화 에칭을 행하면 바람직하다(도 5a 및 도 5b 참조).

또한, 레이저 광을 조사할 때의 단결정 반도체층의 막 두께가 300㎚보다 두꺼우면, 레이저 광을 충분히 흡수할 수 없는 경우가 있으므로, 레이저 광을 조사할 때의 단결정 반도체층의 막 두께가 300㎚ 이하인 것이 바람직하다.

본 실시형태는 다른 모든 실시형태와 조합하여 실시할 수 있다.

(실시형태 2)

본 실시형태에서는 SOI 기판을 사용하여 형성한 반도체 장치의 제작 방법의 일례에 대하여 설명한다.

우선, 베이스 기판(100)과, 베이스 기판(100) 위에 형성된 접합층(200)과, 접합층(200) 위에 형성된 단결정 반도체층(300)을 갖는 구조의 SOI 기판을 준비한다(도 6a 참조).

베이스 기판, 접합층, 단결정 반도체층은 각각 실시형태 1에 기재한 것과 같은 재료를 사용할 수 있다.

다음에, 단결정 반도체층(300)을 에칭하여 섬 형상으로 가공한다.

여기서는, 섬 형상 반도체층(301, 302) 등을 형성한다(소자 분리 공정).

그리고, 섬 형상 반도체층(301, 302) 위에 게이트 절연막(400), 게이트 전극(501, 502)을 순차로 형성한다(도 6b 참조).

게이트 절연막은 열 산화막, 산화실리콘막, 질화실리콘막, 질화산화실리콘막, 산화질화실리콘막, 하프늄 화합물막 등을 사용할 수 있다.

게이트 절연막은 단층과 적층의 어느 쪽이라도 좋다.

게이트 전극은 텅스텐, 몰리브덴, 알루미늄, 티타늄, 실리콘 등을 사용할 수 있다.

게이트 전극은 단층과 적층의 어느 쪽이라도 좋다.

다음에, 섬 형상 반도체층(301)에 제 1 불순물 원소를 선택적으로 첨가하여 불순물 영역(301a, 301b)을 형성한다(도 6c 참조).

또한, 섬 형상 반도체층(302)에 제 2 불순물 원소를 선택적으로 첨가하여 불순물 영역(302a, 302b)을 형성한다(도 6c 참조).

제 1 불순물 원소와 제 2 불순물 원소는 어느 쪽을 먼저 첨가하여도 좋다.

또한, 제 1 불순물 원소는 도너 원소(인, 비소 등) 또는 억셉터 원소(붕소 등)의 한쪽이다.

또한, 제 2 불순물 원소는 도너 원소(인, 비소 등) 또는 억셉터 원소(붕소 등)의 다른 쪽이다.

또한, 불순물 영역(301a, 301b, 302a, 302b)에는 마스크 또는 사이드 월 등을 사용하여 LDD 영역을 형성하여도 좋다.

다음에, 게이트 전극 위에 층간 절연막(600)을 형성하고, 층간 절연막(600)에 콘택트 홀을 형성하고, 층간 절연막(600) 위에 콘택트 홀을 통하여 반도체층 및 게이트 전극과 전기적으로 접속되는 배선(701a 내지 701c, 702a 내지 702c)을 형성한다(도 7a 및 도 7b 참조).

또한, 도 7a 및 도 7b는 상이한 개소의 단면도이다.

그리고, 게이트 전극과 배선의 콘택트 개소는 게이트 전극 아래에 반도체층이 존재하지 않는 개소로 한다(도 7b 참조).

층간 절연막은 산화실리콘막, 질화실리콘막, 질소를 함유한 산화실리콘막, 산소를 함유한 질화실리콘막, 폴리이미드, 아크릴, 실록산 폴리머 등을 사용할 수 있다.

층간 절연막은 단층과 적층의 어느 쪽이라도 좋다.

배선은 알루미늄, 티타늄, 몰리브덴, 텅스텐, 금, 은, 구리 등의 금속, 또는 ITO(산화인듐주석) 등의 투명 도전물을 사용할 수 있다.

배선은 단층과 적층의 어느 쪽이라도 좋다.

본 실시형태는 다른 모든 실시형태와 조합하여 실시할 수 있다.

(실시형태 3)

본 실시형태에서는 SOI 기판을 사용하여 형성한 반도체 장치의 제작 방법의 일례에 대하여 설명한다.

우선, 베이스 기판(1100)과, 베이스 기판(1100) 위에 형성된 접합층(1200)과, 접합층(1200) 위에 형성된 단결정 반도체층(1300)을 갖는 구조의 SOI 기판을 준비한다(도 8a 참조).

베이스 기판, 접합층, 단결정 반도체층은 각각 실시형태 1에 기재한 것과 같은 재료를 사용할 수 있다.

다음에, 단결정 반도체층(1300) 위에 섬 형상의 마스크 절연막(1400)을 형성한다(도 8b 참조).

다음에, 마스크 절연막(1400)을 마스크로서 사용하여 단결정 반도체층(1300)을 에칭하여 섬 형상으로 한다(섬 형상 반도체층(1301, 1302) 등을 형성함; 도 8c 참조, 소자 분리 공정).

다음에, 마스크 절연막(1400) 위에 절연막을 형성하고, 절연막을 에치 백 또는 연마하여 섬 형상 반도체층 사이를 채우는 매립(embedded) 절연막(1500)을 형성한다(도 9a 참조).

여기서, 마스크 절연막(1400) 및 매립 절연막(1500)은 산화실리콘막, 질화실리콘막, 질화산화실리콘막, 산화질화실리콘막 등을 사용할 수 있다.

다만, 마스크 절연막(1400)을 매립 절연막(1500)을 형성할 때의 에칭 스토퍼로서 사용하기 위해서는 마스크 절연막(1400)과 매립 절연막(1500)을 상이한 재질의 막으로 하는 것이 바람직하다.

다음에, 마스크 절연막(1400)을 제거한다(도 9b 참조).

다음에, 섬 형상 반도체층(1301) 위에 게이트 절연막(1601)을 형성함과 함께, 섬 형상 반도체층(1302) 위에 게이트 절연막(1602)을 형성한다(도 9c 참조).

게이트 절연막은 열 산화막, 산화실리콘막, 질화실리콘막, 질화산화실리콘막, 산화질화실리콘막, 하프늄 화합물막 등을 사용할 수 있다.

게이트 절연막은 단층과 적층의 어느 쪽이라도 좋다.

다음에, 게이트 절연막 위에 실리콘을 주성분으로 하는 게이트 전극(1701) 및 실리콘을 주성분으로 하는 게이트 전극(1702)을 형성한다(도 10a 참조).

실리콘을 주성분으로 하는 게이트 전극에는 도너 원소 또는 억셉터 원소를 첨가하여 저항 값을 낮추는 것이 바람직하다.

또한, 도 10a에 도시하는 바와 같이 게이트 전극을 형성할 때, 게이트 절연 막도 동시에 에칭하여 게이트 절연막(1601, 1602)을 형성한다.

또한, 게이트 전극은 섬 형상 반도체층과 중첩되는 위치 및 매립 절연막과 중첩되는 위치에 형성된다.

한편, 매립 절연막(1500)은 섬 형상 반도체층과 대략 같은 막 두께가 되도록 형성된다.

따라서, 매립 절연막이 존재함으로써 섬 형상 반도체층의 에지의 단차가 낮아지므로, 섬 형상 반도체층의 에지의 단차로 인하여 게이트 절연막이 단절되어 게이트 전극과 섬 형상 반도체층이 단락되어 버리는 것을 방지할 수 있다.

또한, 섬 형상 반도체층의 에지는 도 15의 파선(18001, 18002)으로 도시된 부분이다.

도 15는 섬 형상 반도체층(11301)과, 섬 형상 반도체층(11301)의 주위에 형성된 매립 절연막(11500)과, 섬 형상 반도체층(11301) 및 매립 절연막(11500)과 중첩되는 위치에 배치된 게이트 전극(11701)과, 섬 형상 반도체층(11301)과 배선의 콘택트 영역(12401a, 12401b)과, 게이트 전극과 배선의 콘택트 영역(12401c)을 도시한 것이다.

다음에, 게이트 전극(1701, 1702), 섬 형상 반도체층(1301, 1302)을 산화하여 산화막(1801) 및 산화막(1802)을 형성한다(도 10b 참조).

또한, 산화막 대신에 질화막을 형성하여도 좋고, 산화와 질화를 동시에 행한 절연막으로 하여도 좋다.

다음에, 섬 형상 반도체층(1301)의 얕은 깊이에 억셉터 원소(붕소)를 선택적 으로 첨가하여 저농도 불순물 영역(1311a, 1311b)을 형성한다(도 10c 참조).

또한, 섬 형상 반도체층(1302)의 얕은 깊이에 도너 원소(비소)를 선택적으로 첨가하여 저농도 불순물 영역(1312a, 1312b)을 형성한다(도 10c 참조).

여기서, 인이 아니라 비소를 첨가하는 이유는 활성화 처리시의 열 확산을 억제하기 위하여 확산 계수가 낮은 원소를 사용하기 때문이다.

열이 확산되는 것을 상관하지 않으면 인을 사용하여도 좋다.

또한, 도너 원소와 억셉터 원소는 어느 쪽을 먼저 첨가하여도 좋다.

다음에, 게이트 전극(1701)을 덮는 사이드 월 형성용 절연막(1901)과, 게이트 전극(1702)을 덮는 사이드 월 형성용 절연막(1902)과, 사이드 월 형성용 절연막(1901, 1902) 위에 형성된 사이드 월 형성용 절연막(1903)을 형성한다(도 11a 참조).

다음에, 사이드 월 형성용 절연막을 에치 백하여, 사이드 월(1901a, 1901b, 1902a, 1902b, 1903a, 1903b)을 형성한다(도 11b 참조).

또한, 사이드 월(1901a, 1901b)은 사이드 월 형성용 절연막(1901)을 에칭하여 형성한 것이고, 사이드 월(1902a, 1902b)은 사이드 월 형성용 절연막(1902)을 에칭하여 형성한 것이고, 사이드 월(1903a, 1903b)은 사이드 월 형성용 절연막(1903)을 에칭하여 형성한 것이다.

사이드 월 형성용 절연막은 산화실리콘막, 질화실리콘막, 질화산화실리콘막, 산화질화실리콘막 등을 사용할 수 있다.

다만, 게이트 전극(1701)의 측벽에 형성되는 사이드 월의 폭을 게이트 전 극(1702)의 측벽에 형성되는 사이드 월의 폭보다 넓게 하기 위하여, 사이드 월 형성용 절연막(1901)의 막 두께를 사이드 월 형성용 절연막(1902)의 막 두께보다 두껍게 한다.

또한, 게이트 전극(1701)의 측벽에 형성되는 사이드 월의 단면 형상이 L자 형상이 되도록 하기 위하여, 사이드 월 형성용 절연막(1903)의 재료와 사이드 월 형성용 절연막(1901)의 재료를 상이한 것으로 한다.

사이드 월 형성용 절연막(1901)의 막 두께를 사이드 월 형성용 절연막(1902)의 막 두께보다 두껍게 하고, 또 사이드 월 형성용 절연막(1903)의 재료와 사이드 월 형성용 절연막(1901)의 재료를 상이한 것으로 함으로써, 사이드 월 형성용 절연막(1903)이 마스크로서 기능하므로, 게이트 전극(1701)의 측벽에 형성되는 사이드 월의 단면 형상이 L자 형상이 되고, 사이드 월의 폭을 넓게 할 수 있다.

즉, 사이드 월 형성용 절연막(1901)의 막 두께를 사이드 월 형성용 절연막(1902)의 막 두께보다 두껍게 하고, 또 사이드 월 형성용 절연막(1903)의 재료와 사이드 월 형성용 절연막(1901)의 재료와 상이한 것으로 함으로써, 동일한 에치 백 공정으로 폭이 상이한 사이드 월을 형성할 수 있다.

다음에, 노출된 산화막(1801, 1802)을 제거한다(도 11c 참조).

또한, 사이드 월 형성시의 에치 백은 노출된 산화막(1801, 1802)을 제거하였을 때, 게이트 전극의 정상이 돌출되는 조건으로 에칭한다(도 11c의 파선(8001, 8002) 참조).

게이트 전극의 정상이 돌출되어 게이트 전극의 측벽이 일부분 노출됨으로써, 이후의 실리사이드화 공정에 있어서 게이트 전극의 실리사이드화를 촉진할 수 있다.

구체적으로는, 게이트 전극의 정상이 돌출되므로 금속막과 접촉 면적이 커져, 실리사이드화가 촉진되어 실리사이드 영역의 막 두께를 두껍게 할 수 있다.

또한, 도 15의 파선(18003)에 도시하는 바와 같이 게이트 전극의 콘택트부는 섬 형상 반도체층과 중첩되는 위치에서 떨어진 위치에 형성되기 때문에, 실리사이드 영역의 막 두께를 두껍게 하여 게이트 전극의 저저항화를 행하는 것은 바람직하다.

다음에, 섬 형상 반도체층(1301)에 억셉터 원소(붕소)를 선택적으로 첨가하여 고농도 불순물 영역(1321a, 1321b)을 형성한다(도 12a 참조).

또한, 섬 형상 반도체층(1302)에 도너 원소(비소)를 선택적으로 첨가하여 고농도 불순물 영역(1322a, 1322b)을 형성한다(도 12a 참조).

여기서, 인이 아니라 비소를 첨가하는 이유는 활성화 처리시의 열 확산을 억제하기 위하여 확산 계수가 낮은 원소를 사용하기 때문이다.

또한, 도너 원소와 억셉터 원소는 어느 쪽을 먼저 첨가하여도 좋다.

열이 확산되는 것을 상관하지 않으면 인을 사용하여도 좋다.

다음에, 활성화 처리를 행한다(도 12b 참조).

활성화 처리에 의하여 열 확산이 생겨 불순물 원소의 확산이 생긴다(도 12b의 파선(8011a, 8011b, 8012a, 8012b 등 참조).

사이드 월의 폭이 짧은 트랜지스터는 확산 계수가 낮은 비소를 첨가해 두면, 확산되는 거리가 짧아지므로 확산으로 인하여 LDD 영역이 손실해 버리는 것을 방지할 수 있다(도 12b의 파손(8011a, 8011b, 8012a, 8012b 참조).

다음에, 금속막(2000)을 형성하고, 가열 처리를 행함으로써 실리사이드 영역(2001a 내지 2001c, 2002a 내지 2002c)을 형성한다(도 12c 참조).

금속막으로서는, 코발트, 니켈, 텅스텐 등을 사용할 수 있다.

여기서, 게이트 전극의 정상을 돌출시킴으로써 실리사이드 영역의 막 두께를 두껍게 할 수 있다.

실리사이드 영역의 막 두께를 두껍게 함으로써 게이트 전극의 저저항화가 가능하다.

다음에, 금속막(2000)을 제거하고, 게이트 전극(1701, 1702) 위에 층간 절연막(2100)을 형성하고, 층간 절연막(2100) 위의 게이트 전극(1702) 위에 선택적으로 층간 절연막(2200)을 형성한다(도 13a 참조).

다음에, 층간 절연막(2200)을 마스크로서 사용하여 층간 절연막(2100)을 에치 백하여 사이드 월(2101a, 2101b)을 형성한다(도 13b 참조).

다음에, 층간 절연막(2101)을 게이트 전극(1702) 위에 선택적으로 형성하고, 층간 절연막(2101, 2200) 위에 층간 절연막(2300)을 형성한다(도 13c 참조).

층간 절연막은 산화실리콘막, 질화실리콘막, 질화산화실리콘막, 산화질화실리콘막, 폴리이미드, 아크릴, 실록산 폴리머 등을 사용할 수 있다.

다만, 층간 절연막(2200)을 마스크로서 사용하여 층간 절연막(2100)을 에치 백하기 때문에, 층간 절연막(2200)과 층간 절연막(2100)은 상이한 재료로 하는 것 이 바람직하다.

또한, n채널형 트랜지스터 위에 형성되는 층간 절연막을 인장 응력을 갖게 하고, 또 p채널형 트랜지스터 위에 형성되는 층간 절연막을 압축 응력을 갖게 하면, n채널형 트랜지스터 및 p채널형 트랜지스터의 특성값이 상승된다.

따라서, 층간 절연막(2100)을 인장 응력을 갖는 막으로 하고, 층간 절연막(2200)을 압축 응력을 갖는 막으로 하면 바람직하다(다만, 층간 절연막(2100)의 인장 응력의 값은 층간 절연막(2200)의 압축 응력보다 작은 값으로 함).

다음에, 층간 절연막에 콘택트 홀을 형성하고, 층간 절연막 위에 콘택트 홀을 통하여 트랜지스터와 접속되는 배선(2401a 내지 2401c, 2402a 내지 2402c)을 형성한다(도 14a 참조).

또한, 도 14a와 도 14b는 상이한 개소의 단면도이다.

그리고, 게이트 전극과 배선의 콘택트 개소는 게이트 전극 아래에 반도체층이 존재하지 않는 개소로 한다(도 14b).

배선은 알루미늄, 티타늄, 몰리브덴, 텅스텐, 금, 은, 구리 등의 금속, 또는 ITO(산화인듐주석) 등의 투명 도전물을 사용할 수 있다.

배선은 단층과 적층의 어느 쪽이라도 좋다.

본 실시형태는 다른 모든 실시형태와 조합하여 실시할 수 있다.

(실시예 1)

본 발명자들은 베이스 기판과, 베이스 기판 위에 형성된 절연층(접합층)과, 절연층(접합층) 위에 형성된 단결정 반도체층을 갖는 SOI 구조로 이루어진 샘플을 복수개 준비하여, SIMS 분석(2차 이온 질량 분석)을 행하여 단결정 반도체층 중의 산소의 농도를 측정하는 실험을 행하였다.

(제 1 설명: 샘플의 제작 방법)

우선, 염화수소를 함유한 분위기 중에서 950℃의 온도로 열 산화를 행함으로써 실리콘 웨이퍼의 표면에 열 산화막을 100㎚의 막 두께로 형성하였다.

다음에, 열 산화막을 형성한 실리콘 웨이퍼에 질량 분리를 행하지 않는 이온 도핑법을 사용하여 수소를 첨가하였다.

또한, 이온 도핑은 수소 가스를 도핑 가스로서 사용하여 가속 전압을 50㎸로 설정하여 행하였다.

다음에, 유리 기판(ASAHI GLASS CO., LTD. AN100 기판)으로 이루어진 베이스 기판을 준비하였다.

그리고, 베이스 기판의 표면과 열 산화막의 표면을 세정한 후, 베이스 기판의 표면과 열 산화막의 표면을 접합하였다.

다음에, 200℃로 2시간의 가열 처리(접합 강화)를 행하고, 이어서 600℃로 2시간의 가열 처리(균열 형성)를 행함으로써 SOI 기판을 형성하였다.

그 후, SOI 기판의 단결정 반도체층의 표면을 드라이 에칭법에 의하여 에치 백하였다.

에치 백 후의 SOI 기판의 단결정 반도체층의 막 두께의 평균 값은 105㎚이었다.

또한, 단결정 반도체층의 막 두께의 평균값은 광학적인 막 두께 측정기(나노 스펙)를 사용하여 복수의 개소를 측정하여 복수의 개소의 평균값으로부터 산출하였다.

그리고, 상술한 공정과 같은 공정을 거친 복수의 샘플을 형성하였다.

(제 2 설명: 샘플의 종류)

참조 샘플은 레이저 광을 조사하지 않은 샘플이다.

제 1 샘플은 베이스 기판을 가열하지 않고, 단결정 반도체층에 레이저 광을 조사한 샘플이다.

제 2 샘플은 베이스 기판의 온도를 300℃로 하여 단결정 반도체층에 레이저 광을 조사한 샘플이다.

제 3 샘플은 베이스 기판의 온도를 500℃로 하여 단결정 반도체층에 레이저 광을 조사한 샘플이다.

또한, 레이저 광의 조사 분위기는 질소 분위기로 하였다.

또한, 레이저는 엑시머 레이저를 사용하였다.

또한, 레이저 광을 조사할 때 부분 용융하였다.

또한, 베이스 기판과 접촉되는 스테이지를 가열함으로써 베이스 기판을 접촉 가열하였다.

(제 3 설명: SIMS 측정 결과)

참조 샘플(레이저 광이 조사되지 않았음), 제 1 샘플(레이저 광이 조사되었음(실온)), 제 2 샘플(레이저 광이 조사되었음(300℃)), 제 3 샘플(레이저 광이 조사되었음(500℃))의 단결정 반도체층 중의 산소 농도를 측정하기 위하여 SIMS 분 석(2차 이온 질량 분석)을 행하였다.

참조 샘플(레이저 광이 조사되지 않았음), 제 1 샘플(레이저 광이 조사되었음(실온)), 제 2 샘플(레이저 광이 조사되었음(300℃)), 및 제 3 샘플(레이저 광이 조사되었음(500℃))의 SIMS 측정 결과를 정리한 것을 도 16에 도시한다.

또한, 참조 샘플(레이저 광이 조사되지 않았음), 제 1 샘플(레이저 광이 조사되었음(실온))을 비교한 것을 도 17에 도시한다.

또한, 제 1 샘플(레이저 광이 조사되었음(실온)), 제 2 샘플(레이저 광이 조사되었음(300℃)), 제 3 샘플(레이저 광이 조사되었음(500℃))을 비교한 것을 도 18에 도시한다.

도 16 내지 도 18에 있어서, 그래프(20000)가 참조 샘플(레이저 광이 조사되지 않았음)의 측정 결과이고, 그래프(20001)가 제 1 샘플(레이저 광이 조사되었음(실온))의 측정 결과이고, 그래프(20002)가 제 2 샘플(레이저 광이 조사되었음(300℃))의 측정 결과이고, 그래프(20003)가 제 3 샘플(레이저 광이 조사되었음(500℃))의 측정 결과이다.

또한, 도 16 내지 도 18의 그래프 중 부호가 같은 것은 같은 데이터에 의거하는 그래프이다.

또한, 도 16 내지 도 18에 있어서, 1E+n(n은 자연수)은 10의 n승을 뜻한다.

(제 4 설명: 고찰)

우선, 도 16 내지 도 18의 그래프를 어떻게 해석하는지에 대하여 설명한다.

SIMS 분석에 의하여 검출되는 산소 농도 중, 단결정 반도체층 표면 근방(도 면 중의 막 두께가 0㎚ 내지 20㎚의 범위) 및 단결정 반도체층과 접합층의 계면 근방(도면 중의 막 두께가 80㎚ 내지 105㎚의 범위)은 보통 측정 정밀도가 떨어지는 영역이므로, 단결정 반도체층 중의 산소 농도를 비교하는 경우는 참고가 되지 않는다.

측정 정밀도가 떨어지는 이유는 녹온(knock-on) 효과의 영향, 단결정 반도체층 표면의 요철의 영향, 단결정 반도체층 표면의 오염의 영향을 생각할 수 있다(오염에 대해서는 SIMS 장치가 청정한 분위기인 크린 룸 밖에 있고, SIMS 분석을 위한 샘플을 청정한 분위기 밖으로 반출했기 때문이라고 생각됨).

따라서, 도면 중의 막 두께가 20㎚ 내지 80㎚의 범위의 산소 농도를 비교하면 좋다.

우선, 레이저 광이 조사되지 않은 참조 샘플과, 레이저 광이 조사된 제 1 샘플 내지 제 3 샘플을 비교하면, 적어도 레이저 광을 조사하면 산소 농도가 감소되는 것을 알 수 있다(도 16 참조).

특히, 레이저 광이 조사되지 않은 참조 샘플과 실온에서 레이저 광이 조사된 제 1 샘플을 비교하여도, 제 1 샘플은 산소 농도가 감소되기 때문에, 기판을 가열하지 않아도 산소 농도의 감소 효과를 얻을 수 있는 것을 알 수 있다(도 16 및 도 17 참조).

다음에, 제 1 샘플(레이저 광이 조사되었음(실온)), 제 2 샘플(레이저 광이 조사되었음(300℃)), 제 3 샘플(레이저 광이 조사되었음(500℃))을 비교한다(도 16 및 도 18 참조).

제 1 샘플(레이저 광이 조사되었음(실온))과 제 2 샘플(레이저 광이 조사되었음(300℃))은 산소 농도에 거의 차이가 없다.

한편, 제 1 샘플(레이저 광이 조사되었음(실온))과 제 3 샘플(레이저 광이 조사되었음(500℃))을 비교하면, 제 3 샘플(레이저 광이 조사되었음(500℃))은 산소 농도가 감소되는 것을 알 수 있다.

따라서, 적어도 베이스 기판의 온도를 500℃로 한 상태에서 레이저 광을 조사하면, 산소 농도가 감소되는 것을 알 수 있다.

상술한 결과에 의거하면, 본 발명자들은 레이저 광을 조사함으로써 산소 농도가 감소된 이유는 단결정 반도체층이 산소의 확산 계수가 높은 용융 상태가 되어 산소의 외방 확산이 촉진되어 산소 농도가 감소되기 때문이라고 생각하였다.

또한, 본 발명자들은 300℃의 기판 가열은 산소의 감소가 현저하지 않고, 500℃의 기판 가열은 산소의 감소가 현저하므로, 확산 계수가 높은 용융 상태의 유지 시간이 길수록 산소의 외방 확산이 촉진된다고 생각하였다.

따라서, 기판 가열의 온도가 높을수록 용융 상태의 유지 시간이 길어지는 것이 분명하므로, 500℃보다 높은 온도의 기판 가열을 행하면 산소의 감소가 촉진되는 것은 분명하다.

따라서, 적어도 레이저 광을 조사함으로써 산소의 외방 확산이 생기므로, 산소 농도를 감소시킬 수 있다고 할 수 있다.

또한, 500℃ 이상의 온도로 가열하면서 레이저 광을 조사함으로써 산소의 외방 확산을 촉진할 수 있다고 할 수 있다.

(제 5 설명: 이온 도핑법에 대하여)

샘플 제작에 사용한 실리콘 웨이퍼는 산소 농도가 1.0×1018atom/㎤ 내지 2.0×1018atom/㎤가 되도록 제어된 실리콘 웨이퍼이었다.

그러나, 참조 샘플의 단결정 반도체층 중의 산소 농도는 2.0×1018atom/㎤보다 높은 값을 나타냈다.

따라서, SOI 기판의 제작 공정 중에서 산소 농도가 상승된 것은 분명하다.

산소 농도가 상승한 원인의 하나는 질량 분리를 행하지 않는 이온 도핑법을 사용하여 수소를 첨가하는 공정이다.

즉, 질량 분리를 행하지 않는 경우는 이온 도핑 처리 챔버 내의 분위기 중에 존재하는 원소를 모두 이온화하여 도핑되어 버린다.

그리고, 대기 중에는 산소가 대량으로 존재하기 때문에, 처리 챔버 내에 산소가 완전히 혼입되지 않도록 챔버 내 분위기를 관리하기 어렵다.

따라서, 질량 분리하지 않는 이온 도핑법을 사용하여 수소를 첨가하는 공정을 행하는 경우는, 단결정 반도체층 중에 산소도 동시에 도핑되어 버린다.

도 1a 내지 도 1c는 SOI 기판의 제작 방법의 일례.

도 2a 및 도 2b는 SOI 기판의 제작 방법의 일례.

도 3a 내지 도 3c는 SOI 기판의 제작 방법의 일례.

도 4a 및 도 4b는 SOI 기판의 제작 방법의 일례.

도 5a 및 도 5b는 SOI 기판의 제작 방법의 일례.

도 6a 내지 도 6c는 반도체 장치의 제작 방법의 일례.

도 7a 및 도 7b는 반도체 장치의 제작 방법의 일례.

도 8a 내지 도 8c는 반도체 장치의 제작 방법의 일례.

도 9a 내지 도 9c는 반도체 장치의 제작 방법의 일례.

도 10a 내지 도 10c는 반도체 장치의 제작 방법의 일례.

도 11a 내지 도 11c는 반도체 장치의 제작 방법의 일례.

도 12a 내지 도 12c는 반도체 장치의 제작 방법의 일례.

도 13a 내지 도 13c는 반도체 장치의 제작 방법의 일례.

도 14a 및 도 14b는 반도체 장치의 제작 방법의 일례.

도 15는 반도체 장치의 상면도의 일례.

도 16은 SIMS 분석 결과의 일례.

도 17은 SIMS 분석 결과의 일례.

도 18은 SIMS 분석 결과의 일례.

<도면의 주요 부분에 대한 부호의 설명>

11b: 제 2 영역 11d: 용융 상태의 반도체

12: 접합층 13: 베이스 기판

14: 레이저 광 80: 파선

90: 파선

Claims (24)

- 베이스 기판과, 상기 베이스 기판 위에 형성된 산소를 함유한 접합층과, 상기 산소를 함유한 접합층 위에 형성된 단결정 반도체층을 포함하는 SOI 구조를 형성하는 단계와;상기 베이스 기판이 500℃ 이상이고 상기 베이스 기판의 융점보다 낮은 온도로 가열되면서, 상기 단결정 반도체층의 일부분을 레이저 광을 조사함으로써 용융하는 단계를 포함하는, SOI 기판의 제작 방법.

- 제 1 항에 있어서,상기 레이저 광의 조사 분위기는 감압 분위기인, SOI 기판의 제작 방법.

- 제 1 항에 있어서,상기 레이저 광의 조사 분위기는 환원 가스를 포함하는, SOI 기판의 제작 방법.

- 제 1 항에 있어서,상기 레이저 광의 조사 분위기는 불화 수소 가스를 포함하는, SOI 기판의 제작 방법.

- 제 4 항에 있어서,상기 SOI 구조를 형성한 후이며 상기 레이저 광을 조사하기 전에, 상기 불화 수소 가스를 함유한 분위기에 상기 SOI 구조가 노출되는, SOI 기판의 제작 방법.

- 제 1 항에 있어서,상기 레이저 광이 조사될 때, 상기 베이스 기판이 광 조사와 유도 가열 중 하나에 의하여 가열되는, SOI 기판의 제작 방법.

- 제 1 항에 있어서,질량 분리하지 않는 이온 도핑법을 사용하여 단결정 반도체 기판에 취화 영역이 형성되고, 상기 단결정 반도체 기판의 일부분을 분리하기 위하여 상기 취화 영역이 가열 처리됨으로써, 상기 단결정 반도체층이 형성되는, SOI 기판의 제작 방법.

- 제 1 항에 따른 상기 SOI 기판을 사용하여 반도체 소자가 형성되는, 반도체 장치의 제작 방법.

- 베이스 기판과, 상기 베이스 기판 위에 형성된 산소를 함유한 접합층과, 상기 산소를 함유한 접합층 위에 형성된 단결정 반도체층을 포함하는 SOI 구조를 형성하는 단계와;상기 베이스 기판이 500℃ 이상이고 상기 베이스 기판의 융점보다 낮은 온도로 가열되면서, 상기 단결정 반도체층의 일부분을 레이저 광을 조사함으로써 용융하는 단계를 포함하고,상기 단결정 반도체층의 상기 일부분은 상기 접합층과 접촉하지 않는, SOI 기판의 제작 방법.

- 제 9 항에 있어서,상기 레이저 광의 조사 분위기는 감압 분위기인, SOI 기판의 제작 방법.

- 제 9 항에 있어서,상기 레이저 광의 조사 분위기는 환원 가스를 포함하는, SOI 기판의 제작 방법.

- 제 9 항에 있어서,상기 레이저 광의 조사 분위기는 불화 수소 가스를 포함하는, SOI 기판의 제작 방법.

- 제 12 항에 있어서,상기 SOI 구조를 형성한 후이며 상기 레이저 광을 조사하기 전에, 상기 불화 수소 가스를 함유한 분위기에 상기 SOI 구조가 노출되는, SOI 기판의 제작 방법.

- 제 9 항에 있어서,상기 레이저 광이 조사될 때, 상기 베이스 기판이 광 조사와 유도 가열 중의 하나에 의하여 가열되는, SOI 기판의 제작 방법.

- 제 9 항에 있어서,질량 분리하지 않는 이온 도핑법을 사용하여 단결정 반도체 기판에 취화 영역이 형성되고, 상기 단결정 반도체 기판의 일부분을 분리하기 위하여 상기 취화 영역이 가열 처리됨으로써, 상기 단결정 반도체층이 형성되는, SOI 기판의 제작 방법.

- 제 9 항에 따른 상기 SOI 기판을 사용하여 반도체 소자가 형성되는, 반도체 장치의 제작 방법.

- 베이스 기판과, 상기 베이스 기판 위에 형성된 산소를 함유한 접합층과, 상기 산소를 함유한 접합층 위에 형성된 단결정 반도체층을 포함하는 SOI 구조를 형성하는 단계와;상기 단결정 반도체층을 에치 백하는 단계와;상기 베이스 기판이 500℃ 이상이고 상기 베이스 기판의 융점보다 낮은 온도로 가열되면서, 상기 단결정 반도체층의 일부분을 레이저 광을 조사함으로써 용융하는 단계를 포함하고,상기 에치 백 단계를 행한 후이며 상기 용융 단계를 행하기 전에, 상기 단결정 반도체층의 두께의 평균 값은 100㎚이상인, SOI 기판의 제작 방법.

- 제 17 항에 있어서,상기 레이저 광의 조사 분위기는 감압 분위기인, SOI 기판의 제작 방법.

- 제 17 항에 있어서,상기 레이저 광의 조사 분위기는 환원 가스를 포함하는, SOI 기판의 제작 방법.

- 제 17 항에 있어서,상기 레이저 광의 조사 분위기는 불화 수소 가스를 포함하는, SOI 기판의 제작 방법.

- 제 20 항에 있어서,상기 SOI 구조를 형성한 후이며 상기 레이저 광을 조사하기 전에, 상기 불화 수소 가스를 함유한 분위기에 상기 SOI 구조가 노출되는, SOI 기판의 제작 방법.

- 제 17 항에 있어서,상기 레이저 광이 조사될 때, 상기 베이스 기판이 광 조사와 유도 가열 중의 하나에 의하여 가열되는, SOI 기판의 제작 방법.

- 제 17 항에 있어서,질량 분리하지 않는 이온 도핑법을 사용하여 단결정 반도체 기판에 취화 영역이 형성되고, 상기 단결정 반도체 기판의 일부분을 분리하기 위하여 상기 취화 영역이 가열 처리됨으로써, 상기 단결정 반도체층이 형성되는, SOI 기판의 제작 방법.

- 제 17 항에 따른 상기 SOI 기판을 사용하여 반도체 소자가 형성되는, 반도체 장치의 제작 방법.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008318377 | 2008-12-15 | ||

| JPJP-P-2008-318377 | 2008-12-15 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020160128549A Division KR20160120266A (ko) | 2008-12-15 | 2016-10-05 | Soi 기판의 제작 방법, 반도체 장치의 제작 방법 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20100069595A true KR20100069595A (ko) | 2010-06-24 |

Family

ID=42241035

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020090123832A KR20100069595A (ko) | 2008-12-15 | 2009-12-14 | Soi 기판의 제작 방법, 반도체 장치의 제작 방법 |

| KR1020160128549A KR20160120266A (ko) | 2008-12-15 | 2016-10-05 | Soi 기판의 제작 방법, 반도체 장치의 제작 방법 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020160128549A KR20160120266A (ko) | 2008-12-15 | 2016-10-05 | Soi 기판의 제작 방법, 반도체 장치의 제작 방법 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8394703B2 (ko) |

| JP (1) | JP5610759B2 (ko) |

| KR (2) | KR20100069595A (ko) |

| CN (1) | CN101752294B (ko) |

| SG (2) | SG182208A1 (ko) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2972564B1 (fr) * | 2011-03-08 | 2016-11-04 | S O I Tec Silicon On Insulator Tech | Procédé de traitement d'une structure de type semi-conducteur sur isolant |

| TWI664731B (zh) * | 2013-05-20 | 2019-07-01 | 半導體能源研究所股份有限公司 | 半導體裝置 |

| US9425063B2 (en) * | 2014-06-19 | 2016-08-23 | Infineon Technologies Ag | Method of reducing an impurity concentration in a semiconductor body, method of manufacturing a semiconductor device and semiconductor device |

| DE112015005339T5 (de) | 2014-11-28 | 2017-08-17 | Semiconductor Energy Laboratory Co., Ltd. | Halbleitervorrichtung, Modul und elektronisches Gerät |

| JP6850096B2 (ja) * | 2015-09-24 | 2021-03-31 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法及び電子機器の作製方法 |

| US10026843B2 (en) * | 2015-11-30 | 2018-07-17 | Taiwan Semiconductor Manufacturing Co., Ltd. | Fin structure of semiconductor device, manufacturing method thereof, and manufacturing method of active region of semiconductor device |

| US11255606B2 (en) * | 2015-12-30 | 2022-02-22 | Mattson Technology, Inc. | Gas flow control for millisecond anneal system |

| JP6579086B2 (ja) * | 2016-11-15 | 2019-09-25 | 信越半導体株式会社 | デバイス形成方法 |

| EP3586356B1 (de) * | 2017-02-21 | 2023-11-08 | EV Group E. Thallner GmbH | Verfahren zum bonden von substraten |

| KR20200143143A (ko) | 2019-06-14 | 2020-12-23 | 삼성전자주식회사 | 집적 회로 반도체 소자의 제조 방법 |

Family Cites Families (45)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6384013A (ja) * | 1986-09-27 | 1988-04-14 | Agency Of Ind Science & Technol | 半導体結晶層の製造方法 |

| FR2681472B1 (fr) | 1991-09-18 | 1993-10-29 | Commissariat Energie Atomique | Procede de fabrication de films minces de materiau semiconducteur. |

| US5923962A (en) | 1993-10-29 | 1999-07-13 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a semiconductor device |

| TW264575B (ko) | 1993-10-29 | 1995-12-01 | Handotai Energy Kenkyusho Kk | |

| US6444506B1 (en) | 1995-10-25 | 2002-09-03 | Semiconductor Energy Laboratory Co., Ltd. | Method of manufacturing silicon thin film devices using laser annealing in a hydrogen mixture gas followed by nitride formation |

| US6391690B2 (en) | 1995-12-14 | 2002-05-21 | Seiko Epson Corporation | Thin film semiconductor device and method for producing the same |

| US5970368A (en) | 1996-09-30 | 1999-10-19 | Kabushiki Kaisha Toshiba | Method for manufacturing polycrystal semiconductor film |

| JPH1140501A (ja) | 1997-05-20 | 1999-02-12 | Fujitsu Ltd | 半導体装置の製造方法及び半導体装置 |

| US6534380B1 (en) | 1997-07-18 | 2003-03-18 | Denso Corporation | Semiconductor substrate and method of manufacturing the same |

| JP3349931B2 (ja) | 1997-10-30 | 2002-11-25 | 松下電器産業株式会社 | 半導体レーザ装置の製造方法 |

| JPH11163363A (ja) | 1997-11-22 | 1999-06-18 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP2000012864A (ja) | 1998-06-22 | 2000-01-14 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| JP2000082679A (ja) | 1998-07-08 | 2000-03-21 | Canon Inc | 半導体基板とその作製方法 |

| JP3345363B2 (ja) * | 1998-12-07 | 2002-11-18 | 富士通株式会社 | 多結晶シリコン薄膜の形成方法及び薄膜トランジスタの製造方法 |

| US7153729B1 (en) | 1998-07-15 | 2006-12-26 | Semiconductor Energy Laboratory Co., Ltd. | Crystalline semiconductor thin film, method of fabricating the same, semiconductor device, and method of fabricating the same |

| JP4476390B2 (ja) | 1998-09-04 | 2010-06-09 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP3794876B2 (ja) | 1998-09-09 | 2006-07-12 | 松下電器産業株式会社 | 半導体装置の製造方法 |

| JP4101409B2 (ja) | 1999-08-19 | 2008-06-18 | シャープ株式会社 | 半導体装置の製造方法 |

| US7052943B2 (en) | 2001-03-16 | 2006-05-30 | Semiconductor Energy Laboratory Co., Ltd. | Method of manufacturing a semiconductor device |

| US7253032B2 (en) | 2001-04-20 | 2007-08-07 | Semiconductor Energy Laboratory Co., Ltd. | Method of flattening a crystallized semiconductor film surface by using a plate |

| TW544938B (en) | 2001-06-01 | 2003-08-01 | Semiconductor Energy Lab | Method of manufacturing a semiconductor device |

| US7119365B2 (en) | 2002-03-26 | 2006-10-10 | Sharp Kabushiki Kaisha | Semiconductor device and manufacturing method thereof, SOI substrate and display device using the same, and manufacturing method of the SOI substrate |

| JP2004006700A (ja) | 2002-03-27 | 2004-01-08 | Seiko Epson Corp | 表面処理方法、表面処理基板、膜パターンの形成方法、電気光学装置の製造方法、電気光学装置、及び電子機器 |

| JP4610178B2 (ja) * | 2002-11-15 | 2011-01-12 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4759919B2 (ja) * | 2004-01-16 | 2011-08-31 | セイコーエプソン株式会社 | 電気光学装置の製造方法 |

| JP5110772B2 (ja) | 2004-02-03 | 2012-12-26 | 株式会社半導体エネルギー研究所 | 半導体薄膜層を有する基板の製造方法 |

| US20070117287A1 (en) | 2005-11-23 | 2007-05-24 | Semiconductor Energy Laboratory Co., Ltd. | Laser irradiation apparatus |

| US7579654B2 (en) | 2006-05-31 | 2009-08-25 | Corning Incorporated | Semiconductor on insulator structure made using radiation annealing |

| CN101281912B (zh) | 2007-04-03 | 2013-01-23 | 株式会社半导体能源研究所 | Soi衬底及其制造方法以及半导体装置 |

| KR101440930B1 (ko) * | 2007-04-20 | 2014-09-15 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | Soi 기판의 제작방법 |

| US7960262B2 (en) | 2007-05-18 | 2011-06-14 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device by applying laser beam to single-crystal semiconductor layer and non-single-crystal semiconductor layer through cap film |

| US7745268B2 (en) | 2007-06-01 | 2010-06-29 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a semiconductor device with irradiation of single crystal semiconductor layer in an inert atmosphere |

| US7776718B2 (en) | 2007-06-25 | 2010-08-17 | Semiconductor Energy Laboratory Co., Ltd. | Method of manufacturing semiconductor substrate with reduced gap size between single-crystalline layers |

| US7795111B2 (en) | 2007-06-27 | 2010-09-14 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of SOI substrate and manufacturing method of semiconductor device |

| JP5442224B2 (ja) | 2007-07-23 | 2014-03-12 | 株式会社半導体エネルギー研究所 | Soi基板の製造方法 |

| KR101499175B1 (ko) | 2007-10-04 | 2015-03-05 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 기판의 제조방법 |

| US7799658B2 (en) | 2007-10-10 | 2010-09-21 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor substrate and method for manufacturing semiconductor device |

| WO2009057669A1 (en) | 2007-11-01 | 2009-05-07 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing photoelectric conversion device |

| US7851318B2 (en) | 2007-11-01 | 2010-12-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor substrate and method for manufacturing the same, and method for manufacturing semiconductor device |

| US7816232B2 (en) * | 2007-11-27 | 2010-10-19 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor substrate and semiconductor substrate manufacturing apparatus |

| JP5248995B2 (ja) | 2007-11-30 | 2013-07-31 | 株式会社半導体エネルギー研究所 | 光電変換装置の製造方法 |

| JP5286046B2 (ja) | 2007-11-30 | 2013-09-11 | 株式会社半導体エネルギー研究所 | 光電変換装置の製造方法 |

| JP5248994B2 (ja) | 2007-11-30 | 2013-07-31 | 株式会社半導体エネルギー研究所 | 光電変換装置の製造方法 |

| US7947523B2 (en) | 2008-04-25 | 2011-05-24 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing photoelectric conversion device |

| JP5552276B2 (ja) | 2008-08-01 | 2014-07-16 | 株式会社半導体エネルギー研究所 | Soi基板の作製方法 |

-

2009

- 2009-12-07 SG SG2012044475A patent/SG182208A1/en unknown

- 2009-12-07 SG SG200908120-9A patent/SG162675A1/en unknown

- 2009-12-09 US US12/634,107 patent/US8394703B2/en active Active

- 2009-12-10 JP JP2009280207A patent/JP5610759B2/ja not_active Expired - Fee Related

- 2009-12-14 KR KR1020090123832A patent/KR20100069595A/ko active Application Filing

- 2009-12-15 CN CN200910262141.XA patent/CN101752294B/zh not_active Expired - Fee Related

-

2016

- 2016-10-05 KR KR1020160128549A patent/KR20160120266A/ko active Search and Examination

Also Published As

| Publication number | Publication date |

|---|---|

| US20100151663A1 (en) | 2010-06-17 |

| SG182208A1 (en) | 2012-07-30 |

| CN101752294B (zh) | 2015-02-25 |

| JP5610759B2 (ja) | 2014-10-22 |

| US8394703B2 (en) | 2013-03-12 |

| JP2010166035A (ja) | 2010-07-29 |

| KR20160120266A (ko) | 2016-10-17 |

| SG162675A1 (en) | 2010-07-29 |

| CN101752294A (zh) | 2010-06-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20100069595A (ko) | Soi 기판의 제작 방법, 반도체 장치의 제작 방법 | |

| CN101937861B (zh) | 半导体衬底的制造方法、以及半导体装置的制造方法 | |

| US8216929B2 (en) | Method of manufacturing silicon carbide semiconductor device | |

| JP5548351B2 (ja) | 半導体装置の作製方法 | |

| JP5706670B2 (ja) | Soi基板の作製方法 | |

| US8653536B2 (en) | Method for manufacturing semiconductor substrate, and semiconductor device | |

| JP5668414B2 (ja) | 半導体装置の製造方法 | |

| TWI445060B (zh) | 半導體基板之製造方法 | |

| CN105047601A (zh) | Soi衬底的制造方法及soi衬底 | |

| JP2008277696A (ja) | 半導体装置の製造方法 | |

| JP5941285B2 (ja) | Soi基板の作製方法 | |

| US8501549B2 (en) | Method of manufacturing a reverse blocking insulated gate bipolar transistor | |

| US9105558B2 (en) | Silicon carbide semiconductor device and manufacturing method of the same | |

| US8349702B2 (en) | Method for manufacturing semiconductor substrate | |

| GB2437995A (en) | Semiconductor processing | |

| JP7155759B2 (ja) | 半導体装置及び半導体装置の製造方法 | |

| CN101599464A (zh) | 半导体装置的制造方法 | |

| JP5977947B2 (ja) | Soi基板の作製方法 | |

| US6952269B2 (en) | Apparatus and method for adiabatically heating a semiconductor surface | |

| JP5633328B2 (ja) | 半導体装置の製造方法 | |

| JPWO2006013898A1 (ja) | 半導体装置の製造方法 | |

| CN108701648B (zh) | 用于在薄绝缘体上碳化硅(SiCOI)晶片上形成微带传输线的方法和结构 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| AMND | Amendment | ||

| E902 | Notification of reason for refusal | ||

| AMND | Amendment | ||

| E601 | Decision to refuse application | ||

| AMND | Amendment | ||

| A107 | Divisional application of patent | ||

| J201 | Request for trial against refusal decision | ||

| J301 | Trial decision |

Free format text: TRIAL NUMBER: 2016101005790; TRIAL DECISION FOR APPEAL AGAINST DECISION TO DECLINE REFUSAL REQUESTED 20161005 Effective date: 20180625 |