KR101871029B1 - 프린트 배선판용 구리박, 그 제조 방법, 프린트 배선판용 수지 기판 및 프린트 배선판 - Google Patents

프린트 배선판용 구리박, 그 제조 방법, 프린트 배선판용 수지 기판 및 프린트 배선판 Download PDFInfo

- Publication number

- KR101871029B1 KR101871029B1 KR1020147035862A KR20147035862A KR101871029B1 KR 101871029 B1 KR101871029 B1 KR 101871029B1 KR 1020147035862 A KR1020147035862 A KR 1020147035862A KR 20147035862 A KR20147035862 A KR 20147035862A KR 101871029 B1 KR101871029 B1 KR 101871029B1

- Authority

- KR

- South Korea

- Prior art keywords

- resin

- copper foil

- average diameter

- layer

- wiring board

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/02—Apparatus or processes for manufacturing printed circuits in which the conductive material is applied to the surface of the insulating support and is thereafter removed from such areas of the surface which are not intended for current conducting or shielding

- H05K3/022—Processes for manufacturing precursors of printed circuits, i.e. copper-clad substrates

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C18/00—Chemical coating by decomposition of either liquid compounds or solutions of the coating forming compounds, without leaving reaction products of surface material in the coating; Contact plating

- C23C18/16—Chemical coating by decomposition of either liquid compounds or solutions of the coating forming compounds, without leaving reaction products of surface material in the coating; Contact plating by reduction or substitution, e.g. electroless plating

- C23C18/1601—Process or apparatus

- C23C18/1633—Process of electroless plating

- C23C18/1646—Characteristics of the product obtained

- C23C18/165—Multilayered product

- C23C18/1651—Two or more layers only obtained by electroless plating

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C28/00—Coating for obtaining at least two superposed coatings either by methods not provided for in a single one of groups C23C2/00 - C23C26/00 or by combinations of methods provided for in subclasses C23C and C25C or C25D

- C23C28/02—Coating for obtaining at least two superposed coatings either by methods not provided for in a single one of groups C23C2/00 - C23C26/00 or by combinations of methods provided for in subclasses C23C and C25C or C25D only coatings only including layers of metallic material

- C23C28/023—Coating for obtaining at least two superposed coatings either by methods not provided for in a single one of groups C23C2/00 - C23C26/00 or by combinations of methods provided for in subclasses C23C and C25C or C25D only coatings only including layers of metallic material only coatings of metal elements only

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D1/00—Electroforming

- C25D1/04—Wires; Strips; Foils

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D11/00—Electrolytic coating by surface reaction, i.e. forming conversion layers

- C25D11/38—Chromatising

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D3/00—Electroplating: Baths therefor

- C25D3/02—Electroplating: Baths therefor from solutions

- C25D3/38—Electroplating: Baths therefor from solutions of copper

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D5/00—Electroplating characterised by the process; Pretreatment or after-treatment of workpieces

- C25D5/10—Electroplating with more than one layer of the same or of different metals

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D5/00—Electroplating characterised by the process; Pretreatment or after-treatment of workpieces

- C25D5/10—Electroplating with more than one layer of the same or of different metals

- C25D5/12—Electroplating with more than one layer of the same or of different metals at least one layer being of nickel or chromium

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D5/00—Electroplating characterised by the process; Pretreatment or after-treatment of workpieces

- C25D5/60—Electroplating characterised by the structure or texture of the layers

- C25D5/605—Surface topography of the layers, e.g. rough, dendritic or nodular layers

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D7/00—Electroplating characterised by the article coated

- C25D7/06—Wires; Strips; Foils

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D7/00—Electroplating characterised by the article coated

- C25D7/06—Wires; Strips; Foils

- C25D7/0614—Strips or foils

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/09—Use of materials for the conductive, e.g. metallic pattern

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/02—Apparatus or processes for manufacturing printed circuits in which the conductive material is applied to the surface of the insulating support and is thereafter removed from such areas of the surface which are not intended for current conducting or shielding

- H05K3/06—Apparatus or processes for manufacturing printed circuits in which the conductive material is applied to the surface of the insulating support and is thereafter removed from such areas of the surface which are not intended for current conducting or shielding the conductive material being removed chemically or electrolytically, e.g. by photo-etch process

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/38—Improvement of the adhesion between the insulating substrate and the metal

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/38—Improvement of the adhesion between the insulating substrate and the metal

- H05K3/382—Improvement of the adhesion between the insulating substrate and the metal by special treatment of the metal

- H05K3/383—Improvement of the adhesion between the insulating substrate and the metal by special treatment of the metal by microetching

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/38—Improvement of the adhesion between the insulating substrate and the metal

- H05K3/382—Improvement of the adhesion between the insulating substrate and the metal by special treatment of the metal

- H05K3/384—Improvement of the adhesion between the insulating substrate and the metal by special treatment of the metal by plating

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/03—Conductive materials

- H05K2201/0332—Structure of the conductor

- H05K2201/0335—Layered conductors or foils

- H05K2201/0355—Metal foils

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/03—Conductive materials

- H05K2201/0332—Structure of the conductor

- H05K2201/0335—Layered conductors or foils

- H05K2201/0358—Resin coated copper [RCC]

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/03—Metal processing

- H05K2203/0307—Providing micro- or nanometer scale roughness on a metal surface, e.g. by plating of nodules or dendrites

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/38—Improvement of the adhesion between the insulating substrate and the metal

- H05K3/388—Improvement of the adhesion between the insulating substrate and the metal by the use of a metallic or inorganic thin film adhesion layer

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S428/00—Stock material or miscellaneous articles

- Y10S428/922—Static electricity metal bleed-off metallic stock

- Y10S428/9335—Product by special process

- Y10S428/934—Electrical process

- Y10S428/935—Electroplating

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/12—All metal or with adjacent metals

- Y10T428/12014—All metal or with adjacent metals having metal particles

- Y10T428/12028—Composite; i.e., plural, adjacent, spatially distinct metal components [e.g., layers, etc.]

- Y10T428/12063—Nonparticulate metal component

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/12—All metal or with adjacent metals

- Y10T428/12431—Foil or filament smaller than 6 mils

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/12—All metal or with adjacent metals

- Y10T428/12431—Foil or filament smaller than 6 mils

- Y10T428/12438—Composite

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/12—All metal or with adjacent metals

- Y10T428/12472—Microscopic interfacial wave or roughness

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/12—All metal or with adjacent metals

- Y10T428/12493—Composite; i.e., plural, adjacent, spatially distinct metal components [e.g., layers, joint, etc.]

- Y10T428/12535—Composite; i.e., plural, adjacent, spatially distinct metal components [e.g., layers, joint, etc.] with additional, spatially distinct nonmetal component

- Y10T428/12542—More than one such component

- Y10T428/12549—Adjacent to each other

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/12—All metal or with adjacent metals

- Y10T428/12493—Composite; i.e., plural, adjacent, spatially distinct metal components [e.g., layers, joint, etc.]

- Y10T428/12771—Transition metal-base component

- Y10T428/12861—Group VIII or IB metal-base component

- Y10T428/12903—Cu-base component

- Y10T428/1291—Next to Co-, Cu-, or Ni-base component

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/12—All metal or with adjacent metals

- Y10T428/12993—Surface feature [e.g., rough, mirror]

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/24—Structurally defined web or sheet [e.g., overall dimension, etc.]

- Y10T428/24355—Continuous and nonuniform or irregular surface on layer or component [e.g., roofing, etc.]

Abstract

구리박의 적어도 일방의 면에, 입자 길이의 10 % 위치의 입자 근원의 평균 직경 (D1) 이 0.2 ㎛ ∼ 1.0 ㎛ 이고, 입자 길이 (L1) 와 상기 입자 근원의 평균 직경 (D1) 의 비 (L1/D1) 가 15 이하인 구리박의 조화 처리층을 가지는 것을 특징으로 하는 프린트 배선판용 구리박. 조화 처리층을 가지는 프린트 배선용 구리박과 수지를 적층한 후, 구리층을 에칭에 의해 제거한 수지의 표면에 있어서, 요철을 가지는 수지 조화면의 구멍이 차지하는 면적의 총합이 20 % 이상인 것을 특징으로 하는 프린트 배선판용 구리박. 구리박의 다른 여러 특성을 열화시키지 않고, 상기 회로 침식 현상을 회피하는 반도체 패키지 기판용 구리박을 개발하는 것이다. 특히, 구리박의 조화 처리층을 개선하여, 구리박과 수지의 접착 강도를 높일 수 있는 프린트 배선판용 구리박 및 그 제조 방법을 제공하는 것을 과제로 한다.

Description

본 발명은 내약품성 및 접착성이 우수한 프린트 배선판용 구리박, 그 제조 방법, 프린트 배선판용 수지 기판 및 프린트 배선판에 관한 것이다. 특히, BT (비스말레이미드·트리아진) 수지 함침 기재를 대표로 하는 패키지용 기판에 대해, 파인 패턴 형성시의 약품 처리에 대해, 강한 박리 강도를 얻을 수 있어, 파인 에칭을 가능하게 한 구리박 및 그 제조 방법 그리고 프린트 배선판을 제공한다. 또, 구리박을 전체 면 에칭 후, 무전해 도금으로 구리 패턴을 형성하는 방법에 있어서, 필 강도를 크게 향상시킬 수 있는 프린트 배선판용 구리박, 그 제조 방법, 프린트 배선판용 수지 기판 및 프린트 배선판을 제공한다.

반도체 패키지 기판용 구리박은, 일반적으로 프린트 배선판용 구리박이라고도 일컬어지고 있지만, 통상, 다음과 같은 공정에 의해 제작된다. 먼저, 합성 수지 등의 기재에 구리박을 고온 고압하에서 적층 접착한다. 다음으로, 기판 상에 목적으로 하는 도전성의 회로를 형성하기 위해, 구리박 상에 내에칭성 수지 등의 재료에 의해 회로와 동등한 회로를 인쇄한다.

그리고, 노출되어 있는 구리박의 불필요부를 에칭 처리에 의해 제거한다. 에칭 후, 수지 등의 재료로 이루어지는 인쇄부를 제거하고, 기판 상에 도전성의 회로를 형성한다. 형성된 도전성의 회로에는, 최종적으로 소정의 소자를 납땜하여, 일렉트로닉스 디바이스용의 여러 가지 인쇄 회로판을 형성한다.

최종적으로는, 레지스트 또는 빌드업 수지 기판과 접합한다. 일반적으로, 인쇄 배선판용 구리박에 대한 품질 요구는, 수지 기재와 접착되는 접착면 (소위, 조화면) 과 비접착면 (소위 광택면) 에서 상이하여, 양자를 동시에 만족시키는 것이 필요하다.

광택면에 대한 요구로서는, (1) 외관이 양호할 것 및 보존시의 산화 변색이 없을 것, (2) 땜납 젖음성이 양호할 것, (3) 고온 가열시에 산화 변색이 없을 것, (4) 레지스트와의 밀착성이 양호할 것 등이 요구된다.

한편, 조화면에 대해서는, 주로 (1) 보존시의 산화 변색이 없을 것, (2) 기재와의 박리 강도가, 고온 가열, 습식 처리, 납땜, 약품 처리 등의 후에도 충분할 것, (3) 기재와의 적층, 에칭 후에 발생하는, 소위 적층 오점이 없을 것 등을 들 수 있다.

또, 최근 패턴의 파인화에 수반하여, 구리박의 로우프로파일화가 요구되어 오고 있다. 그 만큼, 구리박 조화면의 박리 강도의 증가가 필요해졌다.

또한, PC 나 이동체 통신 등의 전자기기에서는, 통신의 고속화, 대용량화에 수반하여, 전기 신호의 고주파화가 진행되고 있으며, 이에 대응 가능한 프린트 배선판 및 구리박이 요구되고 있다. 전기 신호의 주파수가 1 ㎓ 이상이 되면, 전류가 도체의 표면에만 흐르는 표피 효과의 영향이 현저해져, 표면의 요철에서 전류 전송 경로가 변화되어 임피던스가 증대되는 영향을 무시할 수 없게 된다. 이 점에서도 구리박의 표면 조도가 작은 것이 바람직하다.

이러한 요구에 부응하기 위해, 인쇄 배선판용 구리박에 대해 많은 처리 방법이 제창되어 왔다.

일반적으로, 인쇄 배선판용 구리박의 처리 방법은, 압연 구리박 또는 전해 구리박을 이용하여, 먼저 구리박과 수지의 접착력 (필 강도) 을 높이기 위해, 일반적으로는 구리 및 산화구리로 이루어지는 미립자를 구리박 표면에 부여하는 조화 처리를 실시한다. 다음으로, 내열·방청 특성을 가지게 하기 위해 황동 또는 아연 등의 내열 처리층 (장벽층) 을 형성한다. 그리고, 이 위에 운반중 또는 보관중의 표면 산화 등을 방지하기 위해, 침지 또는 전해 크로메이트 처리 혹은 전해 크롬·아연 처리 등의 방청 처리를 실시함으로써 제품으로 한다.

이 중에서, 특히 조화 처리층은, 구리박과 수지의 접착력 (필 강도) 을 높이는 큰 역할을 담당하고 있다. 종래, 이 조화 처리는, 둥그스름한 (구상) 돌기물이 양호하다고 여겨져 왔다. 이 둥그스름한 돌기물은, 덴드라이트의 발달을 억제함으로써 달성되는 것이다. 그러나, 이 둥그스름한 돌기물은, 에칭시에 박리되어, 「가루 떨어짐」과 같은 현상이 발생하였다. 이 현상은 당연하다고 할 수 있다. 그것은 구상 돌기물과 구리박의 접촉 면적이 둥그스름한 (구상) 돌기물의 직경에 비해 매우 작기 때문이다.

이 「가루 떨어짐」현상을 피하기 위해, 상기 조화 처리 후에, 돌기물 상에 얇은 구리 도금층을 형성하여, 돌기물의 박리를 방지하는 것이 실시되었다 (특허문헌 1 참조). 이것은 「가루 떨어짐」을 방지하는 효과를 가지지만, 공정이 늘어난다는 것, 그 얇은 구리 도금에 의해 「가루 떨어짐」방지 효과가 상이하다는 문제가 있었다.

또, 구리박 상에, 구리와 니켈의 합금으로 이루어지는 침상의 노듈러 피복층을 형성한다는 기술이 알려져 있다 (특허문헌 2). 이 노듈러 피복층은, 침상으로 되어 있으므로, 상기 특허문헌 1 에 개시된 둥그스름한 (구상) 돌기물에 비해 수지와의 접착 강도는 증가될 것으로 생각되지만, 하지가 되는 구리박과는 성분이 상이한 구리-니켈 합금이며, 구리의 회로를 형성하는 에칭시에는 상이한 에칭 속도를 갖는다. 따라서, 안정된 회로 설계에는 적합하지 않다는 문제가 있다.

프린트 배선판용 구리박을 형성할 때에는, 일반적으로 내열·방청 처리층을 형성하는 것이 실시된다. 내열 처리층을 형성하는 금속 또는 합금의 예로서, Zn, Cu-Ni, Cu-Co 및 Cu-Zn 등의 피복층을 형성한 다수의 구리박이 실용화되어 있다 (예를 들어, 특허문헌 3 참조).

이들 중에서, Cu-Zn (황동) 으로 이루어지는 내열 처리층을 형성한 구리박은, 에폭시 수지 등으로 이루어지는 인쇄 회로판에 적층한 경우에 수지층의 얼룩이 없는 것, 또 고온 가열 후의 박리 강도의 열화가 적은 등의 우수한 특성을 가지고 있기 때문에, 공업적으로 널리 사용되고 있다.

이 황동으로 이루어지는 내열 처리층을 형성하는 방법에 대해서는, 특허문헌 4 및 특허문헌 5 에 상세히 서술되어 있다.

이러한 황동으로 이루어지는 내열 처리층을 형성한 구리박은, 이어서 인쇄 회로를 형성하기 위해 에칭 처리된다. 최근, 인쇄 회로의 형성에 염산계의 에칭액이 많이 사용되도록 되어 가고 있다.

그런데, 황동으로 이루어지는 내열 처리층을 형성한 구리박을 사용한 인쇄 회로판을 염산계의 에칭액 (예를 들어 CuCl2, FeCl3 등) 으로 에칭 처리하여, 인쇄 회로 부분을 제외한 구리박의 불필요 부분을 제거하고 도전성의 회로를 형성하면, 회로 패턴의 양측에 소위 회로 단부 (에지부) 의 침식 (회로 침식) 현상이 일어나, 수지 기재와의 박리 강도가 열화된다는 문제점이 발생하였다.

이 회로 침식 현상이란, 상기 에칭 처리에 의해 형성된 회로의 구리박과 수지 기재의 접착 경계층, 즉 황동으로 이루어지는 내열·방청 처리층이 노출된 에칭측면으로부터, 상기 에칭액에 의해 침식되고, 또 그 후의 수세 부족 때문에, 통상 황색 (황동으로 이루어지기 때문에) 을 띠는 양 사이드가 침식되어 적색을 띠고, 그 부분의 박리 강도가 현저하게 열화되는 현상을 말한다. 그리고, 이 현상이 회로 패턴 전체 면에 발생하면, 회로 패턴이 기재로부터 박리되게 되어 문제가 된다.

이와 같은 점에서, 구리박의 표면에 조화 처리, 아연 또는 아연 합금의 방청 처리 및 크로메이트 처리를 실시한 후, 크로메이트 처리 후의 표면에, 소량의 크롬 이온을 함유시킨 실란 커플링제를 흡착시켜 내염산성을 향상시키고자 하는 제안이 이루어지져 있다 (특허문헌 7 참조).

본 발명의 과제는, 구리박의 다른 여러 특성을 열화시키지 않고, 상기 회로 침식 현상을 회피하는 반도체 패키지 기판용 구리박을 개발하는 것이다. 특히, 구리박의 조화 처리와 공정을 개선하여, 구리박과 수지의 접착 강도를 높일 수 있는 프린트 배선판용 구리박, 그 제조 방법, 프린트 배선판용 수지 기판 및 프린트 배선판을 제공하는 것을 과제로 한다.

상기 과제를 해결하기 위해, 본 발명자가 예의 검토한 결과, 이하의 프린트 배선판용 구리박 및 그 제조 방법 그리고 프린트 배선판을 제공하는 것이다.

1) 구리박의 적어도 일방의 면에, 입자 길이의 10 % 위치의 입자 근원의 평균 직경 (D1) 이 0.2 ㎛ ∼ 1.0 ㎛ 이고, 입자 길이 (L1) 와 상기 입자 근원의 평균 직경 (D1) 의 비 (L1/D1) 가 15 이하인 구리박의 조화 처리층을 가지는 것을 특징으로 하는 프린트 배선판용 구리박.

2) 구리박의 적어도 일방의 면에, 입자 길이의 50 % 위치의 입자 중앙의 평균 직경 (D2) 과 상기 입자 근원의 평균 직경 (D1) 의 비 (D2/D1) 가 1 ∼ 4 인 것을 특징으로 하는 상기 1) 에 기재된 프린트 배선판용 구리박.

3) 상기 입자 중앙의 평균 직경 (D2) 과 입자 길이의 90 % 위치의 입자 선단 (D3) 의 비 (D2/D3) 가 0.8 ∼ 1.0 인 것을 특징으로 하는 상기 2) 에 기재된 프린트 배선판용 구리박.

4) 상기 입자 중앙 (D2) 의 평균 직경이 0.7 ∼ 1.5 ㎛ 인 것을 특징으로 하는 상기 2) 또는 3) 에 기재된 프린트 배선판용 구리박.

5) 상기 입자 선단의 평균 직경 (D3) 이 0.7 ∼ 1.5 ㎛ 인 것을 특징으로 하는 상기 3) 또는 4) 에 기재된 프린트 배선판용 구리박.

6) 상기 조화 처리층 상에, 아연, 니켈, 구리, 인에서 선택된 적어도 1 종류 이상의 원소를 함유하는 내열·방청층, 당해 내열·방청층 상에, 크로메이트 피막층 및 당해 크로메이트 피막층 상에, 실란 커플링제층을 구비하는 것을 특징으로 하는 청구항 1 ∼ 5 중 어느 한 항에 기재된 프린트 배선판용 구리박.

7) 황산알킬에스테르염, 텅스텐 이온, 비소 이온에서 선택된 물질 중 적어도 1 종류 이상을 함유하는 황산·황산구리로 이루어지는 전해욕을 사용하여, 상기 청구항 1 ∼ 6 의 어느 한 항에 기재된 조화 처리층을 형성하는 것을 특징으로 하는 프린트 배선판용 구리박의 제조 방법.

8) 상기 조화 처리층 상에 아연, 니켈, 구리, 인에서 선택된 적어도 1 종류 이상의 원소를 함유하는 내열·방청층을 형성하고, 다음으로 당해 내열·방청층 상에 크로메이트 피막층을 형성하고, 추가로 당해 크로메이트 피막층 상에 실란 커플링제층을 형성하는 것을 특징으로 하는 청구항 7 에 기재된 프린트 배선판용 구리박의 제조 방법.

9) 조화 처리층을 가지는 프린트 배선판용 구리박에 수지층을 적층한 후, 구리층을 에칭에 의해 제거한 수지의 표면에 있어서, 요철을 가지는 수지 조화면의 구멍이 차지하는 면적의 총합이 20 % 이상인 것을 특징으로 하는 프린트 배선판용 구리박.

10) 상기 1 ∼ 8 중 어느 하나의 조화 처리층을 가지는 프린트 배선판용 구리박에 수지층을 적층한 후, 구리층을 에칭에 의해 제거한 수지에 있어서, 구리박의 조화면이 전사된 요철을 가지는 수지면의 구멍이 차지하는 면적의 총합이 20 % 이상인 것을 특징으로 하는 프린트 배선판용 수지 기판.

11) 조화 처리층을 가지는 프린트 배선판용 구리박에 수지층을 적층한 후, 구리층을 에칭에 의해 제거한 수지 표면에, 무전해 구리 도금·전해 도금 순으로 도금을 실시하여 구리층을 형성하고, 추가로 에칭에 의해 회로를 형성한 프린트 배선판.

12) 상기 1 ∼ 8 중 어느 하나의 조화 처리층을 가지는 프린트 배선판용 구리박에 수지층을 적층한 후, 구리층을 에칭에 의해 제거한 수지 표면에, 무전해 구리 도금·전해 도금 순으로 도금을 실시하여 구리층을 형성하고, 추가로 에칭에 의해 회로를 형성한 프린트 배선판.

13) 침상 입자가, 회로 폭 10 ㎛ 중에 5 개 이상 존재하는 것을 특징으로 하는 청구항 11 또는 12 에 기재된 프린트 배선판.

이상에 나타낸 바와 같이, 본 발명의 프린트 배선판용 구리박은, 종래 양호하다고 여겨져 온 조화 처리의 둥그스름한 (구상) 돌기물이 아니라, 구리박의 적어도 일방의 면에, 침상 또는 봉상의 미세한 조화 입자를 형성하는 것이다.

이 구리박은, 수지와의 접착 강도를 높여, 패키지용 기판에 대해, 파인 패턴 형성시의 약품 처리에 대해서도, 박리 강도를 크게 하는 것이 가능해져, 파인 에칭을 가능하게 한 프린트 배선판을 제공할 수 있다는 우수한 효과를 갖는다. 또 이 구리박은, 구리층을 일단 에칭에 의해 전체 면 제거하고, 조화면이 수지층에 전사됨으로써, 그 후에 수지면에 형성되는 회로용 구리 도금층 (무전해 도금층) 과의 밀착력을 높이는 공법에도 유용하다.

최근 인쇄 회로의 파인 패턴화 및 고주파화가 진행되는 가운데 인쇄 회로용 구리박 (반도체 패키지 기판용 구리박) 및 반도체 패키지 기판용 구리박과 반도체 패키지용 수지를 접착하여 제작한 반도체 패키지용 기판으로서 매우 유효하다.

도 1 은 입자 치수의 개략 설명도이다.

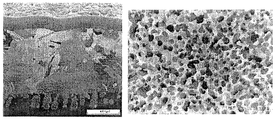

도 2 는 실시예 1 의 조화 처리층의 FIB-SIM 사진 (좌측) 및 구리층에 수지를 적층한 후, 구리층을 에칭에 의해 제거한 수지 (레플리카) 표면의 SEM 사진 (우측) 이다.

도 3 은 비교예 1 의 조화 처리층의 FIB-SIM 사진 및 구리층에 수지를 적층한 후, 구리층을 에칭에 의해 제거한 수지 (레플리카) 표면의 SEM 사진 (우측) 이다.

도 2 는 실시예 1 의 조화 처리층의 FIB-SIM 사진 (좌측) 및 구리층에 수지를 적층한 후, 구리층을 에칭에 의해 제거한 수지 (레플리카) 표면의 SEM 사진 (우측) 이다.

도 3 은 비교예 1 의 조화 처리층의 FIB-SIM 사진 및 구리층에 수지를 적층한 후, 구리층을 에칭에 의해 제거한 수지 (레플리카) 표면의 SEM 사진 (우측) 이다.

다음으로, 본 발명의 이해를 용이하게 하기 위해, 본 발명을 구체적이고 상세하게 설명한다. 본 발명에 있어서 사용하는 구리박은, 전해 구리박 혹은 압연 구리박 중 어느 것이어도 된다.

상기와 같이, 본 발명의 프린트 배선판용 구리박은, 종래 양호하다고 여겨져 온 조화 처리의 둥그스름한 (구상) 돌기물이 아니라, 구리박의 적어도 일방의 면에, 침상 또는 봉상의 미세한 구리의 조화 입자를 형성하는 것이다.

그 형상은, 입자 길이의 10 % 위치의 입자 근원의 평균 직경 (D1) 이 0.2 ㎛ ∼ 1.0 ㎛ 이고, 입자 길이 (L1) 와 상기 입자 근원의 평균 직경 (D1) 의 비 (L1/D1) 가 15 이하인 구리박의 조화 처리층을 가지는 것이다. 보다 바람직한 형상으로서는, 구리박의 적어도 일방의 면에, 입자 길이의 50 % 위치의 입자 중앙의 평균 직경 (D2) 과 상기 입자 근원의 평균 직경 (D1) 의 비 (D2/D1) 가 1 ∼ 4 인 것이다. 또한, 상기 입자 중앙의 평균 직경 (D2) 과 입자 길이의 90 % 위치의 입자 선단 (D3) 의 비 (D2/D3) 를 0.8 ∼ 1.0 으로 할 수 있다. 이 경우, 상기 입자 중앙 (D2) 의 평균 직경이 0.7 ∼ 1.5 ㎛ 인 것, 상기 입자 선단의 평균 직경 (D3) 이 0.7 ∼ 1.5 ㎛ 인 것이 바람직하다.

도 1 에, 입자 치수의 개략 설명도를 나타낸다. 도 1 에는, 입자 길이의 10 % 위치의 입자 근원의 평균 직경 (D1), 입자 길이의 50 % 위치의 입자 중앙의 평균 직경 (D2), 입자 길이의 90 % 위치의 입자 선단 (D3) 을 나타낸다. 이로써, 입자의 형상을 특정할 수 있다.

또, 상기 조화 처리층 상에, 아연, 니켈, 구리, 인에서 선택된 적어도 1 종류 이상의 원소를 함유하는 내열·방청층, 당해 내열·방청층 상에, 크로메이트 피막층 및 당해 크로메이트 피막층 상에, 실란 커플링제층을 형성할 수 있다.

이들 구리박의 조화 처리층은, 황산알킬에스테르염, 텅스텐 이온, 비소 이온에서 선택된 물질 중 적어도 1 종류 이상을 함유하는 황산·황산구리로 이루어지는 전해욕을 사용하여 형성할 수 있지만, 상기 형상이 되도록, 전해 처리 조건을 임의로 설정함으로써 달성할 수 있다. 또한, 상기 조화 처리층 상에 아연, 니켈, 구리, 인에서 선택된 적어도 1 종류 이상의 원소를 함유하는 내열·방청층을 형성하고, 다음으로 당해 내열·방청층 상에 크로메이트 피막층을 형성하고, 다시 당해 크로메이트 피막층 상에 실란 커플링제층을 형성할 수 있다.

상기 조화 처리층을 형성한 구리박과 수지는, 프레스법 혹은 라미네이트법과 같은 수단에 의해 적층체로 할 수 있다.

또한, 이와 같이 조화 처리층을 가지는 구리박에 수지를 적층하고, 에칭에 의해 구리층을 제거하면, 구리층이 제거된 수지에, 구리박의 조화면의 요철이 전사된다. 이 전사된 수지의 요철은 구리박 표면의 조화 입자의 형상과 개수 분포를 나타낸 것으로, 중요하다. 구리박의 조면의 입자의 근원이 가는 경우에는, 구멍의 직경이 작아, 수지면의 구멍이 차지하는 면적의 총합이 작아진다.

구리박의 조면의 입자의 근원이 가는, 이른바 역눈물방울형 입자는, 일견 구리박과 수지와 접착 강도가 증가하는 것처럼 보이지만, 구리층과 조화 입자의 밀착 폭이 좁기 때문에, 구리층과 수지층을 박리할 때, 조화 입자는 그 근원부터 절단되기 쉬워, 구리층과 조화 입자의 계면 혹은 조화 입자의 근원부터 절단된 부분에서 박리되어, 밀착력이 저하된다. 수지면의 구멍이 차지하는 면적의 총합이 20 % 이상인 것이 필요하다.

또, 구리박의 조면의 입자의 근원이 가는 경우에는, 에칭에 의해 구리층을 제거한 수지의 구멍이 항아리 형상이 되어, 표면의 구멍이 작기 때문에, 수지 표면에 무전해 도금을 형성하는 경우에도, 무전해 도금액이 들어가지 않아, 무전해 도금이 불완전해진다. 당연히, 도금의 박리 강도가 저하된다는 문제를 발생시킨다.

이와 같이, 구리박의 조화면은, 어느 정도의 직경과 길이가 필요하고, 이 구리박의 조면이 전사된 요철을 가지는 수지면의 구멍이 차지하는 면적의 총합이 중요해진다. 이것을 20 % 이상으로 함으로써, 회로의 필링 강도를 향상시킬 수 있다.

상기와 같이, 조화 처리층을 가지는 구리박에 수지층을 적층한 후, 구리층을 에칭에 의해 제거한 수지 표면에, 무전해 구리 도금·전해 구리 도금 순으로 도금을 실시하여 구리층을 형성하고, 다시 에칭에 의해 회로를 형성한 프린트 배선판을 얻을 수 있지만, 무전해 도금·전해 도금층 (구리층) 은, 수지 기판의 조면의 요철 상에 형성되고, 그 수지면의 요철을 반영하여 침상 입자 또는 봉상의 입자가 형성된다.

이 침상 입자 또는 봉상의 입자는, 회로 폭 10 ㎛ 중에 5 개 이상 존재하는 것이 바람직하고, 이로써, 수지와 무전해 도금에 의한 회로층과의 접착 강도를 크게 향상시킬 수 있다. 본 발명은 이와 같이 하여 형성된 프린트 배선판을 제공한다.

상기와 같이, 침상 또는 봉상의 미세한 구리의 조화 입자로 이루어지는 조화 처리층은, 황산알킬에스테르염, 텅스텐 이온, 비소 이온에서 선택된 물질 중 적어도 1 종류 이상을 함유하는 황산·황산구리로 이루어지는 전해욕을 사용하여 제조할 수 있다.

침상의 미세한 구리의 조화 입자로 이루어지는 조화 처리층은, 가루 떨어짐 방지, 필 강도 향상을 위해 황산·황산구리로 이루어지는 전해욕으로 피복 도금을 실시하는 것이 바람직하다.

구체적인 처리 조건은, 다음과 같다.

(액 조성 1)

CuSO4·5H2O : 39.3 ∼ 118 g/ℓ

Cu : 10 ∼ 30 g/ℓ

H2SO4 : 10 ∼ 150 g/ℓ

Na2WO4·2H2O : 0 ∼ 90 ㎎/ℓ

W : 0 ∼ 50 ㎎/ℓ

도데실황산나트륨 : 0 ∼ 50 ㎎

H3AsO3 (60 % 수용액) : 0 ∼ 6315 ㎎/ℓ

As : 0 ∼ 2000 ㎎/ℓ

(전기 도금 조건 1)

온도 : 30 ∼ 70 ℃

(전류 조건 1)

전류 밀도 : 25 ∼ 110 A/d㎡

조화 쿨롬량 : 50 ∼ 500 As/d㎡

도금 시간 : 0.5 ∼ 20 초

(액 조성 2)

CuSO4·5H2O : 78 ∼ 314 g/ℓ

Cu : 20 ∼ 80 g/ℓ

H2SO4 : 50 ∼ 200 g/ℓ

(전기 도금 조건 2)

온도 : 30 ∼ 70 ℃

(전류 조건 2)

전류 밀도 : 5 ∼ 50 A/d㎡

조화 쿨롬량 : 50 ∼ 300 As/d㎡

도금 시간 : 1 ∼ 60 초

또한, 상기 조화 처리층 상에, 또한 아연, 니켈, 구리, 인에서 선택된 적어도 1 종류 이상의 원소를 함유하는 내열·방청층, 당해 내열·방청층 상에, 크로메이트 피막층 및 당해 크로메이트 피막층 상에, 실란 커플링제층을 형성하여 프린트 배선판용 구리박으로 할 수 있다.

내열·방청층으로서는, 특별히 제한되지 않고, 종래의 내열·방청층을 사용하는 것이 가능하다. 예를 들어, 반도체 패키지 기판용 구리박에 대해, 종래 사용되어 온 황동 피복층을 사용할 수 있다.

또한, 이 내열·방청층에, 크로메이트 피막층 및 실란 커플링제층을 형성하여 구리박의 적어도 수지와의 접착면으로 한다. 이들 크로메이트 피막층과 실란 커플링제층으로 이루어지는 피복층을 가지는 구리박을 수지에 적층 접착하고, 다시 당해 구리박 상에, 내에칭성의 인쇄 회로를 형성한 후, 인쇄 회로 부분을 제외한 구리박의 불필요 부분을 에칭에 의해 제거하고, 도전성의 회로를 형성한다.

내열·방청층으로서는, 기존의 처리를 사용할 수 있지만, 구체적으로는 예를 들어, 다음의 것을 사용할 수 있다.

(액 조성)

NaOH : 40 ∼ 200 g/ℓ

NaCN : 70 ∼ 250 g/ℓ

CuCN : 50 ∼ 200 g/ℓ

Zn(CN)2 : 2 ∼ 100 g/ℓ

As2O3 : 0.01 ∼ 1 g/ℓ

(액온)

40 ∼ 90 ℃

(전류 조건)

전류 밀도 : 1 ∼ 50 A/d㎡

도금 시간 : 1 ∼ 20 초

상기 크로메이트 피막층은, 전해 크로메이트 피막층 또는 침지 크로메이트 피막층을 사용할 수 있다. 이 크로메이트 피막층은, Cr 량이 25-150 ㎍/d㎡ 인 것이 바람직하다.

Cr 량이 25 ㎍/d㎡ 미만에서는, 방청층 효과가 없다. 또, Cr 량이 150 ㎍/d㎡ 를 초과하면 효과가 포화되므로, 소용없어진다. 따라서, Cr 량은 25-150 ㎍/d㎡ 로 하는 것이 좋다.

상기 크로메이트 피막층을 형성하기 위한 조건의 예를 이하에 기재한다. 그러나, 상기와 같이, 이 조건에 한정될 필요는 없고, 이미 공지된 크로메이트 처리는 모두 사용할 수 있다. 이 방청 처리는, 내산성에 영향을 주는 인자의 하나로, 크로메이트 처리에 의해, 내산성은 보다 향상된다.

(a) 침지 크로메이트 처리

K2Cr2O7 : 1 ∼ 5 g/ℓ, pH : 2.5 ∼ 4.5, 온도 : 40 ∼ 60 ℃, 시간 : 0.5 ∼ 8 초

(b) 전해 크로메이트 처리 (크롬·아연 처리 (알칼리성욕))

K2Cr2O7 : 0.2 ∼ 20 g/ℓ, 산 : 인산, 황산, 유기산, pH : 1.0 ∼ 3.5, 온도 : 20 ∼ 40 ℃, 전류 밀도 : 0.1 ∼ 5 A/d㎡, 시간 : 0.5 ∼ 8 초

(c) 전해 크롬·아연 처리 (알칼리성욕)

K2Cr2O7(Na2Cr2O7 혹은 CrO3) : 2 ∼ 10 g/ℓ, NaOH 또는 KOH : 10 ∼ 50 g/ℓ, ZnOH 또는 ZnSO4·7H2O : 0.05 ∼ 10 g/ℓ, pH : 7 ∼ 13, 욕온 : 20 ∼ 80 ℃, 전류 밀도 : 0.05 ∼ 5 A/d㎡, 시간 : 5 ∼ 30 초

(d) 전해 크로메이트 처리 (크롬·아연 처리 (산성욕))

K2Cr2O7 : 2 ∼ 10 g/ℓ, Zn : 0 ∼ 0.5 g/ℓ, Na2SO4 : 5 ∼ 20 g/ℓ, pH : 3.5 ∼ 5.0, 욕온 : 20 ∼ 40 ℃, 전류 밀도 : 0.1 ∼ 3.0 A/d㎡, 시간 : 1 ∼ 30 초

본 발명의 반도체 패키지 기판용 구리박에 사용하는 실란 커플링제층으로서는, 통상 구리박에 사용되고 있는 실란 커플링제를 사용할 수 있고, 특별히 제한은 없다. 예를 들어, 실란 처리의 구체적인 조건을 나타내면, 다음과 같다.

0.2 % 에폭시실란/0.4 %TEOS, PH 5

테트라알콕시실란과, 수지와의 반응성을 가지는 관능기를 구비한 알콕시실란을 1 종 이상 함유하고 있는 것을 사용할 수도 있다. 이 실란 커플링제층의 선택도 임의이지만, 수지와의 접착성을 고려한 선택이 바람직하다고 할 수 있다. 실시예

다음으로, 실시예 및 비교예에 대하여 설명한다. 또한, 본 실시예는 바람직한 일례를 나타내는 것으로, 본 발명은 이들 실시예에 한정되는 것은 아니다. 따라서, 본 발명의 기술 사상에 포함되는 변형, 다른 실시예 또는 양태는, 모두 본 발명에 포함된다.

또한, 본 발명과의 대비를 위해, 비교예를 게재하였다.

(실시예 1)

두께 12 ㎛ 의 전해 구리박 (구리층 조화 형성면 조도 : Rz 0.6 ㎛) 을 사용하여, 이 구리박의 조면 (매트면 : M 면) 에, 하기에 나타내는 조화 도금을 실시하였다. 이하에, 처리 조건을 나타낸다. 이들은 모두 본원 발명의 구리박에 조화 처리층을 형성하기 위한 공정이다. 조화 입자 형성시의 대 (對) 한계 전류 밀도비는 2.50 으로 하였다.

(액 조성 1)

CuSO4·5H2O : 58.9 g/ℓ

Cu : 15 g/ℓ

H2SO4 : 100 g/ℓ

Na2WO4·2H2O : 5.4 ㎎/ℓ

W : 3 ㎎/ℓ

도데실황산나트륨 첨가량 : 10 ppm

(전기 도금 온도 1) 50 ℃

본 조화 처리 후, 하기에 나타내는 정상 도금을 실시하였다. 이하에, 처리 조건을 나타낸다.

(액 조성 2)

CuSO4·5H2O : 156 g/ℓ

Cu : 40 g/ℓ

H2SO4 : 100 g/ℓ

(전기 도금 온도 1) 40 ℃

(전류 조건 1)

전류 밀도 : 30 A/d㎡

조화 쿨롬량 : 150 As/d㎡

다음으로, 내열·방청층 상에 전해 크로메이트 처리를 실시하였다.

전해 크로메이트 처리 (크롬·아연 처리 (산성욕))

CrO3 : 1.5 g/ℓ

ZnSO4·7H2O : 2.0 g/ℓ

Na2SO4 : 18 g/ℓ

pH : 4.6, 욕온 : 37 ℃

전류 밀도 : 2.0 A/d㎡

시간 : 1 ∼ 30 초

(PH 조정은 황산 또는 수산화칼륨으로 실시)

다음으로, 이 크로메이트 피막층 상에, 실란 처리 (도포에 의한) 를 실시하였다.

실란 처리 조건은, 다음과 같다.

0.2 % 에폭시실란

실시예 1 의 조화 처리층의 FIB-SIM 사진을 도 2 의 좌측에 나타낸다. 이 조화 처리층의 표면 조도 (Rz) 가 1.17 ㎛ 이고, 입자 길이의 10 % 위치의 입자 근원의 평균 직경 (D1) 이 0.57 ㎛, 입자 길이 (L1) 가 2.68 이며, 상기 입자 근원의 평균 직경 (D1) 과의 비 (L1/D1) 가 4.74 가 되어, 상기 도 2 로부터, 침상 또는 봉상의 입자 형상으로 형성되어 있는 것을 알 수 있다. 또한, 조화 입자의 직경의 측정은, JIS H 0501 항목 7 절단법에 기초한다.

본원 발명의 입자 길이의 10 % 위치의 입자 근원의 평균 직경 (D1) 이 0.2 ㎛ ∼ 1.0 ㎛ 이고, 입자 길이 (L1) 와 상기 입자 근원의 평균 직경 (D1) 의 비 (L1/D1) 가 15 이하인 구리박의 조화 처리층이라는 본원 발명의 조건을 만족하였다. 이 조건은, 본원 발명을 달성하는 데에 있어서 필수 요건이다. 이 결과를 표 1 에 나타낸다.

또한, 표 1 에는, 조화 입자의 근원의 평균 직경 (폭) (D1) : 0.57 이외에, 중앙의 평균 직경 (D2) : 0.83, 선단의 평균 직경 (D3) : 0.68, 또한 중앙의 평균 직경과 근원의 평균 직경의 비 : D2/D1=1.47, 선단의 평균 직경과 근원의 평균 직경의 비 : D3/D1=1.21, 선단의 평균 직경과 중앙의 평균 직경의 비 : D3/D2=0.83 을 나타내지만, 모두 본원 발명의 바람직한 요건에 적합한 것이었다.

그러나, 이들은 본원 발명의 제일의적 요건, 즉 필수 요건으로 하는 것이 아닌 것은 용이하게 이해되어야 하는 것이다. 어디까지나 더욱 바람직한 조건을 나타내는 것이다.

다음으로, 이 구리박을 사용하고, 수지에 MBT-830 을 사용하여, 구리박에 수지를 적층하였다. 수지를 적층한 구리층을 에칭에 의해 제거한 수지 (레플리카) 표면의 SEM 사진을 도 2 의 우측에 나타낸다.

구리박의 조화면이 전사된 요철을 가지는 수지면의 구멍이 차지하는 면적의 총합이 51 %, 구멍의 밀도는 2.10 개/μ㎡ 로, 본원 발명의 구멍이 차지하는 면적의 총합이 20 % 이상인 조건을 만족하는 것을 알 수 있다.

상기와 같이 구리박에 수지 (MBT-830) 를 적층한 것을, 적층체의 상태 (常態) 필 강도와 가열 후의 필 강도로서 측정하여, 그 결과를 동일하게 표 1 에 나타낸다. 필 강도의 회로 폭은, 10 ㎜ 이다. 상태 필 강도는 1.01 ㎏/㎝, 가열 후의 필 강도는 0.94 ㎏/㎝ 로, 모두 후술하는 비교예에 비해, 필 강도가 향상되어 있었다.

(실시예 2)

두께 12 ㎛ 의 전해 구리박을 사용하여, 이 구리박의 조면 (매트면 : M 면) 에, 하기에 나타내는 조화 도금과 실시예 1 과 동일한 정상 도금을 실시하였다. 이하에, 조화 도금 처리 조건을 나타낸다. 이들은 모두 본원 발명의 구리박에 조화 처리층을 형성하기 위한 공정이다. 조화 입자 형성시의 대한계 전류 밀도비는 3.10 으로 하였다.

(액 조성 1)

CuSO4·5H2O : 58.9 g/ℓ

Cu : 15 g/ℓ

H2SO4 : 100 g/ℓ

Na2WO4·2H2O : 5.4 ㎎/ℓ

W : 3 ㎎/ℓ

도데실황산나트륨 첨가량 : 10 ppm

(전기 도금 온도 1) 50 ℃

이 조화 처리층의 표면 조도 (Rz) 가 1.51 ㎛ 이고, 입자 길이의 10 % 위치의 입자 근원의 평균 직경 (D1) 이 0.51 ㎛, 입자 길이 (L1) 가 2.68 ㎛ 이며, 상기 입자 근원의 평균 직경 (D1) 과의 비 (L1/D1) 가 5.21 이 되어, 상기 도 2 로부터 추정하여, 침상 또는 봉상의 입자 형상으로 형성되어 있는 것을 알 수 있다. 또한, 조화 입자의 직경의 측정은, JIS H 0501 항목 7 절단법에 기초한다.

본원 발명의 입자 길이의 10 % 위치의 입자 근원의 평균 직경 (D1) 이 0.2 ㎛ ∼ 1.0 ㎛ 이고, 입자 길이 (L1) 와 상기 입자 근원의 평균 직경 (D1) 의 비 (L1/D1) 가 15 이하인 구리박의 조화 처리층이라는 본원 발명의 조건을 만족하였다. 이 조건은, 본원 발명을 달성하는 데에 있어서 필수 요건이다. 이 결과를 표 1 에 나타낸다.

또한, 표 1 에는, 조화 입자의 근원의 평균 직경 (폭) (D1) : 0.51 ㎛ 이외에, 중앙의 평균 직경 (D2) : 0.78 ㎛, 선단의 평균 직경 (D3) : 0.68 ㎛, 또한 중앙의 평균 직경과 근원의 평균 직경의 비 : D2/D1=1.51, 선단의 평균 직경과 근원의 평균 직경의 비 : D3/D1=1.32, 선단의 평균 직경과 중앙의 평균 직경의 비 : D3/D2=0.87 을 나타내지만, 모두 본원 발명의 바람직한 요건에 적합한 것이었다.

그러나, 이들은 본원 발명의 제일의적 요건, 즉 필수 요건으로 하는 것이 아닌 것은 용이하게 이해되어야 하는 것이다. 어디까지나 더욱 바람직한 조건을 나타내는 것이다.

다음으로, 이 구리박을 사용하고, 수지에 MBT-830 을 사용하여, 구리박에 수지를 적층한 후, 에칭에 의해 구리층을 제거하였다. 구리박의 조화면이 전사된 요철을 가지는 수지면의 구멍이 차지하는 면적의 총합이 29 %, 구멍의 밀도는 1.93 개/μ㎡ 로, 본원 발명의 구멍이 차지하는 면적의 총합이 20 % 이상인 조건을 만족하는 것을 알 수 있다.

상기와 같이 구리박에 수지 (MBT-830) 를 적층한 것을, 적층체의 상태 필 강도와 가열 후의 필 강도로서 측정하여, 그 결과를 동일하게 표 1 에 나타낸다. 필 강도의 회로 폭은, 10 ㎜ 이다. 상태 필 강도는 0.81 ㎏/㎝, 가열 후의 필 강도는 0.78 ㎏/㎝ 로, 모두 후술하는 비교예에 비해, 필 강도가 향상되어 있었다.

(실시예 3)

두께 12 ㎛ 의 전해 구리박을 사용하여, 이 구리박의 조면 (매트면 : M 면) 에, 하기에 나타내는 조화 도금과 실시예 1 과 동일한 정상 도금을 실시하였다. 이하에, 조화 도금 처리 조건을 나타낸다. 이들은 모두 본원 발명의 구리박에 조화 처리층을 형성하기 위한 공정이다. 조화 입자 형성시의 대한계 전류 밀도비는 4.30 으로 하였다.

(액 조성 1)

CuSO4·5H2O : 58.9 g/ℓ

Cu : 15 g/ℓ

H2SO4 : 100 g/ℓ

Na2WO4·2H2O : 5.4 ㎎/ℓ

W : 3 ㎎/ℓ

도데실황산나트륨 첨가량 : 10 ppm

(전기 도금 온도 1) 50 ℃

이 조화 처리층의 표면 조도 (Rz) 가 1.56 ㎛ 이고, 입자 길이의 10 % 위치의 입자 근원의 평균 직경 (D1) 이 0.59 ㎛, 입자 길이 (L1) 가 2.68 ㎛ 이며, 상기 입자 근원의 평균 직경 (D1) 과의 비 (L1/D1) 가 4.52 가 되어, 상기 도 2 로부터 추정하여, 침상 또는 봉상의 입자 형상으로 형성되어 있는 것을 알 수 있다. 또한, 조화 입자의 직경의 측정은, JIS H 0501 항목 7 절단법에 기초한다.

본원 발명의 입자 길이의 10 % 위치의 입자 근원의 평균 직경 (D1) 이 0.2 ㎛ ∼ 1.0 ㎛ 이고, 입자 길이 (L1) 와 상기 입자 근원의 평균 직경 (D1) 의 비 (L1/D1) 가 15 이하인 구리박의 조화 처리층이라는 본원 발명의 조건을 만족하였다. 이 조건은, 본원 발명을 달성하는 데에 있어서 필수 요건이다. 이 결과를 표 1 에 나타낸다.

또한, 표 1 에는, 조화 입자의 근원의 평균 직경 (폭) (D1) : 0.51 ㎛ 이외에, 중앙의 평균 직경 (D2) : 0.73 ㎛, 선단의 평균 직경 (D3) : 0.65 ㎛, 더욱 중앙의 평균 직경과 근원의 평균 직경의 비 : D2/D1=1.23, 선단의 평균 직경과 근원의 평균 직경의 비 : D3/D1=1.10, 선단의 평균 직경과 중앙의 평균 직경의 비 : D3/D2=0.89 를 나타내지만, 모두 본원 발명의 바람직한 요건에 적합한 것이었다.

그러나, 이들은 본원 발명의 제일의적 요건, 즉 필수 요건으로 하는 것이 아닌 것은 용이하게 이해되어야 하는 것이다. 어디까지나 더욱 바람직한 조건을 나타내는 것이다.

다음으로, 이 구리박을 사용하고, 수지에 MBT-830 을 사용하여, 구리박에 수지를 적층한 후, 에칭에 의해 구리층을 제거하였다.

구리박의 조화면이 전사된 요철을 가지는 수지면의 구멍이 차지하는 면적의 총합이 43 %, 구멍의 밀도는 1.77 개/μ㎡ 로, 본원 발명의 구멍이 차지하는 면적의 총합이 20 % 이상인 조건을 만족하는 것을 알 수 있다.

상기와 같이 구리박에 수지 (MBT-830) 를 적층한 것을, 적층체의 상태 필 강도와 가열 후의 필 강도로서 측정하여, 그 결과를 동일하게 표 1 에 나타낸다. 필 강도의 회로 폭은, 10 ㎜ 이다. 상태 필 강도는 0.84 ㎏/㎝, 가열 후의 필 강도는 0.77 ㎏/㎝ 로, 모두 후술하는 비교예에 비해, 필 강도가 향상되어 있었다.

(실시예 4)

두께 12 ㎛ 의 전해 구리박을 사용하여, 이 구리박의 조면 (매트면 : M 면) 에, 하기에 나타내는 조화 도금과 실시예 1 과 동일한 정상 도금을 실시하였다. 이하에, 조화 도금 처리 조건을 나타낸다. 이들은 모두 본원 발명의 구리박 에 조화 처리층을 형성하기 위한 공정이다. 조화 입자 형성시의 대한계 전류 밀도비는 3.50 으로 하였다.

(액 조성 1)

CuSO4·5H2O : 58.9 g/ℓ

Cu : 15 g/ℓ

H2SO4 : 100 g/ℓ

Na2WO4·2H2O : 5.4 ㎎/ℓ

W : 3 ㎎/ℓ

도데실황산나트륨 첨가량 : 10 ppm

(전기 도금 온도 1) 50 ℃

이 조화 처리층의 표면 조도 (Rz) 가 1.62 ㎛ 이고, 입자 길이의 10 % 위치의 입자 근원의 평균 직경 (D1) 이 0.89 ㎛, 입자 길이 (L1) 가 2.98 ㎛ 이며, 상기 입자 근원의 평균 직경 (D1) 과의 비 (L1/D1) 가 3.33 이 되어, 상기 도 2 로부터 추정하여, 침상 또는 봉상의 입자 형상으로 형성되어 있는 것을 알 수 있다. 또한, 조화 입자의 직경의 측정은, JIS H 0501 항목 7 절단법에 기초한다.

본원 발명의 입자 길이의 10 % 위치의 입자 근원의 평균 직경 (D1) 이 0.2 ㎛ ∼ 1.0 ㎛ 이고, 입자 길이 (L1) 와 상기 입자 근원의 평균 직경 (D1) 의 비 (L1/D1) 가 15 이하인 구리박의 조화 처리층이라는 본원 발명의 조건을 만족하였다. 이 조건은, 본원 발명을 달성하는 데에 있어서 필수 요건이다. 이 결과를 표 1 에 나타낸다.

또한, 표 1 에는, 조화 입자의 근원의 평균 직경 (폭) (D1) : 0.89 ㎛ 이외에, 중앙의 평균 직경 (D2) : 1.65 ㎛, 선단의 평균 직경 (D3) : 0.98 ㎛, 또한 중앙의 평균 직경과 근원의 평균 직경의 비 : D2/D1=1.18, 선단의 평균 직경과 근원의 평균 직경의 비 : D3/D1=1.10, 선단의 평균 직경과 중앙의 평균 직경의 비 : D3/D2=0.93 을 나타내지만, 모두 본원 발명의 바람직한 요건에 적합한 것이었다.

그러나, 이들은 본원 발명의 제일의적 요건, 즉 필수 요건으로 하는 것이 아닌 것은 용이하게 이해되어야 하는 것이다. 어디까지나 더욱 바람직한 조건을 나타낸 것이다.

다음으로, 이 구리박을 사용하고, 수지에 MBT-830 을 사용하여, 구리박에 수지를 적층한 후, 에칭에 의해 구리층을 제거하였다.

구리박의 조화면이 전사된 요철을 가지는 수지면의 구멍이 차지하는 면적의 총합이 78 %, 구멍의 밀도는 2.02 개/μ㎡ 로, 본원 발명의 구멍이 차지하는 면적의 총합이 20 % 이상인 조건을 만족하는 것을 알 수 있다.

상기와 같이 구리박에 수지 (MBT-830) 를 적층한 것을, 적층체의 상태 필 강도와 가열 후의 필 강도로서 측정하여, 그 결과를 동일하게 표 1 에 나타낸다. 필 강도의 회로 폭은, 10 ㎜ 이다. 상태 필 강도는 0.90 ㎏/㎝, 가열 후의 필 강도는 0.86 ㎏/㎝ 로, 모두 후술하는 비교예에 비해, 필 강도가 향상되어 있었다.

(실시예 5)

두께 12 ㎛ 의 전해 구리박을 사용하여, 이 구리박의 조면 (매트면 : M 면) 에, 하기에 나타내는 조화 도금과 실시예 1 과 동일한 정상 도금을 실시하였다. 이하에, 조화 도금 처리 조건을 나타낸다. 이들은 모두 본원 발명의 구리박에 조화 처리층을 형성하기 위한 공정이다. 조화 입자 형성시의 대한계 전류 밀도비는 4.80 으로 하였다.

(액 조성 1)

CuSO4·5H2O : 58.9 g/ℓ

Cu : 15 g/ℓ

H2SO4 : 100 g/ℓ

Na2WO4·2H2O : 5.4 ㎎/ℓ

W : 3 ㎎/ℓ

도데실황산나트륨 첨가량 : 10 ppm

(전기 도금 온도 1) 50 ℃

이 조화 처리층의 표면 조도 (Rz) 가 1.01 ㎛ 이고, 입자 길이의 10 % 위치의 입자 근원의 평균 직경 (D1) 이 0.26 ㎛, 입자 길이 (L1) 가 2.68 ㎛ 이며, 상기 입자 근원의 평균 직경 (D1) 과의 비 (L1/D1) 가 10.34 가 되어, 상기 도 2 로부터 추정하여, 침상 또는 봉상의 입자 형상으로 형성되어 있는 것을 알 수 있다. 또한, 조화 입자의 직경의 측정은, JIS H 0501 항목 7 절단법에 기초한다.

본원 발명의 입자 길이의 10 % 위치의 입자 근원의 평균 직경 (D1) 이 0.2 ㎛ ∼ 1.0 ㎛ 이고, 입자 길이 (L1) 와 상기 입자 근원의 평균 직경 (D1) 의 비 (L1/D1) 가 15 이하인 구리박의 조화 처리층이라는 본원 발명의 조건을 만족하였다. 이 조건은, 본원 발명을 달성하는 데에 있어서 필수 요건이다. 이 결과를 표 1 에 나타낸다.

또한, 표 1 에는, 조화 입자의 근원의 평균 직경 (폭) (D1) : 0.26 ㎛ 이외에, 중앙의 평균 직경 (D2) : 0.84 ㎛, 선단의 평균 직경 (D3) : 0.79 ㎛, 또한 중앙의 평균 직경과 근원의 평균 직경의 비 : D2/D1=3.23, 선단의 평균 직경과 근원의 평균 직경의 비 : D3/D1=3.06, 선단의 평균 직경과 중앙의 평균 직경의 비 : D3/D2=0.95 를 나타내지만, 모두 본원 발명의 바람직한 요건에 적합한 것이었다.

그러나, 이들은 본원 발명의 제일의적 요건, 즉 필수 요건으로 하는 것이 아닌 것은 용이하게 이해되어야 하는 것이다. 어디까지나 더욱 바람직한 조건을 나타낸 것이다.

다음으로, 이 구리박을 사용하고, 수지에 MBT-830 을 사용하여, 구리박에 수지를 적층하였다. 구리박의 조화면이 전사된 요철을 가지는 수지면의 구멍이 차지하는 면적의 총합이 40 %, 구멍의 밀도는 2.65 개/μ㎡ 로, 본원 발명의 구멍이 차지하는 면적의 총합이 20 % 이상인 조건을 만족하는 것을 알 수 있다.

상기와 같이 구리박에 수지 (MBT-830) 를 적층한 것을, 적층체의 상태 필 강도와 가열 후의 필 강도로서 측정하여, 그 결과를 동일하게 표 1 에 나타낸다. 필 강도의 회로 폭은, 10 ㎜ 이다. 상태 필 강도는 0.91 ㎏/㎝, 가열 후의 필 강도는 0.84 ㎏/㎝ 로, 모두 후술하는 비교예에 비해, 필 강도가 향상되어 있었다.

(실시예 6)

두께 12 ㎛ 의 전해 구리박을 사용하여, 이 구리박의 조면 (매트면 : M 면) 에, 하기에 나타내는 조화 도금과 실시예 1 과 동일한 정상 도금을 실시하였다. 이하에, 조화 도금 처리 조건을 나타낸다. 이들은 모두 본원 발명의 구리박에 조화 처리층을 형성하기 위한 공정이다. 조화 입자 형성시의 대한계 전류 밀도비는 3.20 으로 하였다.

(액 조성 1)

CuSO4·5H2O : 58.9 g/ℓ

Cu : 15 g/ℓ

H2SO4 : 100 g/ℓ

Na2WO4·2H2O : 5.4 ㎎/ℓ

W : 3 ㎎/ℓ

도데실황산나트륨 첨가량 : 10 ppm

(전기 도금 온도 1) 50 ℃

이 조화 처리층의 표면 조도 (Rz) 가 1.48 ㎛ 이고, 입자 길이의 10 % 위치의 입자 근원의 평균 직경 (D1) 이 0.60 ㎛, 입자 길이 (L1) 가 2.68 ㎛ 이며, 상기 입자 근원의 평균 직경 (D1) 과의 비 (L1/D1) 가 4.44 가 되어, 상기 도 2 로부터 추정하여, 침상 또는 봉상의 입자 형상으로 형성되어 있는 것을 알 수 있다. 또한, 조화 입자의 직경의 측정은, JIS H 0501 항목 7 절단법에 기초한다.

본원 발명의 입자 길이의 10 % 위치의 입자 근원의 평균 직경 (D1) 이 0.2 ㎛ ∼ 1.0 ㎛ 이고, 입자 길이 (L1) 와 상기 입자 근원의 평균 직경 (D1) 의 비 (L1/D1) 가 15 이하인 구리박의 조화 처리층이라는 본원 발명의 조건을 만족하였다. 이 조건은, 본원 발명을 달성하는 데에 있어서 필수 요건이다. 이 결과를 표 1 에 나타낸다.

또한, 표 1 에는, 조화 입자의 근원의 평균 직경 (폭) (D1) : 0.60 ㎛ 이외에, 중앙의 평균 직경 (D2) : 0.84 ㎛, 선단의 평균 직경 (D3) : 0.78 ㎛, 또한 중앙의 평균 직경과 근원의 평균 직경의 비 : D2/D1=1.39, 선단의 평균 직경과 근원의 평균 직경의 비 : D3/D1=1.30, 선단의 평균 직경과 중앙의 평균 직경의 비 : D3/D2=0.94 를 나타내지만, 모두 본원 발명의 바람직한 요건에 적합한 것이었다.

그러나, 이들은 본원 발명의 제일의적 요건, 즉 필수 요건으로 하는 것이 아닌 것은 용이하게 이해되어야 하는 것이다. 어디까지나 더욱 바람직한 조건을 나타낸 것이다.

다음으로, 이 구리박을 사용하고, 수지에 MBT-830 을 사용하여, 구리박과 수지의 적층체를 형성한 후, 에칭에 의해 구리층을 제거하였다.

구리박의 조화면이 전사된 요철을 가지는 수지 조화면의 구멍이 차지하는 면적의 총합이 93 %, 구멍의 밀도는 2.22 개/μ㎡ 로, 본원 발명의 구멍이 차지하는 면적의 총합이 20 % 이상인 조건을 만족하는 것을 알 수 있다.

상기와 같이 구리박에 수지 (MBT-830) 를 적층한 것을, 적층체의 상태 필 강도와 가열 후의 필 강도로서 측정하여, 그 결과를 동일하게 표 1 에 나타낸다. 필 강도의 회로 폭은, 10 ㎜ 이다. 상태 필 강도는 0.91 ㎏/㎝, 가열 후의 필 강도는 0.91 ㎏/㎝ 로, 모두 후술하는 비교예에 비해, 필 강도가 향상되어 있었다.

(비교예 1)

두께 12 ㎛ 의 전해 구리박을 사용하여, 이 구리박의 조면 (매트면 : M 면) 에, 하기에 나타내는 조화 도금과 실시예 1 과 동일한 정상 도금을 실시하였다. 이하에, 조화 도금 처리 조건을 나타낸다. 조화 입자 형성시의 대한계 전류 밀도비는 10.50 으로 하였다.

(액 조성 1)

CuSO4·5H2O : 58.9 g/ℓ

Cu : 15 g/ℓ

H2SO4 : 100 g/ℓ

Na2WO4·2H2O : 5.4 ㎎/ℓ

W : 3 ㎎/ℓ

도데실황산나트륨 첨가량 : 10 ppm

(전기 도금 온도 1) 50 ℃

비교예 1 의 조화 처리층의 SEM 사진을 도 3 의 좌측에 나타낸다. 이 조화 처리층의 표면 조도 (Rz) 가 1.13 ㎛ 이고, 입자 길이의 10 % 위치의 입자 근원의 평균 직경 (D1) 이 0.12 ㎛ 로 근원 폭이 작고, 입자 길이 (L1) 가 3.87 이고, 상기 입자 근원의 평균 직경 (D1) 과의 비 (L1/D1) 가 30.97 이 되어, 상기 도 3 으로부터, 본원 발명에 적합하지 않은 침상 또는 덴드라이트상의 입자 형상으로 형성되어 있는 것을 알 수 있다. 또한, 조화 입자의 직경의 측정은, JIS H 0501 항목 7 절단법에 기초한다.

상기와 같이, 본원 발명의 입자 길이의 10 % 위치의 입자 근원의 평균 직경 (D1) 이 0.2 ㎛ ∼ 1.0 ㎛ 이고, 입자 길이 (L1) 와 상기 입자 근원의 평균 직경 (D1) 의 비 (L1/D1) 가 15 이하인 구리박의 조화 처리층이라는, 본원 발명의 조건을 만족하지 않았다. 이 결과를 표 1 에 나타낸다.

또한, 표 1 에는, 조화 입자의 근원의 평균 직경 (폭) (D1) : 0.12 ㎛ 이외에, 중앙의 평균 직경 (D2) : 0.74 ㎛, 선단의 평균 직경 (D3) : 0.74 ㎛, 또한 중앙의 평균 직경과 근원의 평균 직경의 비 : D2/D1=5.93, 선단의 평균 직경과 근원의 평균 직경의 비 : D3/D1=5.93, 선단의 평균 직경과 중앙의 평균 직경의 비 : D3/D2=1.00 을 나타내지만, 모두 본원 발명의 바람직한 요건에 적합하지 않았다.

다음으로, 이 구리박을 사용하고, 수지에 MBT-830 을 사용하여, 구리박에 수지를 적층한 후, 에칭에 의해 구리층을 제거하였다.

구리박의 조화면이 전사된 요철을 가지는 수지면의 구멍이 차지하는 면적의 총합이 2 %, 구멍의 밀도는 1.06 개/μ㎡ 로, 본원 발명의 구멍이 차지하는 면적의 총합이 20 % 이상인 조건을 만족하지 않는 것을 알 수 있다.

상기와 같이 구리박에 수지 (MBT-830) 를 적층한 것을, 적층체의 상태 필 강도와 가열 후의 필 강도로서 측정하여, 그 결과를 동일하게 표 1 에 나타낸다. 필 강도의 회로 폭은, 10 ㎜ 이다. 상태 필 강도는 0.54 ㎏/㎝, 가열 후의 필 강도는 0.53 ㎏/㎝ 로, 모두 전술한 실시예에 비해, 필 강도가 크게 뒤떨어져 있었다. 상기와 같이 근원이 가는 조화 입자를 가지는 구리박을 사용한 경우에는, 구리박과 수지를 박리할 때, 구리층과 조화 입자 계면에서 박리가 일어나기 때문에, 필 강도의 향상은 기대할 수 없는 것이었다.

(비교예 2)

두께 12 ㎛ 의 전해 구리박을 사용하여, 이 구리박의 조면 (매트면 : M 면) 에, 하기에 나타내는 조화 도금과 실시예 1 과 동일한 정상 도금을 실시하였다. 이하에, 조화 도금 처리 조건을 나타낸다. 조화 입자 형성시의 대한계 전류 밀도비는 9.50 으로 하였다.

(액 조성 1)

CuSO4·5H2O : 58.9 g/ℓ

Cu : 15 g/ℓ

H2SO4 : 100 g/ℓ

Na2WO4·2H2O : 5.4 ㎎/ℓ

W : 3 ㎎/ℓ

도데실황산나트륨 첨가량 : 10 ppm

(전기 도금 온도 1) 50 ℃

비교예 2 의 조화 처리층의 표면 조도 (Rz) 가 1.02 ㎛ 이고, 입자 길이의 10 % 위치의 입자 근원의 평균 직경 (D1) 이 0.15 ㎛ 로 근원 폭이 작고, 입자 길이 (L1) 가 2.83 이고, 상기 입자 근원의 평균 직경 (D1) 과의 비 (L1/D1) 가 18.54 가 되어, 상기 도 3 으로부터 추정하여, 본원 발명에 적합하지 않은 침상 또는 덴드라이트상의 입자 형상으로 형성되어 있는 것을 알 수 있다. 또한, 조화 입자의 직경의 측정은, JIS H 0501 항목 7 절단법에 기초한다.

상기와 같이, 본원 발명의 입자 길이의 10 % 위치의 입자 근원의 평균 직경 (D1) 이 0.2 ㎛ ∼ 1.0 ㎛ 이고, 입자 길이 (L1) 와 상기 입자 근원의 평균 직경 (D1) 의 비 (L1/D1) 가 15 이하인 구리박의 조화 처리층이라는, 본원 발명의 조건을 만족하지 않았다. 이 결과를 표 1 에 나타낸다.

또한, 표 1 에는, 조화 입자의 근원의 평균 직경 (폭) (D1) : 0.15 ㎛ 이외에, 중앙의 평균 직경 (D2) : 0.65 ㎛, 선단의 평균 직경 (D3) : 0.65 ㎛, 또한 중앙의 평균 직경과 근원의 평균 직경의 비 : D2/D1=4.25, 선단의 평균 직경과 근원의 평균 직경의 비 : D3/D1=4.25, 선단의 평균 직경과 중앙의 평균 직경의 비 : D3/D2=1.00 을 나타내지만, 모두 본원 발명의 바람직한 요건에 적합하지 않았다.

다음으로, 이 구리박을 사용하고, 수지에 MBT-830 을 사용하여, 구리박에 수지를 적층한 후, 에칭에 의해 구리층을 제거하였다.

구리박의 조화면이 전사된 요철을 가지는 수지면의 구멍이 차지하는 면적의 총합이 4 %, 구멍의 밀도는 2.11 개/μ㎡ 로, 본원 발명의 구멍이 차지하는 면적의 총합이 20 % 이상인 조건을 만족하지 않는 것을 알 수 있다.

상기와 같이 구리박에 수지 (MBT-830) 를 적층한 것을, 적층체의 상태 필 강도와 가열 후의 필 강도로서 측정하여, 그 결과를 동일하게 표 1 에 나타낸다. 필 강도의 회로 폭은, 10 ㎜ 이다. 상태 필 강도는 0.54 ㎏/㎝, 가열 후의 필 강도는 0.53 ㎏/㎝ 로, 모두 전술한 실시예에 비해, 필 강도가 크게 뒤떨어져 있었다.

상기와 같이 근원이 가는 조화 입자를 가지는 구리박을 사용한 경우에는, 구리박과 수지를 박리할 때, 구리층과 조화 입자 계면에서 박리가 일어나기 때문에, 필 강도의 향상은 기대할 수 없는 것이었다.

(비교예 3)

두께 12 ㎛ 의 전해 구리박을 사용하여, 이 구리박의 조면 (매트면 : M 면) 에, 하기에 나타내는 조화 도금과 실시예 1 과 동일한 정상 도금을 실시하였다. 이하에, 조화 도금 처리 조건을 나타낸다. 조화 입자 형성시의 대한계 전류 밀도비는 9.80 으로 하였다.

(액 조성 1)

CuSO4·5H2O : 58.9 g/ℓ

Cu : 15 g/ℓ

H2SO4 : 100 g/ℓ

Na2WO4·2H2O : 5.4 ㎎/ℓ

W : 3 ㎎/ℓ

도데실황산나트륨 첨가량 : 10 ppm

(전기 도금 온도 1) 50 ℃

비교예 3 의 조화 처리층의 표면 조도 (Rz) 가 0.88 ㎛ 이고, 입자 길이의 10 % 위치의 입자 근원의 평균 직경 (D1) 이 0.14 ㎛ 로 근원 폭이 작고, 입자 길이 (L1) 가 2.98 이고, 상기 입자 근원의 평균 직경 (D1) 과의 비 (L1/D1) 가 20.64 가 되어, 상기 도 3 으로부터 추정하여, 본원 발명에 적합하지 않은 침상 또는 덴드라이트상의 입자 형상으로 형성되어 있는 것을 알 수 있다. 또한, 조화 입자의 직경의 측정은, JIS H 0501 항목 7 절단법에 기초한다.

상기와 같이, 본원 발명의 입자 길이의 10 % 위치의 입자 근원의 평균 직경 (D1) 이 0.2 ㎛ ∼ 1.0 ㎛ 이고, 입자 길이 (L1) 와 상기 입자 근원의 평균 직경 (D1) 의 비 (L1/D1) 가 15 이하인 구리박의 조화 처리층이라는, 본원 발명의 조건을 만족하지 않았다. 이 결과를 표 1 에 나타낸다.

또한, 표 1 에는, 조화 입자의 근원의 평균 직경 (폭) (D1) : 0.14 ㎛ 이외에, 중앙의 평균 직경 (D2) : 0.65 ㎛, 선단의 평균 직경 (D3) : 0.65 ㎛, 또한 중앙의 평균 직경과 근원의 평균 직경의 비 : D2/D1=4.50, 선단의 평균 직경과 근원의 평균 직경의 비 : D3/D1=4.50, 선단의 평균 직경과 중앙의 평균 직경의 비 : D3/D2=1.00 을 나타내지만, 모두 본원 발명의 바람직한 요건에 적합하지 않았다.

다음으로, 이 구리박을 사용하고, 수지에 MBT-830 을 사용하여, 구리박과 수지의 적층체를 형성한 후, 에칭에 의해 구리층을 제거하였다.

구리박의 조화면이 전사된 요철을 가지는 수지 조화면의 구멍이 차지하는 면적의 총합이 14 %, 구멍의 밀도는 3.12 개/μ㎡ 로, 본원 발명의 구멍이 차지하는 면적의 총합이 20 % 이상인 조건을 만족하지 않는 것을 알 수 있다.

상기와 같이 구리박에 수지 (MBT-830) 를 적층한 것을, 적층체의 상태 필 강도와 가열 후의 필 강도로서 측정하여, 그 결과를 동일하게 표 1 에 나타낸다. 필 강도의 회로 폭은, 10 ㎜ 이다. 상태 필 강도는 0.54 ㎏/㎝, 가열 후의 필 강도는 0.53 ㎏/㎝ 로, 모두 전술한 실시예에 비해, 필 강도가 크게 뒤떨어져 있었다. 상기와 같이 근원이 가는 조화 입자를 가지는 구리박을 사용한 경우에는, 구리박과 수지를 박리할 때, 구리층과 조화 입자 계면에서 박리가 일어나기 때문에, 필 강도의 향상은 기대할 수 없는 것이었다.

이상으로부터, 본원 발명의 프린트 배선판용 구리박은, 종래 양호하다고 여겨져 온 조화 처리의 둥그스름한 (구상) 돌기물 또는 덴드라이트상의 결정립 직경이 아니라, 구리박의 적어도 일방의 면에, 침상의 미세한 조화 입자를 형성함으로써, 구리박 자체의 수지와의 접착 강도를 높여, 패키지용 기판에 대해, 파인 패턴 형성시의 약품 처리에 대해서도, 박리 강도를 크게 하는 것이 가능해져, 파인 에칭을 가능하게 한 구리박 및 그 제조 방법을 제공할 수 있다는 큰 효과를 가지는 것을 알 수 있다.

산업상 이용가능성

이상에 나타낸 바와 같이, 본 발명은 구리박의 적어도 일방의 면에, 침상의 미세한 조화 입자를 형성함으로써, 구리박 자체의 수지와의 접착 강도를 높여, 패키지용 기판에 대해, 파인 패턴 형성시의 약품 처리에 대해서도, 박리 강도를 크게 하는 것이 가능해져, 파인 에칭을 가능하게 한 구리박 및 그 제조 방법을 제공할 수 있다는 큰 효과를 갖는다.

최근 인쇄 회로의 파인 패턴화 및 고주파화가 진행되는 가운데 인쇄 회로용 구리박 (반도체 패키지 기판용 구리박) 및 반도체 패키지 기판용 구리박과 반도체 패키지용 수지를 접착하여 제작한 반도체 패키지용 기판으로서 매우 유효하다.

Claims (23)

- 조화 처리층을 가지는 구리박으로서, 상기 구리박에 수지층을 적층한 후, 상기 구리박을 에칭에 의해 제거한 후에, 상기 수지층의 표면을 관찰한 경우에, 요철을 가지는 수지 조화면의 구멍이 차지하는 면적의 총합이, 수지 표면 전체의 면적에 대해 20 % 이상이 되는 상기 조화 처리층을 갖고,

이하의 (A) ~ (C) 중 어느 1 개, 2 개, 또는 3 개를 만족하는 것을 특징으로하는 상기 구리박.:

(A) 상기 조화 처리층에 있어서, 조화 입자의 일단으로부터 상기 조화 입자 길이의 50 % 의 위치의 상기 조화 입자 중앙의 평균 직경 (D2) 과 상기 조화 입자의 일단으로부터 상기 조화 입자 길이의 10 % 의 위치의 상기 조화 입자 근원의 평균 직경 (D1) 의 비 (D2/D1) 가 1 ∼ 4 인 것

(B) 상기 조화 처리층에 있어서, 상기 조화 입자의 일단으로부터 상기 조화 입자 길이의 50 % 의 위치의 상기 조화 입자 중앙의 평균 직경 (D2) 과 상기 조화 입자의 일단으로부터 상기 조화 입자 길이의 90 % 의 위치의 상기 조화 입자 선단의 평균 직경 (D3) 의 비 (D3/D2) 가 0.8 ∼ 1.0 인 것

(C) 상기 조화 처리층에 있어서, 상기 조화 입자의 일단으로부터 상기 조화 입자 길이의 10 % 의 위치의 상기 조화 입자 근원의 평균 직경 (D1) 이 0.2 ㎛ ∼ 1.0 ㎛ 인 것 - 제 1 항에 기재된 구리박에 수지층을 적층한 후, 상기 구리박을 에칭에 의해 제거한 수지의 표면에, 무전해 구리 도금·전해 도금 순으로 도금을 실시하는 것에 의해 구리층을 형성하고, 추가로 에칭에 의해 회로를 형성한 프린트 배선판.

- 제 2 항에 있어서,

상기 수지 조화면에 형성되는 조화 입자가, 회로 폭 10 ㎛ 중에 5 개 이상 존재하는 것을 특징으로 하는 프린트 배선판. - 제 1 항에 있어서,

상기 조화 처리층에 있어서, 상기 조화 입자의 일단으로부터 상기 조화 입자 길이의 50 % 의 위치의 상기 조화 입자 중앙의 평균 직경 (D2) 과 상기 조화 입자의 일단으로부터 상기 조화 입자 길이의 10 % 의 위치의 상기 조화 입자 근원의 평균 직경 (D1) 의 비 (D2/D1) 가 1 ∼ 1.51 인 구리박. - 제 1 항에 있어서,

상기 조화 처리층에 있어서, 평균 입자 길이 (L1) 와 상기 조화 입자의 일단으로부터 상기 조화 입자 길이의 10 % 의 위치의 상기 조화 입자 근원의 평균 직경 (D1) 의 비 (L1/D1) 가 3.33 ∼ 15 인 구리박. - 삭제

- 제 1 항 또는 제 4 항에 있어서,

상기 조화 처리층에 있어서, 평균 입자 길이 (L1) 와 상기 조화 입자의 일단으로부터 상기 조화 입자 길이의 10 % 의 위치의 상기 조화 입자 근원의 평균 직경 (D1) 의 비 (L1/D1) 가 15 이하인 구리박. - 삭제

- 삭제

- 제 1 항, 제 4 항 및 제 5 항 중 어느 한 항에 있어서,

이하의 (A) 및 (B) 의 어느 일방 또는 양방을 만족하는 것을 특징으로 하는 구리박.

(A) 상기 조화 입자의 일단으로부터 상기 조화 입자 길이의 50 % 의 위치의 상기 조화 입자 중앙의 평균 직경 (D2) 이 0.7 ∼ 1.5 ㎛ 이다.

(B) 상기 조화 입자의 일단으로부터 상기 조화 입자 길이의 90 % 의 위치의 상기 조화 입자 선단의 평균 직경 (D3) 이 0.7 ∼ 1.5 ㎛ 이다. - 프린트 배선판용 수지로서,

상기 수지는, 요철을 가지는 수지 조화면을 갖고,

상기 요철은, 구리박 표면 상의 요철이 전사됨으로써 형성되고,

상기 구리박은, 조화 처리층을 갖고,

상기 전사는, 상기 구리박의 조화 처리층 측에 수지를 적층함으로써 실시되고,

상기 구리박은, 적층 후, 에칭에 의해 제거되고,

상기 제거 후의 수지 표면을 관찰했을 때에, 상기 수지 조화면의 구멍이 차지하는 면적의 총합이, 관찰 시야 전체의 면적에 대해 20 % 이상이고,

상기 구리박이, 이하의 (A) ~ (C) 중 어느 1 개, 2 개, 또는 3 개를 만족하는 것을 특징으로 하는 프린트 배선판용 수지.:

(A) 상기 조화 처리층에 있어서, 조화 입자의 일단으로부터 상기 조화 입자 길이의 50 % 의 위치의 상기 조화 입자 중앙의 평균 직경 (D2) 과 상기 조화 입자의 일단으로부터 상기 조화 입자 길이의 10 % 의 위치의 상기 조화 입자 근원의 평균 직경 (D1) 의 비 (D2/D1) 가 1 ∼ 4 인 것

(B) 상기 조화 처리층에 있어서, 상기 조화 입자의 일단으로부터 상기 조화 입자 길이의 50 % 의 위치의 상기 조화 입자 중앙의 평균 직경 (D2) 과 상기 조화 입자의 일단으로부터 상기 조화 입자 길이의 90 % 의 위치의 상기 조화 입자 선단의 평균 직경 (D3) 의 비 (D3/D2) 가 0.8 ∼ 1.0 인 것

(C) 상기 조화 처리층에 있어서, 상기 조화 입자의 일단으로부터 상기 조화 입자 길이의 10 % 의 위치의 상기 조화 입자 근원의 평균 직경 (D1) 이 0.2 ㎛ ∼ 1.0 ㎛ 인 것 - 제 11 항에 있어서,

상기 수지 조화면은, 당해 조화면 상에 회로를 형성함으로써 프린트 배선판을 형성하기 위한 조화면인 것을 특징으로 하는 프린트 배선판용 수지. - 제 11 항에 있어서,

상기 수지가 BT (비스말레이미드·트리아진) 수지 또는 BT (비스말레이미드·트리아진) 수지 함침 기재인 것을 특징으로 하는 프린트 배선판용 수지. - 제 12 항에 있어서,

상기 수지가 BT (비스말레이미드·트리아진) 수지 또는 BT (비스말레이미드·트리아진) 수지 함침 기재인 것을 특징으로 하는 프린트 배선판용 수지. - 제 11 항 내지 제 14 항 중 어느 한 항에 기재된 수지를 사용하여 제조한 프린트 배선판.

- 제 11 항 내지 제 14 항 중 어느 한 항에 기재된 수지를 사용하여 제조한 반도체 패키지 기판.

- 제 11 항 내지 제 14 항 중 어느 한 항에 기재된 수지의 수지 조화면에, 무전해 구리 도금·전해 도금 순으로 도금을 실시하여, 구리층을 형성하고, 추가로 에칭에 의해 회로를 형성함으로써 얻어진 프린트 배선판.

- 제 11 항 내지 제 14 항 중 어느 한 항에 기재된 수지의 수지 조화면에, 회로를 형성함으로써 얻어진 프린트 배선판.

- 제 11 항 내지 제 14 항 중 어느 한 항에 기재된 수지의 수지 조화면에, 구리층을 형성하고, 회로를 형성함으로써 얻어진 프린트 배선판.

- 제 11 항 내지 제 14 항 중 어느 한 항에 기재된 수지의 수지 조화면에, 무전해 구리 도금·전해 도금 순으로 도금을 실시하여, 구리층을 형성하고, 추가로 에칭에 의해 회로를 형성하는 프린트 배선판의 제조 방법.

- 제 11 항 내지 제 14 항 중 어느 한 항에 기재된 수지의 수지 조화면에, 회로를 형성하는 프린트 배선판의 제조 방법.

- 제 11 항 내지 제 14 항 중 어느 한 항에 기재된 수지의 수지 조화면에, 구리층을 형성하고, 회로를 형성하는 프린트 배선판의 제조 방법.

- 제 1 항, 제 4 항 및 제 5 항 중 어느 한 항에 기재된 구리박을 사용하여 프린트 배선판을 제조하는, 프린트 배선판의 제조 방법.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JPJP-P-2010-214724 | 2010-09-27 | ||

| JP2010214724 | 2010-09-27 | ||

| PCT/JP2011/070448 WO2012043182A1 (ja) | 2010-09-27 | 2011-09-08 | プリント配線板用銅箔、その製造方法、プリント配線板用樹脂基板及びプリント配線板 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020137008539A Division KR101740092B1 (ko) | 2010-09-27 | 2011-09-08 | 프린트 배선판용 구리박, 그 제조 방법, 프린트 배선판용 수지 기판 및 프린트 배선판 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20150003413A KR20150003413A (ko) | 2015-01-08 |

| KR101871029B1 true KR101871029B1 (ko) | 2018-06-25 |

Family

ID=45892655

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020137008539A KR101740092B1 (ko) | 2010-09-27 | 2011-09-08 | 프린트 배선판용 구리박, 그 제조 방법, 프린트 배선판용 수지 기판 및 프린트 배선판 |

| KR1020147035862A KR101871029B1 (ko) | 2010-09-27 | 2011-09-08 | 프린트 배선판용 구리박, 그 제조 방법, 프린트 배선판용 수지 기판 및 프린트 배선판 |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020137008539A KR101740092B1 (ko) | 2010-09-27 | 2011-09-08 | 프린트 배선판용 구리박, 그 제조 방법, 프린트 배선판용 수지 기판 및 프린트 배선판 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US9028972B2 (ko) |

| EP (1) | EP2624671A4 (ko) |

| JP (3) | JP5781525B2 (ko) |

| KR (2) | KR101740092B1 (ko) |

| CN (2) | CN106028638B (ko) |

| MY (1) | MY161680A (ko) |

| TW (1) | TWI525222B (ko) |

| WO (1) | WO2012043182A1 (ko) |

Families Citing this family (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102884228B (zh) | 2010-05-07 | 2015-11-25 | 吉坤日矿日石金属株式会社 | 印刷电路用铜箔 |

| WO2012043182A1 (ja) * | 2010-09-27 | 2012-04-05 | Jx日鉱日石金属株式会社 | プリント配線板用銅箔、その製造方法、プリント配線板用樹脂基板及びプリント配線板 |

| US9049795B2 (en) | 2011-03-25 | 2015-06-02 | Jx Nippon Mining & Metals Corporation | Rolled copper or copper-alloy foil provided with roughened surface |

| JP5204908B1 (ja) | 2012-03-26 | 2013-06-05 | Jx日鉱日石金属株式会社 | キャリア付銅箔、キャリア付銅箔の製造方法、プリント配線板用キャリア付銅箔及びプリント配線板 |

| JP6166614B2 (ja) * | 2013-07-23 | 2017-07-19 | Jx金属株式会社 | 表面処理銅箔、キャリア付銅箔、基材、プリント配線板、プリント回路板、銅張積層板及びプリント配線板の製造方法 |

| CN105408525B (zh) | 2013-07-23 | 2019-03-08 | Jx日矿日石金属株式会社 | 表面处理铜箔、附载体铜箔、基材、树脂基材、印刷配线板、覆铜积层板及印刷配线板的制造方法 |

| JP6593979B2 (ja) * | 2013-07-24 | 2019-10-23 | Jx金属株式会社 | 表面処理銅箔、キャリア付銅箔、基材、銅張積層板の製造方法、電子機器の製造方法及びプリント配線板の製造方法 |

| EP3026144A4 (en) * | 2013-07-24 | 2017-04-12 | JX Nippon Mining & Metals Corp. | Surface-treated copper foil, copper foil with carrier, substrate, resin substrate, printed circuit board, copper-clad laminate, and method for manufacturing printed circuit board |

| KR102504286B1 (ko) * | 2015-06-26 | 2023-02-24 | 에스케이넥실리스 주식회사 | 표면 처리 동박 및 그 제조방법 |

| JP6782561B2 (ja) * | 2015-07-16 | 2020-11-11 | Jx金属株式会社 | キャリア付銅箔、積層体、積層体の製造方法、プリント配線板の製造方法及び電子機器の製造方法 |

| JP6200042B2 (ja) | 2015-08-06 | 2017-09-20 | Jx金属株式会社 | キャリア付銅箔、積層体、プリント配線板の製造方法及び電子機器の製造方法 |

| WO2017026490A1 (ja) * | 2015-08-12 | 2017-02-16 | 古河電気工業株式会社 | 高周波回路用銅箔、銅張積層板、プリント配線基板 |

| JP6182584B2 (ja) * | 2015-12-09 | 2017-08-16 | 古河電気工業株式会社 | プリント配線板用表面処理銅箔、プリント配線板用銅張積層板及びプリント配線板 |

| WO2017149810A1 (ja) * | 2016-02-29 | 2017-09-08 | 三井金属鉱業株式会社 | キャリア付銅箔及びその製造方法、並びに配線層付コアレス支持体及びプリント配線板の製造方法 |

| KR102338103B1 (ko) * | 2016-04-14 | 2021-12-10 | 미쓰이금속광업주식회사 | 표면 처리 동박, 캐리어를 구비하는 동박, 그리고 그것들을 사용한 동장 적층판 및 프린트 배선판의 제조 방법 |

| TWI619852B (zh) * | 2017-02-24 | 2018-04-01 | 南亞塑膠工業股份有限公司 | 具近似橄欖球狀銅瘤的電解銅箔與線路板組件的製造方法 |

| TWI619851B (zh) * | 2017-02-24 | 2018-04-01 | 南亞塑膠工業股份有限公司 | 具近似絨毛狀銅瘤的電解銅箔與線路板組件的製造方法 |

| WO2018193935A1 (ja) * | 2017-04-17 | 2018-10-25 | 住友金属鉱山株式会社 | 導電性基板、導電性基板の製造方法 |

| WO2019021895A1 (ja) * | 2017-07-24 | 2019-01-31 | 古河電気工業株式会社 | 表面処理銅箔、並びにこれを用いた銅張積層板およびプリント配線板 |

| JP6623320B2 (ja) * | 2017-12-05 | 2019-12-18 | 古河電気工業株式会社 | 表面処理銅箔、並びにこれを用いた銅張積層板及びプリント配線板 |

| TWI646227B (zh) * | 2017-12-08 | 2019-01-01 | 南亞塑膠工業股份有限公司 | 應用於信號傳輸的銅箔以及線路板組件的製造方法 |

| JP6606317B1 (ja) * | 2018-04-25 | 2019-11-13 | 古河電気工業株式会社 | 表面処理銅箔、銅張積層板、及びプリント配線板 |

| JP6816193B2 (ja) * | 2019-03-26 | 2021-01-20 | 古河電気工業株式会社 | 表面処理銅箔、並びにこれを用いた銅張積層板及びプリント配線板 |

| US10697082B1 (en) * | 2019-08-12 | 2020-06-30 | Chang Chun Petrochemical Co., Ltd. | Surface-treated copper foil |

| CN111188070A (zh) * | 2020-01-22 | 2020-05-22 | 惠州中京电子科技有限公司 | 一种ic封装板电镀镍银金的制作方法 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002069691A (ja) | 2000-08-31 | 2002-03-08 | Nippon Denkai Kk | 印刷回路基板用銅箔の製造方法 |

| JP2005217052A (ja) * | 2004-01-28 | 2005-08-11 | Kyocera Corp | 配線基板及びその製造方法 |

| JP2005248323A (ja) * | 2004-02-06 | 2005-09-15 | Furukawa Circuit Foil Kk | 表面処理銅箔 |

| WO2007145164A1 (ja) | 2006-06-12 | 2007-12-21 | Nippon Mining & Metals Co., Ltd. | 粗化処理面を備えた圧延銅又は銅合金箔及び圧延銅又は銅合金箔の粗化方法 |

| JP2009215604A (ja) | 2008-03-10 | 2009-09-24 | Hitachi Cable Ltd | 銅箔とその製造方法 |

| WO2009145207A1 (ja) | 2008-05-28 | 2009-12-03 | 三井金属鉱業株式会社 | 銅箔の粗化処理方法及びその粗化処理方法で得られるプリント配線板用銅箔 |

| WO2010093009A1 (ja) | 2009-02-13 | 2010-08-19 | 古河電気工業株式会社 | 金属箔およびその製造方法,絶縁基板,配線基板 |

Family Cites Families (51)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3585010A (en) | 1968-10-03 | 1971-06-15 | Clevite Corp | Printed circuit board and method of making same |

| JPS546701B1 (ko) | 1972-03-21 | 1979-03-30 | ||

| JPS62198192A (ja) * | 1986-02-26 | 1987-09-01 | 住友ベークライト株式会社 | プリント配線板の製造方法 |

| JP2739507B2 (ja) | 1989-10-06 | 1998-04-15 | 日鉱グールド・フォイル株式会社 | 銅箔の電解処理方法 |

| JPH0654830B2 (ja) * | 1990-08-14 | 1994-07-20 | 株式会社ジャパンエナジー | 印刷回路用銅箔の処理方法 |

| JP2826206B2 (ja) * | 1991-06-20 | 1998-11-18 | イビデン株式会社 | プリント配線板 |

| JP2717911B2 (ja) * | 1992-11-19 | 1998-02-25 | 日鉱グールド・フォイル株式会社 | 印刷回路用銅箔及びその製造方法 |

| JPH06310835A (ja) | 1993-04-23 | 1994-11-04 | Hitachi Chem Co Ltd | 銅表面への無電解金めっき方法 |

| JP3476264B2 (ja) * | 1993-12-24 | 2003-12-10 | 三井金属鉱業株式会社 | プリント回路内層用銅箔およびその製造方法 |

| TW317575B (ko) | 1994-01-21 | 1997-10-11 | Olin Corp | |

| JPH07226575A (ja) * | 1994-02-14 | 1995-08-22 | Hitachi Chem Co Ltd | プリント配線板の製造法 |

| JP2513158B2 (ja) | 1994-05-25 | 1996-07-03 | 日本電気株式会社 | プリント配線板の製造方法 |

| JP2920083B2 (ja) | 1995-02-23 | 1999-07-19 | 日鉱グールド・フォイル株式会社 | 印刷回路用銅箔及びその製造方法 |

| JP2000294922A (ja) * | 1999-04-01 | 2000-10-20 | Victor Co Of Japan Ltd | 多層プリント配線板用の絶縁樹脂組成物 |

| JP4394234B2 (ja) | 2000-01-20 | 2010-01-06 | 日鉱金属株式会社 | 銅電気めっき液及び銅電気めっき方法 |

| JP3306404B2 (ja) * | 2000-01-28 | 2002-07-24 | 三井金属鉱業株式会社 | 表面処理銅箔の製造方法及びその製造方法で得られた表面処理銅箔を用いた銅張積層板 |

| JP3258308B2 (ja) | 2000-02-03 | 2002-02-18 | 株式会社日鉱マテリアルズ | レーザー穴開け性に優れた銅箔及びその製造方法 |

| US6346335B1 (en) * | 2000-03-10 | 2002-02-12 | Olin Corporation | Copper foil composite including a release layer |

| US20020182432A1 (en) | 2000-04-05 | 2002-12-05 | Masaru Sakamoto | Laser hole drilling copper foil |

| JP4475836B2 (ja) | 2000-09-25 | 2010-06-09 | イビデン株式会社 | 半導体素子の製造方法 |

| US6893742B2 (en) * | 2001-02-15 | 2005-05-17 | Olin Corporation | Copper foil with low profile bond enhancement |

| JP2003051673A (ja) * | 2001-08-06 | 2003-02-21 | Mitsui Mining & Smelting Co Ltd | プリント配線板用銅箔及びそのプリント配線板用銅箔を用いた銅張積層板 |

| JP4298943B2 (ja) | 2001-10-18 | 2009-07-22 | 日鉱金属株式会社 | 銅箔表面処理剤 |

| JP2003133719A (ja) * | 2001-10-26 | 2003-05-09 | Sumitomo Bakelite Co Ltd | 多層配線板の製造方法 |

| JP4379854B2 (ja) | 2001-10-30 | 2009-12-09 | 日鉱金属株式会社 | 表面処理銅箔 |

| JP4025177B2 (ja) * | 2001-11-26 | 2007-12-19 | 三井金属鉱業株式会社 | 絶縁層付銅箔の製造方法 |

| JP2003273484A (ja) * | 2002-03-13 | 2003-09-26 | Alps Electric Co Ltd | 接続構造 |

| US7749611B2 (en) * | 2002-12-05 | 2010-07-06 | Gbc Metals, L.L.C. | Peel strength enhancement of copper laminates |

| JP2005008955A (ja) * | 2003-06-19 | 2005-01-13 | Hitachi Cable Ltd | 銅箔の表面処理方法 |

| TW200535259A (en) * | 2004-02-06 | 2005-11-01 | Furukawa Circuit Foil | Treated copper foil and circuit board |

| KR100852863B1 (ko) | 2004-02-17 | 2008-08-18 | 닛코킨조쿠 가부시키가이샤 | 흑화 처리 면 또는 층을 가지는 동박 |

| JP2006103189A (ja) * | 2004-10-06 | 2006-04-20 | Furukawa Circuit Foil Kk | 表面処理銅箔並びに回路基板 |

| JP4986060B2 (ja) | 2005-06-23 | 2012-07-25 | Jx日鉱日石金属株式会社 | プリント配線板用銅箔 |

| JP2007046095A (ja) * | 2005-08-09 | 2007-02-22 | Mitsubishi Shindoh Co Ltd | 銅箔およびその表面処理方法 |

| JP5023732B2 (ja) * | 2006-03-23 | 2012-09-12 | 日立化成工業株式会社 | 積層板 |

| JP4918342B2 (ja) * | 2006-12-11 | 2012-04-18 | 福田金属箔粉工業株式会社 | 銅箔の粗面化処理方法 |

| JP4758945B2 (ja) | 2007-05-17 | 2011-08-31 | 株式会社リコー | スイッチバック機構および画像形成装置 |

| MY151361A (en) | 2008-06-17 | 2014-05-15 | Jx Nippon Mining & Metals Corp | Copper foil for printed circuit board and copper clad laminate for printed circuit board |

| JP5351461B2 (ja) | 2008-08-01 | 2013-11-27 | 日立電線株式会社 | 銅箔及び銅箔製造方法 |

| KR101426038B1 (ko) * | 2008-11-13 | 2014-08-01 | 주식회사 엠디에스 | 인쇄회로기판 및 그 제조방법 |

| US8524378B2 (en) | 2008-11-25 | 2013-09-03 | Jx Nippon Mining & Metals Corporation | Copper foil for printed circuit |

| CN102362559B (zh) * | 2009-03-27 | 2014-12-10 | 吉坤日矿日石金属株式会社 | 印刷布线板用铜箔及其制造方法 |

| CN107263959A (zh) | 2009-06-05 | 2017-10-20 | 吉坤日矿日石金属株式会社 | 半导体封装基板用铜箔及半导体封装用基板 |

| MY159142A (en) | 2009-06-19 | 2016-12-15 | Jx Nippon Mining & Metals Corp | Copper foil and method for producing same |

| MY172093A (en) | 2009-12-24 | 2019-11-13 | Jx Nippon Mining & Metals Corp | Surface-treated copper foil |

| EP2530770A1 (en) | 2010-01-25 | 2012-12-05 | JX Nippon Mining & Metals Corporation | Copper foil for secondary battery negative electrode power collector |

| CN102884228B (zh) | 2010-05-07 | 2015-11-25 | 吉坤日矿日石金属株式会社 | 印刷电路用铜箔 |

| WO2012043182A1 (ja) * | 2010-09-27 | 2012-04-05 | Jx日鉱日石金属株式会社 | プリント配線板用銅箔、その製造方法、プリント配線板用樹脂基板及びプリント配線板 |

| US9049795B2 (en) | 2011-03-25 | 2015-06-02 | Jx Nippon Mining & Metals Corporation | Rolled copper or copper-alloy foil provided with roughened surface |

| KR101999422B1 (ko) | 2011-03-30 | 2019-07-11 | 제이엑스금속주식회사 | 인쇄 회로용 동박 |

| JP5654416B2 (ja) | 2011-06-07 | 2015-01-14 | Jx日鉱日石金属株式会社 | 液晶ポリマー銅張積層板及び当該積層板に用いる銅箔 |

-

2011

- 2011-09-08 WO PCT/JP2011/070448 patent/WO2012043182A1/ja active Application Filing

- 2011-09-08 KR KR1020137008539A patent/KR101740092B1/ko active IP Right Grant

- 2011-09-08 US US13/825,889 patent/US9028972B2/en active Active

- 2011-09-08 MY MYPI2013001053A patent/MY161680A/en unknown

- 2011-09-08 JP JP2012536311A patent/JP5781525B2/ja active Active

- 2011-09-08 CN CN201610319842.2A patent/CN106028638B/zh active Active

- 2011-09-08 KR KR1020147035862A patent/KR101871029B1/ko active IP Right Grant

- 2011-09-08 CN CN201180046337.0A patent/CN103125149B/zh active Active

- 2011-09-08 EP EP11828743.2A patent/EP2624671A4/en not_active Withdrawn

- 2011-09-14 TW TW100132982A patent/TWI525222B/zh active

-

2014

- 2014-09-16 JP JP2014188321A patent/JP6029629B2/ja active Active

-

2016

- 2016-07-05 JP JP2016133772A patent/JP6243483B2/ja active Active

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002069691A (ja) | 2000-08-31 | 2002-03-08 | Nippon Denkai Kk | 印刷回路基板用銅箔の製造方法 |

| JP2005217052A (ja) * | 2004-01-28 | 2005-08-11 | Kyocera Corp | 配線基板及びその製造方法 |

| JP2005248323A (ja) * | 2004-02-06 | 2005-09-15 | Furukawa Circuit Foil Kk | 表面処理銅箔 |

| WO2007145164A1 (ja) | 2006-06-12 | 2007-12-21 | Nippon Mining & Metals Co., Ltd. | 粗化処理面を備えた圧延銅又は銅合金箔及び圧延銅又は銅合金箔の粗化方法 |

| JP2009215604A (ja) | 2008-03-10 | 2009-09-24 | Hitachi Cable Ltd | 銅箔とその製造方法 |

| WO2009145207A1 (ja) | 2008-05-28 | 2009-12-03 | 三井金属鉱業株式会社 | 銅箔の粗化処理方法及びその粗化処理方法で得られるプリント配線板用銅箔 |

| WO2010093009A1 (ja) | 2009-02-13 | 2010-08-19 | 古河電気工業株式会社 | 金属箔およびその製造方法,絶縁基板,配線基板 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2016208041A (ja) | 2016-12-08 |

| KR20130054405A (ko) | 2013-05-24 |

| KR20150003413A (ko) | 2015-01-08 |

| JPWO2012043182A1 (ja) | 2014-02-06 |

| CN103125149B (zh) | 2016-09-14 |

| WO2012043182A1 (ja) | 2012-04-05 |

| KR101740092B1 (ko) | 2017-05-25 |

| CN106028638B (zh) | 2019-09-03 |

| JP6243483B2 (ja) | 2017-12-06 |

| US9028972B2 (en) | 2015-05-12 |

| EP2624671A1 (en) | 2013-08-07 |

| JP2014241447A (ja) | 2014-12-25 |

| TW201221705A (en) | 2012-06-01 |

| US20130220685A1 (en) | 2013-08-29 |

| CN106028638A (zh) | 2016-10-12 |

| JP5781525B2 (ja) | 2015-09-24 |

| CN103125149A (zh) | 2013-05-29 |

| MY161680A (en) | 2017-05-15 |

| TWI525222B (zh) | 2016-03-11 |

| EP2624671A4 (en) | 2016-12-21 |

| JP6029629B2 (ja) | 2016-11-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101871029B1 (ko) | 프린트 배선판용 구리박, 그 제조 방법, 프린트 배선판용 수지 기판 및 프린트 배선판 | |

| JP5512567B2 (ja) | プリント配線板用銅箔の製造方法 | |

| KR102059280B1 (ko) | 수지와의 밀착성이 우수한 동박 및 그 제조 방법 그리고 그 전해 동박을 사용한 프린트 배선판 또는 전지용 부극재 | |

| KR102104161B1 (ko) | 프린트 배선판용 동박 및 그 제조 방법 | |

| JP4938130B2 (ja) | 印刷回路基板用銅箔及び印刷回路基板用銅張積層板 | |

| KR101853519B1 (ko) | 액정 폴리머 구리 피복 적층판 및 당해 적층판에 사용하는 구리박 | |

| KR101830994B1 (ko) | 조화처리된 동박, 그 제조방법, 동박 적층판 및 인쇄회로기판 | |

| EP3072682A1 (en) | Printed wiring board and its method of manufacture | |

| KR101344176B1 (ko) | 인쇄 회로 기판용 동박 및 인쇄 회로 기판용 동장 적층판 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A107 | Divisional application of patent | ||

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant |