KR100683100B1 - 반도체 집적 회로 장치 및 그 제조 방법 - Google Patents

반도체 집적 회로 장치 및 그 제조 방법 Download PDFInfo

- Publication number

- KR100683100B1 KR100683100B1 KR1020010082458A KR20010082458A KR100683100B1 KR 100683100 B1 KR100683100 B1 KR 100683100B1 KR 1020010082458 A KR1020010082458 A KR 1020010082458A KR 20010082458 A KR20010082458 A KR 20010082458A KR 100683100 B1 KR100683100 B1 KR 100683100B1

- Authority

- KR

- South Korea

- Prior art keywords

- conductivity type

- region

- type

- buried layer

- layer

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 46

- 238000000034 method Methods 0.000 title claims description 16

- 238000004519 manufacturing process Methods 0.000 title claims description 14

- 238000009792 diffusion process Methods 0.000 claims abstract description 67

- 239000000758 substrate Substances 0.000 claims description 41

- 239000012535 impurity Substances 0.000 claims description 18

- 230000015572 biosynthetic process Effects 0.000 claims description 11

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 claims description 6

- 229910052796 boron Inorganic materials 0.000 claims description 6

- 229910052787 antimony Inorganic materials 0.000 claims description 4

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 claims description 4

- 230000006698 induction Effects 0.000 claims 2

- 238000000151 deposition Methods 0.000 claims 1

- 230000015556 catabolic process Effects 0.000 abstract description 15

- 230000003071 parasitic effect Effects 0.000 description 29

- 238000000926 separation method Methods 0.000 description 10

- 150000002500 ions Chemical class 0.000 description 8

- 238000002955 isolation Methods 0.000 description 8

- 229920002120 photoresistant polymer Polymers 0.000 description 8

- 238000009795 derivation Methods 0.000 description 6

- 230000007423 decrease Effects 0.000 description 4

- 238000000206 photolithography Methods 0.000 description 4

- 230000003321 amplification Effects 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 238000003199 nucleic acid amplification method Methods 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- 239000003795 chemical substances by application Substances 0.000 description 2

- 230000006378 damage Effects 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 230000001965 increasing effect Effects 0.000 description 2

- 230000001939 inductive effect Effects 0.000 description 2

- 238000010030 laminating Methods 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- -1 for example Substances 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 238000003892 spreading Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/06—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66234—Bipolar junction transistors [BJT]

- H01L29/66272—Silicon vertical transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/06—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration

- H01L27/0611—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration integrated circuits having a two-dimensional layout of components without a common active region

- H01L27/0641—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration integrated circuits having a two-dimensional layout of components without a common active region without components of the field effect type

- H01L27/0647—Bipolar transistors in combination with diodes, or capacitors, or resistors, e.g. vertical bipolar transistor and bipolar lateral transistor and resistor

- H01L27/0652—Vertical bipolar transistor in combination with diodes, or capacitors, or resistors

- H01L27/0664—Vertical bipolar transistor in combination with diodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/08—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/0821—Collector regions of bipolar transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/86—Types of semiconductor device ; Multistep manufacturing processes therefor controllable only by variation of the electric current supplied, or only the electric potential applied, to one or more of the electrodes carrying the current to be rectified, amplified, oscillated or switched

- H01L29/861—Diodes

- H01L29/8611—Planar PN junction diodes

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Ceramic Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Bipolar Integrated Circuits (AREA)

- Bipolar Transistors (AREA)

Abstract

본 발명은, 출력 트랜지스터 보호에 적합한 스파크 킬러 다이오드(spark killer diode)를 내장한 반도체 집적 회로 장치에 있어서, 다이오드 소자가 OFF시에서의 내압을 큰 폭으로 향상시키는 다이오드 소자를 효율적으로 집적화하는 것을 목적으로 한다. 본 발명의 반도체 집적 회로 장치에서는, 애노드 영역으로서 형성되어 있는 제1 P+형 매립층(35)과 캐소드 영역에 형성되어 있는 N+형 확산 영역(41)을 깊이 방향으로 이격시켜 형성함으로써, 다이오드 소자(21)에 역방향 바이어스 전압이 걸린 경우에, PN 접합에서의 제1 및 제2 에피택셜층(25 및 26)으로 구성되는 N형 영역에 공핍층 형성 영역을 큰 폭으로 얻을 수 있고, 그의 형성된 공핍층에 의해 내압을 확보함으로써 항복 전류(breakdown current)에 의한 내부 소자 파괴를 억제할 수 있다.

반도체 집적 회로 장치, 다이오드, 애노드, 캐소드, 스파크 킬러 다이오드

Description

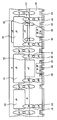

도 1은 본 발명의 반도체 집적 회로 장치를 설명하는 단면도.

도 2는 본 발명의 도 1의 반도체 집적 회로 장치의 다이오드 소자를 설명하기 위한 (A) 확대 단면도 및 (B) 등가 회로도.

도 3은 본 발명의 반도체 집적 회로 장치의 제조 방법을 설명하는 단면도.

도 4는 본 발명의 반도체 집적 회로 장치의 제조 방법을 설명하는 단면도.

도 5는 본 발명의 반도체 집적 회로 장치의 제조 방법을 설명하는 단면도.

도 6은 본 발명의 반도체 집적 회로 장치의 제조 방법을 설명하는 단면도.

도 7은 본 발명의 반도체 집적 회로 장치의 제조 방법을 설명하는 단면도.

도 8은 본 발명의 반도체 집적 회로 장치의 제조 방법을 설명하는 단면도.

도 9는 본 발명의 반도체 집적 회로 장치의 제조 방법을 설명하는 단면도.

도 10은 본 발명의 반도체 집적 회로 장치의 제조 방법을 설명하는 단면도.

도 11은 본 발명의 반도체 집적 회로 장치를 설명하는 회로도.

도 12는 종래의 반도체 집적 회로 장치의 다이오드 소자를 설명하기 위한 단면도.

<도면의 주요 부분에 대한 부호의 설명>

21 : 다이오드 소자

22 : 종형 PNP 트랜지스터

23 : NPN 트랜지스터

25, 26 : 에피택셜층

35 : P+형 매립층

41 : N+형 확산 영역

본 발명은 출력 트랜지스터 보호에 적합한 스파크 킬러 다이오드(spark killer diode)를 내장한 반도체 집적 회로 장치에 관한 것이다.

예를 들면, 3상 모터 드라이버는, 도 11과 같이, 직류 전원 VCC 및 GND간에 직렬 접속된 트랜지스터(Tr1-Tr2, Tr3-Tr4 및 Tr5-Tr6)가 병렬 접속되고, Tr1-Tr2, Tr3-TR4 및 Tr5-Tr6의 사이에서 인출된 출력 단자를 모터(M)에 접속한 회로 구성을 채용한다.

이와 같이 부하가 유도성 부하인 경우, 모터의 회전/정지에 따른 정/역방향의 기전력이 발생한다. 종래는, IC화된 직렬 접속 트랜지스터의 컬렉터 ·에미터간에 보호 다이오드를 접속하여, 상기 역방향 기전력에 의해서 출력 단자가 GND 전위보다 낮거나 VCC 전위보다 높아진 경우에 다이오드(4)가 ON됨으로써, 상기 기전 력을 고정 전위로 대피시키고, 직렬 접속된 트랜지스터를 포함하는 IC의 내부를 보호하였다. 특히, 다이오드(4)에 수 A의 대전류가 흐를 경우는, 다이오드(4)로서 개별 부품을 이용하여 구성하였다.

여기서, 유저측에서 보면 기기의 부품 개수를 감하기 위해서 다이오드(4)도 IC화할 필요가 있다. 하지만, 수 A의 대전류가 흐르는 다이오드를 집적화하면, 집적 회로 내에서 불가피하게 발생하는 기생 트랜지스터 효과에 의해서 기생 전류가 흘러서, 무효 전류가 흐르는 것 외에 최악의 경우는 래치업에 이르는 위험성을 내포하고 있다.

그래서, 기생 전류를 방지하는 구조로서, 예를 들면, 특개평6-100459호 공보에 기재된 구조가 제안되었다.

도 12를 참조하면, P형 반도체 기판(1)과 N형 반도체 기판(2)과의 사이에 N+형 매립층(3)이 설치되고, 이 매립층(3)을 둘러싸도록 P+형 분리 영역(4)이 반도체층(2) 표면으로부터 반도체 기판(1)까지 확산되어, 하나의 섬(5)을 형성하고 있다. 상기 매립층(3)의 위에는 일부 중첩하도록 P+형 매립층(6)이 형성되어 있다. 이러한 P+형 매립층(6)을 둘러싸고, 반도체층(2) 표면으로부터 N+형 매립층(3)에 도달하는 N+형 도출 영역(7)이 설치되고, 이 둘러싸인 영역에는 N+형 확산 영역(8)이 형성되어 있다. 또한, 도출 영역(7)으로 둘러싸인 영역에 있어서, 상기 확산 영역(8) 을 둘러싸고, 반도체층(2)으로부터 P+형 매립층(6)에 도달하는 P+형 도출 영역(9)이 설치되어 있다. 또한, 상기 확산 영역(8)에는 캐소드 전극(10)이, P+형 도출 영역(9)에는 애노드 전극(11)이 설치되고, 이 전극은 N+형 도출 영역(7)과 전기적으로 접속되어 있다.

요컨대, P+형 도출 영역(9)과 P+형 매립층(6)이 애노드 영역, N+형 확산 영역(8)과 도출 영역(9)으로 둘러싸인 N형 반도체 영역이 캐소드 영역으로 이루어져 다이오드가 구성된다.

이러한 다이오드 소자에 있어서는, N+형 매립층(3)을 베이스, P+형 매립층(6)을 에미터, P형 반도체 기판(1)이나 P+형 분리 영역(4)을 컬렉터로 하는 PNP형 기생 트랜지스터(Tr2)가 생기지만, 애노드 전극의 접속에 의해 이러한 기생 트랜지스터(Tr2)의 베이스와 에미터 사이가 동전위로 되기 때문에, 기생 PNP 트랜지스터(Tr2)가 ON 동작하는 것을 방지할 수 있다.

상기한 바와 같이 종래의 반도체 집적 회로 장치에서는 도 11에 도시한 바와 같이, 부하가 유도성 부하인 경우, 모터의 회전/정지에 따른 정/역방향의 기전력이 발생하기 때문에, IC화된 직렬 접속 트랜지스터의 컬렉터 ·에미터간에 보호 다이오드를 접속하고, 상기 역방향 기전력에 의해서 출력 단자가 GND 전위보다 낮거나 VCC 전위보다 높은 경우에 다이오드(4)가 ON됨으로써 상기 기전력을 고정 전위로 대피시키고, 직렬 접속된 트랜지스터를 포함하는 IC의 내부를 보호하였다. 특히, 다이오드(4)에 수 A의 대전류를 흘릴 경우는, 다이오드(4)로서 개별 부품을 이용하여 구성하였다.

또한, 기기의 부품 개수를 감하기 위해서 다이오드(4)도 IC화할 의도의 요망에 따라, 수 A의 대전류를 흘리는 다이오드를 집적화하였지만, 집적 회로 내에서 불가피하게 발생하는 기생 트랜지스터 효과에 의해서 기생 전류가 흘러서, 무효 전류가 흐르는 등의 문제에 따라 도 12에 도시한 바와 같은 다이오드를 IC의 내부에 도입한 구조로 되었다.

하지만, 상기한 바와 같이, 다이오드(4)를 IC의 내부에 인입하는 것은 가능하지만, 도 12에 도시하는 구조에 있어서 다이오드(4)가 OFF인 경우, 즉, 캐소드 전극(10)이 애노드 전극(11)보다 고전압으로 된 경우, 기생 트랜지스터(TR1)의 PN 접합면에서의 항복 전류에 의한 반도체 소자의 파괴에 대응하기 위한 내압이 필요하다. 따라서, 종래의 구조에서는 기생 트랜지스터(TR1)의 베이스 영역으로서의 P+형 매립층(6)의 폭이 좁고, 전류 증폭율(hfe)을 억제하기가 곤란하여 기생 트랜지스터(TR1)의 내압이 확보될 수 없는 문제가 발생하였다.

본 발명은 상기한 종래의 문제를 해결하기 위해 안출된 것으로서, 본 발명의 반도체 집적 회로 장치에서는, 일도전형의 반도체 기판과, 해당 기판 표면에 적층 되어 있는 역도전형의 제1 에피택셜층과, 상기 기판과 상기 제1 에피택셜층과의 사이에 형성되어 있는 고농도 불순물 확산층으로 구성되는 제1 역도전형의 매립층과 중첩하여 형성되어 있는 고농도 불순물 확산층으로 구성되는 제1 일도전형의 매립층과, 상기 제1 에피택셜층 표면에 적층되어 있는 역도전형의 제2 에피택셜층과, 상기 제1 에피택셜층과 상기 제2 에피택셜층과의 사이에 형성되어 있는 고농도 불순물 확산층으로 구성되는 제2 일도전형의 매립층 및 고농도 불순물 확산층으로 구성되는 제2 역도전형의 매립층과, 상기 제2 에피택셜층 표면으로부터 상기 제2 일도전형의 매립층까지 확산하여 형성되어 있는 고농도 불순물 확산층으로 구성되는 일도전형의 확산 영역과, 상기 제2 에피택셜층 표면으로부터 상기 제2 역도전형의 매립층까지 확산하여 형성되어 있고 고농도 불순물 확산층으로 구성되는 제1 역도전형의 확산 영역과, 상기 제2 일도전형의 매립층과 상기 일도전형의 확산 영역에 의해 샌드위치되고 상기 제2 에피택셜층에 형성되어 있는 역도전형의 웰 영역과, 상기 웰 영역에 중첩하여 형성되어 있는 고농도 불순물 확산층으로 구성되는 제2 역도전형의 확산 영역을 포함하는 다이오드 소자에 있어서, 상기 제1 일도전형의 매립층과 상기 제2 역도전형의 확산 영역이 깊이 방향으로 이격되어 형성되는 것을 특징으로 한다.

본 발명의 반도체 집적 회로 장치는, 바람직하게는, 상기 다이오드 소자의 상기 제1 일도전형의 매립층과 상기 제1 역도전형의 매립층을 중첩하여 형성하고, 또한, 상기 제1 일도전형의 매립층과 상기 일도전형의 확산 영역을 상기 제2 일도전형의 매립층을 통해서 연결한다. 또한, 상기 제1 일도전형의 매립층과 상기 제2 역도전형의 확산 영역을 깊이 방향으로 이격하여 형성하고 있는 구조를 갖는다. 그에 따라서, 상기 다이오드 소자가 OFF의 상태인 경우, 상기 다이오드 소자 내의 상기 제1 일도전형의 매립층과 상기 제1 에피택셜층을 접면으로 하는 PN 접합에 있어서, N형 영역에 공핍층 형성 영역을 큰 폭으로 얻을 수 있고, 상기 공핍층에 의해 내압을 확보함으로써 역방향 바이어스 상태에 대처하여, 항복 전류에 의한 내부 소자 파괴를 억제할 수 있는 반도체 접적 회로 장치를 얻을 수 있다.

본 발명의 반도체 집적 회로 장치는, 바람직하게는, 상기 다이오드 소자의 상기 역도전형의 캐소드 도출 영역과 중첩하여 상기 역도전형의 웰 영역을 형성하는데 그 특징을 갖는다. 그에 따라서, 상기 다이오드 소자가 ON의 상태인 경우, PN 접합의 N형 영역의 저항치가 낮아짐에 따라서 순방향 전압(VBFF)이 저감함으로써, 순방향에서 전류(If) 능력을 큰 폭으로 향상시키는 반도체 집적 회로 장치를 얻을 수 있다.

상술한 문제를 해결하기 위해서, 본 발명의 반도체 집적 회로 장치의 제조 방법에서는, 일도전형의 반도체 기판을 준비하는 공정과, 해당 기판에 불순물을 확산시켜서, 다이오드 소자, 일도전형의 종형 트랜지스터 및 역도전형의 종형 트랜지스터 형성 영역에 각각 역도전형의 매립층을 형성하는 공정과, 상기 기판 상에 불순물을 확산하여, 상기 다이오드 소자 형성 영역에 상기 역도전형의 매립층과 중첩하여 제1 일도전형의 매립층을 형성하는 공정과, 상기 기판 상에 역도전형의 제1 에피택셜층을 적층하는 공정과, 해당 제1 에피택셜층 상에 불순물을 확산하여, 상기 다이오드 소자 및 상기 일도전형의 종형 트랜지스터 형성 영역에 각각 제2 일도 전형의 매립층을 형성하는 공정과, 상기 제1 에피택셜층 상에 역도전형의 제2 에피택셜층을 적층하는 공정과, 해당 제2 에피택셜층 상에 불순물을 확산하여, 상기 다이오드 소자 형성 영역에 일도전형의 확산 영역을 형성하고, 상기 제2 일도전형의 매립층을 통해서 상기 제1 일도전형의 매립층과 연결하는 공정과, 상기 제2 에피택셜층 상에 불순물을 확산하여, 상기 다이오드 소자 및 상기 일도전형의 종형 트랜지스터 형성 영역에 역도전형의 웰 영역을 동시에 형성하는 공정과, 상기 다이오드 소자 형성 영역의 상기 웰 영역에 역도전형의 확산 영역을 형성하는 공정을 포함하는 것을 특징으로 한다.

본 발명의 반도체 집적 회로의 제조 방법은, 바람직하게는, 상기 제2 일도전형의 매립층을 형성하는 공정은, 상기 제1 일도전형의 매립층과 상기 일도전형의 확산 영역을 연결시키는 공정으로 함으로써, 상기 제1 역도전형의 매립층과 상기 역도전형의 확산 영역을 깊이 방향으로 큰 폭으로 격리하여 공핍층 형성 영역을 증대시킬 수 있는 공정인 것을 특징으로 한다.

이하에 본 발명의 실시 형태에 있어서, 도면을 참조하면서 상세히 설명한다.

도 1은 다이오드(21), 종형 PNP 트랜지스터(22) 및 NPN 트랜지스터(23)를 조립한 반도체 집적 회로 장치의 단면도이다.

P형 단결정 실리콘 기판(24) 상에는, 두께 2 ~ 10 ㎛의 제1 에피택셜층(25) 및 두께 8 ~ 10 ㎛의 제2 에피택셜층(26)이, 2층의 합계 막두께가 8 ~ 16 ㎛ 정도로 되도록 형성되어 있다. 또한, 기판(24)과, 제1 및 제2 에피택셜층(25 및 26)은 이들을 관통하는 P+형 분리 영역(27)에 의해서 다이오드 소자(21)를 형성하는 제1 섬영역(28), 종형 PNP 트랜지스터(22)를 형성하는 제2 섬영역(29) 및 NPN 트랜지스터(23)를 형성하는 제3 섬영역(30)이 전기적으로 분리되어 형성되어 있다.

이러한 분리 영역(27)은, 기판(24) 표면으로부터 상하 방향으로 확산한 제1 분리 영역(31)과, 제1 및 제2 에피택셜층(25 및 26)의 경계로부터 상하 방향으로 확산한 제2 분리 영역(32)과, 제2 에피택셜층(26) 표면으로부터 형성한 제3 분리 영역(33)으로 구성되고, 3자가 연결됨으로써 제1 및 제2 에피택셜층(25 및 26)을 섬 형상으로 분리한다.

제1 섬영역(28)에 형성되어 있는 다이오드 소자(21)에는, 기판(24)과 제1 에피택셜층(25)과의 사이에 N+형의 제1 매립층(34)과 P+형의 제1 매립층(35)이 중첩하여 형성되어 있고, 제1 및 제2 에피택셜층(25 및 26)의 경계 부분에 P+형의 제2 매립층(36)이 형성되어 있고, 제2 에피택셜층(26) 표면으로부터 P+형의 제2 매립층(36)에 달하는 P+형 확산 영역(39)이 애노드 도출 영역으로서 형성되어 있다. 또한, 이들 P+형 영역(36 및 39)에 끼여있는 N_형의 제1 및 제2 에피택셜층(25 및 26)이 캐소드 영역으로서 형성됨으로써 PN 접합 다이오드가 구성되어 있다. 이때, 제2 에피택셜층(26)에 N+형 확산 영역(38)을 애노드 영역으로서 형성하고, N+형 확산 영역(38)과 P+형 확산 영역(39)을 단락시켜서 애노드 도출 영역으로 하여도 된 다. 이는 NPN 트랜지스터라고 하면, 베이스와 컬렉터간을 단락시켜 형성한 다이오드로 된다.

상기 본 실시 형태의 반도체 회로 장치에 따르면, 기판(24)과 제1 에피택셜층(25)과의 사이에 N+형의 제1 매립층(34)과 P+형의 제1 매립층(35)이 중첩하여 형성되어 있지만, 예를 들면, N+형의 제1 매립층(34)은 안티몬(Sb)을 사용하고, P+형의 제1 매립층(35)은 붕소(B)를 사용하여 형성되어 있다. 그 때문에, 불순물의 확산 속도 및 불순물의 사용 농도의 상이함에 따라, 도 1에 도시한 바와 같이, N+형의 제1 매립층(34)의 상하에 P+형의 제1 매립층(35)이 형성되어 있는 구조를 갖는다. 또한, 제1 에피택셜층(25)과 제2 에피택셜층(26)과의 사이에 형성되어 있는 P+형의 제2 매립층(36)은 P+형의 제1 매립층(35) 및 P+형 확산 영역(39)과 연결된다. 이러한 구조에 따라서, P+형의 제1 매립층(35)을 애노드 영역으로서, 또한, 제1 및 제2 에피택셜층(25 및 26)을 캐소드 영역으로 한 PN 접합 다이오드가 형성되어 있다.

여기서, 캐소드 영역으로서 형성되어 있는 제2 에피택셜층(26)에는, N+형 확산 영역(41)이 캐소드 도출 영역으로서 형성되어 있지만, 상술한 바와 같이, N+형의 확산 영역(41)과 P+형의 제1 매립층(35)이 깊이 방향으로 이격되어 형성되어 있는 구조가 된다.

따라서, 상술한 구조를 가짐에 따라, 다이오드 소자(21)가 OFF의 상태인 경우, 요컨대, P+형의 제1 매립층(35)과 N-형의 제1 에피택셜층(25)으로 형성되어 있는 PN 접합면에 역바이어스 전압이 걸리는 경우, 제1 및 제2 에피택셜층(25 및 26)으로 구성되는 N형 영역에 공핍층 형성 영역을 큰 폭으로 얻을 수 있고, 그의 형성된 공핍층에 의해 내압을 확보함으로써 항복 전류에 의한 내부 소자 파괴를 억제할 수 있는 반도체 집적 회로 장치를 얻을 수 있다.

또한, 상기의 본 실시 형태의 반도체 집적 회로 장치에 따르면, 다이오드 소자가 ON시에 있어서, 캐소드 영역으로서 형성되어 있고, P+형 영역(36 및 39)에 의해 샌드위치된 N+형의 제2 에피택셜층(26)에, N+형 웰 영역(40)이 형성되어 있다. 이 N+형 웰 영역(40)에 의해, PN 접합의 N형 영역의 저항치가 낮아짐에 따라 순방향 전압(VBFF)이 저감함으로써 순방향에서의 전류(If) 능력을 큰 폭으로 향상시킬 수 있다.

또한, 제2 에피택셜층(26)의 표면은 실리콘 산화막에 의해서 피복되고, 산화막에 형성된 콘택트홀을 통해서 각종 알루미늄 전극이 설치되어 있다. 기판(24)에는 접합 분리를 위한 접지 전위(GND)가 인가되어 있다.

여기서, 도 2의 (A)는 다이오드 소자(21)의 확대 단면도를 도시한 도면이고, 도 2의 (B)는 기생 트랜지스터를 도시한 등가 회로도이다. 이하, 다이오드 소자(21)가 ON 상태에서의 기판(24)으로의 누설 전류를 좌우하는 기생 트랜지스터의 동작에 대해서 설명한다.

기생 NPN 트랜지스터(TR1)는, N+형의 제1 매립층(34)을 컬렉터, P+형 매립층(35)을 베이스, 그리고 제1 및 제2 에피택셜층(25 및 26)을 에미터로 하여 구성되어 있다. 한편, 기생 PNP 트랜지스터(TR2)는 P형 기판(24)을 컬렉터, N+형의 제1 매립층(34)을 베이스 및 P+형 매립층(35)을 에미터로 하여 구성되어 있다.

도 2의 (B)를 참조하면, 기생 NPN 트랜지스터(TR1)의 베이스 ·컬렉터는 애노드 전극(55)에 의해서 단락되고, 동일하게 기생 PNP 트랜지스터(TR2)의 베이스 ·에미터 간이 단락된다. 이때, 기생 NPN 트랜지스터(TR1)의 베이스 ·컬렉터간에는 P+형 확산 영역(39)과 P+형 매립층(36)이 갖는 저항 성분(R1)이 접속되고, 기생 PNP 트랜지스터(TR2)의 베이스 ·에미터간에는 N+형 확산 영역(38), N+형의 제2 매립층(37) 및 N+형 제1 매립층(34)이 갖는 저항 성분(R2)이 접속되어 있다. 본 발명의 다이오드 소자(21)의 구조에서는, 기생 NPN 트랜지스터(TR1)의 저항 성분(R1)의 경우는, P+형 확산 영역(39), P+형 매립층(36) 및 P+형의 제1 매립층(35)의 연결에 의해 구성되기 때문에, 저항 성분(R1)의 값은 극히 작아 진다. 또한, 기생 PNP 트랜지스터(TR2)의 저항 성분(R2)의 경우도, N+형 확산 영역(38), N+형의 제2 매립층(37) 및 N+형의 제1 매립층(34)의 연결에 따라서 저항 성분(R2)의 값은 극히 작아 진다.

본 발명은 N+형 웰 영역(40)의 형성에 의해 캐소드 영역의 저항을 낮출 수 있기 때문에, 순방향 전류(If)의 능력을 향상시킬 수 있다.

한편, 기생 PNP 트랜지스터(TR2)의 베이스 ·에미터간에 접속되는 저항 성분(R2)의 값은 작아질 수 있기 때문에, 기생 PNP 트랜지스터(TR2)의 베이스 전위(N+형의 제1 매립층(34)의 전위)를 에미터 전위(P+형 매립층(35 및 36)의 전위)보다 높게 유지시킬 수 있다. 따라서, 기생 PNP 트랜지스터(TR2)의 ON 동작을 방지하고, 기판(24)으로의 누설 전류를 작게 유지할 수 있게 된다.

그 결과, 상술한 기생 PNP 트랜지스터(TR2)에 있어서, 예를 들면, 종래의 구조에서는 1A를 흘릴 때 기판(24)으로의 누설 전류가 100㎃인 것에 대하여, 본 발명의 구조(저항 성분(R2)의 저항치를 8Ω으로 한 경우)에서는 20㎃까지 저감할 수 있다.

제2 섬영역(29)에 형성되어 있는 종형 PNP 트랜지스터(22)에 있어서, 기본적으로 다이오드 소자(21)와 동일한 구조를 구비하고 있다. 구체적으로, 제1 및 제2 에피택셜층(25 및 26)의 경계 부분에 P+형 매립층(43)이 컬렉터 영역으로서 형성되어 있고, 제2 에피택셜층(26) 표면으로부터 P+형 매립층(43)에 달하는 P+형 확산 영 역(46)이 컬렉터 도출 영역으로서 형성되어 있다. 또한, 이들 P+형 영역에 둘러싸인 N-형의 제2 에피택셜층(26)에 N+형 웰 영역(47)이 베이스 영역으로서 형성되어 있고, N+형 웰 영역(47)에는 P+형 확산 영역(48)이 에미터 영역으로서, 또한, N+

형 확산 영역(49)이 베이스 도출 영역으로 형성됨으로써 종형 PNP 트랜지스터(22)가 구성된다. 또한, P+형 확산 영역(46)을 둘러싸도록 N+형 확산 영역(45)을 형성하고, N+형의 제2 매립층(44)을 통해서 제1 매립층(42)에 연결되고, 도시하지 않은 전극에 의해 전원 전위(Vcc) 또는 에미터 전극(58)의 전위를 인가하였다. 이는 P+형 확산 영역(46)을 에미터, 제2 섬영역(29)을 베이스, P+형 확산 영역(27)을 컬렉터로 하는 기생 PNP 트랜지스터의 발생을 억제하는 것으로, 이 종형 PNP 트랜지스터를 대전류 용도에 적합한 PNP 트랜지스터로 할 수 있다.

제3 섬영역(30)에 형성되어 있는 NPN 트랜지스터(23)에 있어서, 제3 섬영역(30)을 컬렉터 영역으로 하고, P형 확산 영역(53)을 베이스 영역으로 하고, N+형 확산 영역(54)을 에미터 영역으로 하여 형성되어 있는 것으로 구성된다. 또한, 기판(24)과 제1 에피택셜층(25)간에 제1 N+형 매립층(50)과 제1 및 제2 에피택셜층(25 및 26)의 경계 부분에도 제2 N+형 매립층(51)이 연결되어 형성된다. 또한, N+형 확산 영역(52)을 컬렉터 도출 영역으로 하고, N+형 확산 영역(52)도 제2 N+

형 매립층(51)과 연결하여 형성되어 있다. 이와 같이, 컬렉터 전극(62)의 하부에 고농도 저저항 영역을 구성함으로써, NPN 트랜지스터(23)의 포화 저항(Vce)(Sat)을 저감한다. 따라서, 이 NPN 트랜지스터(23)는 고내압, 대전류용으로서, 모터 드라이버 등의 회로 용도에 적합하다.

다음에, 도 1에 도시한 본 발명의 반도체 집적 회로 장치의 제조 방법에 대해서 도 3 ~ 도 10을 참조하여 설명한다.

우선, 도 3에 도시한 바와 같이, P_형 단결정 실리콘 기판(24)을 준비하고, 이 기판(24)의 표면을 열산화하여 열산화막을 형성하고, N+형의 제1 매립층(34, 42 및 50)에 대응하는 산화막을 핫 에칭하여 선택 마스크로 한다. 그리고, 기판(24) 표면에 N+형 매립층(34, 42 및 50)을 형성하는 안티몬(Sb)을 확산한다.

다음에, 도 4에 도시한 바와 같이, P+형 매립층(35) 및 P+형 분리 영역(27)의 제1 분리 영역(31)을 형성하기 위해서, 이온 주입을 행한다. 도 3에 있어서, 선택 마스크로서 이용한 산화막을 모두 제거한 후, 공지의 포토리소그래피 기술에 의해 P+형의 제1 분리 영역(31)을 형성하는 부분에 개구부가 설치된 포토 레지스트(도시되지 않음)를 선택 마스크로서 형성한다. 그리고, P형 불순물, 예를 들면, 붕소(B)를 이온 에너지 160keV, 도입량 1.0 ×1014/㎠로 이온 주입한다. 그 후, 포토레지스트를 제거한다.

다음에, 도 5에 도시한 바와 같이, 산화막을 전부 제거한 후, 기판(24)을 에피택셜 성장 장치의 서셉터 상에 배치하고, 램프 가열에 의해서 기판(24)에 1140℃ 정도의 온도를 제공함과 함께 반응관 내에 SiH2Cl2 가스와 H2 가스를 도입함으로써 저농도 에피(ρ= 1.25Ω㎝), 두께 2.0 ~ 10.0㎛의 제1 에피택셜층(25)을 성장시킨다. 그리고, 제1 에피택셜층(25)의 표면을 열산화하여 열산화막을 형성한 후, N+형의 제2 매립층(37, 44, 51)에 대응하는 산화막을 핫 에칭하여 선택 마스크로 한다.

여기서, 동시에, 기판(24) 표면에 N+형 매립층(34, 42 및 50) 및 P+형 매립층(31 및 35)을 확산한다. 이때, P+형 매립층(35)을 형성하는 붕소(B)는, N+형 매립층(34)을 형성하는 안티몬(Sb)과 비교해서 확산 속도가 빠르고, 또한, 불순물 농도가 낮기 때문에, N+형 매립층(34)의 상하에 형성 영역이 형성된다.

다음에, 도 6에 도시한 바와 같이, 산화막을 전부 제거한 후, 다시, 제1 에피택셜층(25)의 표면을 열산화하여 산화막을 형성하고, 공지의 포토리소그래피 기술에 의해 P+형 매립층(36 및 43) 및 P+형의 제2 분리 영역(32)을 형성하는 부분에 개구부가 설치된 포토레지스트(도시되지 않음)를 선택 마스크로서 형성한다. 그리고, P형 불순물, 예를 들면, 붕소(B)를 이온 에너지 40keV, 도입량 3.0 ×1013/㎠로 이온 주입한다. 그 후, 포토레지스트를 제거한다. 이때, 제2 N+형 매립층(37, 44 및 51)은 동시에 확산되어, 제1 N+형 매립층(34, 42 및 50)과 연결된다.

다음에, 도 7에 도시한 바와 같이, 산화막을 전부 제거한 후, 기판(24)을 에피택셜 성장 장치의 서셉터 상에 배치하고, 램프 가열에 의해 기판(24)에 1140℃ 정도의 온도를 제공함과 함께 반응관 내에 SiH2Cl2 가스와 H2 가스를 도입함으로써 저농도 에피(ρ= 1.25Ω㎝), 두께 8.0 ~ 10.0㎛의 제2 에피택셜층(26)을 제1 에피택셜층(25) 상에 성장시킨다. 그리고, 제2 에피택셜층(26)의 표면을 열산화하여 열산화막을 형성한 후, 공지의 포토리소그래피 기술에 의해 N+형 웰 영역(40 및 47)을 형성하는 부분에 개구부가 설치된 포토레지스트(도시되지 않음)를 선택 마스크로서 형성한다. 그리고, N형 불순물, 예를 들면, 인(P)를 이온 에너지 160keV, 도입량 1.0 ×1012/㎠로 이온 주입한다. 그 후, 포토레지스트를 제거한다.

이때, P+형 매립층(36 및 43) 및 P+형의 제2 분리 영역(32)은 동시에 확산되어, 각각 제1 P+형 매립층(35), 제1 N+형 매립층(42) 및 P+형의 제1 분리 영역(31)과 연결된다.

다음에, 도 8에 도시한 바와 같이, 제2 에피택셜층(26)의 표면을 열산화하여 산화막을 형성하고, N+형의 컬렉터 도출 영역(38, 45 및 52) 및 베이스 도출 영역(49)에 대응하는 산화막을 핫 에칭하여 선택 마스크로 한다. 또한, 제2 에피택셜층(26) 표면에 N+형 확산 영역(38, 45 및 52) 및 베이스 도출 영역(49)을 형성 하는 안티몬(Sb)을 확산한다.

다음에, 도 9에 도시한 바와 같이, 산화막을 모두 제거한 후, 다시, 제2 에피택셜층(26)의 표면을 열산화하여 산화막을 형성하고, 공지의 포토리소그래피 기술에 의해 P+형 확산 영역(39 및 46) 및 P+형의 에미터 영역(48) 및 P+형의 제3 분리 영역(33)을 형성하는 부분에 개구부가 설치된 포토레지스트(도시되지 않음)를 선택 마스크로서 형성한다. 그리고, P형 불순물, 예를 들면, 붕소(B)를 이온 에너지 40keV, 도입량 3.0 ×1013/㎠로 이온 주입한다. 그 후, 포토레지스트를 제거한다.

이때, 제2 N+형 매립층(37, 44 및 51)은 동시에 확산되어, 제1 N+형 매립층(34, 42 및 50)과 연결된다. 또한, N+형 확산 영역(38, 45 및 52)은 동시에 확산되어, 각각 제2 N+형 매립층(37, 44 및 51)과 연결된다. 그 결과, 제1 섬영역(28)에는 다이오드 소자(21)가 완성되고, 제2 섬영역(29)에는 종형 PNP 트랜지스터(22)가 완성된다.

다음에, 도 10에 도시한 바와 같이, 제3 섬영역(30)에는 P형 베이스 영역(53) 및 N+형 에미터 영역(54)을 형성함으로써, NPN 트랜지스터(23)가 완성된다. 그 후, 도 1에 도시한 바와 같이, 다이오드 소자(21)에는 애노드 전극(55), 캐소드 전극(56)이, 종형 PNP 트랜지스터(22)에는 컬렉터 전극(57), 에미터 전극(58), 베이스 전극(59)이, NPN 트랜지스터(23)에는 에미터 전극(60), 베이스 전극(61), 컬렉터 전극(62)이 알루미늄 재료에 의해 형성함으로써 외부 전극과 접속된다.

본 발명에 따르면, 반도체 집적 회로 장치의 다이오드 소자에 있어서, 기판과 제1 에피택셜층과의 사이에 형성되어 있는 P+형의 제1 매립층과, 캐소드 전극과 접속되어 있는 N+형 확산 영역과는 PN 접합을 형성하고 있지만, 이러한 양자는 깊이 방향으로 사이를 두고서 형성되어 있다. 그에 따라서, 상기 다이오드 소자가 OFF의 경우, 요컨대, 상기 다이오드 소자에 역방향 바이어스 전압이 걸리는 경우, 제1 및 제2 에피택셜층으로 구성되는 N형 영역에 공핍층 형성 영역을 큰 폭으로 얻을 수 있고, 그의 형성된 공핍층에 의해 내압을 확보하여 항복 전류에 의한 내부 소자 파괴를 억제할 수 있는 반도체 집적 회로 장치를 얻을 수 있다.

또한, 본 발명에 따르면, 반도체 집적 회로 장치의 다이오드 소자에 있어서, 다이오드 소자가 ON의 상태인 경우, 캐소드 영역으로서 형성되어 있는 N-형의 제2 에피택셜층에, N+형 웰 영역이 형성되어 있다. 이러한 N+형 웰 영역에 의해 PN 접합의 N형 영역의 저항치가 낮아짐에 따라 순방향 전압(VBEF)가 저감함으로써, 순방향에서의 전류(If) 능력을 큰 폭으로 향상시킬 수 있다.

또한, 본 발명에 따른 N+형 웰 영역 형성에 의해, 다이오드 소자가 ON의 상태인 경우, 다이오드 소자 내에 형성되는 기생 트랜지스터(TR1)의 전류 증폭율은 향상되고, 기생 트랜지스터(TR2)의 전류 증폭율은 저감할 수 있고, 기판으로의 누설 전류의 억제 효과가 높아진다. 그 결과, 출력 트랜지스터 보호에 적합한 스파크 킬러 다이오드를 반도체 집적 회로 장치에 집적화할 수 있고, 전자 기기의 소형화, 고밀도화에 기여할 수 있다.

Claims (7)

- 일 도전형의 반도체 기판과,상기 기판 상면에 적층되어 있는 역도전형의 제1 에피택셜층과,상기 기판 및 상기 제1 에피택셜층에 형성되어 있는 역도전형의 제1 매립층과,상기 기판 및 상기 제1 에피택셜층에 상기 역도전형의 제1 매립층과 형성 영역을 중첩시켜, 적어도 일 영역이 상기 역도전형의 제1 매립층의 상면에 형성되어 있는 일 도전형의 제1의 매립층과,상기 제1 에피택셜층 상면에 적층되어 있는 역도전형의 제2 에피택셜층과,상기 제1 및 제2 에피택셜층에 형성되어, 상기 일 도전형의 제1 매립층과 연결하는 일 도전형의 제2 매립층과,상기 제1 및 제2 에피택셜층에 형성되어, 상기 역도전형의 제1 매립층과 연결하는 역도전형의 제2 매립층과,상기 제2 에피택셜층에 형성되어, 상기 일 도전형의 제2 매립층과 연결하는 일 도전형의 확산 영역과,상기 제2 에피택셜층에 형성되어, 상기 일 도전형의 확산 영역에 둘러싸여진 영역에 배치된 역도전형의 제1 확산 영역과,상기 제2 에피택셜층에 형성되어, 상기 역도전형의 제2 매립층과 연결하는 역도전형의 제2 확산 영역을 포함하는 것을 특징으로 하는 반도체 집적 회로 장치.

- 제1항에 있어서,상기 일 도전형의 확산 영역에 둘러싸여진 영역에서는, 역도전형의 제3 확산 영역이 상기 역도전형의 제1 확산 영역과 형성 영역을 중첩시키고 있는 것을 특징으로 하는 반도체 집적 회로 장치.

- 제1항에 있어서,상기 일 도전형의 확산 영역과 상기 역도전형의 제2 확산 영역은, 상기 제2 에피택셜층 상면에서 단락되어 있는 것을 특징으로 하는 반도체 집적 회로 장치.

- 제3항에 있어서,상기 일 도전형의 확산 영역과 상기 역도전형의 제2 확산 영역은 애노드 도출 영역으로서, 상기 역도전형의 제1 확산 영역은 캐소드 도출 영역으로서 형성되어 있는 것을 특징으로 하는 반도체 집적 회로 장치.

- 일 도전형의 반도체 기판 상면에 역도전형의 제1 에피택셜층을 퇴적하고, 상기 기판 및 상기 제1 에피택셜층에 역도전형의 제1 매립층과 형성 영역을 중첩시켜 적어도 일영역이 상기 역도전형의 제1 매립층의 상면에 배치되는 일 도전형의 제1 매립층을 형성하는 공정과,상기 제1 에피탤셜층 상면에 역도전형의 제2 에피택셜층을 퇴적하고, 상기 제1 및 제2 에피택셜층에 상기 일 도전형의 제1 매립층과 연결하는 일 도전형의 제2 매립층 및 상기 역도전형의 제1 매립층과 연결하는 역도전형의 제2 매립층을 형성하는 공정과,상기 제2 에피택셜층에 역도전형의 제1 확산 영역을 형성하고,상기 역도전형의 제1 확산 영역을 둘러싸도록, 상기 일도전형의 제2 매립층과 연결하는 일 도전형의 확산 영역을 형성하는 공정과,상기 제2 에피택셜층에 상기 역도전형의 제2 매립층과 연결하는 역도전형의 제2 확산 영역을 형성하는 공정을 포함하는 것을 특징으로 하는 반도체 집적 회로장치의 제조 방법.

- 제5항에 있어서,상기 일 도전형의 제1 매립층은, 상기 기판에 역도전형의 불순물을 주입하고, 확산 시킨 후, 상기 확산시킨 영역에 일 도전형의 불순물을 주입하고, 확산하여 형성하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

- 제6항에 있어서,상기 일 도전형의 제1 매립층은, 상기 기판에 붕소를 주입하고, 확산시켜서 형성하고,상기 역도전형의 제1 매립층은, 상기 기판에 안티몬을 주입하고, 확산함으로써 형성하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000392221A JP4065104B2 (ja) | 2000-12-25 | 2000-12-25 | 半導体集積回路装置およびその製造方法 |

| JPJP-P-2000-00392221 | 2000-12-25 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20020052954A KR20020052954A (ko) | 2002-07-04 |

| KR100683100B1 true KR100683100B1 (ko) | 2007-02-15 |

Family

ID=18858242

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020010082458A KR100683100B1 (ko) | 2000-12-25 | 2001-12-21 | 반도체 집적 회로 장치 및 그 제조 방법 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US6590273B2 (ko) |

| JP (1) | JP4065104B2 (ko) |

| KR (1) | KR100683100B1 (ko) |

| CN (1) | CN100431153C (ko) |

Families Citing this family (64)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6524921B1 (en) * | 2002-03-08 | 2003-02-25 | Micron Technology, Inc. | Methods of forming bipolar transistor constructions |

| JP3761162B2 (ja) * | 2002-03-27 | 2006-03-29 | ローム株式会社 | バイポーラトランジスタ及びこれを用いた半導体装置 |

| JP4067346B2 (ja) * | 2002-06-25 | 2008-03-26 | 三洋電機株式会社 | 半導体集積回路装置 |

| DE10250204B8 (de) * | 2002-10-28 | 2008-09-11 | Infineon Technologies Ag | Verfahren zur Herstellung von Kollektorbereichen einer Transistorstruktur |

| JP4775683B2 (ja) * | 2003-09-29 | 2011-09-21 | オンセミコンダクター・トレーディング・リミテッド | 半導体集積回路装置 |

| JP4775684B2 (ja) * | 2003-09-29 | 2011-09-21 | オンセミコンダクター・トレーディング・リミテッド | 半導体集積回路装置 |

| US7138701B2 (en) * | 2003-10-02 | 2006-11-21 | International Business Machines Corporation | Electrostatic discharge protection networks for triple well semiconductor devices |

| DE10351014B4 (de) * | 2003-10-31 | 2008-06-05 | Infineon Technologies Ag | Diodenstruktur und integrale Leistungsschaltanordnung mit Low-Leakage-Diode |

| US7095092B2 (en) * | 2004-04-30 | 2006-08-22 | Freescale Semiconductor, Inc. | Semiconductor device and method of forming the same |

| JP2006237224A (ja) * | 2005-02-24 | 2006-09-07 | Sanyo Electric Co Ltd | 半導体装置 |

| JP4927340B2 (ja) * | 2005-02-24 | 2012-05-09 | オンセミコンダクター・トレーディング・リミテッド | 半導体装置 |

| JP4944460B2 (ja) * | 2005-03-30 | 2012-05-30 | オンセミコンダクター・トレーディング・リミテッド | 半導体装置 |

| KR100752484B1 (ko) * | 2005-09-27 | 2007-08-27 | 산요덴키가부시키가이샤 | 반도체 장치 및 그 제조 방법 |

| JP2007158188A (ja) * | 2005-12-07 | 2007-06-21 | Sanyo Electric Co Ltd | 半導体装置及びその製造方法 |

| JP5261640B2 (ja) * | 2005-12-09 | 2013-08-14 | セミコンダクター・コンポーネンツ・インダストリーズ・リミテッド・ライアビリティ・カンパニー | 半導体装置の製造方法 |

| JP2007165370A (ja) * | 2005-12-09 | 2007-06-28 | Sanyo Electric Co Ltd | 半導体装置及びその製造方法 |

| JP2007294613A (ja) | 2006-04-24 | 2007-11-08 | Sanyo Electric Co Ltd | 半導体装置及びその製造方法 |

| JP5108250B2 (ja) * | 2006-04-24 | 2012-12-26 | オンセミコンダクター・トレーディング・リミテッド | 半導体装置及びその製造方法 |

| JP2007317767A (ja) * | 2006-05-24 | 2007-12-06 | Matsushita Electric Ind Co Ltd | 光半導体装置およびその製造方法 |

| JP2007317869A (ja) * | 2006-05-25 | 2007-12-06 | Sanyo Electric Co Ltd | 半導体装置及びその製造方法 |

| JP2008085187A (ja) * | 2006-09-28 | 2008-04-10 | Sanyo Electric Co Ltd | 半導体装置 |

| JP2008085186A (ja) * | 2006-09-28 | 2008-04-10 | Sanyo Electric Co Ltd | 半導体装置 |

| JP4979513B2 (ja) * | 2007-08-22 | 2012-07-18 | ルネサスエレクトロニクス株式会社 | 半導体装置及びその製造方法 |

| JP2009194301A (ja) * | 2008-02-18 | 2009-08-27 | Sanyo Electric Co Ltd | 半導体装置 |

| EP2180517A1 (en) * | 2008-10-24 | 2010-04-28 | Epcos Ag | Pnp bipolar transistor with lateral collector and method of production |

| US7989923B2 (en) * | 2008-12-23 | 2011-08-02 | Amazing Microelectronic Corp. | Bi-directional transient voltage suppression device and forming method thereof |

| US8222698B2 (en) * | 2009-06-29 | 2012-07-17 | Analog Devices, Inc. | Bond pad with integrated transient over-voltage protection |

| US8044457B2 (en) * | 2009-06-29 | 2011-10-25 | Analog Devices, Inc. | Transient over-voltage clamp |

| US9520486B2 (en) | 2009-11-04 | 2016-12-13 | Analog Devices, Inc. | Electrostatic protection device |

| US8665571B2 (en) | 2011-05-18 | 2014-03-04 | Analog Devices, Inc. | Apparatus and method for integrated circuit protection |

| US8432651B2 (en) | 2010-06-09 | 2013-04-30 | Analog Devices, Inc. | Apparatus and method for electronic systems reliability |

| US8368116B2 (en) | 2010-06-09 | 2013-02-05 | Analog Devices, Inc. | Apparatus and method for protecting electronic circuits |

| US8416543B2 (en) | 2010-07-08 | 2013-04-09 | Analog Devices, Inc. | Apparatus and method for electronic circuit protection |

| US8553380B2 (en) | 2010-07-08 | 2013-10-08 | Analog Devices, Inc. | Apparatus and method for electronic circuit protection |

| CN102386121B (zh) * | 2010-09-01 | 2014-11-05 | 无锡华润上华半导体有限公司 | 半导体器件和半导体埋层的制造方法 |

| US10199482B2 (en) | 2010-11-29 | 2019-02-05 | Analog Devices, Inc. | Apparatus for electrostatic discharge protection |

| US8466489B2 (en) | 2011-02-04 | 2013-06-18 | Analog Devices, Inc. | Apparatus and method for transient electrical overstress protection |

| US8592860B2 (en) | 2011-02-11 | 2013-11-26 | Analog Devices, Inc. | Apparatus and method for protection of electronic circuits operating under high stress conditions |

| US8680620B2 (en) | 2011-08-04 | 2014-03-25 | Analog Devices, Inc. | Bi-directional blocking voltage protection devices and methods of forming the same |

| JP2013073993A (ja) * | 2011-09-27 | 2013-04-22 | Semiconductor Components Industries Llc | 半導体装置 |

| US8947841B2 (en) | 2012-02-13 | 2015-02-03 | Analog Devices, Inc. | Protection systems for integrated circuits and methods of forming the same |

| US8829570B2 (en) | 2012-03-09 | 2014-09-09 | Analog Devices, Inc. | Switching device for heterojunction integrated circuits and methods of forming the same |

| US8946822B2 (en) | 2012-03-19 | 2015-02-03 | Analog Devices, Inc. | Apparatus and method for protection of precision mixed-signal electronic circuits |

| US8610251B1 (en) | 2012-06-01 | 2013-12-17 | Analog Devices, Inc. | Low voltage protection devices for precision transceivers and methods of forming the same |

| US8637899B2 (en) | 2012-06-08 | 2014-01-28 | Analog Devices, Inc. | Method and apparatus for protection and high voltage isolation of low voltage communication interface terminals |

| US8796729B2 (en) | 2012-11-20 | 2014-08-05 | Analog Devices, Inc. | Junction-isolated blocking voltage devices with integrated protection structures and methods of forming the same |

| US9123540B2 (en) | 2013-01-30 | 2015-09-01 | Analog Devices, Inc. | Apparatus for high speed signal processing interface |

| US8860080B2 (en) | 2012-12-19 | 2014-10-14 | Analog Devices, Inc. | Interface protection device with integrated supply clamp and method of forming the same |

| US9006781B2 (en) | 2012-12-19 | 2015-04-14 | Analog Devices, Inc. | Devices for monolithic data conversion interface protection and methods of forming the same |

| US9275991B2 (en) | 2013-02-13 | 2016-03-01 | Analog Devices, Inc. | Apparatus for transceiver signal isolation and voltage clamp |

| US9147677B2 (en) | 2013-05-16 | 2015-09-29 | Analog Devices Global | Dual-tub junction-isolated voltage clamp devices for protecting low voltage circuitry connected between high voltage interface pins and methods of forming the same |

| US9171832B2 (en) | 2013-05-24 | 2015-10-27 | Analog Devices, Inc. | Analog switch with high bipolar blocking voltage in low voltage CMOS process |

| US9306034B2 (en) * | 2014-02-24 | 2016-04-05 | Vanguard International Semiconductor Corporation | Method and apparatus for power device with multiple doped regions |

| US9484739B2 (en) | 2014-09-25 | 2016-11-01 | Analog Devices Global | Overvoltage protection device and method |

| US9478608B2 (en) | 2014-11-18 | 2016-10-25 | Analog Devices, Inc. | Apparatus and methods for transceiver interface overvoltage clamping |

| US10068894B2 (en) | 2015-01-12 | 2018-09-04 | Analog Devices, Inc. | Low leakage bidirectional clamps and methods of forming the same |

| US10181719B2 (en) | 2015-03-16 | 2019-01-15 | Analog Devices Global | Overvoltage blocking protection device |

| US9673187B2 (en) | 2015-04-07 | 2017-06-06 | Analog Devices, Inc. | High speed interface protection apparatus |

| US9831233B2 (en) | 2016-04-29 | 2017-11-28 | Analog Devices Global | Apparatuses for communication systems transceiver interfaces |

| US10734806B2 (en) | 2016-07-21 | 2020-08-04 | Analog Devices, Inc. | High voltage clamps with transient activation and activation release control |

| JP2020009790A (ja) * | 2016-11-09 | 2020-01-16 | シャープ株式会社 | アバランシェフォトダイオード |

| US10249609B2 (en) | 2017-08-10 | 2019-04-02 | Analog Devices, Inc. | Apparatuses for communication systems transceiver interfaces |

| US10700056B2 (en) | 2018-09-07 | 2020-06-30 | Analog Devices, Inc. | Apparatus for automotive and communication systems transceiver interfaces |

| US11387648B2 (en) | 2019-01-10 | 2022-07-12 | Analog Devices International Unlimited Company | Electrical overstress protection with low leakage current for high voltage tolerant high speed interfaces |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR0152155B1 (ko) * | 1994-03-31 | 1998-10-01 | 다까노 야스아끼 | 반도체 집적 회로 |

| KR100208632B1 (ko) * | 1995-10-31 | 1999-07-15 | 다카노 야스아키 | 반도체 집적 회로 및 그 제조 방법 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| SE427598B (sv) * | 1981-08-25 | 1983-04-18 | Ericsson Telefon Ab L M | Halvledardiod avsedd att inga i integrerade kretsar |

| JPS614459A (ja) * | 1984-06-18 | 1986-01-10 | Matsushita Electric Ind Co Ltd | ステツプモ−タ |

| CN1003334B (zh) * | 1985-04-19 | 1989-02-15 | 三洋电机株式会社 | 双极晶体管 |

| JPH06104459A (ja) | 1992-09-21 | 1994-04-15 | Sanken Electric Co Ltd | 半導体装置 |

| JPH1041488A (ja) * | 1996-07-19 | 1998-02-13 | Nec Corp | 回路内蔵受光素子 |

| US6365447B1 (en) * | 1998-01-12 | 2002-04-02 | National Semiconductor Corporation | High-voltage complementary bipolar and BiCMOS technology using double expitaxial growth |

| US6127723A (en) * | 1998-01-30 | 2000-10-03 | Sgs-Thomson Microelectronics, S.R.L. | Integrated device in an emitter-switching configuration |

-

2000

- 2000-12-25 JP JP2000392221A patent/JP4065104B2/ja not_active Expired - Fee Related

-

2001

- 2001-12-21 KR KR1020010082458A patent/KR100683100B1/ko not_active IP Right Cessation

- 2001-12-21 US US10/029,895 patent/US6590273B2/en not_active Expired - Lifetime

- 2001-12-25 CN CNB011338423A patent/CN100431153C/zh not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR0152155B1 (ko) * | 1994-03-31 | 1998-10-01 | 다까노 야스아끼 | 반도체 집적 회로 |

| KR100208632B1 (ko) * | 1995-10-31 | 1999-07-15 | 다카노 야스아키 | 반도체 집적 회로 및 그 제조 방법 |

Non-Patent Citations (2)

| Title |

|---|

| 1001521550000 * |

| 1002086320000 * |

Also Published As

| Publication number | Publication date |

|---|---|

| US6590273B2 (en) | 2003-07-08 |

| KR20020052954A (ko) | 2002-07-04 |

| CN1361552A (zh) | 2002-07-31 |

| JP2002198541A (ja) | 2002-07-12 |

| CN100431153C (zh) | 2008-11-05 |

| US20020079554A1 (en) | 2002-06-27 |

| JP4065104B2 (ja) | 2008-03-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100683100B1 (ko) | 반도체 집적 회로 장치 및 그 제조 방법 | |

| KR100683099B1 (ko) | 반도체 집적 회로 장치 및 그 제조 방법 | |

| KR100208632B1 (ko) | 반도체 집적 회로 및 그 제조 방법 | |

| CN103811486B (zh) | 保护装置以及相关制作方法 | |

| US9330961B2 (en) | Stacked protection devices and related fabrication methods | |

| JPH07297373A (ja) | 誘導性負荷要素に対する集積ドライバ回路装置 | |

| US9543420B2 (en) | Protection device and related fabrication methods | |

| US6815799B2 (en) | Semiconductor integrated circuit device | |

| JPH06104459A (ja) | 半導体装置 | |

| CN114188400A (zh) | 一种NPN功率SiGe双极晶体管及其制作方法 | |

| JP3909741B2 (ja) | 半導体集積回路の静電気保護装置およびそれを用いた静電気保護回路ならびにその製造方法 | |

| JP2001522540A (ja) | クロスカレント防止のための構造を有する半導体構成素子 | |

| US20040120085A1 (en) | Semiconductor device with surge protection circuit | |

| JP4822480B2 (ja) | 半導体集積回路装置およびその製造方法 | |

| JP3883681B2 (ja) | 半導体集積回路 | |

| US20120112291A1 (en) | Semiconductor Apparatus And Manufacturing Method Thereof | |

| JP3343892B2 (ja) | 半導体集積回路 | |

| JPH09116021A (ja) | 半導体集積回路とその製造方法 | |

| JP2527049B2 (ja) | 半導体装置の製造方法 | |

| KR100218263B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| JPH05109745A (ja) | 半導体装置 | |

| JPH0256935A (ja) | 半導体集積回路装置 | |

| JPH0629374A (ja) | 半導体集積回路装置 | |

| KR19990085651A (ko) | 반도체장치에서의 하나의 셀로 제조된 출력 증폭기 | |

| JPH05109748A (ja) | 半導体装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20120131 Year of fee payment: 6 |

|

| LAPS | Lapse due to unpaid annual fee |