JP6749427B2 - 高性能、フレキシブル、かつコンパクトな低密度パリティ検査(ldpc)コード - Google Patents

高性能、フレキシブル、かつコンパクトな低密度パリティ検査(ldpc)コード Download PDFInfo

- Publication number

- JP6749427B2 JP6749427B2 JP2018565065A JP2018565065A JP6749427B2 JP 6749427 B2 JP6749427 B2 JP 6749427B2 JP 2018565065 A JP2018565065 A JP 2018565065A JP 2018565065 A JP2018565065 A JP 2018565065A JP 6749427 B2 JP6749427 B2 JP 6749427B2

- Authority

- JP

- Japan

- Prior art keywords

- code

- graph

- family

- lifted

- range

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 230000005540 biological transmission Effects 0.000 claims description 101

- 238000004891 communication Methods 0.000 claims description 80

- 238000000034 method Methods 0.000 claims description 72

- 239000011159 matrix material Substances 0.000 claims description 68

- 238000003860 storage Methods 0.000 claims description 19

- 108091064702 1 family Proteins 0.000 claims description 2

- 238000013461 design Methods 0.000 description 30

- 238000010586 diagram Methods 0.000 description 23

- 238000005516 engineering process Methods 0.000 description 22

- 238000012545 processing Methods 0.000 description 21

- 125000004122 cyclic group Chemical group 0.000 description 18

- 238000005457 optimization Methods 0.000 description 17

- 238000004904 shortening Methods 0.000 description 16

- 230000006870 function Effects 0.000 description 14

- 235000019580 granularity Nutrition 0.000 description 14

- 230000008569 process Effects 0.000 description 11

- 238000012937 correction Methods 0.000 description 10

- 230000008901 benefit Effects 0.000 description 7

- 230000002829 reductive effect Effects 0.000 description 7

- 230000009471 action Effects 0.000 description 6

- 230000009897 systematic effect Effects 0.000 description 6

- 238000004590 computer program Methods 0.000 description 5

- 230000001186 cumulative effect Effects 0.000 description 5

- 238000009825 accumulation Methods 0.000 description 4

- 238000010276 construction Methods 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 230000006872 improvement Effects 0.000 description 4

- 238000000926 separation method Methods 0.000 description 4

- 238000001228 spectrum Methods 0.000 description 4

- 230000001360 synchronised effect Effects 0.000 description 4

- 230000002776 aggregation Effects 0.000 description 3

- 238000004220 aggregation Methods 0.000 description 3

- 230000001413 cellular effect Effects 0.000 description 3

- 230000001419 dependent effect Effects 0.000 description 3

- 239000000835 fiber Substances 0.000 description 3

- 230000002441 reversible effect Effects 0.000 description 3

- 238000012546 transfer Methods 0.000 description 3

- 238000013459 approach Methods 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 238000013500 data storage Methods 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 238000009826 distribution Methods 0.000 description 2

- 230000009977 dual effect Effects 0.000 description 2

- 230000000670 limiting effect Effects 0.000 description 2

- 230000007774 longterm Effects 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 230000008520 organization Effects 0.000 description 2

- 241000700159 Rattus Species 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 238000004458 analytical method Methods 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- 230000006399 behavior Effects 0.000 description 1

- 230000009286 beneficial effect Effects 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 238000012790 confirmation Methods 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 230000002452 interceptive effect Effects 0.000 description 1

- 238000012804 iterative process Methods 0.000 description 1

- 238000007726 management method Methods 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 230000003278 mimic effect Effects 0.000 description 1

- 238000010295 mobile communication Methods 0.000 description 1

- 238000005192 partition Methods 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 239000012782 phase change material Substances 0.000 description 1

- 238000002135 phase contrast microscopy Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000013468 resource allocation Methods 0.000 description 1

- 238000005549 size reduction Methods 0.000 description 1

- 239000004984 smart glass Substances 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- 208000011580 syndromic disease Diseases 0.000 description 1

- 238000011144 upstream manufacturing Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/033—Theoretical methods to calculate these checking codes

- H03M13/036—Heuristic code construction methods, i.e. code construction or code search based on using trial-and-error

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/11—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits using multiple parity bits

- H03M13/1102—Codes on graphs and decoding on graphs, e.g. low-density parity check [LDPC] codes

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/11—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits using multiple parity bits

- H03M13/1102—Codes on graphs and decoding on graphs, e.g. low-density parity check [LDPC] codes

- H03M13/1148—Structural properties of the code parity-check or generator matrix

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/11—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits using multiple parity bits

- H03M13/1102—Codes on graphs and decoding on graphs, e.g. low-density parity check [LDPC] codes

- H03M13/1148—Structural properties of the code parity-check or generator matrix

- H03M13/116—Quasi-cyclic LDPC [QC-LDPC] codes, i.e. the parity-check matrix being composed of permutation or circulant sub-matrices

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/61—Aspects and characteristics of methods and arrangements for error correction or error detection, not provided for otherwise

- H03M13/615—Use of computational or mathematical techniques

- H03M13/616—Matrix operations, especially for generator matrices or check matrices, e.g. column or row permutations

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/63—Joint error correction and other techniques

- H03M13/6306—Error control coding in combination with Automatic Repeat reQuest [ARQ] and diversity transmission, e.g. coding schemes for the multiple transmission of the same information or the transmission of incremental redundancy

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/63—Joint error correction and other techniques

- H03M13/635—Error control coding in combination with rate matching

- H03M13/6362—Error control coding in combination with rate matching by puncturing

- H03M13/6368—Error control coding in combination with rate matching by puncturing using rate compatible puncturing or complementary puncturing

- H03M13/6393—Rate compatible low-density parity check [LDPC] codes

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/65—Purpose and implementation aspects

- H03M13/6502—Reduction of hardware complexity or efficient processing

- H03M13/6505—Memory efficient implementations

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/65—Purpose and implementation aspects

- H03M13/6508—Flexibility, adaptability, parametrability and configurability of the implementation

- H03M13/6516—Support of multiple code parameters, e.g. generalized Reed-Solomon decoder for a variety of generator polynomials or Galois fields

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/0001—Systems modifying transmission characteristics according to link quality, e.g. power backoff

- H04L1/0009—Systems modifying transmission characteristics according to link quality, e.g. power backoff by adapting the channel coding

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0041—Arrangements at the transmitter end

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0056—Systems characterized by the type of code used

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0056—Systems characterized by the type of code used

- H04L1/0057—Block codes

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0056—Systems characterized by the type of code used

- H04L1/0057—Block codes

- H04L1/0058—Block-coded modulation

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0056—Systems characterized by the type of code used

- H04L1/0061—Error detection codes

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0056—Systems characterized by the type of code used

- H04L1/0067—Rate matching

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0056—Systems characterized by the type of code used

- H04L1/0067—Rate matching

- H04L1/0068—Rate matching by puncturing

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/12—Arrangements for detecting or preventing errors in the information received by using return channel

- H04L1/16—Arrangements for detecting or preventing errors in the information received by using return channel in which the return channel carries supervisory signals, e.g. repetition request signals

- H04L1/18—Automatic repetition systems, e.g. Van Duuren systems

- H04L1/1812—Hybrid protocols; Hybrid automatic repeat request [HARQ]

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/12—Arrangements for detecting or preventing errors in the information received by using return channel

- H04L1/16—Arrangements for detecting or preventing errors in the information received by using return channel in which the return channel carries supervisory signals, e.g. repetition request signals

- H04L1/18—Automatic repetition systems, e.g. Van Duuren systems

- H04L1/1812—Hybrid protocols; Hybrid automatic repeat request [HARQ]

- H04L1/1819—Hybrid protocols; Hybrid automatic repeat request [HARQ] with retransmission of additional or different redundancy

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Probability & Statistics with Applications (AREA)

- Theoretical Computer Science (AREA)

- Mathematical Physics (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- General Physics & Mathematics (AREA)

- Computational Mathematics (AREA)

- Mathematical Analysis (AREA)

- Mathematical Optimization (AREA)

- Pure & Applied Mathematics (AREA)

- Algebra (AREA)

- Computing Systems (AREA)

- Quality & Reliability (AREA)

- Mobile Radio Communication Systems (AREA)

- Error Detection And Correction (AREA)

- Detection And Prevention Of Errors In Transmission (AREA)

Description

本出願は、2016年6月14日に出願した、米国仮特許出願第62/349,784号(163764P1)、2016年8月12日に出願した、米国仮特許出願第62/374,514号(164403P1)、および2017年6月13日に出願した、米国特許出願第15/622,008号(164403)の利益および優先権を主張するものであり、それら3つの出願は全体が、すべての適用可能な目的のために参照により本明細書に組み込まれている。

など、他の世代ベースの通信システムにおいて適用できることに留意されたい。

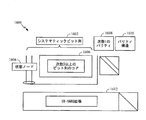

図1は、本開示の態様が実行される場合がある例示的なワイヤレス通信ネットワーク100を示す。ワイヤレス通信ネットワーク100は、ニューラジオ(NR)または5Gネットワークであり得る。ワイヤレス通信ネットワーク100は、ユーザ機器(UE)120または基地局(BS)110などの送信デバイスを含み得る。送信デバイスは、コードワードを生成するために低密度パリティ検査(LDPC)コードに基づいて情報ビットのセットを符号化することができ、LDPCコードは、第1の数の変数ノードおよび第2の数のチェックノードを有する行列によって定義される。送信デバイスによって使用されるLDPCコードは、高性能、フレキシブル、かつコンパクトなLDPCコードのための本明細書で説明するLDCコード設計に従って設計され得る。LDPCコード設計は、広範囲のコードレート、ブロック長、および粒度をサポートするために、情報ビットのセットを符号化するために送信デバイスによって使用され得る。

多くの通信システムは誤り訂正コードを使用する。具体的には、誤り訂正コードは、データストリーム内に冗長性を取り入れることによってこれらのシステム内の情報転送の固有の不信頼性を補償する。低密度パリティ検査(LDPC)コードは、反復コーディングシステムを使用する特定のタイプの誤り訂正コードである。具体的には、Gallagerコードは、「正規」LDPCコードの初期の例である。正規LDPCコードは、そのパリティチェック行列の要素Hの大部分が「0」である線形ブロックコードである。

本開示のいくつかの態様は、高性能を与え、フレキシブル、かつコンパクトな低密度パリティ検査(LDPC)コード設計を提供する。以下でより詳細に説明するように、LDPCコードは、ファインインクリメンタル冗長ハイブリッド自動再送要求(IR-HARQ)拡張が可能であり、良好なエラーフロア性能、高いスループット性能に対するハイレベルの並列性、および低い記述複雑性を維持しながら、広範囲のコードレート、ブロック長、および粒度のために使用され得る。

ワイヤレス通信システム(たとえば、ワイヤレス通信システム100)では、たとえば、使用されるべき様々な範囲のブロック長および/またはコードレートに対して、エラー訂正コード(たとえば、LDPCコード)のセットが使用され得る。記述の実装およびコンパクト性の点で効率を高めるために、コードのセットが関係づけられることが望ましい。

上記で説明したように、リフティングのクラスタ化されたセット(たとえば、リフティングの「タワー」)内のリフティングは、同じリフティング値(エッジ置換に関連する整数)を使用してよく、したがって、リフティングおよびリフティング値のすべてを指定するために使用されるビットの数を低減し得る。このサイズ低減は、LDPCコードのすべての記述を記憶するためのメモリの量を低減させることを可能にし得る。

上記で説明したように、リフティング値およびクラスタ化されたLDPCコードのセットに関するリフティングの大きな収集をコンパクトに記述すること(たとえば、表すこと/生成すること/判定すること/記憶すること)ができる。所与の基本グラフに関して、これは、大きな範囲のブロック長を取得するコンパクトな方法を提供する。しかしながら、多くの異なるコードレートをやはりサポートすることが望ましい場合があり、これは、多くの異なる基本グラフを必要とし得る。加えて、ブロック長の粒度は指数関数的である。実際に、ブロック長内のより細かな粒度が望ましい場合がある。パンクチャリングおよび短縮によって、より細かな粒度を達成することができ、したがって、コーディングシステムの高性能を確実にするために、パンクチャリングおよび/または短縮を考慮した適切なコード設計が望ましい場合がある。HARQ拡張(たとえば、IR-HARQ拡張)を用いてLDPCコードを設計することができる。したがって、基本グラフ構造は、HARQシーケンス内の第1の送信のために使用され得る最高レートから一部の最低サポートレートまでのコードレートの範囲をサポートし得る。

ブロック長において細かな粒度を提供するために、リフトされたLDPCコード内のリフティングの大きな収集をコンパクトに表し、リフティング値のセットで基本グラフを短縮するための技法について上記で説明している。

上記のセクションで説明したように、ブロック長の細かな粒度は、リフトされたベースパリティチェック行列(PCM)(基本グラフまたは基底行列とも呼ばれる)の短縮によって達成され得る。ハイブリッド自動再送要求(HARQ)拡張ビット(たとえば、IR-HARQ拡張)を基本グラフに追加することによって、より高いレートの基本グラフをより低いレートに拡張することができる。性能は、HARQ拡張のすべてのレベルにおいて達成され得る。したがって、単一の高レート基底行列から始めて、大規模なHARQ拡張を追加することによって、多くのコードレートおよびブロック長をカバーするLDPCコードを設計することが可能である。範囲[rmin,rmax]内のコードレートおよび範囲kb,minZ1≦K≦kb,maxZm内のブロック長をサポートし得る、HARQ拡張を含む、基本グラフ構造から生成されるLDPCコードは、コードのファミリーと呼ばれることがある。コードファミリー内のリフティングのセットは、上記で説明したように、クラスタ化されたリフティングのタワーであり得る。

上記のセクションで説明したように、2つ以上のLDPCファミリー(すなわち、短縮およびパンクチャリングを用いた複数のリフトされた基本グラフ)を使用するコーディング方式を使用することができ、ここで、所望の(開始)送信レート(および、他の要因)に応じて、送信されるべき情報を符号化するために異なるLDPCファミリーが使用され得る。

上記で説明したように、最終グラフまたは最終PCMを取得するために、コードのマクロ構造(すなわち、基本グラフ内の変数ノードおよびチェックノードの数ならびにそれらの接続)を記述する基本グラフをリフトすることによって、準巡回リフトされたLDPCコードを構築することができる。基本グラフは、基本グラフをZ回コピーして(すなわち、リフティングサイズ)、任意の置換によってそれらのコピーを相互接続することによってリフトされ得る。使用される置換は、リフト値をモジュロとする整数の巡回群からである。

D(x)=M(x)C(x)、

式中、M(x)は、mxnPCM(H)の平方mxm部分行列であり、C(x)は、パリティビットに対応するコードワードの部分であり、D(x)は、システマティックビットを使用して取得されるシンドロームである。たとえば、802.11nでは、次数3のパリティビットを使用して終了する次数2のパリティビットの累積チェーンが存在する。これは、以下に示す多項式行列によって表される。

前記のように、累積チェーン内の次数3のパリティビットに対する異なる巡回置換(すなわち、異なるリフティング値k)を使用して、ディープなエラーフロアを取得することができる。場合によっては、累積チェーンを用いて達成可能なエラーフロア挙動よりも一層ディープなエラーフロア挙動を達成することが望ましい場合がある。たとえば、累積チェーンは、追加のエッジを変数ノードに追加することによって、累積チェーン内の変数ノードのうちの1つまたは複数を次数3のノードにプロモートすることによって短縮され得る。追加のエッジは、単純な符号化を促す方法で追加され得る。

基本グラフを比較的小さく維持しながら、非常に高いレートコードを達成し、HARQ拡張をサポートしてレートをより低くするために、符号化構造内の次数2のノードのうちのいくつかをパンクチャリングすることによって、最高送信レートを達成することができる。以下の行列が802.11nタイプの符号化部分行列を表す場合、第1の列以外のパリティビットはパンクチャリングのための良好な候補である。

パリティを形成するために使用されるビットの配置数を選定するために密度展開を使用して、コアグラフのHARQ拡張のために形成されたパリティビットを設計することができる。密度展開は、構造の漸近的性能が最適化されるように選定を行う。具体的には、密度展開は、ループを伴わない無限に大きなグラフに関して動作していたかのように機能し得る。有限LDPCグラフはループを有し得る。これらのループは、様々な方法で性能を低下し得る。トラッピングセットまたはニアコードワードと呼ばれる、LDPCグラフ内の小さな構造は、エラーフロア故障イベントをもたらし得る。密度展開によって実行される最適化はトラッピングセットを考慮しない場合があるが、これは、トラッピングセットは有限グラフ内のループから生じるためである。結果として、HARQパリティビットの密度展開最適化は、エラーフロアを受けやすい状態にソリューションを残す可能性がある。

高性能、フレキシブル、かつコンパクトなLDPCコードのための本明細書で説明した符号化技法は、改善されたプロセッサ性能をもたらし得る。たとえば、これらの技法は、プロセッサが、(たとえば、少数のループを有する)良好なコードを使用して様々なブロック長およびコードレートの情報を効率的に符号化することを可能にし得る。たとえば、図1に示したBS110またはUE120内の処理システムなど、デバイスは、以前に知られていた態様に従ってコードワード符号化および/または復号するデバイスよりも、本開示の態様に従ってコードワードをより迅速にまたはより効率的に(たとえば、より少ない電力を消費して)符号化および/復号することができる。

102a マクロセル

102b マクロセル

102c マクロセル

102x ピコセル

102y フェムトセル

102z フェムトセル

110 BS、基地局(BS)

110a BS

110b BS

110c BS

110r 中継局

110x BS

110y BS

110z BS

120 UE、ユーザ機器(UE)

120r UE

120x UE

120y UE

130 ネットワークコントローラ

200 分散RAN

202 アクセスノードコントローラ(ANC)

204 次世代コアネットワーク(NG-CN)

206 5Gアクセスノード(AN)

208 TRP、DU

210 NG-AN

300 分散RAN

302 集中型コアネットワークユニット(C-CU)

304 集中型RANユニット(C-RU)

306 DU

412 データソース

420 送信プロセッサ

430 TX MIMOプロセッサ、送信(TX)多入力多出力(MIMO)プロセッサ

432 変調器

432a〜432t 復調器/変調器

434 アンテナ

434a〜434t アンテナ

436 MIMO検出器

438 受信プロセッサ

439 データシンク

440 コントローラ/プロセッサ

442 メモリ

444 スケジューラ

452a〜452r アンテナ

454 復調器

454a〜454r 復調器/変調器(DEMOD)

456 MIMO検出器

458 受信プロセッサ

460 データシンク

462 データソース

464 送信プロセッサ

466 TX MIMOプロセッサ

480 コントローラ/プロセッサ

482 メモリ

500 図

505-a 第1のオプション

505-b 第2のオプション

510 RRCレイヤ

515 PDCPレイヤ

520 RLCレイヤ

525 MACレイヤ

530 PHYレイヤ

600 DLセントリックサブフレーム

602 制御部分

604 DLデータ部分

606 通常のUL部分

700 ULセントリックサブフレーム

702 制御部分

704 ULデータ部分

706 通常のUL部分

800 2部グラフ

800A 行列表現

801 変数ノード

802 変数ノード

803 変数ノード

804 変数ノード

805 変数ノード

810 変数ノード

811 チェックノード

812 チェックノード

813 チェックノード

814 チェックノード

820 チェックノード

900 2部グラフ

1100 簡素化ブロック図、エンコーダ

1102 エンコーダ

1104 パンクチャリングモジュール

1106 マッパ

1108 Txチェーン

1110 アンテナ

1112 パンクチャリングパターン

1120 メッセージ

1122 符号化ビットストリーム、ビットストリーム、非パンクチャリングされたビットストリーム

1124 出力

1126 Txシンボル

1128 RF信号

1150 無線周波数(RF)モデム、モデム部分

1200 簡素化概略図

1202 アンテナ

1204 RFチェーン

1206 デマッパ

1208 畳み込みデコーダ、デコーダ

1210 パンクチャパターン

1220 RF信号

1222 シンボル、パンクチャリングされたビットストリーム

1224 ビットストリーム、デパンクチャリングされたビットストリーム

1226 復号メッセージ、メッセージ

1228 LLR

1250 RFモデム、モデム

1300 動作

1400 動作

1500 動作

1600 ベースPCM

1602 情報(システマティック)ビット列、情報ビット列

1604 状態(パンクチャリングされた)ノード

1606 コア構造、次数3以上のビット列のコア

1608 次数1のパリティビット

1610 パリティ構造

1612 IR-HARQ拡張

1700 基本グラフ

1702 状態ノード

1704 コア

1706 情報ビット列

1708 情報ビット列

1710 列、ビット列

1800 コア、表、基本グラフ

1800A グラフ

1900 グラフ

1900A 表

2000 グラフ

2000A 表

2200 表

2200A グラフ

2300 表

2300A グラフ

2400 動作

2500 動作

2600 コア

2700 コア

Claims (26)

- ワイヤレス通信のための方法であって、

選択回路によって、基本グラフのセットから第1の基本グラフを選択するステップであって、前記第1の基本グラフが、情報ビットに対応する変数ノードの列とパリティチェックに対応するチェックノードの行とを有するパリティチェック行列を定義し、基本グラフの前記セットが、リフトされた低密度パリティ検査(LDPC)コードのファミリーのセットに関連付けられ、前記第1の基本グラフが、送信コードレートの範囲での送信のための情報ビットを符号化するために、リフトされたLDPCコードのファミリーの前記セットのうちのリフトされたLDPCコードの第1のファミリーに関連付けられ、前記第1の基本グラフが、リフトされたLDPCコードの前記第1のファミリーによってサポートされるコードレートの範囲と送信コードレートの前記範囲との比較に基づいて選択される、ステップと、

符号化回路によって、1つまたは複数のコードワードを生成するために、送信コードレートの前記範囲における少なくとも1つの送信コードレートでの送信のために前記選択された第1の基本グラフに関連付けられたリフトされたLDPCコードの前記第1のファミリーからの少なくとも1つのリフトされたLDPCコードを使用して情報ビットを符号化するステップと、

アンテナに結合された送信機によって、前記1つまたは複数のコードワードを復号するための受信機に前記少なくとも1つの送信コードレートで媒体を介して前記1つまたは複数のコードワードを送信するステップと

を含み、

前記第1の基本グラフを選択するステップが、同一の送信コードレートをサポートする複数の基本グラフに関して、前記送信のブロック長のための最大リフティングサイズ値に関連付けられた前記基本グラフを選択するステップを含む、方法。 - リフトされたLDPCコードのファミリーの前記セットの各ファミリーが、基本グラフの前記セットのうちの異なる基本グラフに関連付けられる、請求項1に記載の方法。

- リフトされたLDPCコードのファミリーの前記セットの各ファミリーが、そのファミリーに関連付けられた前記基本グラフのクラスタ化されたリフティングのサイズ値のタワーに対応するLDPCコードを含み、クラスタ化されたリフティングのサイズ値の前記タワーが、クラスタ化されたリフティングのサイズ値の複数のセットを含み、クラスタ化されたリフティングのサイズ値の各セットが、互いの因数にリフティングサイズ値を含み、クラスタ化されたリフティングのサイズ値の前記複数のセットが指数関数的に離間する、請求項2に記載の方法。

- LDPCコードの前記ファミリーに関連付けられた前記異なる基本グラフが、完全なハイブリッド自動再送要求(HARQ)拡張においてほぼ等しい最大数のベース変数ノードを有する、請求項2に記載の方法。

- リフトされたLDPCコードの各ファミリーが、クラスタ化されたリフティングのサイズ値の前記タワーによってサポートされるブロック長の範囲とそのファミリーに関連付けられた前記基本グラフの拡張によってサポートされるコードレートの範囲とに対応するリフトされたLDPCコードのセットを含む、請求項3に記載の方法。

- サポートされるブロック長の前記範囲が、リフトされたLDPCコードの前記ファミリーに関連付けられたクラスタ化されたリフティングのサイズ値の前記セットによって定義され、

サポートされるコードレートの前記範囲が、リフトされたLDPCコードの前記ファミリーに関連付けられた前記基本グラフをパンクチャリングすることによって取得されるコアグラフに対応するリフトされたLDPCコードの前記ファミリーの前記コードレートおよびハイブリッド自動再送要求(HARQ)拡張ビットを前記基本グラフに追加することによって取得される拡張されたグラフに対応する最低コードレートによって定義される、

請求項5に記載の方法。 - 前記第1の基本グラフを選択するステップが、

送信コードレートの前記範囲の最高送信コードレートに最も近い前記コードレートをサポートする前記基本グラフを選択する、または、複数の基本グラフが前記コードレートをサポートしている場合には、より小さい基本グラフサイズを有する前記基本グラフを選択するステップ

を含む、請求項6に記載の方法。 - 前記少なくとも1つのリフトされたLDPCコードを使用して前記情報ビットを符号化するステップが、

送信コードレートの前記範囲における前記最高送信コードレートに関して、前記コードレートに対応する、リフトされたLDPCコードの前記第1のファミリーからの前記リフトされたLDPCコードを使用するステップと、

送信コードレートの前記範囲における他の送信コードレートに関して、前記選択された第1の基本グラフの前記拡張された基本グラフから取得されるより低いコードレートに対応する、リフトされたLDPCコードの前記第1のファミリーからのリフトされたLDPCコードを使用するステップと

を含む、請求項7に記載の方法。 - 前記選択回路によって、基本グラフの前記セットから第2の基本グラフを選択するステップであって、前記第2の基本グラフが、送信コードレートの別の範囲での送信のための他の情報ビットを符号化するために、リフトされたLDPCコードのファミリーの前記セットのうちのリフトされたLDPCコードの第2のファミリーに関連付けられ、前記第2の基本グラフが、リフトされたLDPCコードの前記第2のファミリーによってサポートされるコードレートの範囲と送信コードレートの前記別の範囲との比較に基づいて選択される、ステップをさらに含む、請求項1に記載の方法。

- ワイヤレス通信のための装置であって、

基本グラフのセットから第1の基本グラフを選択するための手段であって、前記第1の基本グラフが、情報ビットに対応する変数ノードの列とパリティチェックに対応するチェックノードの行とを有するパリティチェック行列を定義し、基本グラフの前記セットが、リフトされた低密度パリティ検査(LDPC)コードのファミリーのセットに関連付けられ、前記第1の基本グラフが、送信コードレートの範囲での送信のための情報ビットを符号化するために、リフトされたLDPCコードのファミリーの前記セットのうちのリフトされたLDPCコードの第1のファミリーに関連付けられ、前記第1の基本グラフが、リフトされたLDPCコードの前記第1のファミリーによってサポートされるコードレートの範囲と送信コードレートの前記範囲との比較に基づいて選択される、手段と、

1つまたは複数のコードワードを生成するために、送信コードレートの前記範囲における少なくとも1つの送信コードレートでの送信のために前記選択された第1の基本グラフに関連付けられたリフトされたLDPCコードの前記第1のファミリーからの少なくとも1つのリフトされたLDPCコードを使用して情報ビットを符号化するための手段と、

前記1つまたは複数のコードワードを復号するための受信機に前記少なくとも1つの送信コードレートで媒体を介して前記1つまたは複数のコードワードを送信するための手段と

を含み、

前記第1の基本グラフを選択するための手段が、同一の送信コードレートをサポートする複数の基本グラフに関して、前記送信のブロック長のための最大リフティングサイズ値に関連付けられた前記基本グラフを選択するための手段を含む、装置。 - リフトされたLDPCコードのファミリーの前記セットの各ファミリーが、基本グラフの前記セットのうちの異なる基本グラフに関連付けられる、請求項10に記載の装置。

- リフトされたLDPCコードのファミリーの前記セットの各ファミリーが、そのファミリーに関連付けられた前記基本グラフのクラスタ化されたリフティングのサイズ値のタワーに対応するLDPCコードを含み、クラスタ化されたリフティングのサイズ値の前記タワーが、クラスタ化されたリフティングのサイズ値の複数のセットを含み、クラスタ化されたリフティングのサイズ値の各セットが、互いの因数にリフティングサイズ値を含み、クラスタ化されたリフティングのサイズ値の前記複数のセットが指数関数的に離間する、請求項11に記載の装置。

- LDPCコードの前記ファミリーに関連付けられた前記異なる基本グラフが、完全なハイブリッド自動再送要求(HARQ)拡張においてほぼ等しい最大数のベース変数ノードを有する、請求項11に記載の装置。

- リフトされたLDPCコードの各ファミリーが、クラスタ化されたリフティングのサイズ値の前記タワーによってサポートされるブロック長の範囲とそのファミリーに関連付けられた前記基本グラフの拡張によってサポートされるコードレートの範囲とに対応するリフトされたLDPCコードのセットを含む、請求項12に記載の装置。

- サポートされるブロック長の前記範囲が、リフトされたLDPCコードの前記ファミリーに関連付けられたクラスタ化されたリフティングのサイズ値の前記セットによって定義され、

サポートされるコードレートの前記範囲が、リフトされたLDPCコードの前記ファミリーに関連付けられた前記基本グラフをパンクチャリングすることによって取得されるコアグラフに対応するリフトされたLDPCコードの前記ファミリーの前記コードレートおよびハイブリッド自動再送要求(HARQ)拡張ビットを前記基本グラフに追加することによって取得される拡張されたグラフに対応する最低コードレートによって定義される、

請求項14に記載の装置。 - 前記第1の基本グラフを選択するための手段が、

送信コードレートの前記範囲の最高送信コードレートに最も近い前記コードレートをサポートする前記基本グラフを選択する、または、複数の基本グラフが前記コードレートをサポートしている場合には、より小さい基本グラフサイズを有する前記基本グラフを選択するための手段

を含む、請求項15に記載の装置。 - 前記少なくとも1つのリフトされたLDPCコードを使用して前記情報ビットを符号化するための手段が、

送信コードレートの前記範囲における前記最高送信コードレートに関して、前記コードレートに対応する、リフトされたLDPCコードの前記第1のファミリーからの前記リフトされたLDPCコードを使用するための手段と、

送信コードレートの前記範囲における他の送信コードレートに関して、前記選択された第1の基本グラフの前記拡張された基本グラフから取得されるより低いコードレートに対応する、リフトされたLDPCコードの前記第1のファミリーからのリフトされたLDPCコードを使用するための手段と

を含む、請求項16に記載の装置。 - ワイヤレス通信のための装置であって、

メモリに結合された少なくとも1つのプロセッサであって、

基本グラフのセットから第1の基本グラフを選択することであって、前記第1の基本グラフが、情報ビットに対応する変数ノードの列とパリティチェックに対応するチェックノードの行とを有するパリティチェック行列を定義し、基本グラフの前記セットが、リフトされた低密度パリティ検査(LDPC)コードのファミリーのセットに関連付けられ、前記第1の基本グラフが、送信コードレートの範囲での送信のための情報ビットを符号化するために、リフトされたLDPCコードのファミリーの前記セットのうちのリフトされたLDPCコードの第1のファミリーに関連付けられ、前記第1の基本グラフが、リフトされたLDPCコードの前記第1のファミリーによってサポートされるコードレートの範囲と送信コードレートの前記範囲との比較に基づいて選択される、ことと、

1つまたは複数のコードワードを生成するために、送信コードレートの前記範囲における少なくとも1つの送信コードレートでの送信のために前記選択された第1の基本グラフに関連付けられたリフトされたLDPCコードの前記第1のファミリーからの少なくとも1つのリフトされたLDPCコードを使用して情報ビットを符号化することと

をするように構成された、少なくとも1つのプロセッサと、

前記1つまたは複数のコードワードを復号するための受信機に前記少なくとも1つの送信コードレートで媒体を介して前記1つまたは複数のコードワードを送信するように構成された送信機と

を含み、

前記少なくとも1つのプロセッサが、同一の送信コードレートをサポートする複数の基本グラフに関して、前記送信のブロック長のための最大リフティングサイズ値に関連付けられた前記基本グラフを選択することによって、前記第1の基本グラフを選択するように構成される、装置。 - リフトされたLDPCコードのファミリーの前記セットの各ファミリーが、基本グラフの前記セットのうちの異なる基本グラフに関連付けられる、請求項18に記載の装置。

- リフトされたLDPCコードのファミリーの前記セットの各ファミリーが、そのファミリーに関連付けられた前記基本グラフのクラスタ化されたリフティングのサイズ値のタワーに対応するLDPCコードを含み、クラスタ化されたリフティングのサイズ値の前記タワーが、クラスタ化されたリフティングのサイズ値の複数のセットを含み、クラスタ化されたリフティングのサイズ値の各セットが、互いの因数にリフティングサイズ値を含み、クラスタ化されたリフティングのサイズ値の前記複数のセットが指数関数的に離間する、請求項19に記載の装置。

- LDPCコードの前記ファミリーに関連付けられた前記異なる基本グラフが、完全なハイブリッド自動再送要求(HARQ)拡張においてほぼ等しい最大数のベース変数ノードを有する、請求項19に記載の装置。

- リフトされたLDPCコードの各ファミリーが、クラスタ化されたリフティングのサイズ値の前記タワーによってサポートされるブロック長の範囲とそのファミリーに関連付けられた前記基本グラフの拡張によってサポートされるコードレートの範囲とに対応するリフトされたLDPCコードのセットを含む、請求項20に記載の装置。

- 前記少なくとも1つのプロセッサが、

送信コードレートの前記範囲における最高送信コードレートに関して、前記コードレートに対応する、リフトされたLDPCコードの前記第1のファミリーからの前記リフトされたLDPCコードを使用し、

送信コードレートの前記範囲における他の送信コードレートに関して、前記選択された第1の基本グラフの拡張された基本グラフから取得されるより低いコードレートに対応する、リフトされたLDPCコードの前記第1のファミリーからのリフトされたLDPCコードを使用する

ことによって、前記情報ビットを符号化するように構成される、請求項18に記載の装置。 - ワイヤレス通信のためのコンピュータ実行可能コードを記憶したコンピュータ可読記憶媒体であって、前記コードが、

基本グラフのセットから第1の基本グラフを選択するためのコードであって、前記第1の基本グラフが、情報ビットに対応する変数ノードの列とパリティチェックに対応するチェックノードの行とを有するパリティチェック行列を定義し、基本グラフの前記セットが、リフトされた低密度パリティ検査(LDPC)コードのファミリーのセットに関連付けられ、前記第1の基本グラフが、送信コードレートの範囲での送信のための情報ビットを符号化するために、リフトされたLDPCコードのファミリーの前記セットのうちのリフトされたLDPCコードの第1のファミリーに関連付けられ、前記第1の基本グラフが、リフトされたLDPCコードの前記第1のファミリーによってサポートされるコードレートの範囲と送信コードレートの前記範囲との比較に基づいて選択される、コードと、

1つまたは複数のコードワードを生成するために、送信コードレートの前記範囲における少なくとも1つの送信コードレートでの送信のために前記選択された第1の基本グラフに関連付けられたリフトされたLDPCコードの前記第1のファミリーからの少なくとも1つのリフトされたLDPCコードを使用して情報ビットを符号化するためのコードと、

前記1つまたは複数のコードワードを復号するための受信機に前記少なくとも1つの送信コードレートで媒体を介して前記1つまたは複数のコードワードを送信するためのコードと

を含み、

前記第1の基本グラフを選択するためのコードが、同一の送信コードレートをサポートする複数の基本グラフに関して、前記送信のブロック長のための最大リフティングサイズ値に関連付けられた前記基本グラフを選択するためのコードを含む、コンピュータ可読記憶媒体。 - リフトされたLDPCコードのファミリーの前記セットの各ファミリーが、そのファミリーに関連付けられた前記基本グラフのクラスタ化されたリフティングのサイズ値のタワーに対応するLDPCコードを含み、クラスタ化されたリフティングのサイズ値の前記タワーが、クラスタ化されたリフティングのサイズ値の複数のセットを含み、クラスタ化されたリフティングのサイズ値の各セットが、互いの因数にリフティングサイズ値を含み、クラスタ化されたリフティングのサイズ値の前記複数のセットが指数関数的に離間する、請求項24に記載のコンピュータ可読記憶媒体。

- 送信コードレートの前記範囲における最高送信コードレートに関して、前記コードレートに対応する、リフトされたLDPCコードの前記第1のファミリーからの前記リフトされたLDPCコードを使用するためのコードと、

送信コードレートの前記範囲における他の送信コードレートに関して、前記選択された第1の基本グラフの拡張された基本グラフから取得されるより低いコードレートに対応する、リフトされたLDPCコードの前記第1のファミリーからのリフトされたLDPCコードを使用するためのコードと

をさらに含む、請求項24に記載のコンピュータ可読記憶媒体。

Applications Claiming Priority (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201662349784P | 2016-06-14 | 2016-06-14 | |

| US62/349,784 | 2016-06-14 | ||

| US201662374514P | 2016-08-12 | 2016-08-12 | |

| US62/374,514 | 2016-08-12 | ||

| US15/622,008 US10291354B2 (en) | 2016-06-14 | 2017-06-13 | High performance, flexible, and compact low-density parity-check (LDPC) code |

| US15/622,008 | 2017-06-13 | ||

| PCT/US2017/037465 WO2017218665A1 (en) | 2016-06-14 | 2017-06-14 | Lifted low-density parity check (ldpc) codes in combination with harq |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020092262A Division JP7050853B2 (ja) | 2016-06-14 | 2020-05-27 | 高性能、フレキシブル、かつコンパクトな低密度パリティ検査(ldpc)コード |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2019518385A JP2019518385A (ja) | 2019-06-27 |

| JP2019518385A5 JP2019518385A5 (ja) | 2019-08-08 |

| JP6749427B2 true JP6749427B2 (ja) | 2020-09-02 |

Family

ID=60573132

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018565065A Active JP6749427B2 (ja) | 2016-06-14 | 2017-06-14 | 高性能、フレキシブル、かつコンパクトな低密度パリティ検査(ldpc)コード |

| JP2020092262A Active JP7050853B2 (ja) | 2016-06-14 | 2020-05-27 | 高性能、フレキシブル、かつコンパクトな低密度パリティ検査(ldpc)コード |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020092262A Active JP7050853B2 (ja) | 2016-06-14 | 2020-05-27 | 高性能、フレキシブル、かつコンパクトな低密度パリティ検査(ldpc)コード |

Country Status (10)

| Country | Link |

|---|---|

| US (9) | US10469104B2 (ja) |

| EP (5) | EP3852276A1 (ja) |

| JP (2) | JP6749427B2 (ja) |

| CN (5) | CN109314525B (ja) |

| AU (2) | AU2017285198B2 (ja) |

| BR (2) | BR112018075015A2 (ja) |

| CA (4) | CA3022954C (ja) |

| SG (1) | SG11201809479PA (ja) |

| TW (3) | TWI688222B (ja) |

| WO (2) | WO2017218665A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2020145739A (ja) * | 2016-06-14 | 2020-09-10 | クアルコム,インコーポレイテッド | 高性能、フレキシブル、かつコンパクトな低密度パリティ検査(ldpc)コード |

Families Citing this family (46)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10784901B2 (en) | 2015-11-12 | 2020-09-22 | Qualcomm Incorporated | Puncturing for structured low density parity check (LDPC) codes |

| US10644839B2 (en) * | 2016-01-15 | 2020-05-05 | Avago Technologies International Sales Pte. Limited | Codeword puncturing for varying code rates |

| US10725860B2 (en) | 2016-03-04 | 2020-07-28 | Sandisk Technologies Llc | Storage system and method for handling a burst of errors |

| US10432232B2 (en) | 2016-03-04 | 2019-10-01 | Sandisk Technologies Llc | Multi-type parity bit generation for encoding and decoding |

| US11043966B2 (en) | 2016-05-11 | 2021-06-22 | Qualcomm Incorporated | Methods and apparatus for efficiently generating multiple lifted low-density parity-check (LDPC) codes |

| US10454499B2 (en) | 2016-05-12 | 2019-10-22 | Qualcomm Incorporated | Enhanced puncturing and low-density parity-check (LDPC) code structure |

| US9917675B2 (en) | 2016-06-01 | 2018-03-13 | Qualcomm Incorporated | Enhanced polar code constructions by strategic placement of CRC bits |

| US10313057B2 (en) | 2016-06-01 | 2019-06-04 | Qualcomm Incorporated | Error detection in wireless communications using sectional redundancy check information |

| KR102748333B1 (ko) * | 2016-07-13 | 2024-12-31 | 삼성전자 주식회사 | 무선 셀룰라 통신 시스템에서 이종 서비스간 공존 방법 및 장치 |

| US20210281359A1 (en) | 2016-07-27 | 2021-09-09 | Qualcomm Incorporated | Design of hybrid automatic repeat request (harq) feedback bits for polar codes |

| CN107734506B (zh) * | 2016-08-10 | 2023-12-08 | 华为技术有限公司 | 数据信道发送和接收方法、网络设备及终端 |

| CN107733554B (zh) * | 2016-08-11 | 2020-09-25 | 华为技术有限公司 | 极化码的速率匹配方法和装置 |

| RU2718161C1 (ru) * | 2016-08-12 | 2020-03-30 | Телефонактиеболагет Лм Эрикссон (Пабл) | Итеративное декодирование передач harq-ip на основе декодеров полярного кода с мягким выводом |

| EP3477865B1 (en) * | 2016-08-19 | 2021-07-28 | Huawei Technologies Co., Ltd. | Basis matrix generating method, coding/decoding method and apparatus for ldpc codes |

| WO2018129254A1 (en) * | 2017-01-06 | 2018-07-12 | Idac Holdings, Inc. | Advanced coding on retranmission of data and control |

| US10581457B2 (en) * | 2017-01-09 | 2020-03-03 | Mediatek Inc. | Shift coefficient and lifting factor design for NR LDPC code |

| CN109120276B (zh) | 2017-05-05 | 2019-08-13 | 华为技术有限公司 | 信息处理的方法、通信装置 |

| US10312939B2 (en) | 2017-06-10 | 2019-06-04 | Qualcomm Incorporated | Communication techniques involving pairwise orthogonality of adjacent rows in LPDC code |

| BR112019020158B1 (pt) | 2017-06-15 | 2022-02-08 | Huawei Technologies Co., Ltd | Método de codificação, método de decodificação, método de processamento de informações, aparelho, terminal, estação base, sistema de comunicação, mídia de armazenamento legível por computador e produto de programa de computador |

| CN118473422A (zh) * | 2017-06-27 | 2024-08-09 | 华为技术有限公司 | 信息处理的方法、装置和通信设备 |

| CN110677157B (zh) | 2017-06-27 | 2023-02-07 | 华为技术有限公司 | 信息处理的方法、装置和通信设备 |

| CN110832799B (zh) | 2017-07-07 | 2021-04-02 | 高通股份有限公司 | 应用低密度奇偶校验码基图选择的通信技术 |

| JP2019057806A (ja) * | 2017-09-20 | 2019-04-11 | 東芝メモリ株式会社 | メモリシステム |

| US11516782B2 (en) * | 2017-12-27 | 2022-11-29 | Ntt Docomo, Inc. | User terminal and radio communication method |

| CN108173628B (zh) * | 2018-01-09 | 2020-04-24 | 北京航空航天大学 | 一种基于高阶调制不等错误保护特性的极化码混合自动重传请求方法 |

| US10536879B2 (en) | 2018-02-16 | 2020-01-14 | At&T Intellectual Property I, L.P. | Redundancy version indication in fifth generation (5G) or other next generation communication systems |

| WO2019164515A1 (en) * | 2018-02-23 | 2019-08-29 | Nokia Technologies Oy | Ldpc codes for 3gpp nr ultra-reliable low-latency communications |

| US11032061B2 (en) * | 2018-04-27 | 2021-06-08 | Microsoft Technology Licensing, Llc | Enabling constant plaintext space in bootstrapping in fully homomorphic encryption |

| US10609573B2 (en) | 2018-05-08 | 2020-03-31 | Landis+Gyr Innovations, Inc. | Switching PANs while maintaining parent/child relationships |

| US10530638B2 (en) | 2018-05-08 | 2020-01-07 | Landis+ Gyr Innovations, Inc. | Managing connectivity for critical path nodes |

| US20190349277A1 (en) * | 2018-05-08 | 2019-11-14 | Landis+Gyr Innovations, Inc. | Information element to indicate loss of backhaul connection |

| US10582507B2 (en) | 2018-05-17 | 2020-03-03 | At&T Intellectual Property I, L.P. | Network coding for bandwidth efficient reliability improvement for URLLC service |

| WO2020042161A1 (en) * | 2018-08-31 | 2020-03-05 | Nokia Shanghai Bell Co., Ltd. | Incremental redundancy hybrid automatic repeat request transmissions for polar coded systems |

| CN109194338A (zh) * | 2018-11-07 | 2019-01-11 | 桂林电子科技大学 | 一种混合节点多比特处理的极化码译码方法 |

| US11777524B2 (en) * | 2019-04-22 | 2023-10-03 | Lg Electronics Inc. | Method for supporting rate-compatible non-binary LDPC code, and wireless terminal using same |

| US11438854B2 (en) * | 2019-06-20 | 2022-09-06 | Qualcomm Incorporated | Synchronization signal block configuration |

| WO2021010512A1 (ko) * | 2019-07-16 | 2021-01-21 | 엘지전자 주식회사 | 무선 통신 시스템에서 프로토그래프로부터 생성된 저밀도 패리티 검사 부호의 패리티 검사 행렬에 기초하여 부호화를 수행하는 방법 및 장치 |

| US12101797B2 (en) | 2019-07-18 | 2024-09-24 | Samsung Electronics Co., Ltd. | Methods and systems for use of carrier aggregation capability |

| CN112311402B (zh) * | 2019-07-31 | 2023-04-18 | 华为技术有限公司 | 编码方法、装置、设备及计算机可读存储介质 |

| US12119932B2 (en) * | 2020-01-10 | 2024-10-15 | California Institute Of Technology | Systems and methods for communicating using nested low density parity check codes |

| US11601946B2 (en) | 2020-02-05 | 2023-03-07 | Samsung Electronics Co., Ltd. | Multi-TRP and URLLC capability signaling |

| US11641253B2 (en) * | 2020-04-26 | 2023-05-02 | Nxp Usa, Inc. | Bandwidth indication, TXOP protection, and bandwidth negotiation |

| US11588704B2 (en) | 2021-03-08 | 2023-02-21 | International Business Machines Corporation | Broadband cellular network deployment fractal generation |

| US11637685B2 (en) | 2021-08-31 | 2023-04-25 | Samsung Display Co., Ltd. | System and method for transition encoding with flexible word-size |

| US12191884B2 (en) * | 2023-03-24 | 2025-01-07 | Qualcomm Incorporated | Extending low-density parity check (LDPC) codes for Wi-Fi |

| TWI852771B (zh) * | 2023-09-19 | 2024-08-11 | 慧榮科技股份有限公司 | 用來為主機裝置進行資料存取控制之方法、控制器、資料存取裝置以及電子裝置 |

Family Cites Families (278)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US1035582A (en) | 1912-03-14 | 1912-08-13 | George Halinka | Rail-fastener. |

| US5583500A (en) | 1993-02-10 | 1996-12-10 | Ricoh Corporation | Method and apparatus for parallel encoding and decoding of data |

| JPH07288479A (ja) | 1994-04-18 | 1995-10-31 | Nec Corp | 誤り訂正連接符号化方法及び装置 |

| US5844918A (en) | 1995-11-28 | 1998-12-01 | Sanyo Electric Co., Ltd. | Digital transmission/receiving method, digital communications method, and data receiving apparatus |

| EP1601109B1 (en) | 1997-07-30 | 2010-04-21 | Samsung Electronics Co., Ltd. | Adaptive channel encoding method and device |

| JP3152217B2 (ja) | 1998-10-09 | 2001-04-03 | 日本電気株式会社 | 有線伝送装置及び有線伝送方法 |

| US6438724B1 (en) | 1999-03-16 | 2002-08-20 | International Business Machines Corporation | Method and apparatus for deterministically altering cyclic redundancy check information for data storage |

| TW427076B (en) | 1999-04-06 | 2001-03-21 | Inst Information Industry | CRC key checking device and the method thereof |

| EP1232596A2 (de) | 1999-11-25 | 2002-08-21 | Siemens Aktiengesellschaft | Verfahren zur anpassung der datenrate in einer kommunikationsvorrichtung und entsprechende kommunikationsvorrichtung |

| US6633865B1 (en) | 1999-12-23 | 2003-10-14 | Pmc-Sierra Limited | Multithreaded address resolution system |

| US6931581B1 (en) | 2000-10-25 | 2005-08-16 | Sun Microsystems, Inc. | Method for superimposing a sequence number in an error detection code in a data network |

| US6961388B2 (en) | 2001-02-01 | 2005-11-01 | Qualcomm, Incorporated | Coding scheme for a wireless communication system |

| US7093179B2 (en) | 2001-03-22 | 2006-08-15 | University Of Florida | Method and coding means for error-correction utilizing concatenated parity and turbo codes |

| US6987778B2 (en) | 2001-05-22 | 2006-01-17 | Qualcomm Incorporated | Enhanced channel interleaving for optimized data throughput |

| US6633856B2 (en) * | 2001-06-15 | 2003-10-14 | Flarion Technologies, Inc. | Methods and apparatus for decoding LDPC codes |

| KR100762632B1 (ko) | 2001-10-17 | 2007-10-01 | 삼성전자주식회사 | 부호 분할 다중 접속 통신 시스템에서 전송 채널 다중화/역다중화 장치 및 방법 |

| US6854082B1 (en) | 2001-11-27 | 2005-02-08 | Lsi Logic Corporation | Unequal error protection Reed-Muller code generator and decoder |

| US7295555B2 (en) | 2002-03-08 | 2007-11-13 | Broadcom Corporation | System and method for identifying upper layer protocol message boundaries |

| US20060013181A1 (en) | 2002-07-31 | 2006-01-19 | Victor Stolpman | Apparatus, and associated method, for allocating communications in a multi-channel communication system |

| US7178080B2 (en) | 2002-08-15 | 2007-02-13 | Texas Instruments Incorporated | Hardware-efficient low density parity check code for digital communications |

| US6961888B2 (en) | 2002-08-20 | 2005-11-01 | Flarion Technologies, Inc. | Methods and apparatus for encoding LDPC codes |

| US7702986B2 (en) | 2002-11-18 | 2010-04-20 | Qualcomm Incorporated | Rate-compatible LDPC codes |

| US6957375B2 (en) | 2003-02-26 | 2005-10-18 | Flarion Technologies, Inc. | Method and apparatus for performing low-density parity-check (LDPC) code operations using a multi-level permutation |

| US7231557B2 (en) | 2003-04-02 | 2007-06-12 | Qualcomm Incorporated | Methods and apparatus for interleaving in a block-coherent communication system |

| US7036720B2 (en) | 2003-06-25 | 2006-05-02 | Centre National De La Recherche Scientifique (Cnrs) | Method and apparatus for resolution of problems using constrained discrete variables |

| US7222284B2 (en) | 2003-06-26 | 2007-05-22 | Nokia Corporation | Low-density parity-check codes for multiple code rates |

| WO2005015748A1 (en) | 2003-08-08 | 2005-02-17 | Intel Corporation | Method and apparatus for varying lengths of low density parity check codewords |

| KR100809619B1 (ko) | 2003-08-26 | 2008-03-05 | 삼성전자주식회사 | 이동 통신 시스템에서 블록 저밀도 패러티 검사 부호부호화/복호 장치 및 방법 |

| KR100955952B1 (ko) * | 2003-10-13 | 2010-05-19 | 삼성전자주식회사 | 무선 통신 시스템에서 리프팅 저밀도 패러티 검사 부호를이용한 시공간 부호화 방법 및 장치 |

| KR100918763B1 (ko) | 2003-11-14 | 2009-09-24 | 삼성전자주식회사 | 병렬 연접 저밀도 패리티 검사 부호를 사용하는 채널 부호화/복호 장치 및 방법 |

| US7237181B2 (en) | 2003-12-22 | 2007-06-26 | Qualcomm Incorporated | Methods and apparatus for reducing error floors in message passing decoders |

| EP1592137A1 (en) | 2004-04-28 | 2005-11-02 | Samsung Electronics Co., Ltd. | Apparatus and method for coding/decoding block low density parity check code with variable block length |

| KR20050118056A (ko) | 2004-05-12 | 2005-12-15 | 삼성전자주식회사 | 다양한 부호율을 갖는 Block LDPC 부호를 이용한이동 통신 시스템에서의 채널부호화 복호화 방법 및 장치 |

| KR100739510B1 (ko) | 2004-06-16 | 2007-07-13 | 포항공과대학교 산학협력단 | 반구조적 블록 저밀도 패리티 검사 부호 부호화/복호 장치및 방법 |

| US20050283707A1 (en) | 2004-06-22 | 2005-12-22 | Eran Sharon | LDPC decoder for decoding a low-density parity check (LDPC) codewords |

| CN101076946B (zh) | 2004-06-24 | 2012-05-30 | Lg电子株式会社 | 无线通信系统中使用低密度奇偶校验码编码和解码数据的方法和装置 |

| US7346832B2 (en) | 2004-07-21 | 2008-03-18 | Qualcomm Incorporated | LDPC encoding methods and apparatus |

| US7395490B2 (en) | 2004-07-21 | 2008-07-01 | Qualcomm Incorporated | LDPC decoding methods and apparatus |

| US7127659B2 (en) | 2004-08-02 | 2006-10-24 | Qualcomm Incorporated | Memory efficient LDPC decoding methods and apparatus |

| AU2005273169B2 (en) | 2004-08-16 | 2008-09-11 | Nokia Technologies Oy | Apparatus and method for coding/decoding block low density parity check code with variable block length |

| EP1641128A1 (en) | 2004-09-22 | 2006-03-29 | STMicroelectronics N.V. | Method and device for delivering punctured code words encoded with a LDPC code. |

| US7996746B2 (en) | 2004-10-12 | 2011-08-09 | Nortel Networks Limited | Structured low-density parity-check (LDPC) code |

| CN1780199A (zh) | 2004-11-17 | 2006-05-31 | 北京三星通信技术研究有限公司 | 判定数据包编码、译码方式的方法 |

| US7581159B2 (en) | 2004-11-23 | 2009-08-25 | Texas Instruments Incorporated | Simplified decoding using structured and punctured LDPC codes |

| US7543197B2 (en) | 2004-12-22 | 2009-06-02 | Qualcomm Incorporated | Pruned bit-reversal interleaver |

| US7571369B2 (en) | 2005-02-17 | 2009-08-04 | Samsung Electronics Co., Ltd. | Turbo decoder architecture for use in software-defined radio systems |

| US7685495B2 (en) | 2005-05-12 | 2010-03-23 | Qualcomm Incorporated | Apparatus and method for channel interleaving in communications system |

| RU2365035C1 (ru) | 2005-05-12 | 2009-08-20 | Квэлкомм Инкорпорейтед | Устройство и способ для перемежения канала в системе связи |

| KR101157246B1 (ko) | 2005-05-16 | 2012-06-15 | 삼성전자주식회사 | 저밀도 패리티 검사 부호의 패딩 및 천공 방법 |

| US7630350B2 (en) | 2005-06-06 | 2009-12-08 | Broadcom Corporation | Method and system for parsing bits in an interleaver for adaptive modulations in a multiple input multiple output (MIMO) wireless local area network (WLAN) system |

| US7571372B1 (en) | 2005-06-23 | 2009-08-04 | Marvell International Ltd. | Methods and algorithms for joint channel-code decoding of linear block codes |

| US7343539B2 (en) | 2005-06-24 | 2008-03-11 | The United States Of America As Represented By The United States National Aeronautics And Space Administration | ARA type protograph codes |

| WO2007001204A1 (en) | 2005-06-29 | 2007-01-04 | Intel Corporation | Wireless data transmission methods, devices, and systems |

| US7783961B2 (en) | 2005-07-01 | 2010-08-24 | Nec Laboratories America, Inc. | Rate-compatible low density parity check coding for hybrid ARQ |

| CN1893342B (zh) | 2005-07-05 | 2010-06-09 | 上海原动力通信科技有限公司 | 多载波hsdpa的业务传输信道编码方法和编码装置 |

| KR100856235B1 (ko) | 2005-09-26 | 2008-09-03 | 삼성전자주식회사 | 가변 부호화율을 가지는 블록 저밀도 패리티 검사 부호부호화/복호 장치 및 방법 |

| KR100943623B1 (ko) | 2005-09-30 | 2010-02-24 | 삼성전자주식회사 | 저밀도 패러티 검사 부호의 천공기법 |

| CN100502245C (zh) | 2005-10-21 | 2009-06-17 | 中兴通讯股份有限公司 | 支持任何码率/码长的低密度奇偶校验码编码装置和方法 |

| KR100929079B1 (ko) | 2005-10-31 | 2009-11-30 | 삼성전자주식회사 | 저밀도 패리티 검사 부호를 사용하는 통신 시스템의 복호 장치 및 방법 |

| KR100966043B1 (ko) | 2005-10-31 | 2010-06-25 | 삼성전자주식회사 | 저밀도 패리티 검사 부호를 사용하는 통신 시스템에서 신호 송수신 장치 및 방법 |

| TWI303414B (en) | 2005-12-21 | 2008-11-21 | Ind Tech Res Inst | A data encoding method for error correcton |

| US8132072B2 (en) | 2006-01-06 | 2012-03-06 | Qualcomm Incorporated | System and method for providing H-ARQ rate compatible codes for high throughput applications |

| US7979784B2 (en) | 2006-03-29 | 2011-07-12 | Samsung Electronics Co., Ltd. | Method and system for enhancing transmission reliability of video information over wireless channels |

| CN100546205C (zh) * | 2006-04-29 | 2009-09-30 | 北京泰美世纪科技有限公司 | 构造低密度奇偶校验码的方法、译码方法及其传输系统 |

| KR101119111B1 (ko) | 2006-05-04 | 2012-03-16 | 엘지전자 주식회사 | Ldpc 부호를 이용한 데이터 재전송 방법 |

| KR101191196B1 (ko) | 2006-06-07 | 2012-10-15 | 엘지전자 주식회사 | 패리티 검사 행렬을 이용하여 부호화 및 복호화하는 방법 |

| KR100834650B1 (ko) | 2006-09-04 | 2008-06-02 | 삼성전자주식회사 | 통신 시스템에서 신호 송수신 장치 및 방법 |

| US7797464B2 (en) | 2006-09-08 | 2010-09-14 | Ciena Corporation | Configuring data transmission over one or more line cards globally or individually |

| US7840880B1 (en) | 2006-09-25 | 2010-11-23 | Altera Corporation | Methods and apparatus for error checking code computation |

| US8464120B2 (en) * | 2006-10-18 | 2013-06-11 | Panasonic Corporation | Method and system for data transmission in a multiple input multiple output (MIMO) system including unbalanced lifting of a parity check matrix prior to encoding input data streams |

| US7986622B2 (en) | 2006-10-24 | 2011-07-26 | Broadcom Corporation | Method and system for physical layer aggregation |

| US8892979B2 (en) | 2006-10-26 | 2014-11-18 | Qualcomm Incorporated | Coding schemes for wireless communication transmissions |

| RU2426241C2 (ru) | 2006-10-26 | 2011-08-10 | Квэлкомм Инкорпорейтед | Схемы кодирования для передач беспроводной связи |

| KR100981501B1 (ko) | 2006-11-06 | 2010-09-10 | 연세대학교 산학협력단 | 통신 시스템에서 신호 송신 장치 및 방법 |

| US8086929B2 (en) | 2006-11-17 | 2011-12-27 | Lg Electronics Inc. | Method of executing LDPC coding using parity check matrix |

| KR100833515B1 (ko) | 2006-12-05 | 2008-05-29 | 한국전자통신연구원 | 가변 정보 길이 및 가변 부호율을 가진 ldpc 부호의패리티 검사 행렬 생성 방법, 부/복호화 방법 및 이를이용하는 장치 |

| CN101217337B (zh) * | 2007-01-01 | 2013-01-23 | 中兴通讯股份有限公司 | 一种支持递增冗余混合自动重传的低密度奇偶校验码编码装置和方法 |

| TW201334425A (zh) * | 2007-01-24 | 2013-08-16 | Qualcomm Inc | 可變大小之封包的低密度同位檢查編碼與解碼 |

| US20100107033A1 (en) | 2007-01-31 | 2010-04-29 | Kenichi Kuri | Radio communication device and puncturing method |

| KR20080077473A (ko) | 2007-02-20 | 2008-08-25 | 엘지전자 주식회사 | 디지털 방송 시스템 및 데이터 처리 방법 |

| US7861134B2 (en) | 2007-02-28 | 2010-12-28 | Cenk Kose | Methods and systems for LDPC coding |

| US8261155B2 (en) | 2007-03-09 | 2012-09-04 | Qualcomm Incorporated | Methods and apparatus for encoding and decoding low density parity check (LDPC) codes |

| CN101047387B (zh) | 2007-03-23 | 2010-06-09 | 北京大学 | 一种多码率兼容ldpc码的构造方法及其译码器 |

| KR101285887B1 (ko) | 2007-03-26 | 2013-07-11 | 엘지전자 주식회사 | 디지털 방송 시스템 및 데이터 처리 방법 |

| KR101253185B1 (ko) | 2007-03-26 | 2013-04-10 | 엘지전자 주식회사 | 디지털 방송 시스템 및 데이터 처리 방법 |

| US7912028B2 (en) | 2007-05-31 | 2011-03-22 | Agere Systems Inc. | Reducing false detection in an HSDPA 3G terminal |

| KR101524869B1 (ko) | 2007-06-04 | 2015-06-02 | 삼성전자주식회사 | 저밀도 패리티 검사 부호의 부호화 및 복호화 장치 및 방법 |

| WO2008151516A1 (fr) | 2007-06-08 | 2008-12-18 | Datang Mobile Communications Equipment Co., Ltd | Procédé, équipement et système pour codage et décodage ldpc |

| CN101325474B (zh) | 2007-06-12 | 2012-05-09 | 中兴通讯股份有限公司 | Ldpc码的混合自动请求重传的信道编码及调制映射方法 |

| CN101682381B (zh) | 2007-06-15 | 2013-06-05 | 松下电器产业株式会社 | 无线通信装置、无线通信系统以及无线通信方法 |

| US7890834B2 (en) | 2007-06-20 | 2011-02-15 | Motorola Mobility, Inc. | Apparatus comprising a circular buffer and method for assigning redundancy versions to a circular buffer |

| KR101461958B1 (ko) | 2007-06-29 | 2014-11-14 | 엘지전자 주식회사 | 디지털 방송 시스템 및 데이터 처리 방법 |

| JP5354979B2 (ja) | 2007-07-12 | 2013-11-27 | パナソニック株式会社 | 低密度パリティ検査畳み込み符号(ldpc−cc)符号化器及びldpc−cc復号器 |

| WO2009011134A1 (ja) | 2007-07-19 | 2009-01-22 | Panasonic Corporation | 無線通信装置およびldpc符号化における通信リソース配置方法 |

| US20110096862A1 (en) | 2007-08-09 | 2011-04-28 | Panasonic Corporation | Radio communication apparatus, radio communication system, and radio communication method |

| BRPI0815159B1 (pt) | 2007-08-14 | 2020-09-08 | Lg Electronics, Inc. | Método de transmissão dados em sistema de acesso sem fio |

| EP2026470A1 (en) | 2007-08-17 | 2009-02-18 | Panasonic Corporation | Running cyclic redundancy check over coding segments |

| KR100928261B1 (ko) | 2007-09-08 | 2009-11-24 | 엘지전자 주식회사 | 비검출 오류 저감을 위한 신호 분할 및 crc 부착 방법 |

| US8555148B2 (en) | 2007-09-18 | 2013-10-08 | Samsung Electronics Co., Ltd. | Methods and apparatus to generate multiple CRCs |

| US20090077457A1 (en) | 2007-09-19 | 2009-03-19 | Rajaram Ramesh | Iterative decoding of blocks with cyclic redundancy checks |

| JP2009081577A (ja) | 2007-09-25 | 2009-04-16 | Samsung Electronics Co Ltd | 受信装置、通信システム、及び信号処理方法 |

| WO2009041034A1 (ja) | 2007-09-27 | 2009-04-02 | Panasonic Corporation | 無線通信装置、無線通信システム及び無線通信方法 |

| CN101141133B (zh) | 2007-10-23 | 2011-09-14 | 北京邮电大学 | 一种结构化低密度校验码的编码方法 |

| US20090113256A1 (en) | 2007-10-24 | 2009-04-30 | Nokia Corporation | Method, computer program product, apparatus and device providing scalable structured high throughput LDPC decoding |

| US8219876B2 (en) | 2007-10-24 | 2012-07-10 | Core Wireless Licensing, S.a.r.l. | Method, apparatus, computer program product and device providing semi-parallel low density parity check decoding using a block structured parity check matrix |

| PL2056510T3 (pl) | 2007-10-30 | 2013-08-30 | Sony Corp | Urządzenie i sposób przetwarzania danych |

| WO2009064439A2 (en) | 2007-11-12 | 2009-05-22 | Solarflare Communications, Inc. | Active idle communication system |

| PL2381583T3 (pl) | 2007-12-06 | 2013-09-30 | Samsung Electronics Co Ltd | Sposób i urządzenie do dekodowania kanałowego w systemie telekomunikacyjnym z wykorzystaniem kodów kontroli parzystości o niskiej gęstości |

| CN101188428B (zh) | 2007-12-10 | 2012-09-05 | 中兴通讯股份有限公司 | 一种ldpc码的有限长度循环缓存的速率匹配方法 |

| KR101502623B1 (ko) * | 2008-02-11 | 2015-03-16 | 삼성전자주식회사 | 저밀도 패리티 검사 부호를 사용하는 통신 시스템에서 채널부호/복호 방법 및 장치 |

| KR101445080B1 (ko) | 2008-02-12 | 2014-09-29 | 삼성전자 주식회사 | 하이브리드 자동 반복 요구 방식을 사용하는 통신 시스템에서 신호 송신 방법 및 장치 |

| KR101503058B1 (ko) | 2008-02-26 | 2015-03-18 | 삼성전자주식회사 | 저밀도 패리티 검사 부호를 사용하는 통신 시스템에서의 채널 부호화/복호화 방법 및 장치 |

| KR101503059B1 (ko) | 2008-02-26 | 2015-03-19 | 삼성전자주식회사 | 저밀도 패리티 검사 부호를 사용하는 통신 시스템에서 채널 부호/복호 방법 및 장치 |

| CN101572554B (zh) | 2008-05-04 | 2013-04-24 | 华为技术有限公司 | 生成码率兼容ldpc码及harq方案的方法及装置 |

| US20090300461A1 (en) | 2008-05-29 | 2009-12-03 | Gadi Shor | Device, method and computer program product for communication |

| EP2299602A1 (en) | 2008-07-09 | 2011-03-23 | Sharp Kabushiki Kaisha | Communication device, communication system, reception method, and communication method |

| CN101645763B (zh) | 2008-08-06 | 2013-05-08 | 中兴通讯股份有限公司 | 一种用于上行数据发送的调度方法及上行调度系统 |

| US20110161772A1 (en) | 2008-09-02 | 2011-06-30 | Panasonic Corporation | Wireless communication device and wireless communication method |

| KR20100058260A (ko) | 2008-11-24 | 2010-06-03 | 삼성전자주식회사 | 저밀도 패리티 검사 부호를 사용하는 통신 시스템에서 채널부호/복호 장치 및 방법 |

| US20100153819A1 (en) | 2008-12-12 | 2010-06-17 | Yeong-Luh Ueng | Decoding Method and System for Low-Density Parity Check Code |

| US8347199B2 (en) | 2009-01-21 | 2013-01-01 | Cisco Technology, Inc. | Enhanced error detection in multilink serdes channels |

| US8433972B2 (en) * | 2009-04-06 | 2013-04-30 | Nec Laboratories America, Inc. | Systems and methods for constructing the base matrix of quasi-cyclic low-density parity-check codes |

| EP2244387A1 (en) | 2009-04-23 | 2010-10-27 | Georgia Tech Research Corporation | Method and transmitter for use in secure communication using error correction codes |

| US8245097B2 (en) | 2009-04-27 | 2012-08-14 | Kan Ling Capital, L.L.C. | Iterative decoding of punctured low-density parity check codes by selection of decoding matrices |

| US8352846B2 (en) | 2009-05-07 | 2013-01-08 | Adeptence, Llc | Method an apparatus for low density parity check codes encoding and decoding |

| US8392789B2 (en) | 2009-07-28 | 2013-03-05 | Texas Instruments Incorporated | Method and system for decoding low density parity check codes |

| WO2011014685A2 (en) | 2009-07-29 | 2011-02-03 | Marvell World Trade Ltd. | Methods and apparatus for wlan transmission |

| US8601352B1 (en) | 2009-07-30 | 2013-12-03 | Apple Inc. | Efficient LDPC codes |

| US8495450B2 (en) | 2009-08-24 | 2013-07-23 | Samsung Electronics Co., Ltd. | System and method for structured LDPC code family with fixed code length and no puncturing |

| US8560911B2 (en) | 2009-09-14 | 2013-10-15 | Samsung Electronics Co., Ltd. | System and method for structured LDPC code family |

| US8402341B2 (en) * | 2010-02-18 | 2013-03-19 | Mustafa Eroz | Method and system for providing low density parity check (LDPC) encoding and decoding |

| JP5073770B2 (ja) | 2010-02-19 | 2012-11-14 | 株式会社エヌ・ティ・ティ・ドコモ | 移動端末装置、無線基地局装置及び無線通信方法 |

| US8687751B1 (en) | 2010-04-02 | 2014-04-01 | Marvell International Ltd. | Multiple-input multiple-output receivers using successive interference cancellation based on cyclic redundancy check |

| CN101826878A (zh) * | 2010-04-26 | 2010-09-08 | 杨磊 | Qc-ldpc码构建方法 |

| US8601345B1 (en) | 2010-05-12 | 2013-12-03 | Tellabs Operations, Inc. | Method and apparatus for searching frame alignment with false alignment protection |

| US9634693B2 (en) | 2010-08-12 | 2017-04-25 | Samsung Electronics Co., Ltd | Apparatus and method for decoding LDPC codes in a communications system |

| US8650457B1 (en) | 2010-09-03 | 2014-02-11 | Marvell International Ltd. | Methods and systems for reconfigurable LDPC decoders |

| US8473821B2 (en) | 2010-11-09 | 2013-06-25 | Qualcomm, Incorporated | Packet-level erasure protection coding in aggregated packet transmissions |

| KR101611169B1 (ko) | 2011-01-18 | 2016-04-11 | 삼성전자주식회사 | 통신/방송 시스템에서 데이터 송수신 장치 및 방법 |

| US8627166B2 (en) | 2011-03-16 | 2014-01-07 | Samsung Electronics Co., Ltd. | LDPC code family for millimeter-wave band communications in a wireless network |

| EP2518923A1 (en) | 2011-04-26 | 2012-10-31 | Panasonic Corporation | Bit permutation patterns for BICM with LDPC codes of rate 2/5 and QAM constellations |

| EP2525495A1 (en) | 2011-05-18 | 2012-11-21 | Panasonic Corporation | Bit-interleaved coding and modulation (BICM) with quasi-cyclic LDPC codes |

| CN103188044A (zh) | 2011-05-19 | 2013-07-03 | 北京新岸线移动多媒体技术有限公司 | 一种用于数据传输的方法和设备 |

| KR20120137198A (ko) * | 2011-06-11 | 2012-12-20 | 삼성전자주식회사 | 통신 시스템에서 패킷 송수신 장치 및 방법 |

| US8566667B2 (en) | 2011-07-29 | 2013-10-22 | Stec, Inc. | Low density parity check code decoding system and method |

| KR101942530B1 (ko) | 2011-08-22 | 2019-01-25 | 삼성전자 주식회사 | 오류정정부호 기반 암호화 시스템의 성능 개선 방법 및 장치 |

| CN102437858B (zh) | 2011-08-31 | 2013-11-06 | 北京理工大学 | 一种卷积码编码器结构的改进方法 |

| US8595589B2 (en) | 2011-09-30 | 2013-11-26 | Mitsubishi Electric Research Laboratories, Inc. | Quasi-cyclic low-density parity-check codes |

| CN102340378A (zh) | 2011-10-23 | 2012-02-01 | 许继集团有限公司 | 纵联保护用光纤通道crc校验方法 |

| US9176927B2 (en) | 2011-11-08 | 2015-11-03 | The Royal Institution For The Advancement Of Learning/Mcgill University | Methods and systems for decoding polar codes |

| CN103220001B (zh) | 2012-01-20 | 2016-09-07 | 华为技术有限公司 | 与循环冗余校验级联的极性码的译码方法和译码装置 |

| CN102571105B (zh) | 2012-02-24 | 2014-03-12 | 西安电子科技大学 | 一种逼近信道容量的码率可变ldpc码的编码方法 |

| US9124872B2 (en) | 2012-04-16 | 2015-09-01 | Qualcomm Incorporated | Coefficient groups and coefficient coding for coefficient scans |

| US9088769B2 (en) | 2012-06-28 | 2015-07-21 | Blackberry Limited | Reduced worst-case context-coded bins in video compression with parity hiding |

| US9503126B2 (en) | 2012-07-11 | 2016-11-22 | The Regents Of The University Of California | ECC polar coding and list decoding methods and codecs |

| US9454552B2 (en) | 2012-07-31 | 2016-09-27 | Empire Technology Development Llc | Entropy coding and decoding using polar codes |

| US8972834B2 (en) | 2012-08-28 | 2015-03-03 | Hughes Network Systems, Llc | System and method for communicating with low density parity check codes |

| US9503513B2 (en) | 2012-10-08 | 2016-11-22 | International Business Machines Corporation | Robust transmission of data utilizing encoded data slices |

| CN108712231B (zh) | 2012-10-17 | 2019-04-19 | 华为技术有限公司 | 一种编译码的方法、装置及系统 |

| CN107659384A (zh) | 2012-11-16 | 2018-02-02 | 华为技术有限公司 | 数据处理的方法和装置 |

| US9191256B2 (en) | 2012-12-03 | 2015-11-17 | Digital PowerRadio, LLC | Systems and methods for advanced iterative decoding and channel estimation of concatenated coding systems |

| KR101951663B1 (ko) | 2012-12-14 | 2019-02-25 | 삼성전자주식회사 | Crc 부호와 극 부호에 의한 부호화 방법 및 장치 |

| KR102007770B1 (ko) | 2012-12-14 | 2019-08-06 | 삼성전자주식회사 | 패킷의 부호화 방법과 그 복호화 장치 및 방법 |

| US9178653B2 (en) | 2013-01-16 | 2015-11-03 | Broadcom Corporation | Very short size LDPC coding for physical and/or control channel signaling |

| US9362956B2 (en) | 2013-01-23 | 2016-06-07 | Samsung Electronics Co., Ltd. | Method and system for encoding and decoding data using concatenated polar codes |

| US9946475B2 (en) | 2013-01-24 | 2018-04-17 | California Institute Of Technology | Joint rewriting and error correction in write-once memories |

| CN103152056B (zh) | 2013-01-30 | 2016-05-25 | 北京大学 | 一种基于原模图的准循环ldpc码构造方法及装置 |

| EP2951925B1 (en) | 2013-01-31 | 2020-07-15 | Intracom S.A. Telecom Solutions | Ldpc code design and encoding apparatus enabling the adjustment of code rate and codelength |

| US9100052B2 (en) | 2013-02-01 | 2015-08-04 | Samsung Electronics Co., Ltd. | QC-LDPC convolutional codes enabling low power trellis-based decoders |

| US20140229788A1 (en) | 2013-02-13 | 2014-08-14 | Qualcomm Incorporated | Ldpc design for high rate, high parallelism, and low error floor |

| CN104038234B (zh) | 2013-03-07 | 2017-09-29 | 华为技术有限公司 | 极性码的译码方法和译码器 |

| US9197385B2 (en) | 2013-03-28 | 2015-11-24 | Sharp Laboratories Of America, Inc. | Systems and methods for demodulation reference signal selection |

| RU2656726C2 (ru) | 2013-05-02 | 2018-06-06 | Сони Корпорейшн | Устройство обработки данных и способ обработки данных |

| CN103281166B (zh) | 2013-05-15 | 2016-05-25 | 北京邮电大学 | 一种基于极化码的混合自动重传请求传输方法 |

| US9432143B2 (en) | 2013-06-06 | 2016-08-30 | Broadcom Corporation | Combining CRC and FEC on a variable number of NCPs |

| US9379848B2 (en) | 2013-06-10 | 2016-06-28 | Broadcom Corporation | Cyclic redundancy check (CRC) and forward error correction (FEC) for ranging within communication systems |

| KR102104937B1 (ko) | 2013-06-14 | 2020-04-27 | 삼성전자주식회사 | Ldpc 부호의 부호화 장치, 그의 부호화 방법, 복호화 장치 및 그의 복호화 방법 |

| TW201519596A (zh) | 2013-07-11 | 2015-05-16 | Interdigital Patent Holdings | 智慧HARQ WiFi系統及方法 |

| KR102019893B1 (ko) | 2013-07-22 | 2019-09-09 | 삼성전자주식회사 | 저밀도 패리티 검사 부호를 지원하는 통신 시스템에서 신호 수신 장치 및 방법 |

| EP3028452A4 (en) | 2013-08-01 | 2017-04-05 | LG Electronics Inc. | Apparatus for transmitting broadcast signals, apparatus for receiving broadcast signals, method for transmitting broadcast signals and method for receiving broadcast signals |

| US9872052B2 (en) | 2013-08-01 | 2018-01-16 | Lg Electronics Inc. | Apparatus for transmitting broadcast signals, apparatus for receiving broadcast signals, method for transmitting broadcast signals and method for receiving broadcast signals |

| WO2015041074A1 (ja) | 2013-09-20 | 2015-03-26 | ソニー株式会社 | データ処理装置、及びデータ処理方法 |

| KR102223056B1 (ko) | 2013-09-26 | 2021-03-05 | 삼성전자주식회사 | 송수신 장치 및 그의 신호 처리 방법 |

| US10075266B2 (en) | 2013-10-09 | 2018-09-11 | Qualcomm Incorporated | Data transmission scheme with unequal code block sizes |

| CN103746708A (zh) | 2013-10-25 | 2014-04-23 | 中国农业大学 | 一种Polar-LDPC级联码的构造方法 |

| KR102218196B1 (ko) | 2013-10-28 | 2021-02-23 | 삼성전자주식회사 | 인코더, 이의 동작 방법과, 상기 인코더를 포함하는 장치들 |

| US9787470B2 (en) | 2013-12-12 | 2017-10-10 | Samsung Electronics Co., Ltd. | Method and apparatus of joint security advanced LDPC cryptcoding |

| US9602241B2 (en) | 2013-12-17 | 2017-03-21 | Samsung Electronics Co., Ltd. | Computing system with polar processing mechanism and method of operation thereof |

| US9262268B2 (en) | 2013-12-20 | 2016-02-16 | Seagate Technology Llc | Method to distribute user data and error correction data over different page types by leveraging error rate variations |

| CN103716130A (zh) | 2014-01-09 | 2014-04-09 | 苏州英菲泰尔电子科技有限公司 | 提高网络传输可靠性的物理层自适应处理方法 |

| US20160012465A1 (en) | 2014-02-08 | 2016-01-14 | Jeffrey A. Sharp | System and method for distributing, receiving, and using funds or credits and apparatus thereof |

| US9319073B2 (en) | 2014-02-11 | 2016-04-19 | Seagate Technology Llc | Mitigation of write errors in multi-level cell flash memory through adaptive error correction code decoding |

| US9325347B1 (en) | 2014-02-21 | 2016-04-26 | Microsemi Storage Solutions (U.S.), Inc. | Forward error correction decoder and method therefor |

| EP3113387B1 (en) | 2014-03-21 | 2019-05-22 | Huawei Technologies Co., Ltd. | Polar code rate-matching method and rate-matching device |

| CN103905152B (zh) * | 2014-03-21 | 2017-06-23 | 华南理工大学 | 删除信道中采用跨层联合编码的有效吞吐量随机优化方法 |

| US20150334700A1 (en) | 2014-05-19 | 2015-11-19 | Mediatek Inc. | Handheld device, base station and transmission control method thereof |

| CN105306165B (zh) | 2014-06-23 | 2019-10-11 | 中兴通讯股份有限公司 | 数据发送方法及装置 |

| US10193578B2 (en) | 2014-07-10 | 2019-01-29 | The Royal Institution For The Advancement Of Learning / Mcgill University | Flexible polar encoders and decoders |

| US20160020783A1 (en) | 2014-07-17 | 2016-01-21 | Lsi Corporation | Low Density Parity Check Decoder With Relative Indexing |

| US9432052B2 (en) | 2014-09-18 | 2016-08-30 | Broadcom Corporation | Puncture-aware low density parity check (LDPC) decoding |

| US9692451B2 (en) * | 2014-09-30 | 2017-06-27 | Avago Technologies General Ip (Singapore) Pte. Ltd | Non-binary low density parity check (NB-LDPC) codes for communication systems |

| US9654144B2 (en) * | 2014-09-30 | 2017-05-16 | Micron Technology, Inc. | Progressive effort decoder architecture |

| US9954645B2 (en) | 2014-12-05 | 2018-04-24 | Lg Electronics Inc. | Method and device for providing secure transmission based on polar code |

| US20160164537A1 (en) | 2014-12-08 | 2016-06-09 | Samsung Electronics Co., Ltd. | Method and apparatus for parallel concatenated ldpc convolutional codes enabling power-efficient decoders |

| US20160173132A1 (en) | 2014-12-10 | 2016-06-16 | Alcatel-Lucent Usa Inc. | Construction of Structured LDPC Convolutional Codes |

| US20160183187A1 (en) | 2014-12-22 | 2016-06-23 | Intel Corporation | Adjacent channel interference mitigation for low-power wake-up radio |

| EP3592094B1 (en) | 2015-01-09 | 2024-11-13 | InterDigital Patent Holdings, Inc. | Method and apparatus for supporting multi-user transmissions in a wireless local area network (wlan) system |

| EP3046259A1 (en) | 2015-01-16 | 2016-07-20 | Alcatel Lucent | Apparatuses and methods for ldpc convolutional encoding and decoding |

| US20160218750A1 (en) | 2015-01-23 | 2016-07-28 | Empire Technology Development Llc | Parity check code encoder |

| US9602133B1 (en) | 2015-01-27 | 2017-03-21 | Microsemi Storage Solutions (U.S.), Inc. | System and method for boost floor mitigation |

| KR101598754B1 (ko) | 2015-03-16 | 2016-03-02 | 세종대학교산학협력단 | Ldpc 복호기 및 그것을 이용한 펑쳐링된 데이터의 디펑쳐링 방법 |

| US9479375B1 (en) | 2015-04-02 | 2016-10-25 | University Of South Florida | Joint physical layer security and PAPR mitigation in OFDM systems |

| US20160309482A1 (en) | 2015-04-15 | 2016-10-20 | Qualcomm Incorporated | Interference-aware group owner, bandwidth, and channel selection in peer-to-peer wireless communication systems |

| US9680605B2 (en) | 2015-05-15 | 2017-06-13 | Nxp Usa, Inc. | Method of offloading cyclic redundancy check on portions of a packet |

| US9742439B1 (en) | 2015-06-08 | 2017-08-22 | Microsemi Solutions (U.S.), Inc. | Method and device for forward error correction decoder system utilizing orthogonality of an H matrix |

| US10231121B2 (en) | 2015-06-24 | 2019-03-12 | Lg Electronics Inc. | Security communication using polar code scheme |

| US9703789B2 (en) | 2015-07-27 | 2017-07-11 | Sas Institute Inc. | Distributed data set storage and retrieval |

| US10461779B2 (en) | 2015-08-12 | 2019-10-29 | Telefonaktiebolaget Lm Ericsson (Publ) | Rate-compatible polar codes |

| US20170063493A1 (en) | 2015-08-25 | 2017-03-02 | Signalchip Innovations Private Limited | Methods and circuits for performing cyclic redundancy check (crc) of an input data stream |

| US9823960B2 (en) | 2015-09-10 | 2017-11-21 | Cavium, Inc. | Apparatus and method for parallel CRC units for variably-sized data frames |

| US10177787B1 (en) | 2015-09-17 | 2019-01-08 | Seagate Technology Llc | Mitigation of error correction failure due to trapping sets |

| CN105227189B (zh) | 2015-09-24 | 2019-01-01 | 电子科技大学 | 分段crc辅助的极化码编译码方法 |

| CN118694482A (zh) | 2015-09-24 | 2024-09-24 | 交互数字专利控股公司 | 用于无线系统中的增强复用的系统 |

| CN105337696B (zh) | 2015-10-08 | 2018-03-30 | 东南大学 | 基于分段crc校验的极化解码方法 |

| US10523364B2 (en) | 2015-11-06 | 2019-12-31 | Samsung Electronics Co., Ltd. | Channel coding framework for 802.11AY and larger block-length LDPC codes for 11AY with 2-step lifting matrices and in-place property |

| US10784901B2 (en) | 2015-11-12 | 2020-09-22 | Qualcomm Incorporated | Puncturing for structured low density parity check (LDPC) codes |

| WO2017091244A1 (en) | 2015-11-23 | 2017-06-01 | Intel IP Corporation | Hybrid arq schemes based on low density parity check codes |

| US10581462B2 (en) | 2015-12-01 | 2020-03-03 | Huawei Technologies Co., Ltd. | Signature-enabled polar encoder and decoder |

| KR20170075627A (ko) | 2015-12-23 | 2017-07-03 | 삼성전자주식회사 | 통신 또는 방송 시스템에서 채널 부호화/복호화 방법 및 장치 |

| EP3378164B1 (en) | 2015-12-23 | 2022-04-27 | Samsung Electronics Co., Ltd. | Apparatus and method for encoding and decoding channel in communication or broadcasting system |

| WO2017119922A1 (en) | 2016-01-04 | 2017-07-13 | Intel IP Corporation | Encoding and decoding using low-density parity-check matrices |

| US11043966B2 (en) | 2016-05-11 | 2021-06-22 | Qualcomm Incorporated | Methods and apparatus for efficiently generating multiple lifted low-density parity-check (LDPC) codes |

| EP3902142A1 (en) | 2016-05-12 | 2021-10-27 | MediaTek Inc. | Qc-ldpc coding methods and apparatus |

| US10454499B2 (en) | 2016-05-12 | 2019-10-22 | Qualcomm Incorporated | Enhanced puncturing and low-density parity-check (LDPC) code structure |

| US10313057B2 (en) | 2016-06-01 | 2019-06-04 | Qualcomm Incorporated | Error detection in wireless communications using sectional redundancy check information |

| US9917675B2 (en) | 2016-06-01 | 2018-03-13 | Qualcomm Incorporated | Enhanced polar code constructions by strategic placement of CRC bits |

| US20170353267A1 (en) | 2016-06-01 | 2017-12-07 | Qualcomm Incorporated | Generalized polar code construction |

| US10469104B2 (en) | 2016-06-14 | 2019-11-05 | Qualcomm Incorporated | Methods and apparatus for compactly describing lifted low-density parity-check (LDPC) codes |

| US20210281359A1 (en) | 2016-07-27 | 2021-09-09 | Qualcomm Incorporated | Design of hybrid automatic repeat request (harq) feedback bits for polar codes |

| WO2018027497A1 (en) | 2016-08-08 | 2018-02-15 | Nokia Technologies Oy | Inter-block modifications to generate sub-matrix of rate compatible parity check matrix |

| CN109565289A (zh) | 2016-08-11 | 2019-04-02 | 瑞典爱立信有限公司 | 基于目标信息长度和目标奇偶校验长度的纠错码选择 |

| CN107733442B (zh) | 2016-08-12 | 2022-12-02 | 中兴通讯股份有限公司 | 结构化ldpc码的处理方法及装置 |

| JP6810790B2 (ja) | 2016-08-12 | 2021-01-06 | テレフオンアクチーボラゲット エルエム エリクソン(パブル) | Ldpc符号のためのレートマッチング方法 |

| CN106341138B (zh) | 2016-09-05 | 2019-05-10 | 厦门大学 | 基于原模图ldpc码的联合信源信道编码矩阵构造方法 |

| US10644829B2 (en) | 2016-09-15 | 2020-05-05 | Huawei Technologies Co., Ltd. | Method and apparatus for encoding data using a polar code |

| CN107888198B (zh) | 2016-09-30 | 2023-05-26 | 中兴通讯股份有限公司 | 准循环ldpc编译码方法、装置及ldpc编译码器 |

| US20180131392A1 (en) | 2016-11-04 | 2018-05-10 | Mediatek Inc. | NR LDPC With Interleaver |

| US10447312B2 (en) | 2016-11-25 | 2019-10-15 | Lg Electronics Inc. | Method of performing interleaving using LDPC and communication apparatus therefor |

| WO2018107430A1 (en) | 2016-12-15 | 2018-06-21 | Qualcomm Incorporated | Crc bits for joint decoding and verification of control information using polar codes |

| EP3542481B1 (en) | 2016-12-20 | 2022-02-16 | Samsung Electronics Co., Ltd. | Apparatus and method for channel encoding/decoding in communication or broadcasting system |

| WO2018128559A1 (en) | 2017-01-09 | 2018-07-12 | Huawei Technologies Co., Ltd. | Efficiently decodable qc-ldpc code |

| TWI652907B (zh) | 2017-01-09 | 2019-03-01 | 聯發科技股份有限公司 | 用於新無線電低密度奇偶校驗碼的偏移係數和提升因數設計 |

| US10630319B2 (en) | 2017-01-24 | 2020-04-21 | Mediatek Inc. | Structure of interleaver with LDPC code |

| CN116260556A (zh) | 2017-02-03 | 2023-06-13 | Idac控股公司 | 依赖于ldpc基础矩阵选择的码块分段 |

| US10594339B2 (en) | 2017-02-03 | 2020-03-17 | Huawei Technologies Co., Ltd. | Method for generating parity check matrix for low density parity check coding |

| US10340949B2 (en) | 2017-02-06 | 2019-07-02 | Qualcomm Incorporated | Multiple low density parity check (LDPC) base graph design |

| US10348329B2 (en) | 2017-02-13 | 2019-07-09 | Qualcomm Incorporated | Low density parity check (LDPC) circular buffer rate matching |

| US10903950B2 (en) | 2017-03-19 | 2021-01-26 | Lg Electronics Inc. | Method and apparatus for transmitting uplink transport block in wireless communication system |

| US10608665B2 (en) | 2017-03-24 | 2020-03-31 | Mediatek Inc. | Method and apparatus for error correction coding in communication |