JP5945392B2 - 発光デバイス - Google Patents

発光デバイス Download PDFInfo

- Publication number

- JP5945392B2 JP5945392B2 JP2011197317A JP2011197317A JP5945392B2 JP 5945392 B2 JP5945392 B2 JP 5945392B2 JP 2011197317 A JP2011197317 A JP 2011197317A JP 2011197317 A JP2011197317 A JP 2011197317A JP 5945392 B2 JP5945392 B2 JP 5945392B2

- Authority

- JP

- Japan

- Prior art keywords

- light emitting

- semiconductor

- emitting element

- semiconductor substrate

- wiring

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 claims description 302

- 239000000758 substrate Substances 0.000 claims description 149

- 239000000463 material Substances 0.000 claims description 10

- 230000000149 penetrating effect Effects 0.000 claims 2

- 239000010410 layer Substances 0.000 description 119

- 238000000034 method Methods 0.000 description 10

- 239000011347 resin Substances 0.000 description 9

- 229920005989 resin Polymers 0.000 description 9

- 230000005540 biological transmission Effects 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 229910052737 gold Inorganic materials 0.000 description 3

- 239000004973 liquid crystal related substance Substances 0.000 description 3

- 230000005855 radiation Effects 0.000 description 3

- 229910052594 sapphire Inorganic materials 0.000 description 3

- 239000010980 sapphire Substances 0.000 description 3

- 150000001875 compounds Chemical class 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 239000012790 adhesive layer Substances 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000000605 extraction Methods 0.000 description 1

- 238000005286 illumination Methods 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 230000008054 signal transmission Effects 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/16—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof the devices being of types provided for in two or more different main groups of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. forming hybrid circuits

- H01L25/167—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof the devices being of types provided for in two or more different main groups of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. forming hybrid circuits comprising optoelectronic devices, e.g. LED, photodiodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/62—Arrangements for conducting electric current to or from the semiconductor body, e.g. lead-frames, wire-bonds or solder balls

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/64—Heat extraction or cooling elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/483—Containers

- H01L33/486—Containers adapted for surface mounting

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Led Device Packages (AREA)

Description

特許文献1 特開平7−178961号公報

特許文献1 特開2009−231134号公報

特許文献2 特開2009−231634号公報

Claims (4)

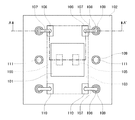

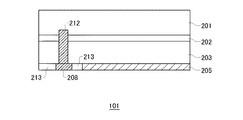

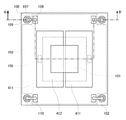

- 半導体発光素子と、

前記半導体発光素子を載置するキャビティを含む半導体基板と、

前記半導体基板内に形成され、前記半導体発光素子を制御する駆動集積回路と、

前記駆動集積回路の表面に形成され、前記半導体発光素子に電気的に接続される素子接続端子と、

前記キャビティの底面および側面を覆い、前記素子接続端子に接続されるように形成される配線と、

前記半導体発光素子が載置される領域とは異なる領域において、前記半導体基板の前記半導体発光素子が載置される表面から裏面まで貫通して形成されたビア配線と、

前記半導体基板の前記表面に載置される接続配線と、

前記半導体発光素子が載置される領域とは異なる領域において、前記半導体基板の前記表面から前記駆動集積回路まで形成されるビア接続部とを備え、

前記駆動集積回路は、前記半導体基板の表面と平行な方向において、前記キャビティよりも外側に形成され、前記ビア接続部および前記接続配線を介して前記ビア配線と電気的に接続され、前記配線および前記素子接続端子を介して前記半導体発光素子に電気的に接続されることを特徴とする発光デバイス。 - 前記ビア配線および前記半導体基板を絶縁する絶縁部を更に備えることを特徴とする請求項1に記載の発光デバイス。

- 前記半導体発光素子が載置される領域において、前記半導体基板の前記表面から前記裏面まで貫通し、前記半導体基板よりも熱伝導率が高い材料で形成された放熱部を更に備え、

前記駆動集積回路は、前記放熱部を囲む領域に形成されることを特徴とする請求項1または2に記載の発光デバイス。 - 前記放熱部の直径は、前記ビア配線の直径より大きいことを特徴とする請求項3に記載の発光デバイス。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR10-2010-0089048 | 2010-09-10 | ||

| KR1020100089048A KR101711961B1 (ko) | 2010-09-10 | 2010-09-10 | 발광 디바이스 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2012060133A JP2012060133A (ja) | 2012-03-22 |

| JP2012060133A5 JP2012060133A5 (ja) | 2014-10-30 |

| JP5945392B2 true JP5945392B2 (ja) | 2016-07-05 |

Family

ID=44582605

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011197317A Active JP5945392B2 (ja) | 2010-09-10 | 2011-09-09 | 発光デバイス |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US9006973B2 (ja) |

| EP (1) | EP2428991B1 (ja) |

| JP (1) | JP5945392B2 (ja) |

| KR (1) | KR101711961B1 (ja) |

| CN (1) | CN102403309B (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102751296B (zh) * | 2012-07-24 | 2015-05-20 | 矽光光电科技(上海)有限公司 | 整合集成电路、发光元件及传感元件的单衬底器件 |

| US9560722B2 (en) | 2013-03-25 | 2017-01-31 | The Hong Kong University Of Science And Technology | Power system-on-chip architecture |

| WO2015008243A1 (en) * | 2013-07-19 | 2015-01-22 | Koninklijke Philips N.V. | Pc led with optical element and without substrate carrier |

| TWM496091U (zh) * | 2014-03-26 | 2015-02-21 | Leadray Energy Co Ltd | 具矽基座的發光二極體及發光二極體燈具 |

| DE102014105734A1 (de) * | 2014-04-23 | 2015-10-29 | Osram Opto Semiconductors Gmbh | Optoelektronisches Halbleiterbauteil und Verfahren zur Herstellung eines optoelektronischen Halbleiterbauteils |

| JP6736260B2 (ja) * | 2015-05-13 | 2020-08-05 | ローム株式会社 | 半導体発光装置 |

| US20170104135A1 (en) * | 2015-10-13 | 2017-04-13 | Sensor Electronic Technology, Inc. | Light Emitting Diode Mounting Structure |

| CN112005455B (zh) * | 2018-04-19 | 2024-06-04 | 索尼半导体解决方案公司 | 半导体激光驱动装置及其制造方法 |

| WO2020122037A1 (ja) * | 2018-12-11 | 2020-06-18 | ソニーセミコンダクタソリューションズ株式会社 | 半導体装置及び電子機器 |

| CN113594194B (zh) * | 2020-04-30 | 2024-09-17 | 华为机器有限公司 | 一种堆叠结构、显示屏及显示装置 |

| KR102557580B1 (ko) * | 2021-01-05 | 2023-07-20 | 엘지전자 주식회사 | 반도체 발광 소자 패키지 및 디스플레이 장치 |

Family Cites Families (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS63111682A (ja) * | 1986-10-29 | 1988-05-16 | Mitsubishi Electric Corp | 光半導体素子用サブマウント |

| CN1300859C (zh) | 1997-01-31 | 2007-02-14 | 松下电器产业株式会社 | 发光元件 |

| US6777883B2 (en) | 2002-04-10 | 2004-08-17 | Koninklijke Philips Electronics N.V. | Integrated LED drive electronics on silicon-on-insulator integrated circuits |

| US20040206970A1 (en) | 2003-04-16 | 2004-10-21 | Martin Paul S. | Alternating current light emitting device |

| JP2005142294A (ja) | 2003-11-05 | 2005-06-02 | Matsushita Electric Ind Co Ltd | 半導体レーザユニットおよびそれを用いた光ピックアップ装置 |

| WO2005104248A1 (ja) * | 2004-04-19 | 2005-11-03 | Matsushita Electric Industrial Co., Ltd. | 発光素子駆動用半導体チップ、発光装置及び照明装置 |

| CN101032034A (zh) | 2004-06-30 | 2007-09-05 | 克里公司 | 用于封装发光器件的芯片级方法和芯片级封装的发光器件 |

| KR100927256B1 (ko) | 2004-07-09 | 2009-11-16 | 엘지전자 주식회사 | 제너다이오드가 집적된 발광소자 서브마운트 제작방법 |

| US7221044B2 (en) | 2005-01-21 | 2007-05-22 | Ac Led Lighting, L.L.C. | Heterogeneous integrated high voltage DC/AC light emitter |

| JP4601464B2 (ja) * | 2005-03-10 | 2010-12-22 | 株式会社沖データ | 半導体装置、プリントヘッド、及びそれを用いた画像形成装置 |

| JP5059739B2 (ja) | 2005-03-11 | 2012-10-31 | ソウル セミコンダクター カンパニー リミテッド | 直列接続された発光セルのアレイを有する発光ダイオードパッケージ |

| KR101241973B1 (ko) | 2005-03-11 | 2013-03-08 | 서울반도체 주식회사 | 발광 장치 및 이의 제조 방법 |

| US7495944B2 (en) | 2005-03-30 | 2009-02-24 | Ovonyx, Inc. | Reading phase change memories |

| JP4969055B2 (ja) * | 2005-04-28 | 2012-07-04 | ローム株式会社 | 光通信モジュール |

| US7994514B2 (en) | 2006-04-21 | 2011-08-09 | Koninklijke Philips Electronics N.V. | Semiconductor light emitting device with integrated electronic components |

| US7655957B2 (en) | 2006-04-27 | 2010-02-02 | Cree, Inc. | Submounts for semiconductor light emitting device packages and semiconductor light emitting device packages including the same |

| KR101134752B1 (ko) | 2006-07-14 | 2012-04-13 | 엘지이노텍 주식회사 | Led 패키지 |

| CN101154656B (zh) | 2006-09-30 | 2010-05-12 | 香港微晶先进封装技术有限公司 | 多芯片发光二极管模组结构及其制造方法 |

| US7855425B2 (en) * | 2007-03-09 | 2010-12-21 | Sanyo Electric Co., Ltd. | Semiconductor device and method of manufacturing the same |

| JP2008235792A (ja) * | 2007-03-23 | 2008-10-02 | Matsushita Electric Ind Co Ltd | 半導体装置とその製造方法 |

| US8436371B2 (en) * | 2007-05-24 | 2013-05-07 | Cree, Inc. | Microscale optoelectronic device packages |

| KR100878326B1 (ko) | 2007-07-03 | 2009-01-14 | 한국광기술원 | 칩스케일 패키징 발광소자 및 그의 제조방법 |

| JP2009117536A (ja) * | 2007-11-05 | 2009-05-28 | Towa Corp | 樹脂封止発光体及びその製造方法 |

| JP5102605B2 (ja) | 2007-12-25 | 2012-12-19 | パナソニック株式会社 | 発光装置およびその製造方法 |

| JP5475954B2 (ja) * | 2008-01-28 | 2014-04-16 | パナソニック株式会社 | 発光装置 |

| US8084780B2 (en) * | 2009-08-13 | 2011-12-27 | Semileds Optoelectronics Co. | Smart integrated semiconductor light emitting system including light emitting diodes and application specific integrated circuits (ASIC) |

-

2010

- 2010-09-10 KR KR1020100089048A patent/KR101711961B1/ko active IP Right Grant

-

2011

- 2011-09-08 EP EP11180601.4A patent/EP2428991B1/en active Active

- 2011-09-09 JP JP2011197317A patent/JP5945392B2/ja active Active

- 2011-09-09 US US13/229,152 patent/US9006973B2/en active Active

- 2011-09-13 CN CN201110276376.1A patent/CN102403309B/zh active Active

Also Published As

| Publication number | Publication date |

|---|---|

| CN102403309B (zh) | 2015-09-16 |

| US20120062115A1 (en) | 2012-03-15 |

| EP2428991A3 (en) | 2014-06-11 |

| EP2428991A2 (en) | 2012-03-14 |

| US9006973B2 (en) | 2015-04-14 |

| KR101711961B1 (ko) | 2017-03-03 |

| KR20120026873A (ko) | 2012-03-20 |

| CN102403309A (zh) | 2012-04-04 |

| EP2428991B1 (en) | 2019-02-20 |

| JP2012060133A (ja) | 2012-03-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5945392B2 (ja) | 発光デバイス | |

| JP2012060133A5 (ja) | ||

| EP3680932B1 (en) | Display device and method for manufacturing same | |

| EP2888729B1 (en) | Display device using semiconductor light emitting devices | |

| US10096647B2 (en) | Display apparatus having a plurality of reflective electrodes | |

| EP3328162B1 (en) | Display device and method for manufacturing same | |

| KR100784057B1 (ko) | 발광소자 패키지 및 발광소자 패키지 제조 방법 | |

| JP2022003413A (ja) | 表示装置 | |

| JP2022058485A (ja) | シリコン上のカラーiledディスプレイ | |

| JP5613361B2 (ja) | 低プロファイルの側面放射led | |

| JP5207812B2 (ja) | 発光デバイスおよび発光デバイスの製造方法 | |

| CN107223285B (zh) | 发光元件以及发光二极管 | |

| JP5113349B2 (ja) | Rgb熱隔離基板 | |

| JP4758921B2 (ja) | 線状光源装置、及びバックライト装置 | |

| JP2010267826A (ja) | Led照明装置および液晶表示装置 | |

| JP5717636B2 (ja) | Ledモジュールおよびその製造方法 | |

| KR20180130845A (ko) | 반도체 발광소자를 이용한 디스플레이 장치 | |

| KR20070099350A (ko) | 발광 다이오드 패키지 및 이를 이용한 조명장치 | |

| JP2009099881A (ja) | 発光装置及びこれを用いた発光モジュールとバックライト装置 | |

| KR101255747B1 (ko) | 발광 소자 모듈 및 이를 포함하는 조명 장치 | |

| CN118213363B (zh) | 发光器件、灯板和显示装置 | |

| US11841528B2 (en) | Linear light-emitting device | |

| US20210408333A1 (en) | Display device using semiconductor light emitting device and method for manufacturing the same | |

| CN116779739A (zh) | 发光模组、显示装置及发光模组制造方法 | |

| JP2018125400A (ja) | 発光装置、及び、照明装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20120813 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20130321 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140908 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140908 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150414 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20150415 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150713 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150908 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20151204 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20160524 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160530 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5945392 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |