JP5622355B2 - 半導体装置およびその作製方法 - Google Patents

半導体装置およびその作製方法 Download PDFInfo

- Publication number

- JP5622355B2 JP5622355B2 JP2008269012A JP2008269012A JP5622355B2 JP 5622355 B2 JP5622355 B2 JP 5622355B2 JP 2008269012 A JP2008269012 A JP 2008269012A JP 2008269012 A JP2008269012 A JP 2008269012A JP 5622355 B2 JP5622355 B2 JP 5622355B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- conductive layer

- semiconductor layer

- transparent conductive

- island

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 194

- 238000004519 manufacturing process Methods 0.000 title claims description 31

- 239000000758 substrate Substances 0.000 claims description 82

- 238000000034 method Methods 0.000 claims description 77

- 229910052751 metal Inorganic materials 0.000 claims description 59

- 239000002184 metal Substances 0.000 claims description 59

- 239000012535 impurity Substances 0.000 claims description 57

- 239000003990 capacitor Substances 0.000 claims description 37

- 238000005530 etching Methods 0.000 claims description 25

- 239000010410 layer Substances 0.000 description 401

- 229920002120 photoresistant polymer Polymers 0.000 description 115

- 239000010408 film Substances 0.000 description 55

- 230000008569 process Effects 0.000 description 50

- 238000000206 photolithography Methods 0.000 description 35

- 239000004020 conductor Substances 0.000 description 33

- 239000011159 matrix material Substances 0.000 description 19

- 230000001681 protective effect Effects 0.000 description 18

- 239000004973 liquid crystal related substance Substances 0.000 description 16

- 239000000463 material Substances 0.000 description 16

- 239000010936 titanium Substances 0.000 description 11

- 239000011347 resin Substances 0.000 description 9

- 229920005989 resin Polymers 0.000 description 9

- 229910021417 amorphous silicon Inorganic materials 0.000 description 8

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 8

- 238000004544 sputter deposition Methods 0.000 description 8

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical group [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 7

- 238000001312 dry etching Methods 0.000 description 7

- 229910052710 silicon Inorganic materials 0.000 description 7

- 239000010703 silicon Substances 0.000 description 7

- 239000002356 single layer Substances 0.000 description 7

- 238000003860 storage Methods 0.000 description 7

- 238000004380 ashing Methods 0.000 description 6

- 239000010949 copper Substances 0.000 description 6

- 229910052719 titanium Inorganic materials 0.000 description 6

- 229910045601 alloy Inorganic materials 0.000 description 5

- 239000000956 alloy Substances 0.000 description 5

- 229910052782 aluminium Inorganic materials 0.000 description 5

- 230000015572 biosynthetic process Effects 0.000 description 5

- 239000011651 chromium Substances 0.000 description 5

- 229910052750 molybdenum Inorganic materials 0.000 description 5

- 239000002245 particle Substances 0.000 description 5

- 238000000059 patterning Methods 0.000 description 5

- 229910052721 tungsten Inorganic materials 0.000 description 5

- 229910052581 Si3N4 Inorganic materials 0.000 description 4

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 4

- 229910052802 copper Inorganic materials 0.000 description 4

- 239000011521 glass Substances 0.000 description 4

- WABPQHHGFIMREM-UHFFFAOYSA-N lead(0) Chemical compound [Pb] WABPQHHGFIMREM-UHFFFAOYSA-N 0.000 description 4

- 238000012545 processing Methods 0.000 description 4

- 230000009467 reduction Effects 0.000 description 4

- 238000006722 reduction reaction Methods 0.000 description 4

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- 229910052990 silicon hydride Inorganic materials 0.000 description 4

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 4

- 238000002834 transmittance Methods 0.000 description 4

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 3

- 229910052779 Neodymium Inorganic materials 0.000 description 3

- 239000000853 adhesive Substances 0.000 description 3

- 230000001070 adhesive effect Effects 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 229910052804 chromium Inorganic materials 0.000 description 3

- 239000000356 contaminant Substances 0.000 description 3

- 238000013461 design Methods 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 238000007687 exposure technique Methods 0.000 description 3

- 239000001257 hydrogen Substances 0.000 description 3

- 229910052739 hydrogen Inorganic materials 0.000 description 3

- 239000011733 molybdenum Substances 0.000 description 3

- 239000000565 sealant Substances 0.000 description 3

- 229910052814 silicon oxide Inorganic materials 0.000 description 3

- 229910052715 tantalum Inorganic materials 0.000 description 3

- 238000001039 wet etching Methods 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 2

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 230000004888 barrier function Effects 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 150000001875 compounds Chemical class 0.000 description 2

- 238000011161 development Methods 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 238000003384 imaging method Methods 0.000 description 2

- 238000007689 inspection Methods 0.000 description 2

- 239000011229 interlayer Substances 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 230000002265 prevention Effects 0.000 description 2

- 230000003014 reinforcing effect Effects 0.000 description 2

- 239000003566 sealing material Substances 0.000 description 2

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 2

- 239000010937 tungsten Substances 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 239000004988 Nematic liquid crystal Substances 0.000 description 1

- 229910003902 SiCl 4 Inorganic materials 0.000 description 1

- 239000004990 Smectic liquid crystal Substances 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- -1 Tungsten nitride Chemical class 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- SLLGVCUQYRMELA-UHFFFAOYSA-N chlorosilicon Chemical compound Cl[Si] SLLGVCUQYRMELA-UHFFFAOYSA-N 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 230000007797 corrosion Effects 0.000 description 1

- 238000005260 corrosion Methods 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000007865 diluting Methods 0.000 description 1

- 238000010790 dilution Methods 0.000 description 1

- 239000012895 dilution Substances 0.000 description 1

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 1

- 238000004090 dissolution Methods 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 239000001307 helium Substances 0.000 description 1

- 229910052734 helium Inorganic materials 0.000 description 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 1

- 150000002431 hydrogen Chemical class 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 229910052743 krypton Inorganic materials 0.000 description 1

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 1

- 229910052754 neon Inorganic materials 0.000 description 1

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 238000002294 plasma sputter deposition Methods 0.000 description 1

- 239000004033 plastic Substances 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 238000006479 redox reaction Methods 0.000 description 1

- 239000003870 refractory metal Substances 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

- 230000007480 spreading Effects 0.000 description 1

- 238000003892 spreading Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/1288—Multistep manufacturing methods employing particular masking sequences or specially adapted masks, e.g. half-tone mask

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

- H01L29/41725—Source or drain electrodes for field effect devices

- H01L29/41733—Source or drain electrodes for field effect devices for thin film transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

- H01L29/6675—Amorphous silicon or polysilicon transistors

- H01L29/66765—Lateral single gate single channel transistors with inverted structure, i.e. the channel layer is formed after the gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

- H01L29/78609—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device for preventing leakage current

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78651—Silicon transistors

- H01L29/7866—Non-monocrystalline silicon transistors

- H01L29/78672—Polycrystalline or microcrystalline silicon transistor

- H01L29/78678—Polycrystalline or microcrystalline silicon transistor with inverted-type structure, e.g. with bottom gate

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Ceramic Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Thin Film Transistor (AREA)

- Liquid Crystal (AREA)

Description

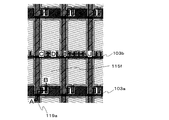

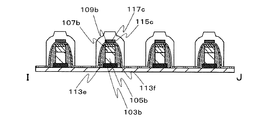

図1は本発明のアモルファス半導体TFTを有するアクティブマトリクス基板の平面図の一例であり、ここでは簡略化のため、マトリックス上に配置された複数の画素のうち1つの画素の構成を示している。

実施の形態1では、非晶質半導体層を用いたTFTを示したが、本実施の形態では、微結晶半導体層を用いたTFTの例を示す。微結晶半導体を用いるTFTの模式図を図9に示す。本実施の形態では、実施の形態1における第1の非晶質半導体層106を、第1の微結晶半導体層126と第1の非晶質半導体層127の積層とする。

本実施の形態では、実施の形態1における第3のフォトリソグラフィ工程において、第3のフォトレジストパターン124a〜124dの代わりにポジ型の感光性樹脂を用いる例を示す。また、ポジ型感光性樹脂を用いるTFTの模式図を図10に示す。

図11はCOG(chip on glass)方式を用いて、電気光学装置の組み立てる様子を模式的に示す図である。第1の基板1100には画素領域1103、外部入出力端子1104、接続配線1105が形成されている。点線で囲まれた領域は、走査線側のICチップ貼り合わせ領域1101とデータ線側のICチップ貼り合わせ領域1102である。第2の基板1108には対向電極1109が形成され、シール材1110で第1の基板1100と貼り合わせる。シール材1110の内側には液晶が封入され液晶層1111を形成する。第1の基板1100と第2の基板1108とは所定の間隔を持って貼り合わせるが、ネマチック液晶の場合には3〜8μm、スメクチック液晶の場合には1〜4μmとする。

本発明の半導体装置、及び電子機器として、液晶TV、ビデオカメラ、デジタルカメラ等のカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機又は電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置。例えば、ポータブルDVDプレイヤー。)などが挙げられる。それら電子機器のうち、一部の電子製品の具体例を図13および図14に示す。

20 容量部

30 端子部

101 基板

102 第1の導電層

103a ゲート配線

103b 容量線

103c 電極

104 第1の絶縁層

105a ゲート絶縁層

105b 絶縁層

106 第1の非晶質半導体層

107a 島状の第1の非晶質半導体層

107b 島状の第1の非晶質半導体層

108 一導電型の不純物元素を含有する第2の非晶質半導体層

109a 島状の一導電型の不純物元素を含有する第2の非晶質半導体層

109b 島状の一導電型の不純物元素を含有する第2の非晶質半導体層

110a フォトレジストパターン

110b フォトレジストパターン

110c フォトレジストパターン

110d フォトレジストパターン

111a フォトレジストパターン

111b フォトレジストパターン

111c フォトレジストパターン

112 第2の絶縁層

113a サイドウォール

113b サイドウォール

113c サイドウォール

113d サイドウォール

113e サイドウォール

113f サイドウォール

113g サイドウォール

114 透明導電層

115a 透明導電層

115b 透明導電層

115c 電極

115d 電極

115e 電極

115f 画素電極

116 金属層

117a 金属層

117b 金属層

117c 金属層

117d 金属層

117e 金属層

118 第2の導電層

119a ソース配線

119b ソース電極又はドレイン電極

120a フォトレジストパターン

120b フォトレジストパターン

120c フォトレジストパターン

120d フォトレジストパターン

120e フォトレジストパターン

121a フォトレジストパターン

121b フォトレジストパターン

121c フォトレジストパターン

121d フォトレジストパターン

121e フォトレジストパターン

122 第3の絶縁層

123a 保護絶縁層

123b 保護絶縁層

123c 保護絶縁層

123d 保護絶縁層

124a フォトレジストパターン

124b フォトレジストパターン

124c フォトレジストパターン

124d フォトレジストパターン

125a フォトレジストパターン

125b フォトレジストパターン

125c フォトレジストパターン

125d フォトレジストパターン

126 第1の微結晶半導体層

127 第1の非晶質半導体層

128 一導電型の不純物元素を含有させた微結晶半導体層

129 ポジ型感光性材料パターン

1100 第1の基板

1101 ICチップ貼り合わせ領域

1102 ICチップ貼り合わせ領域

1103 画素領域

1104 外部入出力端子

1105 接続配線

1106 ICチップ

1107 ICチップ

1108 第2の基板

1109 対向電極

1110 シール材

1111 液晶層

1112 FPC

1113 補強板

1201 第1の基板

1202 第2の基板

1203 シール材

1204 液晶層

1205 引出線

1206 接続配線及び入出力端子

1207 ICチップ

1208 入出力端子

1209 導電性粒子

1210 樹脂

1211 FPC

1212 配線

1213 導電性粒子

1214 樹脂

1215 接着材

1216 Auワイヤ

1217 樹脂

1311 本体

1312 表示部

1314 操作キー

1316 シャッターボタン

1321 本体

1322 筐体

1323 表示部

1324 キーボード

1325 外部接続ポート

1326 ポインティングデバイス

1331 本体

1332 筐体

1333 第1の表示部

1334 第2の表示部

1335 記録媒体(DVD等)読込部

1336 操作キー

1337 スピーカ部

1341 筐体

1342 支持台

1343 表示部

1344 スピーカ

1345 ビデオ入力端子

1400 携帯電話機

1401 本体(A)

1402 本体(B)

1403 筐体

1404 操作スイッチ類

1405 マイクロフォン

1406 スピーカ

1407 回路基板

1408 表示パネル(A)

1409 表示パネル(B)

1410 蝶番

Claims (3)

- 基板上に、第1の導電層、前記第1の導電層上の第1の絶縁層、前記第1の絶縁層上の第1の半導体層、及び前記第1の半導体層上の一導電型の不純物元素を含有する第2の半導体層を有する積層を形成し、

第1のレジストパターンをマスクとして、前記積層をエッチングして、第2の導電層、前記第2の導電層上の第2の絶縁層、前記第2の絶縁層上の第3の半導体層、及び前記第3の半導体層上の一導電型の不純物元素を含有する第4の半導体層を、それぞれ有する第1及び第2の島状の積層を形成し、

前記第1の島状の積層の側面に接する第1のサイドウォールと、前記第2の島状の積層の側面に接する第2のサイドウォールと、を形成し、

前記第1及び前記第2の島状の積層、前記第1及び前記第2のサイドウォール、並びに前記基板を覆うように、第3の導電層を形成し、

前記第3の導電層は、第1の透明導電層及び前記第1の透明導電層上の第1の金属層の積層であり、

第1の膜厚と前記第1の膜厚より厚い第2の膜厚とを有する第2のレジストパターンをマスクとして、前記第3の導電層をエッチングすることにより、前記第1の島状の積層及び前記第1のサイドウォールに接する第4の導電層と、前記第2の島状の積層及び前記第2のサイドウォールに接する第5の導電層とを形成し、

前記第4の導電層は、第2の透明導電層と前記第2の透明導電層上の第2の金属層の積層であり、

前記第5の導電層は、第3の透明導電層と前記第3の透明導電層上の第3の金属層の積層であり、

前記第2の金属層の上面の面積は、前記第2の透明導電層の上面の面積より小さく、

前記第2の金属層は、前記第1の島状の積層の前記第4の半導体層と、前記第1のサイドウォールとに重なり、

前記第3の金属層の上面の面積は、前記第3の透明導電層の上面の面積より小さく、

前記第3の金属層は、前記第2の島状の積層の前記第4の半導体層のみと重なり、

前記第3の透明導電層は、前記第2の島状の積層の前記第4の半導体層上面及び前記第2のサイドウォールと接し、

前記第1の島状の積層及び前記第4の導電層は、トランジスタとして機能し、

前記第2の島状の積層及び前記第5の導電層は、容量素子として機能し、

前記第2の透明導電層のうち、前記第2の金属層と重ならず且つ前記基板上面に接する部分は、画素電極として機能することを特徴とする半導体装置の作製方法。 - 請求項1において、

前記第4の導電層及び前記第5の導電層を形成後、前記第1及び前記第2の島状の積層、前記第1及び前記第2のサイドウォール、前記第4及び前記第5の導電層、並びに前記基板を覆うように、第3の絶縁層を形成し、

前記第3の絶縁層上に第3のレジストパターンを形成し、

前記第3のレジストパターンにリフロー処理を行い、テーパー側面を有する第4のレジストパターンを形成し、

前記第4のレジストパターンをマスクとして、前記第3の絶縁層をパターニングすることを特徴とする半導体装置の作製方法。 - 基板上に、トランジスタと、容量素子と、前記トランジスタと電気的に接続する画素電極とを有し、

前記トランジスタは、

第1の導電層、前記第1の導電層上の第1の絶縁層、前記第1の絶縁層上の第1の半導体層、及び前記第1の半導体層上の一導電型の不純物元素を含有する第2の半導体層を有する第1の島状の積層と、

前記第1の島状の積層の側面に接する第1のサイドウォールと、

前記第2の半導体層上面及び前記第1のサイドウォール側面に接する第2の導電層とを有し、

前記第2の導電層は、第1の透明導電層及び前記第1の透明導電層上の第1の金属層の積層であり、

前記第1の金属層の上面の面積は、前記第1の透明導電層の上面の面積より小さく、

前記第1の金属層は、前記第1の透明導電層を介して前記第2の半導体層と重なり、かつ前記第1の透明導電層を介して前記第1のサイドウォール側面を覆い、

前記容量素子は、

第3の導電層、前記第3の導電層上の第2の絶縁層、前記第2の絶縁層上の第3の半導体層、及び前記第3の半導体層上の一導電型の不純物元素を含有する第4の半導体層を有する第2の島状の積層と、

前記第2の島状の積層の側面に接する第2のサイドウォールと、

前記第4の半導体層上面及び前記第2のサイドウォール側面に接する第4の導電層とを有し、

前記第4の導電層は、第2の透明導電層及び前記第2の透明導電層上の第2の金属層の積層であり、

前記第2の金属層の上面の面積は、前記第2の透明導電層の上面の面積より小さく、

前記第2の金属層は、前記第2の透明導電層を介して前記第2の半導体層のみと重なり、

前記第2の透明導電層は、前記第4の半導体層上面及び前記第2のサイドウォールと接し、

前記第1の導電層と前記第3の導電層とは、同一の導電層をエッチングする工程を経て形成されたものであり、

前記第1の絶縁層と前記第2の絶縁層とは、同一の絶縁層をエッチングする工程を経て形成されたものであり、

前記第1の半導体層と前記第3の半導体層とは、同一の半導体層をエッチングする工程を経て形成されたものであり、

前記第2の半導体層と前記第4の半導体層とは、一導電型の不純物元素を含有する同一の半導体層をエッチングする工程を経て形成されたものであり、

前記第1の透明導電層と前記第2の透明導電層とは、同一の透明導電層をエッチングする工程を経て形成されたものであり、

前記第1の金属層と前記第2の金属層とは、同一の金属層をエッチングする工程を経て形成されたものであり、

前記第1の金属層と重ならず且つ前記基板上面に接する前記第1の透明導電層の部分は、前記画素電極として機能することを特徴とする半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008269012A JP5622355B2 (ja) | 2007-10-23 | 2008-10-17 | 半導体装置およびその作製方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007275612 | 2007-10-23 | ||

| JP2007275612 | 2007-10-23 | ||

| JP2008269012A JP5622355B2 (ja) | 2007-10-23 | 2008-10-17 | 半導体装置およびその作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009124121A JP2009124121A (ja) | 2009-06-04 |

| JP2009124121A5 JP2009124121A5 (ja) | 2011-12-01 |

| JP5622355B2 true JP5622355B2 (ja) | 2014-11-12 |

Family

ID=40562561

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008269012A Expired - Fee Related JP5622355B2 (ja) | 2007-10-23 | 2008-10-17 | 半導体装置およびその作製方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US8148730B2 (ja) |

| JP (1) | JP5622355B2 (ja) |

| KR (1) | KR101448903B1 (ja) |

| CN (1) | CN101419987B (ja) |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7772054B2 (en) | 2007-06-15 | 2010-08-10 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| JP5380037B2 (ja) | 2007-10-23 | 2014-01-08 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP5357493B2 (ja) * | 2007-10-23 | 2013-12-04 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| WO2009072451A1 (en) * | 2007-12-03 | 2009-06-11 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of thin film transistor and manufacturing method of display device |

| JP5137798B2 (ja) * | 2007-12-03 | 2013-02-06 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US8101442B2 (en) * | 2008-03-05 | 2012-01-24 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing EL display device |

| JP5503895B2 (ja) * | 2008-04-25 | 2014-05-28 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US8207026B2 (en) * | 2009-01-28 | 2012-06-26 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of thin film transistor and manufacturing method of display device |

| JP5503995B2 (ja) * | 2009-02-13 | 2014-05-28 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US8003303B2 (en) * | 2009-04-09 | 2011-08-23 | Taiwan Semiconductor Manufacturing Company, Ltd | Intensity selective exposure method and apparatus |

| US8673520B2 (en) | 2009-04-09 | 2014-03-18 | Taiwan Semiconductor Manufacturing Company, Ltd. | Intensity selective exposure photomask |

| KR101349143B1 (ko) | 2010-03-30 | 2014-01-08 | 삼성디스플레이 주식회사 | 유기 발광 디스플레이 장치의 제조 방법 |

| TWI438539B (zh) * | 2010-12-16 | 2014-05-21 | Innolux Corp | 陣列基板的形成方法 |

| KR20130027188A (ko) * | 2011-09-07 | 2013-03-15 | 삼성디스플레이 주식회사 | 표시 장치 및 그 제조 방법 |

| WO2013129155A1 (ja) * | 2012-02-27 | 2013-09-06 | 京セラ株式会社 | 表示装置 |

| CN104155814A (zh) * | 2014-08-29 | 2014-11-19 | 昆山龙腾光电有限公司 | 液晶显示装置及其制造方法 |

| JP6403000B2 (ja) | 2014-11-10 | 2018-10-10 | セイコーエプソン株式会社 | 電気光学装置、電子機器、及び電気光学装置の製造方法 |

Family Cites Families (65)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS56122123A (en) * | 1980-03-03 | 1981-09-25 | Shunpei Yamazaki | Semiamorphous semiconductor |

| USRE34658E (en) * | 1980-06-30 | 1994-07-12 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device of non-single crystal-structure |

| JPS61203484A (ja) | 1985-03-06 | 1986-09-09 | 株式会社東芝 | 表示装置用駆動回路基板及びその製造方法 |

| JPH0311744A (ja) | 1989-06-09 | 1991-01-21 | Citizen Watch Co Ltd | 薄膜トランジスタの製造方法 |

| JPH0992838A (ja) * | 1995-09-26 | 1997-04-04 | Matsushita Electric Ind Co Ltd | 薄膜トランジスタおよびその製造方法 |

| EP0775931B1 (en) * | 1995-11-21 | 2005-10-05 | Samsung Electronics Co., Ltd. | Method of manufacturing a liquid crystal display |

| US5773331A (en) * | 1996-12-17 | 1998-06-30 | International Business Machines Corporation | Method for making single and double gate field effect transistors with sidewall source-drain contacts |

| JPH10198292A (ja) * | 1996-12-30 | 1998-07-31 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| US6297519B1 (en) * | 1998-08-28 | 2001-10-02 | Fujitsu Limited | TFT substrate with low contact resistance and damage resistant terminals |

| US6493048B1 (en) * | 1998-10-21 | 2002-12-10 | Samsung Electronics Co., Ltd. | Thin film transistor array panel for a liquid crystal display and a method for manufacturing the same |

| US6184069B1 (en) * | 1999-05-24 | 2001-02-06 | Chi Mei Electronics Corp. | Fabrication of thin film transistor-liquid crystal display with self-aligned transparent conducting layers |

| KR100325079B1 (ko) * | 1999-12-22 | 2002-03-02 | 주식회사 현대 디스플레이 테크놀로지 | 고개구율 및 고투과율 액정표시장치의 제조방법 |

| US7023021B2 (en) * | 2000-02-22 | 2006-04-04 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method of manufacturing the same |

| JP4118484B2 (ja) | 2000-03-06 | 2008-07-16 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2002333845A (ja) * | 2000-04-21 | 2002-11-22 | Matsushita Electric Ind Co Ltd | 表示パネル用基板、その製造方法およびそれに用いる薄膜形成装置 |

| KR20020002052A (ko) * | 2000-06-29 | 2002-01-09 | 주식회사 현대 디스플레이 테크놀로지 | 프린지 필드 구동 모드 액정 표시 장치의 제조방법 |

| US7223643B2 (en) * | 2000-08-11 | 2007-05-29 | Semiconductor Energy Laboratory Co., Ltd. | Method of manufacturing a semiconductor device |

| TW488080B (en) * | 2001-06-08 | 2002-05-21 | Au Optronics Corp | Method for producing thin film transistor |

| US6623653B2 (en) * | 2001-06-12 | 2003-09-23 | Sharp Laboratories Of America, Inc. | System and method for etching adjoining layers of silicon and indium tin oxide |

| JP4876341B2 (ja) * | 2001-07-13 | 2012-02-15 | 日本電気株式会社 | アクティブマトリクス基板及びその製造方法 |

| TW517392B (en) * | 2001-07-23 | 2003-01-11 | Au Optronics Corp | Manufacturing method of thin film transistor flat panel display |

| JP2003179069A (ja) * | 2001-12-12 | 2003-06-27 | Matsushita Electric Ind Co Ltd | 薄膜トランジスタ、液晶表示装置、有機エレクトロルミネッセンス素子、ならびに表示装置用基板およびその製造方法 |

| TW565943B (en) * | 2002-09-18 | 2003-12-11 | Chi Mei Optoelectronics Corp | Thin film transistor structure and its manufacturing method |

| TW560076B (en) * | 2002-09-27 | 2003-11-01 | Chi Mei Optoelectronics Corp | Structure and manufacturing method of thin film transistor |

| KR100789090B1 (ko) * | 2002-12-30 | 2007-12-26 | 엘지.필립스 엘시디 주식회사 | 액정표시장치 제조방법 |

| JP4118706B2 (ja) | 2003-02-25 | 2008-07-16 | 株式会社半導体エネルギー研究所 | 液晶表示装置の作製方法 |

| US7123332B2 (en) * | 2003-05-12 | 2006-10-17 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device, electronic device having the same, and semiconductor device |

| JP2005108912A (ja) * | 2003-09-29 | 2005-04-21 | Quanta Display Japan Inc | 液晶表示装置とその製造方法 |

| TWI282895B (en) * | 2004-04-23 | 2007-06-21 | Toppoly Optoelectronics Corp | Electrode array structure of a fringe field switching mode LCD |

| KR101086478B1 (ko) * | 2004-05-27 | 2011-11-25 | 엘지디스플레이 주식회사 | 표시 소자용 박막 트랜지스터 기판 및 그 제조 방법 |

| KR101121620B1 (ko) * | 2004-06-05 | 2012-02-28 | 엘지디스플레이 주식회사 | 표시 소자용 박막 트랜지스터 기판 및 그 제조 방법 |

| TWI240111B (en) * | 2004-11-11 | 2005-09-21 | Quanta Display Inc | Array substrate for use in TFT-LCD and fabrication method thereof |

| KR101117979B1 (ko) * | 2004-12-24 | 2012-03-06 | 엘지디스플레이 주식회사 | 박막 트랜지스터 기판의 제조 방법 |

| KR20060079040A (ko) * | 2004-12-31 | 2006-07-05 | 엘지.필립스 엘시디 주식회사 | 프린지 필드 스위칭 타입의 박막 트랜지스터 기판 및 그제조 방법 |

| US7608490B2 (en) * | 2005-06-02 | 2009-10-27 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US7588970B2 (en) * | 2005-06-10 | 2009-09-15 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| KR101201017B1 (ko) * | 2005-06-27 | 2012-11-13 | 엘지디스플레이 주식회사 | 액정 표시 장치 및 그 제조 방법 |

| KR101225440B1 (ko) * | 2005-06-30 | 2013-01-25 | 엘지디스플레이 주식회사 | 액정 표시 장치 및 그 제조 방법 |

| US7807516B2 (en) * | 2005-06-30 | 2010-10-05 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method of the same |

| US7867791B2 (en) * | 2005-07-29 | 2011-01-11 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of semiconductor device using multiple mask layers formed through use of an exposure mask that transmits light at a plurality of intensities |

| US7914971B2 (en) * | 2005-08-12 | 2011-03-29 | Semiconductor Energy Laboratory Co., Ltd. | Light exposure mask and method for manufacturing semiconductor device using the same |

| KR100642761B1 (ko) * | 2005-09-07 | 2006-11-10 | 삼성전자주식회사 | 반도체 소자 및 그 제조 방법 |

| KR101172666B1 (ko) * | 2005-09-29 | 2012-08-08 | 엘지디스플레이 주식회사 | 액정표시소자 및 그 제조방법 |

| US8149346B2 (en) * | 2005-10-14 | 2012-04-03 | Semiconductor Energy Laboratory Co., Ltd. | Display device and manufacturing method thereof |

| JP5105811B2 (ja) | 2005-10-14 | 2012-12-26 | 株式会社半導体エネルギー研究所 | 表示装置 |

| TWI460851B (zh) * | 2005-10-17 | 2014-11-11 | Semiconductor Energy Lab | 半導體裝置及其製造方法 |

| DE602006016537D1 (de) * | 2005-11-25 | 2010-10-14 | Semiconductor Energy Lab | Betriebsverfahren und Anordnung eines Halbleiterspeichers |

| EP2270583B1 (en) * | 2005-12-05 | 2017-05-10 | Semiconductor Energy Laboratory Co., Ltd. | Transflective Liquid Crystal Display with a Horizontal Electric Field Configuration |

| EP2479604B1 (en) * | 2005-12-05 | 2015-07-15 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device |

| KR100978260B1 (ko) * | 2005-12-27 | 2010-08-26 | 엘지디스플레이 주식회사 | 액정표시장치 및 그 제조방법 |

| US7821613B2 (en) * | 2005-12-28 | 2010-10-26 | Semiconductor Energy Laboratory Co., Ltd. | Display device and manufacturing method thereof |

| JP2007189120A (ja) * | 2006-01-16 | 2007-07-26 | Idemitsu Kosan Co Ltd | Tft基板及びその製造方法 |

| JP2007212699A (ja) * | 2006-02-09 | 2007-08-23 | Idemitsu Kosan Co Ltd | 反射型tft基板及び反射型tft基板の製造方法 |

| TWI322288B (en) * | 2006-03-07 | 2010-03-21 | Au Optronics Corp | Manufacture method of pixel array substrate |

| TWI298545B (en) * | 2006-04-24 | 2008-07-01 | Au Optronics Corp | Method for fabricating a thin film transistor |

| TWI275184B (en) * | 2006-05-18 | 2007-03-01 | Au Optronics Corp | Thin film transistor and fabrication method thereof |

| US7636135B2 (en) * | 2006-09-11 | 2009-12-22 | Beijing Boe Optoelectronics Technology Co., Ltd | TFT-LCD array substrate and method for manufacturing the same |

| US8357937B2 (en) * | 2006-12-19 | 2013-01-22 | Lg Display Co., Ltd. | Thin film transistor liquid crystal display device |

| TWI328880B (en) * | 2007-01-31 | 2010-08-11 | Au Optronics Corp | Method for fabricating a pixel structure of a liquid crystal display device |

| TW200837956A (en) * | 2007-03-14 | 2008-09-16 | Chunghwa Picture Tubes Ltd | Thin film transistor |

| JP5427390B2 (ja) * | 2007-10-23 | 2014-02-26 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US7824939B2 (en) * | 2007-10-23 | 2010-11-02 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing display device comprising separated and electrically connected source wiring layers |

| JP5380037B2 (ja) * | 2007-10-23 | 2014-01-08 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP5357493B2 (ja) * | 2007-10-23 | 2013-12-04 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| TWI355553B (en) * | 2007-10-30 | 2012-01-01 | Au Optronics Corp | Pixel structure and method for manufacturing the s |

-

2008

- 2008-10-14 KR KR1020080100665A patent/KR101448903B1/ko not_active IP Right Cessation

- 2008-10-17 JP JP2008269012A patent/JP5622355B2/ja not_active Expired - Fee Related

- 2008-10-20 US US12/254,603 patent/US8148730B2/en not_active Expired - Fee Related

- 2008-10-23 CN CN200810175027.9A patent/CN101419987B/zh not_active Expired - Fee Related

-

2012

- 2012-02-17 US US13/398,883 patent/US9006050B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US9006050B2 (en) | 2015-04-14 |

| US20090101906A1 (en) | 2009-04-23 |

| JP2009124121A (ja) | 2009-06-04 |

| US8148730B2 (en) | 2012-04-03 |

| KR101448903B1 (ko) | 2014-10-13 |

| US20120149157A1 (en) | 2012-06-14 |

| CN101419987B (zh) | 2015-03-25 |

| KR20090041317A (ko) | 2009-04-28 |

| CN101419987A (zh) | 2009-04-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5622355B2 (ja) | 半導体装置およびその作製方法 | |

| US8895333B2 (en) | Method for manufacturing semiconductor device with pixel electrode over gate electrode of thin film transistor | |

| JP5595569B2 (ja) | 半導体装置の作製方法 | |

| TW478014B (en) | Semiconductor device and method of manufacturing thereof | |

| JP4118485B2 (ja) | 半導体装置の作製方法 | |

| JP4118484B2 (ja) | 半導体装置の作製方法 | |

| KR100843506B1 (ko) | 반도체 장치 및 그 제작 방법 | |

| JP5044273B2 (ja) | 薄膜トランジスタアレイ基板、その製造方法、及び表示装置 | |

| US7776664B2 (en) | Method of manufacturing semiconductor device | |

| JP4905136B2 (ja) | 液晶装置 | |

| JP2008209931A (ja) | 液晶表示装置 | |

| JP2007134730A (ja) | 表示装置 | |

| JP2006235638A (ja) | 液晶表示装置 | |

| JP4128588B2 (ja) | 液晶表示装置 | |

| JP4118704B2 (ja) | 液晶表示装置の作製方法 | |

| JP4118705B2 (ja) | 半導体装置の作製方法 | |

| KR20070018291A (ko) | 박막 트랜지스터 표시판 및 그의 제조 방법 | |

| JP2007173850A (ja) | 半導体装置の作製方法および半導体装置を用いた電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111013 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20111013 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130712 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130820 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130919 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140401 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140411 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140916 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140922 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5622355 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |