JP4118706B2 - 液晶表示装置の作製方法 - Google Patents

液晶表示装置の作製方法 Download PDFInfo

- Publication number

- JP4118706B2 JP4118706B2 JP2003047613A JP2003047613A JP4118706B2 JP 4118706 B2 JP4118706 B2 JP 4118706B2 JP 2003047613 A JP2003047613 A JP 2003047613A JP 2003047613 A JP2003047613 A JP 2003047613A JP 4118706 B2 JP4118706 B2 JP 4118706B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- conductive film

- amorphous semiconductor

- source wiring

- wiring

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

【発明の属する技術分野】

本願発明は薄膜トランジスタ(以下、TFTという)で構成された回路を有する半導体装置およびその作製方法に関する。例えば、液晶表示パネルに代表される電気光学装置およびその様な電気光学装置を部品として搭載した電子機器に関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

【0003】

【従来の技術】

近年、絶縁表面を有する基板上に形成された半導体薄膜(厚さ数〜数百nm程度)を用いて薄膜トランジスタ(TFT)を構成する技術が注目されている。薄膜トランジスタはICや電気光学装置のような電子デバイスに広く応用され、特に画像表示装置のスイッチング素子として開発が急がれている。

【0004】

従来より、画像表示装置として液晶表示装置が知られている。パッシブ型の液晶表示装置に比べ高精細な画像が得られることからアクティブマトリクス型の液晶表示装置が多く用いられるようになっている。アクティブマトリクス型の液晶表示装置においては、マトリクス状に配置された画素電極を駆動することによって、画面上に表示パターンが形成される。詳しくは選択された画素電極と該画素電極に対応する対向電極との間に電圧が印加されることによって、画素電極と対向電極との間に配置された液晶層の光学変調が行われ、この光学変調が表示パターンとして観察者に認識される。

【0005】

このようなアクティブマトリクス型の電気光学装置の用途は広がっており、画面サイズの大面積化とともに高精細化や高開口率化や高信頼性の要求が高まっている。また、同時に生産性の向上や低コスト化の要求も高まっている。

【0006】

従来では、300℃以下の低温で大面積の基板上に形成可能であることから非晶質半導体膜として非晶質シリコン膜が好適に用いられている。また、非晶質半導体膜で形成されたチャネル形成領域を有する逆スタガ型(若しくはボトムゲート型)のTFTが多く用いられている。

【0007】

【発明が解決しようとする課題】

従来、アクティブマトリクス型の電気光学装置は、写真蝕刻(フォトリソグラフィー)技術により、最低でも5枚以上のフォトマスクを使用してTFTを基板上に作製していたため製造コストが大きかった。生産性を向上させ歩留まりを向上させるためには、工程数を削減することが有効な手段として考えられる。

【0008】

具体的には、TFTの製造に要するフォトマスクの枚数を削減することが必要である。フォトマスクはフォトリソグラフィーの技術において、エッチング工程のマスクとするフォトレジストパターンを基板上に形成するために用いる。

【0009】

このフォトマスクを1枚使用することによって、レジスト塗布、プレベーク、露光、現像、ポストベークなどの工程と、その前後の工程において、被膜の成膜およびエッチングなどの工程、さらにレジスト剥離、洗浄や乾燥工程などが付加され、煩雑なものとなり、問題となっていた。

【0010】

また、基板が絶縁体であるために製造工程中における摩擦などによって静電気が発生していた。この静電気が発生すると基板上に設けられた配線の交差部でショートしたり、静電気によってTFTが劣化または破壊されて電気光学装置に表示欠陥や画質の劣化が生じていた。特に、製造工程で行われる液晶配向処理のラビング時に静電気が発生し問題となっていた。

【0011】

本発明はこのような問題に答えるものであり、アクティブマトリクス型の液晶表示装置に代表される電気光学装置において、TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現することを課題としている。

【0012】

また、静電気によるTFTの破壊やTFTの特性劣化という問題点を解決しうる構造およびその作製方法を提供することを課題としている。

【0013】

【課題を解決するための手段】

上記課題を解決するために、本発明では、チャネル・エッチ型のボトムゲートTFT構造を採用し、ソース領域及びドレイン領域のパターニングと画素電極のパターニングを同じフォトマスクで行うことを特徴とする。

【0014】

以下に本発明の作製方法を簡略に説明する。

【0015】

まず、第1のマスク(フォトマスク1枚目)でゲート配線102を形成する。

【0016】

次いで、絶縁膜(ゲート絶縁膜)104a、第1の非晶質半導体膜105、n型を付与する不純物元素を含む第2の非晶質半導体膜106、及び第1の導電膜107を順次、積層形成する(図2(A))。なお、非晶質半導体膜に代えて微結晶半導体膜を用いてもよいし、n型を付与する不純物元素を含む非晶質半導体膜に代えてn型を付与する不純物元素を含む微結晶半導体膜を用いてもよい。さらに、これらの膜(104a、105、106、107)はスパッタ法やプラズマCVD法を用いて複数のチャンバー内または同一チャンバー内で連続的に大気に曝すことなく形成することができる。大気に曝さないようにすることで不純物の混入を防止できる。

【0017】

次いで、第2のマスク(フォトマスク2枚目)で上記第1の導電膜107をパターニングして第1の導電膜からなる配線(後にソース配線及び電極(ドレイン電極)となる)111を形成し、上記第2の非晶質半導体膜106をパターニングしてn型を付与する不純物元素を含む第2の非晶質半導体膜110を形成し、上記第1の非晶質半導体膜105をパターニングして第1の非晶質半導体膜109を形成する(図2(B))。

【0018】

その後、全面に第2の導電膜112を成膜する(図2(D))。なお、第2の導電膜112としては、透明導電膜を用いてもよいし、反射性を有する導電膜を用いてもよい。

【0019】

次いで、第3のマスク(フォトマスク3枚目)で上記第2の導電膜112をパターニングして第2の導電膜からなる画素電極119を形成し、上記配線をパターニングしてソース配線117及び電極(ドレイン電極)118を形成し、n型を付与する不純物元素を含む第2の非晶質半導体膜110をパターニングしてn型を付与する不純物元素を含む第2の非晶質半導体膜からなるソース領域115及びドレイン領域116を形成し、上記第1の非晶質半導体膜109を一部除去して第1の非晶質半導体膜114を形成する(図3(A))。

【0020】

このような構成とすることで、画素TFT部の作製する際、フォトリソグラフィー技術で使用するフォトマスクの数を3枚とすることができる。

【0021】

また、ソース配線は画素電極と同じ材料である第2の導電膜120で覆い、基板全体を外部の静電気等から保護する構造とする。また、この第2の導電膜120を用いて画素TFT部以外の領域に保護回路を形成する構造としてもよい。このような構成とすることで、製造工程において製造装置と絶縁体基板との摩擦による静電気の発生を防止することができる。特に、製造工程で行われる液晶配向処理のラビング時に発生する静電気からTFT等を保護することができる。

【0022】

本明細書で開示する本発明の構成は、ゲート配線と、ソース配線と、画素電極とを有する半導体装置であって、

絶縁表面上に形成されたゲート配線102と、

前記ゲート配線上に形成された絶縁膜104bと、

前記絶縁膜上に形成された非晶質半導体膜114と、

前記非晶質半導体膜上に形成されたソース領域115及びドレイン領域116と、

前記ソース領域または前記ドレイン領域上に形成されたソース配線117または電極118と、

前記電極上に形成された画素電極119とを有し、

前記ドレイン領域116または前記ソース領域115の一つの端面は、前記非晶質半導体膜114の端面及び前記電極118の端面と概略一致することを特徴とする半導体装置である。

【0023】

また、他の発明の構成は、ゲート配線と、ソース配線と、画素電極とを有する半導体装置であって、

絶縁表面上に形成されたゲート配線102と、

前記ゲート配線上に形成された絶縁膜104bと、

前記絶縁膜上に形成された非晶質半導体膜114と、

前記非晶質半導体膜上に形成されたソース領域115及びドレイン領域116と、

前記ソース領域または前記ドレイン領域上に形成されたソース配線117または電極118と、

前記電極上に形成された画素電極119とを有し、

前記ドレイン領域115または前記ソース116領域の一つの端面は、前記非晶質半導体膜の端面114及び前記電極118の端面と概略一致し、もう一つの端面は、前記画素電極119の端面及び前記電極118のもう一つの端面と概略一致することを特徴とする半導体装置である。

【0024】

また、他の発明の構成は、ゲート配線と、ソース配線と、画素電極とを有する半導体装置であって、

絶縁表面上に形成されたゲート配線102と、

前記ゲート配線上に形成された絶縁膜104bと、

前記絶縁膜上に形成された非晶質半導体膜114と、

前記非晶質半導体膜上に形成されたソース領域115及びドレイン領域116と、

前記ソース領域または前記ドレイン領域上に形成されたソース配線117または電極118と、

前記電極上に形成された画素電極119とを有し、

前記ソース配線117の下方には、前記非晶質半導体膜と、n型を付与する不純物元素を含む非晶質半導体膜とが積層されていることを特徴とする半導体装置である。

【0025】

また、上記構成において、画素電極119を透明導電膜とすれば透過型の液晶表示装置となり、画素電極119を反射性を有する導電膜とすれば反射型の液晶表示装置となる。また、前記ソース配線上には画素電極と同じ材料からなる配線120が積層されている。

【0026】

また、本発明では、反射型の液晶表示装置の作製方法において、画素電極の表面に凹凸を持たせて光散乱性を図るための凸部601の形成をゲート配線600と同じフォトマスクで行うことを特徴とする。なお、この凸部601はゲート配線、及びTFT部以外の領域の基板上に適宜設ける。

【0027】

以下に本発明の作製方法を簡略に説明する。

【0028】

まず、第1のマスク(フォトマスク1枚目)でゲート配線600及びを凸部601形成する。

【0029】

次いで、絶縁膜(ゲート絶縁膜)602、第1の非晶質半導体膜、n型を付与する不純物元素を含む第2の非晶質半導体膜、及び第1の導電膜を順次、積層形成する。なお、非晶質半導体膜に代えて微結晶半導体膜を用いてもよいし、n型を付与する不純物元素を含む非晶質半導体膜に代えてn型を付与する不純物元素を含む微結晶半導体膜を用いてもよい。さらに、これらの膜はスパッタ法やプラズマCVD法を用いて複数のチャンバー内または同一チャンバー内で連続的に大気に曝すことなく形成することができる。大気に曝さないようにすることで不純物の混入を防止できる。

【0030】

上記絶縁膜602は、凸部601が形成された基板上に形成され、表面に凸凹を有している。

【0031】

次いで、第2のマスク(フォトマスク2枚目)で上記第1の導電膜をパターニングして第1の導電膜からなる配線(後にソース配線及び電極(ドレイン電極)となる)を形成し、上記第2の非晶質半導体膜をパターニングしてn型を付与する不純物元素を含む第2の非晶質半導体膜を形成し、上記第1の非晶質半導体膜をパターニングして第1の非晶質半導体膜を形成する。

【0032】

その後、全面に第2の導電膜を成膜する。なお、第2の導電膜としては、反射性を有する導電膜を用いる。

【0033】

次いで、第3のマスク(フォトマスク3枚目)で上記第2の導電膜をパターニングして第2の導電膜からなる画素電極604を形成し、上記配線をパターニングしてソース配線608及び電極(ドレイン電極)609を形成し、n型を付与する不純物元素を含む第2の非晶質半導体膜をパターニングしてn型を付与する不純物元素を含む第2の非晶質半導体膜からなるソース領域606及びドレイン領域607を形成し、上記第1の非晶質半導体膜を一部除去して第1の非晶質半導体膜605を形成する。

【0034】

このような構成とすることで、画素TFT部の作製する際、フォトリソグラフィー技術で使用するフォトマスクの数を3枚とすることができる。

【0035】

さらに、このような構成とすることで、凸部601上に形成された絶縁膜の表面は凸凹を有し、この凸凹を表面に有する絶縁膜602上に画素電極604が形成されるので、画素電極604の表面に凹凸を持たせて光散乱性を図ることができる。

【0036】

上記作製方法により得られる本発明の構成は、ゲート配線600と、ソース配線608と、反射性を有する画素電極604とを有する半導体装置であって、

絶縁表面上に形成されたゲート配線600及び凸部601と、

前記ゲート配線及び前記凸部上に形成されて表面に凸凹を有する絶縁膜602と、

前記絶縁膜602上に形成された非晶質半導体膜605と、

前記非晶質半導体膜上に形成されたソース領域606及びドレイン領域607と、

前記ソース領域または前記ドレイン領域上に形成されたソース配線608または電極609と、

前記電極609上に形成され、且つ表面に凸凹を有する絶縁膜602上に形成されて表面に凸凹を有する画素電極604と、を有していることを特徴とする半導体装置である。

【0037】

上記構成において、前記ゲート配線600及び前記凸部601は、同一材料からなることを特徴としている。また、上記構成においても前記ドレイン領域607または前記ソース領域608の一つの端面は、前記非晶質半導体膜605の端面及び前記電極609の端面と概略一致することを特徴としている。さらに、上記構成においても前記ドレイン領域607または前記ソース領域608の一つの端面は、前記非晶質半導体膜605の端面及び前記電極609の端面と概略一致し、もう一つの端面は、前記画素電極604の端面及び前記電極604のもう一つの端面と概略一致することを特徴している。

【0038】

また、上記各構成において、前記ソース領域及び前記ドレイン領域は、n型を付与する不純物元素を含む非晶質半導体膜からなることを特徴としている。

【0039】

また、上記各構成において、前記絶縁膜、前記非晶質半導体膜、前記ソース領域、及び前記ドレイン領域は、大気に曝されることなく連続的に形成されたことを特徴としている。

【0040】

また、上記各構成において、前記絶縁膜、前記非晶質半導体膜、前記ソース領域、または前記ドレイン領域は、スパッタ法により形成されたことを特徴としている。

【0041】

また、上記各構成において、前記ソース領域及び前記ドレイン領域は、前記非晶質半導体膜及び前記電極と同一のマスクにより形成されたことを特徴としている。また、前記ソース領域及び前記ドレイン領域は、前記ソース配線と同一のマスクにより形成されたことを特徴としている。

【0042】

また、上記各構成において、前記ソース領域及び前記ドレイン領域は、前記ソース配線及び前記画素電極と同一のマスクにより形成されたことを特徴としている。

【0043】

また、上記各構成において、前記画素電極は前記絶縁膜と接していることを特徴としている。また、前記画素電極は、前記ドレイン領域の端面と、非晶質半導体膜の端面とも接している。

【0044】

また、上記各構成において、第3のマスクを用いたエッチング工程によって、前記非晶質半導体膜の一部が除去されるため、前記非晶質半導体膜のうち、前記ソース領域及びドレイン領域と接する領域における膜厚は、前記ソース領域と接する領域と前記ドレイン領域と接する領域との間の領域における膜厚より厚い構成、即ちチャネル・エッチ型のボトムゲート構造となっている。

【0045】

【発明の実施の形態】

本願発明の実施形態について、以下に説明する。

【0046】

図1は本発明のアクティブマトリクス基板の平面図の一例であり、ここでは簡略化のため、マトリクス状に配置された複数の画素のうちの1つの画素構成を示している。また、図2及び図3は作製工程を示す図である。

【0047】

図1に示すように、このアクティブマトリクス基板は、互いに平行に配置された複数のゲート配線と、各ゲート配線に直交するソース配線を複数有している。

【0048】

また、ゲート配線とソース配線とで囲まれた領域には画素電極119が配置されている。また、この画素電極119と重ならないように、画素電極と同じ材料からなる配線120がソース配線と重なっている。

【0049】

さらに、画素電極119の下方で隣り合う2本のゲート配線の間には、ゲート配線102と平行に容量配線103が配置されている。この容量配線103は全画素に設けられており、画素電極119との間に存在する絶縁膜104bを誘電体として保持容量を形成している。

【0050】

また、ゲート配線102とソース配線117の交差部近傍にはスイッチング素子としてのTFTが設けられている。このTFTは非晶質構造を有する半導体膜(以下、第1の非晶質半導体膜と呼ぶ)で形成されたチャネル形成領域を有する逆スタガ型(若しくはボトムゲート型)のTFTである。

【0051】

また、このTFTは、絶縁性基板上に順次、ゲート電極(ゲート配線102と一体形成された)と、ゲート絶縁膜と、第1の非晶質半導体膜膜と、n型を付与する不純物元素を含む第2の非晶質半導体膜からなるソース領域及びドレイン領域と、ソース電極(ソース配線117と一体形成された)及び電極118(以下、ドレイン電極とも呼ぶ)とが積層形成されている。

【0052】

また、ソース配線(ソース電極含む)及びドレイン電極118の下方には、絶縁性基板上に順次、ゲート絶縁膜と、第1の非晶質半導体膜と、n型を付与する不純物元素を含む第2の非晶質半導体膜とが積層形成されている。

【0053】

また、第1の非晶質半導体膜のうち、ソース領域と接する領域とドレイン領域と接する領域との間の領域は、他の領域と比べ膜厚が薄くなっている。膜厚が薄くなったのは、n型を付与する不純物元素を含む第2の非晶質半導体膜をエッチングにより分離してソース領域とドレイン領域とを形成する際、第1の非晶質半導体膜の一部が除去されたためである。また、このエッチングによって画素電極の端面、ドレイン電極の端面、及びドレイン領域の端面が一致している。

【0054】

また、同様にソース電極を覆う配線120の端面、ソース領域の端面、及びソース配線の端面が一致している。

【0055】

以上の構成でなる本願発明について、以下に示す実施例でもってさらに詳細な説明を行うこととする。

【0056】

【実施例】

[実施例1]

本発明の実施例を図1〜図6を用いて説明する。本実施例は液晶表示装置の作製方法を示し、基板上に画素部のTFTを逆スタガ型で形成し、該TFTに接続する保持容量を作製する方法について工程に従って詳細に説明する。また、同図には該基板の端部に設けられ、他の基板に設けた回路の配線と電気的に接続するための端子部の作製工程を同時に示す。

【0057】

図2(A)において、透光性を有する基板100にはコーニング社の#7059ガラスや#1737ガラスなどに代表されるバリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板を用いることができる。その他に、石英基板、プラスチック基板などの透光性基板を使用することもできる。

【0058】

次いで、導電層を基板全面に形成した後、第1のフォトリソグラフィー工程を行い、レジストマスクを形成し、エッチングにより不要な部分を除去して配線及び電極(ゲート電極を含むゲート配線102、容量配線103、及び端子101)を形成する。このとき少なくともゲート電極102の端部にテーパー部が形成されるようにエッチングする。この段階での上面図を図4に示した。

【0059】

ゲート電極を含むゲート配線102と容量配線103、端子部の端子101は、アルミニウム(Al)や銅(Cu)などの低抵抗導電性材料で形成することが望ましいが、Al単体では耐熱性が劣り、また腐蝕しやすい等の問題点があるので耐熱性導電性材料と組み合わせて形成する。また、低抵抗導電性材料としてAgPdCu合金を用いてもよい。耐熱性導電性材料としては、チタン(Ti)、タンタル(Ta)、タングステン(W)、モリブデン(Mo)、クロム(Cr)、Nd(ネオジム)から選ばれた元素、または前記元素を成分とする合金か、前記元素を組み合わせた合金膜、または前記元素を成分とする窒化物で形成する。例えば、TiとCuの積層、TaNとCuとの積層が挙げられる。また、Ti、Si、Cr、Nd等の耐熱性導電性材料と組み合わせて形成した場合、平坦性が向上するため好ましい。また、このような耐熱性導電性材料のみ、例えばMoとWを組み合わせて形成しても良い。

【0060】

液晶表示装置を実現するためには、ゲート電極およびゲート配線は耐熱性導電性材料と低抵抗導電性材料とを組み合わせて形成することが望ましい。この時の適した組み合わせを説明する。

【0061】

画面サイズが5型程度までなら耐熱性導電性材料の窒化物から成る導電層(A)と耐熱性導電性材料から成る導電層(B)とを積層したニ層構造とする。導電層(B)はAl、Cu、Ta、Ti、W、Nd、Crから選ばれた元素、または前記元素を成分とする合金か、前記元素を組み合わせた合金膜で形成すれば良く、導電層(A)は窒化タンタル(TaN)膜、窒化タングステン(WN)膜、窒化チタン(TiN)膜などで形成する。例えば、導電層(A)としてCr、導電層(B)としてNdを含有するAlとを積層したニ層構造とすることが好ましい。導電層(A)は10〜100nm(好ましくは20〜50nm)とし、導電層(B)は200〜400nm(好ましくは250〜350nm)とする。

【0062】

一方、大画面に適用するには耐熱性導電性材料から成る導電層(A)と低抵抗導電性材料から成る導電層(B)と耐熱性導電性材料から成る導電層(C)とを積層した三層構造とすることが好ましい。低抵抗導電性材料から成る導電層(B)は、アルミニウム(Al)を成分とする材料で形成し、純Alの他に、0.01〜5atomic%のスカンジウム(Sc)、Ti、Nd、シリコン(Si)等を含有するAlを使用する。導電層(C)は導電層(B)のAlにヒロックが発生するのを防ぐ効果がある。導電層(A)は10〜100nm(好ましくは20〜50nm)とし、導電層(B)は200〜400nm(好ましくは250〜350nm)とし、導電層(C)は10〜100nm(好ましくは20〜50nm)とする。本実施例では、Tiをターゲットとしたスパッタ法により導電層(A)をTi膜で50nmの厚さに形成し、Alをターゲットとしたスパッタ法により導電層(B)をAl膜で200nmの厚さに形成し、Tiをターゲットとしたスパッタ法により導電層(C)をTi膜で50nmの厚さに形成した。

【0063】

次いで、絶縁膜104aを全面に成膜する。絶縁膜104aはスパッタ法を用い、膜厚を50〜200nmとする。

【0064】

例えば、絶縁膜104aとして窒化シリコン膜を用い、150nmの厚さで形成する。勿論、ゲート絶縁膜はこのような窒化シリコン膜に限定されるものでなく、酸化シリコン膜、酸化窒化シリコン膜、酸化タンタル膜などの他の絶縁膜を用い、これらの材料から成る単層または積層構造として形成しても良い。例えば、下層を窒化シリコン膜とし、上層を酸化シリコン膜とする積層構造としても良い。

【0065】

次に、絶縁膜104a上に50〜200nm(好ましくは100〜150nm)の厚さで第1の非晶質半導体膜105を、プラズマCVD法やスパッタ法などの公知の方法で全面に形成する(図示せず)。代表的には、シリコンのターゲットを用いたスパッタ法で非晶質シリコン(a−Si)膜を100nmの厚さに形成する。その他、この第1の非晶質半導体膜には、微結晶半導体膜、非晶質シリコンゲルマニウム膜(SiXGe(1-X)、(0<X<1))、非晶質シリコンカーバイト(SiXCY)などの非晶質構造を有する化合物半導体膜を適用することも可能である。

【0066】

次に、一導電型(n型またはp型)の不純物元素を含有する第2の非晶質半導体膜を20〜80nmの厚さで形成する。一導電型(n型またはp型)を付与する不純物元素を含む第2の非晶質半導体膜は、プラズマCVD法やスパッタ法などの公知の方法で全面に形成する。本実施例では、リン(P)が添加されたシリコンターゲットを用いてn型の不純物元素を含有する第2の非晶質半導体膜106を形成した。あるいは、シリコンターゲットを用い、リンを含む雰囲気中でスパッタリングを行い成膜してもよい。或いは、n型を付与する不純物元素を含む第2の非晶質半導体膜を水素化微結晶シリコン膜(μc−Si:H)で形成しても良い。

【0067】

次に、金属材料からなる第1の導電膜107をスパッタ法や真空蒸着法で形成する。第1の導電膜107の材料としては、第2の非晶質半導体膜106とオーミックコンタクトのとれる金属材料であれば特に限定されず、Al、Cr、Ta、Tiから選ばれた元素、または前記元素を成分とする合金か、前記元素を組み合わせた合金膜等が挙げられる。本実施例ではスパッタ法を用い、第1の導電膜107として、50〜150nmの厚さで形成したTi膜と、そのTi膜上に重ねてアルミニウム(Al)を300〜400nmの厚さで形成し、さらにその上にTi膜を100〜150nmの厚さで形成した(図2(A))。

【0068】

絶縁膜104a、第1の非晶質半導体膜105、n型を付与する不純物元素を含む第2の非晶質半導体膜106、及び第1の導電膜107はいずれも公知の方法で作製するものであり、プラズマCVD法やスパッタ法で作製することができる。本実施例では、これらの膜(104a、105、106、107)をスパッタ法で、ターゲット及びスパッタガスを適宣切り替えることにより連続的に形成した。この時、スパッタ装置において、同一の反応室または複数の反応室を用い、これらの膜を大気に曝すことなく連続して積層させることが好ましい。このように、大気に曝さないことで不純物の混入を防止することができる。

【0069】

次に、第2のフォトリソグラフィー工程を行い、レジストマスク108を形成し、エッチングにより不要な部分を除去して配線(後の工程によりソース配線及びドレイン電極となる)111を形成する。この際のエッチング方法としてウエットエッチングまたはドライエッチングを用いる。この時、第1の導電膜107、n型を付与する不純物元素を含む第2の非晶質半導体膜106、及び第1の非晶質半導体膜105が順次、レジストマスク108をマスクとしてエッチングされ、画素TFT部においては、第1の導電膜からなる配線111、n型を付与する不純物元素を含む第2の非晶質半導体膜110、及び第1の非晶質半導体膜109がそれぞれ形成される。本実施例では、SiCl4とCl2とBCl3の混合ガスを反応ガスとしたドライエッチングにより、Ti膜とAl膜とTi膜を順次積層した第1の導電膜107をエッチングし、反応ガスをCF4とO2の混合ガスに代えて第1の非晶質半導体膜105及びn型を付与する不純物元素を含む第2の非晶質半導体膜106を選択的に除去した。(図2(B))また、容量部においては容量配線103と絶縁膜104aを残し、同様に端子部においても、端子101と絶縁膜104aが残る。

【0070】

次に、レジストマスク108を除去した後、シャドーマスクを用いてレジストマスクを形成し、端子部のパッド部分を覆っている絶縁膜104aを選択的に除去して絶縁膜104bを形成した後、レジストマスクを除去する。(図2(C))また、シャドーマスクに代えてスクリーン印刷法によりレジストマスクを形成してエッチングマスクとしてもよい。

【0071】

次に、全面に透明導電膜からなる第2の導電膜112を成膜する。(図2(D))また、この時の上面図を図5に示す。ただし、簡略化のため図5では全面に成膜された第2の導電膜112は図示していない。

【0072】

この第2の導電膜112の材料は、酸化インジウム(In2O3)や酸化インジウム酸化スズ合金(In2O3―SnO2、ITOと略記する)などをスパッタ法や真空蒸着法などを用いて形成する。このような材料のエッチング処理は塩酸系の溶液により行う。しかし、特にITOのエッチングは残渣が発生しやすいので、エッチング加工性を改善するために酸化インジウム酸化亜鉛合金(In2O3―ZnO)を用いても良い。酸化インジウム酸化亜鉛合金は表面平滑性に優れ、ITOと比較して熱安定性にも優れているので、第2の導電膜112と接触する配線111をAl膜で形成しても腐蝕反応をすることを防止できる。同様に、酸化亜鉛(ZnO)も適した材料であり、さらに可視光の透過率や導電率を高めるためにガリウム(Ga)を添加した酸化亜鉛(ZnO:Ga)などを用いることができる。

【0073】

次に、第3のフォトリソグラフィー工程を行い、レジストマスク113a〜113cを形成し、エッチングにより不要な部分を除去して第1の非晶質半導体膜114、ソース領域115及びドレイン領域116、ソース電極117及びドレイン電極118、画素電極119を形成する(図3(A))。

【0074】

この第3のフォトリソグラフィー工程は、第2の導電膜112をパターニングすると同時に、配線111とn型を付与する不純物元素を含む第2の非晶質半導体膜110と第1の非晶質半導体膜109の一部をエッチングにより除去して開孔を形成する。本実施例では、まず、ITOからなる第2の導電膜112を硝酸と塩酸の混合溶液または塩化系第2鉄系の溶液を用いたウエットエッチングにより選択的に除去し、ウエットエッチングにより配線111を選択的に除去した後、ドライエッチングによりn型を付与する不純物元素を含む第2の非晶質半導体膜110と非晶質半導体膜109の一部をエッチングした。なお、本実施例では、ウエットエッチングとドライエッチングとを用いたが、実施者が反応ガスを適宜選択してドライエッチングのみで行ってもよいし、実施者が反応溶液を適宜選択してウエットエッチングのみで行ってもよい。

【0075】

また、開孔の底部は第1の非晶質半導体膜に達しており、凹部を有する第1の非晶質半導体膜114が形成される。この開孔によって配線111はソース配線117とドレイン電極118に分離され、n型を付与する不純物元素を含む第2の非晶質半導体膜110はソース領域115とドレイン領域116に分離される。また、ソース配線と接する第2の導電膜120は、ソース配線を覆い、後の製造工程、特にラビング処理で生じる静電気を防止する役目を果たす。本実施例では、ソース配線上に第2の導電膜120を形成した例を示したが、第2の導電膜120を除去してもよい。

【0076】

また、この第3のフォトリソグラフィー工程において、容量部における絶縁膜104bを誘電体として、容量配線103と画素電極119とで保持容量が形成される。

【0077】

また、この第3のフォトリソグラフィー工程において、レジストマスク113cで覆い端子部に形成された透明導電膜からなる第2の導電膜を残す。

【0078】

次に、レジストマスク113a〜113cを除去した。この状態の断面図を図3(B)に示した。なお、図1は1つの画素の上面図であり、A−A'線 及びB−B'線に沿った断面図がそれぞれ図3(B)に相当する。

【0079】

また、図9(A)は、この状態でのゲート配線端子部501、及びソース配線端子部502の上面図をそれぞれ図示している。なお、図1〜図3と対応する箇所には同じ符号を用いている。また、図9(B)は図9(A)中のE−E'線 及びF−F'線に沿った断面図に相当する。図9(A)において、透明導電膜からなる503は入力端子として機能する接続用の電極である。また、図9(B)において、504は絶縁膜(104bから延在する)、505は第1の非晶質半導体膜(114から延在する)、506はn型を付与する不純物元素を含む第2の非晶質半導体膜(115から延在する)である。

【0080】

こうして3回のフォトリソグラフィー工程により、3枚のフォトマスクを使用して、逆スタガ型のnチャネル型TFT201を有する画素TFT部、保持容量202を完成させることができる。そして、これらを個々の画素に対応してマトリクス状に配置して画素部を構成することによりアクティブマトリクス型の電気光学装置を作製するための一方の基板とすることができる。本明細書では便宜上このような基板をアクティブマトリクス基板と呼ぶ。

【0081】

次に、アクティブマトリクス基板の画素部のみに配向膜121を選択的に形成する。配向膜121を選択的に形成する方法としては、スクリーン印刷法を用いてもよいし、配向膜を塗布後、シャドーマスクを用いてレジストマスクを形成して除去する方法を用いてもよい。通常、液晶表示素子の配向膜にはポリイミド樹脂が多く用いられている。

【0082】

次に、配向膜121にラビング処理を施して液晶分子がある一定のプレチルト角を持って配向するようにする。

【0083】

次いで、アクティブマトリクス基板と、対向電極122と配向膜123とが設けられた対向基板124とをスペーサで基板間隔を保持しながらシール剤により貼り合わせた後、アクティブマトリクス基板と対向基板の間に液晶材料125を注入する。液晶材料125は公知のものを適用すれば良く代表的にはTN液晶を用いる。液晶材料を注入した後、注入口は樹脂材料で封止する。

【0084】

次に、端子部の入力端子101にフレキシブルプリント配線板(Flexible Printed Circuit:FPC)を接続する。FPCはポリイミドなどの有機樹脂フィルム129に銅配線128が形成されていて、異方性導電性接着剤で入力端子を覆う透明導電膜と接続する。異方性導電性接着剤は接着剤126と、その中に混入され金などがメッキされた数十〜数百μm径の導電性表面を有する粒子127により構成され、この粒子127が入力端子101上の透明導電膜と銅配線128とに接触することによりこの部分で電気的な接触が形成される。さらに、この部分の機械的強度を高めるために樹脂層130を設ける(図3(C))。

【0085】

図6はアクティブマトリクス基板の画素部と端子部の配置を説明する図である。基板210上には画素部211が設けられ、画素部にはゲート配線208とソース配線207が交差して形成され、これに接続するnチャネル型TFT201が各画素に対応して設けられている。nチャネル型TFT201のドレイン側には画素電極119及び保持容量202が接続し、保持容量202のもう一方の端子は容量配線209に接続している。nチャネル型TFT201と保持容量202の構造は図3(B)で示すnチャネル型TFT201と保持容量202と同じものとする。

【0086】

基板の一方の端部には、走査信号を入力する入力端子部205が形成され、接続配線206によってゲート配線208に接続している。また、他の端部には画像信号を入力する入力端子部203が形成され、接続配線204によってソース配線207に接続している。ゲート配線208、ソース配線207、容量配線209は画素密度に応じて複数本設けられるものである。また、画像信号を入力する入力端子部212と接続配線213を設け、入力端子部203と交互にソース配線と接続させても良い。入力端子部203、205、212はそれぞれ任意な数で設ければ良いものとし、実施者が適宣決定すれば良い。

【0087】

[実施例2]

図7は液晶表示装置の実装方法の一例である。液晶表示装置は、TFTが作製された基板301の端部には、入力端子部302が形成され、これは実施例1で示したようにゲート配線と同じ材料で形成される端子303で形成される。そして対向基板304とスペーサ306を内包するシール剤305により貼り合わされ、さらに偏光板307、308が設けられている。そして、スペーサ322によって筐体321に固定される。

【0088】

なお、実施例1により得られる非晶質シリコン膜で活性層を形成したTFTは、電界効果移動度が小さく1cm2/Vsec程度しか得られていない。そのために、画像表示を行うための駆動回路はICチップで形成され、TAB(tape automated bonding)方式やCOG(chip on glass)方式で実装されている。本実施例では、ICチップ313に駆動回路を形成し、TAB方式で実装する例を示す。これにはフレキシブルプリント配線板(Flexible Printed Circuit:FPC)が用いられ、FPCはポリイミドなどの有機樹脂フィルム309に銅配線310が形成されていて、異方性導電性接着剤で入力端子302と接続する。入力端子は配線303上に接して設けられた透明導電膜である。異方性導電性接着剤は接着剤311と、その中に混入され金などがメッキされた数十〜数百μm径の導電性表面を有する粒子312により構成され、この粒子312が入力端子302と銅配線310とに接触することにより、この部分で電気的な接触が形成される。そしてこの部分の機械的強度を高めるために樹脂層318が設けられている。

【0089】

ICチップ313はバンプ314で銅配線310に接続し、樹脂材料315で封止されている。そして銅配線310は接続端子316でその他の信号処理回路、増幅回路、電源回路などが形成されたプリント基板317に接続されている。そして、透過型の液晶表示装置では対向基板304に光源319と光導光体320が設けられてバックライトとして使用される。

【0090】

[実施例3]

本実施例では、保護膜を形成した例を図6に示す。なお、本実施例は、実施例1の図3(B)の状態まで同一であるので異なる点について以下に説明する。また、図3(B)に対応する箇所は同一の符号を用いた。

【0091】

まず、実施例1に従って図3(B)の状態を得た後、薄い無機絶縁膜を全面に形成する。この薄い無機絶縁膜としては、スパッタ法またはプラズマCVD法で形成する酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、酸化タンタル膜などの無機絶縁膜を用い、これらの材料から成る単層または積層構造として形成しても良い。

【0092】

次いで、第4のフォトリソグラフィー工程を行い、レジストマスクを形成し、エッチングにより不要な部分を除去して、画素TFT部においては絶縁膜402、端子部においては無機絶縁膜401をそれぞれ形成する。この無機絶縁膜401、402は、パッシベーション膜として機能する。また、端子部においては、第4のフォトリソグラフィー工程により薄い無機絶縁膜401を除去して、端子部の端子101上に形成された透明導電膜からなる第2の導電膜を露呈させる。

【0093】

こうして本実施例では、4回のフォトリソグラフィー工程により、4枚のフォトマスクを使用して、無機絶縁膜で保護された逆スタガ型のnチャネル型TFT、保持容量を完成させることができる。そして、これらを個々の画素に対応してマトリクス状に配置し、画素部を構成することによりアクティブマトリクス型の電気光学装置を作製するための一方の基板とすることができる。

【0094】

なお、本実施例は、実施例1または実施例2の構成と自由に組み合わせることが可能である。

【0095】

[実施例4]

実施例1では、絶縁膜、第1の非晶質半導体膜、n型を付与する不純物元素を含む第2の非晶質半導体膜、及び第1の導電膜をスパッタ法で積層形成した例を示したが、本実施例では、プラズマCVD法を用いた例を示す。

【0096】

本実施例では、絶縁膜、第1の非晶質半導体膜、及びn型を付与する不純物元素を含む第2の非晶質半導体膜をプラズマCVD法で形成した。

【0097】

本実施例では、絶縁膜として酸化窒化シリコン膜を用い、プラズマCVD法により150nmの厚さで形成する。この時、プラズマCVD装置において、電源周波数13〜70MHz、好ましくは27〜60MHzで行えばよい。電源周波数27〜60MHzを使うことにより緻密な絶縁膜を形成することができ、ゲート絶縁膜としての耐圧を高めることができる。また、SiH4とNH3にN2Oを添加させて作製された酸化窒化シリコン膜は、膜中の固定電荷密度が低減されているので、この用途に対して好ましい材料となる。勿論、ゲート絶縁膜はこのような酸化窒化シリコン膜に限定されるものでなく、酸化シリコン膜、窒化シリコン膜、酸化タンタル膜などの他の絶縁膜を用い、これらの材料から成る単層または積層構造として形成しても良い。また、下層を窒化シリコン膜とし、上層を酸化シリコン膜とする積層構造としても良い。

【0098】

例えば、酸化シリコン膜を用いる場合には、プラズマCVD法で、オルトケイ酸テトラエチル(Tetraethyl Orthosilicate:TEOS)とO2とを混合し、反応圧力40Pa、基板温度250〜350℃とし、高周波(13.56MHz)電力密度0.5〜0.8W/cm2で放電させて形成することができる。このようにして作製された酸化シリコン膜は、その後300〜400℃の熱アニールによりゲート絶縁膜として良好な特性を得ることができる。

【0099】

また、第1の非晶質半導体膜として、代表的には、プラズマCVD法で水素化非晶質シリコン(a−Si:H)膜を100nmの厚さに形成する。この時、プラズマCVD装置において、電源周波数13〜70MHz、好ましくは27〜60MHzで行えばよい。電源周波数27〜60MHzを使うことにより成膜速度を向上することが可能となり、成膜された膜は、欠陥密度の少ないa−Si膜となるため好ましい。その他、この第1の非晶質半導体膜には、微結晶半導体膜、非晶質シリコンゲルマニウム膜などの非晶質構造を有する化合物半導体膜を適用することも可能である。

【0100】

また、上記絶縁膜及び上記第1の非晶質半導体膜のプラズマCVD法による成膜において、100〜100kHzのパルス変調放電を行えば、プラズマCVD法の気相反応によるパーティクルの発生を防ぐことができ、成膜においてピンホールの発生を防ぐことができるため好ましい。

【0101】

また、本実施例では、一導電型の不純物元素を含有する半導体膜として、n型を付与する不純物元素を含む第2の非晶質半導体膜を20〜80nmの厚さで形成する。例えば、n型の不純物元素を含有するa−Si:H膜を形成すれば良く、そのためにシラン(SiH4)に対して0.1〜5%の濃度でフォスフィン(PH3)を添加する。或いは、n型を付与する不純物元素を含む第2の非晶質半導体膜106に代えて水素化微結晶シリコン膜(μc−Si:H)を用いても良い。

【0102】

これらの膜は、反応ガスを適宣切り替えることにより、連続的に形成することができる。また、プラズマCVD装置において、同一の反応室または複数の反応室を用い、これらの膜を大気に曝すことなく連続して積層させることもできる。このように、大気に曝さないで連続成膜することで特に、第1の非晶質半導体膜への不純物の混入を防止することができる。

【0103】

なお、本実施例は、実施例1乃至3のいずれか一と組み合わせることが可能である。

【0104】

[実施例5]

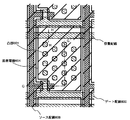

実施例1または実施例4では、絶縁膜、第1の非晶質半導体膜、n型を付与する不純物元素を含む第2の非晶質半導体膜、第1の導電膜を順次、連続的に積層する例を示した。このように連続的に成膜する場合において使用する複数のチャンバーを備えた装置の一例を図10に示した。

【0105】

図10に本実施例で示す装置(連続成膜システム)の上面からみた概要を示す。図10において、10〜15が気密性を有するチャンバーである。各チャンバーには、真空排気ポンプ、不活性ガス導入系が配置されている。

【0106】

10、15で示されるチャンバーは、試料(処理基板)30をシステムに搬入するためのロードロック室である。11は絶縁膜104を成膜するための第1のチャンバーである。12は第1の非晶質半導体膜105を成膜するための第2のチャンバーである。13はn型を付与する第2の非晶質半導体膜106を成膜するための第3のチャンバーである。14は第1の導電膜107を成膜するための第4のチャンバーである。また、20は各チャンバーに対して共通に配置された試料の共通室である。

【0107】

以下に動作の一例を示す。

【0108】

最初、全てのチャンバーは、一度高真空状態に真空引きされた後、さらに不活性ガス、ここでは窒素によりパージされている状態(常圧)とする。また、全てのゲート弁22〜27を閉鎖した状態とする。

【0109】

まず、処理基板は多数枚が収納されたカセット28ごとロードロック室10に搬入される。カセットの搬入後、図示しないロードロック室の扉を閉鎖する。この状態において、ゲート弁22を開けてカセットから処理基板30を1枚取り出し、ロボットアーム21によって共通室20に取り出す。この際、共通室において位置合わせが行われる。なお、この基板30は実施例1に従って得られた配線101、102、103が形成されたものを用いた。

【0110】

ここでゲート弁22を閉鎖し、次いでゲート弁23を開ける。そして第1のチャンバー11へ処理基板30を移送する。第1のチャンバー内では150℃から300℃の温度で成膜処理を行い、絶縁膜104を得る。なお、絶縁膜としては、窒化珪素膜、酸化珪素膜、窒化酸化珪素膜、またはこれらの積層膜等を使用することができる。本実施例では単層の窒化珪素膜を採用しているが、二層または三層以上の積層構造としてもよい。なお、ここではプラズマCVD法が可能なチャンバーを用いたが、ターゲットを用いたスパッタ法が可能なチャンバーを用いても良い。

【0111】

絶縁膜の成膜終了後、処理基板はロボットアームによって共通室に引き出され、第2のチャンバー12に移送される。第2のチャンバー内では第1のチャンバーと同様に150℃〜300℃の温度で成膜処理を行い、プラズマCVD法で第1の非晶質半導体膜105を得る。なお、第1の非晶質半導体膜としては、微結晶半導体膜、非晶質ゲルマニウム膜、非晶質シリコンゲルマニウム膜、またはこれらの積層膜等を使用することができる。また、第1の非晶質半導体膜の形成温度を350℃〜500℃として水素濃度を低減するための熱処理を省略してもよい。なお、ここではプラズマCVD法が可能なチャンバーを用いたが、ターゲットを用いたスパッタ法が可能なチャンバーを用いても良い。

【0112】

第1の非晶質半導体膜の成膜終了後、処理基板は共通室に引き出され、第3のチャンバー13に移送される。第3のチャンバー内では第2のチャンバーと同様に150℃〜300℃の温度で成膜処理を行い、プラズマCVD法でn型を付与する不純物元素(PまたはAs)を含む第2の非晶質半導体膜106を得る。なお、ここではプラズマCVD法が可能なチャンバーを用いたが、ターゲットを用いたスパッタ法が可能なチャンバーを用いても良い。

【0113】

n型を付与する不純物元素を含む第2の非晶質半導体膜の成膜終了後、処理基板は共通室に引き出され、第4のチャンバー14に移送される。第4のチャンバー内では金属ターゲットを用いたスパッタ法で第1の導電膜107を得る。

【0114】

このようにして四層が連続的に成膜された被処理基板はロボットアームによってロードロック室15に移送されカセット29に収納される。

【0115】

なお、図10に示した装置は一例に過ぎないことはいうまでもない。また、本実施例は実施例1乃至4のいずれか一と自由に組み合わせることが必要である。

【0116】

[実施例6]

実施例5では、複数のチャンバーを用いて連続的に積層する例を示したが、本実施例では図11に示した装置を用いて一つのチャンバー内で高真空を保ったまま連続的に積層した。

【0117】

本実施例では図11に示した装置システムを用いた。図11において、40は処理基板、50は共通室、44、46はロードロック室、45はチャンバー、42、43はカセットである。本実施例では基板搬送時に生じる汚染を防ぐために同一チャンバーで積層形成した。

【0118】

本実施例は実施例1乃至4のいずれか一と自由に組み合わせることができる。

【0119】

ただし、実施例1に適用する場合には、チャンバー45に複数のターゲットを用意し、順次、反応ガスを入れ替えて絶縁膜104、第1の非晶質半導体膜105、n型を付与する不純物元素を含む第2の非晶質半導体膜106、第1の導電膜107を積層形成すればよい。

【0120】

また、実施例4に適用する場合には、順次、反応ガスを入れ替えて絶縁膜104、第1の非晶質半導体膜105、n型を付与する不純物元素を含む第2の非晶質半導体膜106を積層形成すればよい。

【0121】

[実施例7]

実施例1では、n型を付与する不純物元素を含む第2の非晶質半導体膜をスパッタ法で形成した例を示したが、本実施例では、プラズマCVD法で形成する例を示す。なお、本実施例はn型を付与する不純物元素を含む第2の非晶質半導体膜の形成方法以外は実施例1と同一であるため異なる点についてのみ以下に述べる。

【0122】

プラズマCVD法を用い、反応ガスとしてシラン(SiH4)に対して0.1〜5%の濃度でフォスフィン(PH3)を添加すれば、n型を付与する不純物元素を含む第2の非晶質半導体膜を得ることができる。

【0123】

[実施例8]

実施例7では、n型を付与する不純物元素を含む第2の非晶質半導体膜をプラズマCVD法で形成した例を示したが、本実施例では、n型を付与する不純物元素を含む微結晶半導体膜を用いた例を示す。

【0124】

形成温度を80〜300℃、好ましくは140〜200℃とし、水素で希釈したシランガス(SiH4:H2=1:10〜100)とフォスフィン(PH3)との混合ガスを反応ガスとし、ガス圧を0.1〜10Torr、放電電力を10〜300mW/cm2とすることで微結晶珪素膜を得ることができる。また、この微結晶珪素膜成膜後にリンをプラズマドーピングして形成してもよい。

【0125】

[実施例9]

図12はCOG方式を用いて、電気光学装置の組み立てる様子を模式的に示す図である。第1の基板には画素領域803、外部入出力端子804、接続配線805が形成されている。点線で囲まれた領域は、走査線側のICチップ貼り合わせ領域801とデータ線側のICチップ貼り合わせ領域802である。第2の基板808には対向電極809が形成され、シール材810で第1の基板800と貼り合わせる。シール材810の内側には液晶が封入され液晶層811を形成する。第1の基板と第2の基板とは所定の間隔を持って貼り合わせるが、ネマチック液晶の場合には3〜8μm、スメチック液晶の場合には1〜4μmとする。

【0126】

ICチップ806、807は、データ線側と走査線側とで回路構成が異なる。ICチップは第1の基板に実装する。外部入出力端子804には、外部から電源及び制御信号を入力するためのFPC(フレキシブルプリント配線板:Flexible Printed Circuit)812を貼り付ける。FPC812の接着強度を高めるために補強板813を設けても良い。こうして電気光学装置を完成させることができる。ICチップは第1の基板に実装する前に電気検査を行えば電気光学装置の最終工程での歩留まりを向上させることができ、また、信頼性を高めることができる。

【0127】

また、ICチップを第1の基板上に実装する方法は、異方性導電材を用いた接続方法やワイヤボンディング方式などを採用することができる。図13にその一例を示す。図13(A)は第1の基板901にICチップ908が異方性導電材を用いて実装する例を示している。第1の基板901上には画素領域902、引出線906、接続配線及び入出力端子907が設けられている。第2の基板はシール材904で第1の基板901と接着されており、その間に液晶層905が設けられている。

【0128】

また、接続配線及び入出力端子907の一方の端にはFPC912が異方性導電材で接着されている。異方性導電材は樹脂915と表面にAuなどがメッキされた数十〜数百μm径の導電性粒子914から成り、導電性粒子914により接続配線及び入出力端子907とFPC912に形成された配線913とが電気的に接続されている。ICチップ908も同様に異方性導電材で第1の基板に接着され、樹脂911中に混入された導電性粒子910により、ICチップ908に設けられた入出力端子909と引出線906または接続配線及び入出力端子907と電気的に接続されている。

【0129】

また、図13(B)で示すように第1の基板にICチップを接着材916で固定して、Auワイヤ917によりスティックドライバの入出力端子と引出線または接続配線とを接続しても良い。そして樹脂918で封止する。

【0130】

ICチップの実装方法は図12及び図13を基にした方法に限定されるものではなく、ここで説明した以外にも公知のCOG方法やワイヤボンディング方法、或いはTAB方法を用いることが可能である。

【0131】

本実施例は実施例1、3乃至8のいずれか一と自由に組み合わせることが可能である。

【0132】

[実施例10]

実施例1では透過型の電気光学装置に対応するアクティブマトリクス基板の作製方法を示したが、本実施例では図14、図15を用いて、反射型の液晶表示装置に適用する例について示す。図14は断面図であり、図15は上面図であり、図15中の鎖線G―G’で切断した面での断面構造とH−H’で切断した面での断面構造を図14に示した。

【0133】

まず、絶縁表面を有する基板を用意する。本実施例は、基板としてガラス基板、石英基板、プラスチック基板のような透光性を有する基板の他に、反射型であるため、半導体基板、ステンレス基板、セラミック基板などに絶縁膜を形成したものでもよい。

【0134】

次いで、基板上に金属材料からなる導電膜を形成した後、第1のマスク(フォトマスク1枚目)でゲート配線600及びを凸部601形成する。この凸部は、ゲート配線とソース配線とで囲まれた領域、即ち画素電極が形成されて表示領域となる領域に配置する。なお、凸部601の形状は特に限定されず、径方向の断面が多角形であってもよいし、左右対称でない形状であってもよい。例えば、凸部601の形状は円柱状や角柱状であってもよいし、円錐状や角錐状であってもよい。また、凸部601を規則的に配置しても不規則に配置してもよい。本実施例ではゲート配線がテーパー形状であることが望ましいため、凸部601もテーパー形状を有する角錐形状となった。

【0135】

次いで、絶縁膜(ゲート絶縁膜)602、第1の非晶質半導体膜、n型を付与する不純物元素を含む第2の非晶質半導体膜、及び第1の導電膜を順次、積層形成する。なお、非晶質半導体膜に代えて微結晶半導体膜を用いてもよいし、n型を付与する不純物元素を含む非晶質半導体膜に代えてn型を付与する不純物元素を含む微結晶半導体膜を用いてもよい。さらに、これらの膜はスパッタ法やプラズマCVD法を用いて複数のチャンバー内または同一チャンバー内で連続的に大気に曝すことなく形成することができる。大気に曝さないようにすることで不純物の混入を防止できる。

【0136】

上記絶縁膜602は、凸部601が形成された基板上に形成され、表面に凸凹を有している。

【0137】

次いで、第2のマスク(フォトマスク2枚目)で上記第1の導電膜をパターニングして第1の導電膜からなる配線(後にソース配線及び電極(ドレイン電極)となる)を形成し、上記第2の非晶質半導体膜をパターニングしてn型を付与する不純物元素を含む第2の非晶質半導体膜を形成し、上記第1の非晶質半導体膜をパターニングして第1の非晶質半導体膜を形成する。

【0138】

その後、全面に第2の導電膜を成膜する。なお、第2の導電膜としては、反射性を有する導電膜を用いる。

【0139】

次いで、第3のマスク(フォトマスク3枚目)で上記第2の導電膜をパターニングして第2の導電膜からなる画素電極604を形成し、上記配線をパターニングしてソース配線608及び電極(ドレイン電極)609を形成し、n型を付与する不純物元素を含む第2の非晶質半導体膜をパターニングしてn型を付与する不純物元素を含む第2の非晶質半導体膜からなるソース領域606及びドレイン領域607を形成し、上記第1の非晶質半導体膜を一部除去して第1の非晶質半導体膜605を形成する。

【0140】

こうして、凸部601上に形成された絶縁膜の表面は凸凹を有し、この凸凹を表面に有する絶縁膜602上に画素電極604が形成されるので、画素電極604の表面に凹凸を持たせて光散乱性を図ることができる。

【0141】

また、本実施例の構成とすることで、画素TFT部の作製する際、フォトリソグラフィー技術で使用するフォトマスクの数を3枚とすることができる。従来では、凸凹部を形成する工程を増やす必要があったが、本実施例はゲート配線と同時に凸部を作製するため、全く工程を増やすことなく画素電極に凸凹部を形成することができた。

【0142】

なお、本実施例は実施例2乃至8のいずれか一と自由に組み合わせることができる。

【0143】

[実施例11]

本実施例は、基板としてプラスチック基板(或いはプラスチックフィルム)を用いた例を示す。なお、本実施例は基板としてプラスチック基板を用いること以外は実施例1とほぼ同一であるため異なる点についてのみ以下に述べる。

【0144】

プラスチック基板の材料としてはPES(ポリエチレンサルファイル)、PC(ポリカーボネート)、PET(ポリエチレンテレフタレート)もしくはPEN(ポリエチレンナフタレート)を用いることができる。

【0145】

プラスチック基板を用いて実施例1に従って作製すればアクティブマトリクス基板が完成する。ただし、絶縁膜、第1の非晶質半導体膜、及びn型を付与する不純物元素を含む第2の非晶質半導体膜は、成膜温度が比較的低温であるスパッタ法で形成することが望ましい。

【0146】

プラスチック基板上に特性の良好なTFTを設けることができるとともに、さらなる表示装置の軽量化を図ることができる。また、基板がプラスチックであるため、フレキシブルな電気光学装置にすることも可能である。また、組み立てが容易となる。

【0147】

なお、本実施例は、実施例1〜3、9、10のいずれか一と自由に組合せることができる。

【0148】

[実施例12]

本実施例では、画素電極と同じ材料膜を利用して画素部以外の領域に保護回路を設ける例を図16を用いて示す。

【0149】

図16(A)において、701は配線であり、画素部から延長されたゲート配線またはソース配線または容量配線を示している。また、第2の導電膜からなる電極701は、配線701が形成されていない領域を埋めるように、且つ配線701と重ならないように形成される。本実施例は、マスクを増やすことなく保護回路を形成する例を示したが、特に図16(A)の構成に限定されないことは言うまでもない。例えば、マスクを増やして保護ダイオードやTFTで保護回路を形成してもよい。

【0150】

また、図16(B)は等価回路図を示している。

【0151】

このような構成とすることで、製造工程において製造装置と絶縁体基板との摩擦による静電気の発生を防止することができる。特に、製造工程で行われる液晶配向処理のラビング時に発生する静電気からTFT等を保護することができる。

【0152】

なお、本実施例は実施例1乃至11のいずれか一と自由に組み合わせることができる。

【0153】

[実施例13]

上記各実施例1乃至12のいずれか一を実施して形成されたボトムゲート型TFTは様々な電気光学装置(アクティブマトリクス型液晶ディスプレイ、アクティブマトリクス型ELディスプレイ、アクティブマトリクス型ECディスプレイ)に用いることができる。即ち、それら電気光学装置を表示部に組み込んだ電子機器全てに本願発明を実施できる。

【0154】

その様な電子機器としては、ビデオカメラ、デジタルカメラ、プロジェクター(リア型またはフロント型)、ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、カーナビゲーション、カーステレオ、パーソナルコンピュータ、携帯情報端末(モバイルコンピュータ、携帯電話または電子書籍等)などが挙げられる。それらの一例を図17及び図18に示す。

【0155】

図17(A)はパーソナルコンピュータであり、本体2001、画像入力部2002、表示部2003、キーボード2004等を含む。本発明を表示部2003に適用することができる。

【0156】

図17(B)はビデオカメラであり、本体2101、表示部2102、音声入力部2103、操作スイッチ2104、バッテリー2105、受像部2106等を含む。本発明を表示部2102に適用することができる。

【0157】

図17(C)はモバイルコンピュータ(モービルコンピュータ)であり、本体2201、カメラ部2202、受像部2203、操作スイッチ2204、表示部2205等を含む。本発明は表示部2205に適用できる。

【0158】

図17(D)はゴーグル型ディスプレイであり、本体2301、表示部2302、アーム部2303等を含む。本発明は表示部2302に適用することができる。

【0159】

図17(E)はプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレーヤーであり、本体2401、表示部2402、スピーカ部2403、記録媒体2404、操作スイッチ2405等を含む。なお、このプレーヤーは記録媒体としてDVD(Digtial Versatile Disc)、CD等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行うことができる。本発明は表示部2402に適用することができる。

【0160】

図17(F)はデジタルカメラであり、本体2501、表示部2502、接眼部2503、操作スイッチ2504、受像部(図示しない)等を含む。本願発明を表示部2502に適用することができる。

【0161】

図18(A)は携帯電話であり、本体2901、音声出力部2902、音声入力部2903、表示部2904、操作スイッチ2905、アンテナ2906等を含む。本願発明を表示部2904に適用することができる。

【0162】

図18(B)は携帯書籍(電子書籍)であり、本体3001、表示部3002、3003、記憶媒体3004、操作スイッチ3005、アンテナ3006等を含む。本発明は表示部3002、3003に適用することができる。

【0163】

図18(C)はディスプレイであり、本体3101、支持台3102、表示部3103等を含む。本発明は表示部3103に適用することができる。本発明のディスプレイは特に大画面化した場合において有利であり、対角10インチ以上(特に30インチ以上)のディスプレイには有利である。

【0164】

以上の様に、本願発明の適用範囲は極めて広く、あらゆる分野の電子機器に適用することが可能である。また、本実施例の電子機器は実施例1〜12のどのような組み合わせからなる構成を用いても実現することができる。

【0165】

【発明の効果】

本発明により、3回のフォトリソグラフィー工程により、3枚のフォトマスクを使用して、逆スタガ型のnチャネル型TFTを有する画素TFT部、及び保持容量を備えた電気光学装置を実現することができる。

【0166】

また、保護膜を形成した場合においては、4回のフォトリソグラフィー工程により、4枚のフォトマスクを使用して、無機絶縁膜で保護された逆スタガ型のnチャネル型TFTを有する画素TFT部、及び保持容量を備えた電気光学装置を実現することができる。

【図面の簡単な説明】

【図1】 本願発明の上面図を示す図。

【図2】 アクティブマトリクス基板の作製工程を示す断面図。

【図3】 アクティブマトリクス基板の作製工程を示す断面図。

【図4】 アクティブマトリクス基板の作製工程を示す上面図。

【図5】 アクティブマトリクス基板の作製工程を示す上面図。

【図6】 液晶表示装置の画素部と入力端子部の配置を説明する上面図。

【図7】 液晶表示装置の実装構造を示す断面図。

【図8】 液晶表示装置の断面図。

【図9】 入力端子部の上面図及び断面図。

【図10】 製造装置の上面図。

【図11】 製造装置の上面図。

【図12】 液晶表示装置の実装を示す図。

【図13】 液晶表示装置の実装構造を示す断面図。

【図14】 反射型の電気光学装置の構造断面図。

【図15】 反射型の電気光学装置の上面図。

【図16】 保護回路の上面図及び回路図。

【図17】 電子機器の一例を示す図。

【図18】 電子機器の一例を示す図。

Claims (7)

- 第1のマスクを用いて、絶縁基板上にゲート配線を形成し、

前記絶縁基板及びゲート配線上にゲート絶縁膜、第1の非晶質半導体膜、n型を付与する不純物元素を含む第2の非晶質半導体膜、及び第1の導電膜を順に形成し、

第2のマスクを用いて、前記第1の非晶質半導体膜、n型を付与する不純物元素を含む第2の非晶質半導体膜、及び第1の導電膜をパターニングすることによって、薄膜トランジスタ、ソース配線及びソース配線端子部に用いる積層膜を形成し、

前記ゲート絶縁膜及び前記積層膜上に第2の導電膜を形成し、

第3のマスクを用いて前記積層膜及び前記第2の導電膜をパターニングすることによって、前記第1の導電膜はドレイン電極とソース電極に分離され、前記第2の非晶質半導体膜は前記ドレイン電極下の領域と前記ソース配線下の領域とに分離され、前記ドレイン電極及び前記ゲート絶縁膜上に前記第2の導電膜からなる画素電極が形成され、前記ソース配線及びソース配線端子部上に前記第2の導電膜からなる導電膜が形成される液晶表示装置の作製方法であって、

前記ソース配線及びソース配線端子部上に形成される前記第2の導電膜からなる導電膜は、前記ソース配線及び前記ソース配線端子部と接し、かつ前記ソース配線及び前記ソース配線端子部全体を覆うように形成されていることを特徴とする液晶表示装置の作製方法。 - 第1のマスクを用いて、絶縁基板上にゲート配線、容量配線、及び凸部を形成し、

前記絶縁基板、ゲート配線、容量配線、及び凸部上にゲート絶縁膜、第1の非晶質半導体膜、n型を付与する不純物元素を含む第2の非晶質半導体膜、及び第1の導電膜を順に形成し、

第2のマスクを用いて、前記第1の非晶質半導体膜、n型を付与する不純物元素を含む第2の非晶質半導体膜、及び第1の導電膜をパターニングすることによって、薄膜トランジスタ、ソース配線及びソース配線端子部に用いる積層膜を形成するとともに、前記容量配線上の前記第1の非晶質半導体膜、n型を付与する不純物元素を含む第2の非晶質半導体膜、及び第1の導電膜は除去し、

前記ゲート絶縁膜、前記積層膜、前記容量配線及び凸部上に第2の導電膜を形成し、

第3のマスクを用いて前記積層膜及び前記第2の導電膜をパターニングすることによって、前記第1の導電膜はドレイン電極とソース電極に分離され、前記第2の非晶質半導体膜は前記ドレイン電極下の領域と前記ソース配線下の領域とに分離され、前記ドレイン電極、前記ゲート絶縁膜、前記容量配線及び凸部上に前記第2の導電膜からなる画素電極が形成され、前記ソース配線及びソース配線端子部上に前記第2の導電膜からなる導電膜が形成される液晶表示装置の作製方法であって、

前記ソース配線及びソース配線端子部上に形成される前記第2の導電膜からなる導電膜は、前記ソース配線及び前記ソース配線端子部と接し、かつ前記ソース配線及び前記ソース配線端子部全体を覆うように形成されていることを特徴とする液晶表示装置の作製方法。 - 第1のマスクを用いて、絶縁基板上にゲート配線を形成し、

前記絶縁基板及びゲート配線上にゲート絶縁膜、微結晶半導体膜、n型を付与する不純物元素を含む非晶質半導体膜、及び第1の導電膜を順に形成し、

第2のマスクを用いて、前記微結晶半導体膜、n型を付与する不純物元素を含む非晶質半導体膜、及び第1の導電膜をパターニングすることによって、薄膜トランジスタ、ソース配線及びソース配線端子部に用いる積層膜を形成し、

前記ゲート絶縁膜及び前記積層膜上に第2の導電膜を形成し、

第3のマスクを用いて前記積層膜及び前記第2の導電膜をパターニングすることによって、前記第1の導電膜はドレイン電極とソース電極に分離され、前記非晶質半導体膜は前 記ドレイン電極下の領域と前記ソース配線下の領域とに分離され、前記ドレイン電極及び前記ゲート絶縁膜上に前記第2の導電膜からなる画素電極が形成され、前記ソース配線及びソース配線端子部上に前記第2の導電膜からなる導電膜が形成される液晶表示装置の作製方法であって、

前記ソース配線及びソース配線端子部上に形成される前記第2の導電膜からなる導電膜は、前記ソース配線及び前記ソース配線端子部と接し、かつ前記ソース配線及び前記ソース配線端子部全体を覆うように形成されていることを特徴とする液晶表示装置の作製方法。 - 第1のマスクを用いて、絶縁基板上にゲート配線、容量配線及び凸部を形成し、

前記絶縁基板、ゲート配線、容量配線及び凸部上にゲート絶縁膜、微結晶半導体膜、n型を付与する不純物元素を含む非晶質半導体膜、及び第1の導電膜を順に形成し、

第2のマスクを用いて、前記微結晶半導体膜、n型を付与する不純物元素を含む非晶質半導体膜、及び第1の導電膜をパターニングすることによって、薄膜トランジスタ、ソース配線及びソース配線端子部に用いる積層膜を形成するとともに、前記容量配線上の前記微結晶半導体膜、n型を付与する不純物元素を含む非晶質半導体膜、及び第1の導電膜は除去し、

前記パターニングされた第1の導電膜、容量配線及び凸部上に、前記ゲート絶縁膜を介して第2の導電膜を形成し、

第3のマスクを用いて前記第2の導電膜をパターニングすることによって、前記第1の導電膜はドレイン電極とソース電極に分離され、前記非晶質半導体膜は前記ドレイン電極下の領域と前記ソース配線下の領域とに分離され、前記ドレイン電極、前記ゲート絶縁膜、前記容量配線及び凸部上に前記第2の導電膜からなる画素電極が形成され、前記ソース配線及びソース配線端子部上に前記第2の導電膜からなる導電膜が形成される液晶表示装置の作製方法であって、

前記ソース配線及びソース配線端子部上に形成される前記第2の導電膜からなる導電膜は、前記ソース配線及び前記ソース配線端子部と接し、かつ前記ソース配線及び前記ソース配線端子部全体を覆うように形成されていることを特徴とする液晶表示装置の作製方法。 - 請求項1乃至請求項4のいずれか一において、

前記ゲート配線は、Alと、Cu、Ti、Mo、W、Ta、NdまたはCrから選ばれた元素を主成分とする膜とを組み合わせた積層膜からなることを特徴とする液晶表示装置の作製方法。 - 請求項2又は請求項4において、

前記容量配線は、Alと、Cu、Ti、Mo、W、Ta、NdまたはCrから選ばれた元素を主成分とする膜とを組み合わせた積層膜からなることを特徴とする液晶表示装置の作製方法。 - 請求項1乃至請求項6のいずれか一において、

前記ソース配線、及び前記ドレイン電極は、Ti膜、Al膜、Ti膜でなる積層膜から形成されていることを特徴とする液晶表示装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003047613A JP4118706B2 (ja) | 2003-02-25 | 2003-02-25 | 液晶表示装置の作製方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003047613A JP4118706B2 (ja) | 2003-02-25 | 2003-02-25 | 液晶表示装置の作製方法 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000069519A Division JP4118485B2 (ja) | 2000-03-13 | 2000-03-13 | 半導体装置の作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003234355A JP2003234355A (ja) | 2003-08-22 |

| JP2003234355A5 JP2003234355A5 (ja) | 2007-03-29 |

| JP4118706B2 true JP4118706B2 (ja) | 2008-07-16 |

Family

ID=27785817

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003047613A Expired - Fee Related JP4118706B2 (ja) | 2003-02-25 | 2003-02-25 | 液晶表示装置の作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4118706B2 (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI227806B (en) * | 2002-05-30 | 2005-02-11 | Fujitsu Display Tech | Substrate for liquid crystal display, liquid crystal display having the same, and method of manufacturing the same |

| WO2005048223A1 (en) | 2003-11-14 | 2005-05-26 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device and method for manufacturing the same |

| CN1914737B (zh) | 2003-11-14 | 2010-06-16 | 株式会社半导体能源研究所 | 半导体元件及其制造方法和液晶显示器及其制造方法 |

| JP2005229098A (ja) * | 2003-12-12 | 2005-08-25 | Semiconductor Energy Lab Co Ltd | 半導体装置及び半導体装置の作製方法 |

| US7768405B2 (en) | 2003-12-12 | 2010-08-03 | Semiconductor Energy Laboratory Co., Ltd | Semiconductor device and manufacturing method thereof |

| KR101061844B1 (ko) | 2004-06-29 | 2011-09-02 | 삼성전자주식회사 | 박막 표시판의 제조 방법 |

| KR20060064388A (ko) * | 2004-12-08 | 2006-06-13 | 삼성전자주식회사 | 박막 트랜지스터, 이의 제조 방법, 이를 갖는 표시장치 및표시장치의 제조 방법 |

| JP5064747B2 (ja) * | 2005-09-29 | 2012-10-31 | 株式会社半導体エネルギー研究所 | 半導体装置、電気泳動表示装置、表示モジュール、電子機器、及び半導体装置の作製方法 |

| EP1995787A3 (en) | 2005-09-29 | 2012-01-18 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device having oxide semiconductor layer and manufacturing method therof |

| KR101448903B1 (ko) | 2007-10-23 | 2014-10-13 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체장치 및 그의 제작방법 |

| JP5377940B2 (ja) * | 2007-12-03 | 2013-12-25 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US8314765B2 (en) | 2008-06-17 | 2012-11-20 | Semiconductor Energy Laboratory Co., Ltd. | Driver circuit, display device, and electronic device |

| KR101915251B1 (ko) | 2009-10-16 | 2018-11-06 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| KR101837102B1 (ko) * | 2009-10-30 | 2018-03-09 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

-

2003

- 2003-02-25 JP JP2003047613A patent/JP4118706B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003234355A (ja) | 2003-08-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4118485B2 (ja) | 半導体装置の作製方法 | |

| JP4683688B2 (ja) | 液晶表示装置の作製方法 | |

| US9786687B2 (en) | Semiconductor device and manufacturing method thereof | |

| JP4393662B2 (ja) | 液晶表示装置の作製方法 | |

| JP4118706B2 (ja) | 液晶表示装置の作製方法 | |

| JP2008209931A (ja) | 液晶表示装置 | |

| JP2007134730A (ja) | 表示装置 | |

| JP4128588B2 (ja) | 液晶表示装置 | |

| JP2006235638A (ja) | 液晶表示装置 | |

| JP4118705B2 (ja) | 半導体装置の作製方法 | |

| JP5604477B2 (ja) | 表示装置 | |

| JP4118704B2 (ja) | 液晶表示装置の作製方法 | |

| JP2006259757A (ja) | 液晶表示装置、アクティブマトリクス型液晶ディスプレイ、及びパーソナルコンピュータ | |

| JP5732552B2 (ja) | 表示装置 | |

| JP2012053467A (ja) | 液晶表示装置 | |

| JP2006227639A (ja) | 液晶表示装置、アクティブマトリクス型液晶ディスプレイ、及びパーソナルコンピュータ | |

| JP2006215579A (ja) | 液晶表示装置、アクティブマトリクス型液晶ディスプレイ、及びパーソナルコンピュータ | |

| JP2010049288A (ja) | 液晶表示装置 | |

| JP2007058247A (ja) | マルチドメイン型液晶表示装置、及びパーソナルコンピュータ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070207 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070207 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070724 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070925 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080212 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080311 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080422 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080423 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110502 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110502 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110502 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120502 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120502 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130502 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130502 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140502 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |