JP5613620B2 - 配線基板及びその製造方法 - Google Patents

配線基板及びその製造方法 Download PDFInfo

- Publication number

- JP5613620B2 JP5613620B2 JP2011119619A JP2011119619A JP5613620B2 JP 5613620 B2 JP5613620 B2 JP 5613620B2 JP 2011119619 A JP2011119619 A JP 2011119619A JP 2011119619 A JP2011119619 A JP 2011119619A JP 5613620 B2 JP5613620 B2 JP 5613620B2

- Authority

- JP

- Japan

- Prior art keywords

- conductive layer

- groove

- layer

- substrate body

- wiring board

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

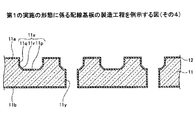

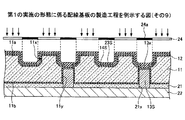

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

- H05K3/42—Plated through-holes or plated via connections

- H05K3/425—Plated through-holes or plated via connections characterised by the sequence of steps for plating the through-holes or via connections in relation to the conductive pattern

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/01—Manufacture or treatment

- H10W70/05—Manufacture or treatment of insulating or insulated package substrates, or of interposers, or of redistribution layers

- H10W70/095—Manufacture or treatment of insulating or insulated package substrates, or of interposers, or of redistribution layers of vias therein

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

- H10W70/62—Insulating or insulated package substrates; Interposers; Redistribution layers characterised by their interconnections

- H10W70/63—Vias, e.g. via plugs

- H10W70/635—Through-vias

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

- H10W70/62—Insulating or insulated package substrates; Interposers; Redistribution layers characterised by their interconnections

- H10W70/65—Shapes or dispositions of interconnections

- H10W70/652—Cross-sectional shapes

- H10W70/6525—Cross-sectional shapes for securing the interconnections to the substrate, e.g. to prevent peeling

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

- H10W70/67—Insulating or insulated package substrates; Interposers; Redistribution layers characterised by their insulating layers or insulating parts

- H10W70/69—Insulating materials thereof

- H10W70/698—Semiconductor materials that are electrically insulating, e.g. undoped silicon

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/03—Use of materials for the substrate

- H05K1/0306—Inorganic insulating substrates, e.g. ceramic, glass

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/03—Conductive materials

- H05K2201/0332—Structure of the conductor

- H05K2201/0335—Layered conductors or foils

- H05K2201/0347—Overplating, e.g. for reinforcing conductors or bumps; Plating over filled vias

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

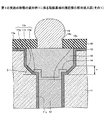

- H05K2201/095—Conductive through-holes or vias

- H05K2201/09563—Metal filled via

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09818—Shape or layout details not covered by a single group of H05K2201/09009 - H05K2201/09809

- H05K2201/09827—Tapered, e.g. tapered hole, via or groove

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09818—Shape or layout details not covered by a single group of H05K2201/09009 - H05K2201/09809

- H05K2201/09845—Stepped hole, via, edge, bump or conductor

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09818—Shape or layout details not covered by a single group of H05K2201/09009 - H05K2201/09809

- H05K2201/09854—Hole or via having special cross-section, e.g. elliptical

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/01—Tools for processing; Objects used during processing

- H05K2203/0147—Carriers and holders

- H05K2203/0152—Temporary metallic carrier, e.g. for transferring material

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/15—Position of the PCB during processing

- H05K2203/1572—Processing both sides of a PCB by the same process; Providing a similar arrangement of components on both sides; Making interlayer connections from two sides

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/0011—Working of insulating substrates or insulating layers

- H05K3/0017—Etching of the substrate by chemical or physical means

- H05K3/002—Etching of the substrate by chemical or physical means by liquid chemical etching

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49117—Conductor or circuit manufacturing

- Y10T29/49124—On flat or curved insulated base, e.g., printed circuit, etc.

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Printing Elements For Providing Electric Connections Between Printed Circuits (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011119619A JP5613620B2 (ja) | 2011-05-27 | 2011-05-27 | 配線基板及びその製造方法 |

| US13/480,985 US8729407B2 (en) | 2011-05-27 | 2012-05-25 | Wiring substrate and method for manufacturing wiring substrate |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011119619A JP5613620B2 (ja) | 2011-05-27 | 2011-05-27 | 配線基板及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2012248703A JP2012248703A (ja) | 2012-12-13 |

| JP2012248703A5 JP2012248703A5 (enExample) | 2014-04-24 |

| JP5613620B2 true JP5613620B2 (ja) | 2014-10-29 |

Family

ID=47218463

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011119619A Active JP5613620B2 (ja) | 2011-05-27 | 2011-05-27 | 配線基板及びその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8729407B2 (enExample) |

| JP (1) | JP5613620B2 (enExample) |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8304863B2 (en) * | 2010-02-09 | 2012-11-06 | International Business Machines Corporation | Electromigration immune through-substrate vias |

| US20140306349A1 (en) * | 2013-04-11 | 2014-10-16 | Qualcomm Incorporated | Low cost interposer comprising an oxidation layer |

| JP2014236102A (ja) * | 2013-05-31 | 2014-12-15 | 凸版印刷株式会社 | 貫通電極付き配線基板、その製造方法及び半導体装置 |

| JP6286169B2 (ja) * | 2013-09-26 | 2018-02-28 | 新光電気工業株式会社 | 配線基板及びその製造方法 |

| US10777839B2 (en) * | 2014-03-28 | 2020-09-15 | Infineon Technologies Ag | Method for forming a battery element, a battery element and a battery |

| TWI553804B (zh) * | 2014-06-06 | 2016-10-11 | 矽品精密工業股份有限公司 | 基板結構之製法 |

| KR102211741B1 (ko) * | 2014-07-21 | 2021-02-03 | 삼성전기주식회사 | 인쇄회로기판 및 인쇄회로기판의 제조 방법 |

| JP2016213283A (ja) * | 2015-05-01 | 2016-12-15 | ソニー株式会社 | 製造方法、および貫通電極付配線基板 |

| EP3109199B1 (fr) * | 2015-06-25 | 2022-05-11 | Nivarox-FAR S.A. | Piece a base de silicium avec au moins un chanfrein et son procede de fabrication |

| TWI625991B (zh) * | 2016-10-17 | 2018-06-01 | 南亞電路板股份有限公司 | 電路板結構與其製造方法 |

| JP7230462B2 (ja) * | 2017-12-04 | 2023-03-01 | ローム株式会社 | 半導体装置およびその製造方法 |

| WO2019171470A1 (ja) * | 2018-03-06 | 2019-09-12 | 株式会社 東芝 | コンデンサ及びその製造方法 |

| CN111508893B (zh) * | 2019-01-31 | 2023-12-15 | 奥特斯(中国)有限公司 | 部件承载件及制造部件承载件的方法 |

| CN112956284B (zh) * | 2019-08-22 | 2023-04-14 | 宏启胜精密电子(秦皇岛)有限公司 | 透明电路板及其制造方法 |

| WO2021155222A1 (en) * | 2020-01-31 | 2021-08-05 | Ttm Technologies Inc. | Printed circuit board assemblies with engineered thermal paths and methods of manufacturing |

| US11901266B2 (en) * | 2021-08-30 | 2024-02-13 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor device structure and method for forming the same |

| US20250142730A1 (en) * | 2023-10-30 | 2025-05-01 | Tong Hsing Electronic Industries, Ltd. | Power component submount and manufacturing method thereof |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4340832B2 (ja) * | 2001-05-10 | 2009-10-07 | 日立電線株式会社 | 配線基板及びその製造方法 |

| JP2003318178A (ja) * | 2002-04-24 | 2003-11-07 | Seiko Epson Corp | 半導体装置及びその製造方法、回路基板並びに電子機器 |

| JP4056854B2 (ja) | 2002-11-05 | 2008-03-05 | 新光電気工業株式会社 | 半導体装置の製造方法 |

| US7088003B2 (en) * | 2004-02-19 | 2006-08-08 | International Business Machines Corporation | Structures and methods for integration of ultralow-k dielectrics with improved reliability |

| JP5038612B2 (ja) * | 2005-09-29 | 2012-10-03 | 富士通セミコンダクター株式会社 | 半導体装置 |

| JP5154789B2 (ja) * | 2006-12-21 | 2013-02-27 | ルネサスエレクトロニクス株式会社 | 半導体装置並びに半導体装置の製造方法 |

| US8334202B2 (en) * | 2009-11-03 | 2012-12-18 | Infineon Technologies Ag | Device fabricated using an electroplating process |

| KR20120048991A (ko) * | 2010-11-08 | 2012-05-16 | 삼성전자주식회사 | 반도체 장치 및 그 제조 방법 |

| US9018094B2 (en) * | 2011-03-07 | 2015-04-28 | Invensas Corporation | Substrates with through vias with conductive features for connection to integrated circuit elements, and methods for forming through vias in substrates |

| JP2013105753A (ja) * | 2011-11-10 | 2013-05-30 | Toshiba Corp | 半導体装置の製造方法 |

-

2011

- 2011-05-27 JP JP2011119619A patent/JP5613620B2/ja active Active

-

2012

- 2012-05-25 US US13/480,985 patent/US8729407B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2012248703A (ja) | 2012-12-13 |

| US8729407B2 (en) | 2014-05-20 |

| US20120298413A1 (en) | 2012-11-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5613620B2 (ja) | 配線基板及びその製造方法 | |

| JP5730654B2 (ja) | 配線基板及びその製造方法 | |

| TWI460836B (zh) | 半導體晶片及其製造方法 | |

| CN1332431C (zh) | 半导体器件的制造方法 | |

| JP5259197B2 (ja) | 半導体装置及びその製造方法 | |

| JP6286169B2 (ja) | 配線基板及びその製造方法 | |

| TWI587470B (zh) | 基板、基板之製造方法、半導體裝置及電子機器 | |

| TWI607495B (zh) | 半導體元件結構及其形成方法 | |

| JP2012099548A (ja) | 貫通配線基板の製造方法及び貫通配線基板 | |

| JP4601686B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| US9241403B2 (en) | Method for producing a structure for microelectronic device assembly | |

| JP5663607B2 (ja) | 半導体装置 | |

| JP5775747B2 (ja) | 配線基板及びその製造方法 | |

| JP2010232400A (ja) | 半導体基板と半導体基板の製造方法および半導体パッケージ | |

| CN209119091U (zh) | 铜柱凸点结构 | |

| JP2003068779A (ja) | 半導体装置及びその製造方法 | |

| JP2005123325A (ja) | 半導体装置、回路基板、及び電子機器 | |

| JP5873145B2 (ja) | 貫通配線基板の製造方法 | |

| CN105070698B (zh) | 晶圆级焊锡微凸点及其制作方法 | |

| CN1667801B (zh) | 半导体装置及其制造方法 | |

| CN107994045B (zh) | 影像传感芯片的封装结构及其制作方法 | |

| TW201501256A (zh) | 中介板及其製法 | |

| JP2011238742A (ja) | 配線基板の製造方法及び配線基板 | |

| TWI339416B (en) | Method of forming conductive bumps with different diameters |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140310 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140310 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140902 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140908 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5613620 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |