JP5613620B2 - 配線基板及びその製造方法 - Google Patents

配線基板及びその製造方法 Download PDFInfo

- Publication number

- JP5613620B2 JP5613620B2 JP2011119619A JP2011119619A JP5613620B2 JP 5613620 B2 JP5613620 B2 JP 5613620B2 JP 2011119619 A JP2011119619 A JP 2011119619A JP 2011119619 A JP2011119619 A JP 2011119619A JP 5613620 B2 JP5613620 B2 JP 5613620B2

- Authority

- JP

- Japan

- Prior art keywords

- conductive layer

- groove

- layer

- substrate body

- wiring board

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 38

- 239000000758 substrate Substances 0.000 claims description 106

- 229910052751 metal Inorganic materials 0.000 claims description 39

- 239000002184 metal Substances 0.000 claims description 39

- 238000000034 method Methods 0.000 claims description 39

- 239000010949 copper Substances 0.000 claims description 33

- 229910052802 copper Inorganic materials 0.000 claims description 20

- 239000010703 silicon Substances 0.000 claims description 19

- 229910052710 silicon Inorganic materials 0.000 claims description 19

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 claims description 18

- 238000009713 electroplating Methods 0.000 claims description 16

- 238000005530 etching Methods 0.000 claims description 15

- 230000002093 peripheral effect Effects 0.000 claims description 8

- 239000010936 titanium Substances 0.000 claims description 8

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 claims description 4

- 229910052719 titanium Inorganic materials 0.000 claims description 4

- 239000012670 alkaline solution Substances 0.000 claims description 2

- 239000010410 layer Substances 0.000 description 432

- 238000007747 plating Methods 0.000 description 22

- 230000007547 defect Effects 0.000 description 20

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 17

- 239000000463 material Substances 0.000 description 17

- 238000010586 diagram Methods 0.000 description 14

- 230000004048 modification Effects 0.000 description 14

- 238000012986 modification Methods 0.000 description 14

- KWYUFKZDYYNOTN-UHFFFAOYSA-M Potassium hydroxide Chemical compound [OH-].[K+] KWYUFKZDYYNOTN-UHFFFAOYSA-M 0.000 description 12

- 239000004065 semiconductor Substances 0.000 description 10

- 239000012790 adhesive layer Substances 0.000 description 9

- 229910052581 Si3N4 Inorganic materials 0.000 description 8

- 229910004298 SiO 2 Inorganic materials 0.000 description 8

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 8

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 8

- WGTYBPLFGIVFAS-UHFFFAOYSA-M tetramethylammonium hydroxide Chemical compound [OH-].C[N+](C)(C)C WGTYBPLFGIVFAS-UHFFFAOYSA-M 0.000 description 8

- 230000000052 comparative effect Effects 0.000 description 7

- 239000004642 Polyimide Substances 0.000 description 6

- 229920001721 polyimide Polymers 0.000 description 6

- 230000008646 thermal stress Effects 0.000 description 6

- 235000012239 silicon dioxide Nutrition 0.000 description 5

- 229910045601 alloy Inorganic materials 0.000 description 4

- 239000000956 alloy Substances 0.000 description 4

- 229920005989 resin Polymers 0.000 description 4

- 239000011347 resin Substances 0.000 description 4

- 239000000377 silicon dioxide Substances 0.000 description 4

- 229910000679 solder Inorganic materials 0.000 description 4

- 239000011800 void material Substances 0.000 description 4

- 239000007864 aqueous solution Substances 0.000 description 3

- 239000013078 crystal Substances 0.000 description 3

- 239000003822 epoxy resin Substances 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 150000003949 imides Chemical class 0.000 description 3

- 238000005498 polishing Methods 0.000 description 3

- 229920000647 polyepoxide Polymers 0.000 description 3

- 239000011342 resin composition Substances 0.000 description 3

- 239000000126 substance Substances 0.000 description 3

- 229910052718 tin Inorganic materials 0.000 description 3

- 229910018503 SF6 Inorganic materials 0.000 description 2

- ROOXNKNUYICQNP-UHFFFAOYSA-N ammonium persulfate Chemical compound [NH4+].[NH4+].[O-]S(=O)(=O)OOS([O-])(=O)=O ROOXNKNUYICQNP-UHFFFAOYSA-N 0.000 description 2

- 238000004380 ashing Methods 0.000 description 2

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 239000005388 borosilicate glass Substances 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- ORTQZVOHEJQUHG-UHFFFAOYSA-L copper(II) chloride Chemical compound Cl[Cu]Cl ORTQZVOHEJQUHG-UHFFFAOYSA-L 0.000 description 2

- 238000000708 deep reactive-ion etching Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000009413 insulation Methods 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 238000001020 plasma etching Methods 0.000 description 2

- 229920002577 polybenzoxazole Polymers 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- SFZCNBIFKDRMGX-UHFFFAOYSA-N sulfur hexafluoride Chemical compound FS(F)(F)(F)(F)F SFZCNBIFKDRMGX-UHFFFAOYSA-N 0.000 description 2

- 229960000909 sulfur hexafluoride Drugs 0.000 description 2

- 229910021578 Iron(III) chloride Inorganic materials 0.000 description 1

- 229910007637 SnAg Inorganic materials 0.000 description 1

- 229910001870 ammonium persulfate Inorganic materials 0.000 description 1

- KGBXLFKZBHKPEV-UHFFFAOYSA-N boric acid Chemical compound OB(O)O KGBXLFKZBHKPEV-UHFFFAOYSA-N 0.000 description 1

- 239000004327 boric acid Substances 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 229960003280 cupric chloride Drugs 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- RBTARNINKXHZNM-UHFFFAOYSA-K iron trichloride Chemical compound Cl[Fe](Cl)Cl RBTARNINKXHZNM-UHFFFAOYSA-K 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 230000002040 relaxant effect Effects 0.000 description 1

- RMAQACBXLXPBSY-UHFFFAOYSA-N silicic acid Chemical compound O[Si](O)(O)O RMAQACBXLXPBSY-UHFFFAOYSA-N 0.000 description 1

- 230000035882 stress Effects 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

- H05K3/42—Plated through-holes or plated via connections

- H05K3/425—Plated through-holes or plated via connections characterised by the sequence of steps for plating the through-holes or via connections in relation to the conductive pattern

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4846—Leads on or in insulating or insulated substrates, e.g. metallisation

- H01L21/486—Via connections through the substrate with or without pins

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/12—Mountings, e.g. non-detachable insulating substrates

- H01L23/14—Mountings, e.g. non-detachable insulating substrates characterised by the material or its electrical properties

- H01L23/147—Semiconductor insulating substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49827—Via connections through the substrates, e.g. pins going through the substrate, coaxial cables

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/03—Use of materials for the substrate

- H05K1/0306—Inorganic insulating substrates, e.g. ceramic, glass

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/03—Conductive materials

- H05K2201/0332—Structure of the conductor

- H05K2201/0335—Layered conductors or foils

- H05K2201/0347—Overplating, e.g. for reinforcing conductors or bumps; Plating over filled vias

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/095—Conductive through-holes or vias

- H05K2201/09563—Metal filled via

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09818—Shape or layout details not covered by a single group of H05K2201/09009 - H05K2201/09809

- H05K2201/09827—Tapered, e.g. tapered hole, via or groove

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09818—Shape or layout details not covered by a single group of H05K2201/09009 - H05K2201/09809

- H05K2201/09845—Stepped hole, via, edge, bump or conductor

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09818—Shape or layout details not covered by a single group of H05K2201/09009 - H05K2201/09809

- H05K2201/09854—Hole or via having special cross-section, e.g. elliptical

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/01—Tools for processing; Objects used during processing

- H05K2203/0147—Carriers and holders

- H05K2203/0152—Temporary metallic carrier, e.g. for transferring material

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/15—Position of the PCB during processing

- H05K2203/1572—Processing both sides of a PCB by the same process; Providing a similar arrangement of components on both sides; Making interlayer connections from two sides

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/0011—Working of insulating substrates or insulating layers

- H05K3/0017—Etching of the substrate by chemical or physical means

- H05K3/002—Etching of the substrate by chemical or physical means by liquid chemical etching

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49117—Conductor or circuit manufacturing

- Y10T29/49124—On flat or curved insulated base, e.g., printed circuit, etc.

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Ceramic Engineering (AREA)

- Printing Elements For Providing Electric Connections Between Printed Circuits (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Description

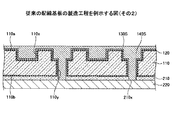

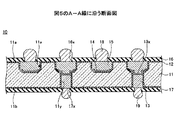

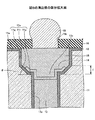

[第1の実施の形態に係る配線基板の構造]

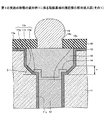

始めに、第1の実施の形態に係る配線基板の構造について説明する。図5は、第1の実施の形態に係る配線基板を例示する平面図である。図6は、図5のA−A線に沿う断面図である。図7は、図6の溝近傍の部分拡大図である。なお、説明の便宜のため、図5において、第2絶縁層16及び第1外部接続端子18は省略されている。

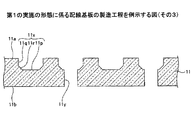

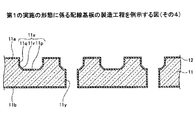

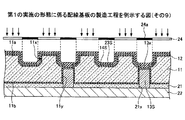

次に、第1の実施の形態に係る配線基板の製造方法について説明する。図8〜図22は、第1の実施の形態に係る配線基板の製造工程を例示する図である。

第1の実施の形態の変形例1では、第1の実施の形態とは第2導電層14の形成位置が異なる例を示す。なお、第1の実施の形態の変形例1において、既に説明した実施の形態と同一構成部品についての説明は省略する。

第1の実施の形態の変形例2では、第1の実施の形態とは出荷形態の異なる配線基板を例示する。なお、第1の実施の形態の変形例2において、既に説明した実施の形態と同一構成部品についての説明は省略する。

11 基板本体

11a 基板本体の一方の面

11b 基板本体の他方の面

11j、11k、11m、11x 溝

11p 内底面

11q 内側面

11r 傾斜面

11y 貫通孔

12 第1絶縁層

13、13S 第1導電層

13x 凹部

14、14A、14B、14S 第2導電層

15、15S 第3導電層

16 第2絶縁層

16x、17x、21x 開口部

17 第3絶縁層

18 第1外部接続端子

19 第2外部接続端子

21 接着層

22 金属板

23、23A、23S レジスト層

24 マスク

24a 遮光部

T 高さ

θ 角度

Claims (13)

- 基板本体と、

前記基板本体の一方の面側に開口する溝であって、内底面の周縁部と内側面の一端部とが、前記内底面に対して末広がりに傾斜する傾斜面を介して連続する溝と、

一端が前記内底面に連通し、他端が前記基板本体の他方の面側に開口する貫通孔と、

前記他端側から前記貫通孔の少なくとも一部を充填する第1導電層と、

前記第1導電層の前記溝側の面を被覆し、前記溝内の前記内側面を除く部分の少なくとも一部に延在する第2導電層と、

前記第2導電層を被覆し、前記溝を充填する第3導電層と、を有する配線基板。 - 前記第2導電層は、前記内底面の全部、及び前記傾斜面の少なくとも一部に延在する請求項1記載の配線基板。

- 前記第1導電層の前記溝側の面は、前記内底面に対して前記基板本体の他方の面側に窪んだ位置にある請求項1又は2記載の配線基板。

- 前記第1導電層の前記溝側の面の反対面は前記貫通孔の前記他端から露出し、前記反対面は前記基板本体の他方の面と略面一である請求項1乃至3の何れか一項記載の配線基板。

- 前記第3導電層は前記溝の開口部から露出し、前記開口部から露出する面は前記基板本体の一方の面と略面一である請求項1乃至4の何れか一項記載の配線基板。

- 前記内側面は、前記内底面に対して垂直である請求項1乃至5の何れか一項記載の配線基板。

- 前記貫通孔の径は、前記溝の幅よりも小さい請求項1乃至6の何れか一項記載の配線基板。

- 前記第2導電層は、チタン(Ti)膜と銅(Cu)膜が前記第1導電層上に順次積層した導電層である請求項1乃至7の何れか一項記載の配線基板。

- 基板本体に、前記基板本体の一方の面側に開口する溝であって、内底面の周縁部と内側面の一端部とが、前記内底面に対して末広がりに傾斜する傾斜面を介して連続する溝を形成する第1工程と、

前記基板本体に、一端が前記内底面に連通し、他端が前記基板本体の他方の面側に開口する貫通孔を形成する第2工程と、

前記基板本体の前記他方の面に金属層を形成する第3工程と、

前記金属層を給電層とする電解めっき法により、前記他端側から前記貫通孔の少なくとも一部を充填する第1導電層を形成する第4工程と、

前記第1導電層の前記溝側の面を被覆し、前記溝内の前記内側面を除く部分の少なくとも一部に延在する第2導電層を形成する第5工程と、

前記金属層、前記第1導電層、及び前記第2導電層を給電層とする電解めっき法により、前記第2導電層を被覆し、前記溝を充填する第3導電層を形成する第6工程と、

前記金属層を除去する第7工程と、を有する配線基板の製造方法。 - 前記第5工程では、前記内底面の全部及び前記傾斜面の少なくとも一部に延在する第2導電層を形成する請求項9記載の配線基板の製造方法。

- 前記第4工程では、前記第1導電層の前記溝側の面が、前記内底面に対して前記基板本体の他方の面側に窪んだ位置となるように第1導電層を形成する請求項9又は10記載の配線基板の製造方法。

- 前記第1工程は、アルカリ性溶液を用いた異方性エッチングにより前記傾斜面を形成する工程を含む請求項9乃至11の何れか一項記載の配線基板の製造方法。

- 前記基板本体はシリコンからなり、

前記基板本体の一方の面は、前記シリコンの(100)面又は(110)面である請求項9乃至12の何れか一項記載の配線基板の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011119619A JP5613620B2 (ja) | 2011-05-27 | 2011-05-27 | 配線基板及びその製造方法 |

| US13/480,985 US8729407B2 (en) | 2011-05-27 | 2012-05-25 | Wiring substrate and method for manufacturing wiring substrate |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011119619A JP5613620B2 (ja) | 2011-05-27 | 2011-05-27 | 配線基板及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2012248703A JP2012248703A (ja) | 2012-12-13 |

| JP2012248703A5 JP2012248703A5 (ja) | 2014-04-24 |

| JP5613620B2 true JP5613620B2 (ja) | 2014-10-29 |

Family

ID=47218463

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011119619A Active JP5613620B2 (ja) | 2011-05-27 | 2011-05-27 | 配線基板及びその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8729407B2 (ja) |

| JP (1) | JP5613620B2 (ja) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8304863B2 (en) * | 2010-02-09 | 2012-11-06 | International Business Machines Corporation | Electromigration immune through-substrate vias |

| US20140306349A1 (en) * | 2013-04-11 | 2014-10-16 | Qualcomm Incorporated | Low cost interposer comprising an oxidation layer |

| JP2014236102A (ja) * | 2013-05-31 | 2014-12-15 | 凸版印刷株式会社 | 貫通電極付き配線基板、その製造方法及び半導体装置 |

| JP6286169B2 (ja) * | 2013-09-26 | 2018-02-28 | 新光電気工業株式会社 | 配線基板及びその製造方法 |

| US10777839B2 (en) * | 2014-03-28 | 2020-09-15 | Infineon Technologies Ag | Method for forming a battery element, a battery element and a battery |

| TWI553804B (zh) * | 2014-06-06 | 2016-10-11 | 矽品精密工業股份有限公司 | 基板結構之製法 |

| KR102211741B1 (ko) * | 2014-07-21 | 2021-02-03 | 삼성전기주식회사 | 인쇄회로기판 및 인쇄회로기판의 제조 방법 |

| JP2016213283A (ja) * | 2015-05-01 | 2016-12-15 | ソニー株式会社 | 製造方法、および貫通電極付配線基板 |

| EP3109199B1 (fr) * | 2015-06-25 | 2022-05-11 | Nivarox-FAR S.A. | Piece a base de silicium avec au moins un chanfrein et son procede de fabrication |

| TWI625991B (zh) * | 2016-10-17 | 2018-06-01 | 南亞電路板股份有限公司 | 電路板結構與其製造方法 |

| JP7230462B2 (ja) * | 2017-12-04 | 2023-03-01 | ローム株式会社 | 半導体装置およびその製造方法 |

| WO2019171470A1 (ja) * | 2018-03-06 | 2019-09-12 | 株式会社 東芝 | コンデンサ及びその製造方法 |

| CN111508893B (zh) * | 2019-01-31 | 2023-12-15 | 奥特斯(中国)有限公司 | 部件承载件及制造部件承载件的方法 |

| CN112956284B (zh) * | 2019-08-22 | 2023-04-14 | 宏启胜精密电子(秦皇岛)有限公司 | 透明电路板及其制造方法 |

| CN113574974B (zh) * | 2020-01-31 | 2024-06-28 | 迅达科技公司 | 具有工程化的热路径的印刷电路板组件以及制造方法 |

| US11901266B2 (en) * | 2021-08-30 | 2024-02-13 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor device structure and method for forming the same |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4340832B2 (ja) * | 2001-05-10 | 2009-10-07 | 日立電線株式会社 | 配線基板及びその製造方法 |

| JP2003318178A (ja) * | 2002-04-24 | 2003-11-07 | Seiko Epson Corp | 半導体装置及びその製造方法、回路基板並びに電子機器 |

| JP4056854B2 (ja) | 2002-11-05 | 2008-03-05 | 新光電気工業株式会社 | 半導体装置の製造方法 |

| US7088003B2 (en) * | 2004-02-19 | 2006-08-08 | International Business Machines Corporation | Structures and methods for integration of ultralow-k dielectrics with improved reliability |

| JP5038612B2 (ja) * | 2005-09-29 | 2012-10-03 | 富士通セミコンダクター株式会社 | 半導体装置 |

| JP5154789B2 (ja) * | 2006-12-21 | 2013-02-27 | ルネサスエレクトロニクス株式会社 | 半導体装置並びに半導体装置の製造方法 |

| US8334202B2 (en) * | 2009-11-03 | 2012-12-18 | Infineon Technologies Ag | Device fabricated using an electroplating process |

| KR20120048991A (ko) * | 2010-11-08 | 2012-05-16 | 삼성전자주식회사 | 반도체 장치 및 그 제조 방법 |

| US9018094B2 (en) * | 2011-03-07 | 2015-04-28 | Invensas Corporation | Substrates with through vias with conductive features for connection to integrated circuit elements, and methods for forming through vias in substrates |

| JP2013105753A (ja) * | 2011-11-10 | 2013-05-30 | Toshiba Corp | 半導体装置の製造方法 |

-

2011

- 2011-05-27 JP JP2011119619A patent/JP5613620B2/ja active Active

-

2012

- 2012-05-25 US US13/480,985 patent/US8729407B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2012248703A (ja) | 2012-12-13 |

| US8729407B2 (en) | 2014-05-20 |

| US20120298413A1 (en) | 2012-11-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5613620B2 (ja) | 配線基板及びその製造方法 | |

| JP5730654B2 (ja) | 配線基板及びその製造方法 | |

| TWI460836B (zh) | 半導體晶片及其製造方法 | |

| JP5259197B2 (ja) | 半導体装置及びその製造方法 | |

| TWI587470B (zh) | 基板、基板之製造方法、半導體裝置及電子機器 | |

| JP6286169B2 (ja) | 配線基板及びその製造方法 | |

| JP3972846B2 (ja) | 半導体装置の製造方法 | |

| JP4922193B2 (ja) | 自己整合ウェハまたはチップ構造、自己整合積層構造およびそれを製造する方法 | |

| TWI607495B (zh) | 半導體元件結構及其形成方法 | |

| WO2012057200A1 (ja) | 貫通配線基板の製造方法及び貫通配線基板 | |

| JP4564166B2 (ja) | ウエハ・パッシベーション層の形成方法 | |

| JP5663607B2 (ja) | 半導体装置 | |

| JP4601686B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| US9241403B2 (en) | Method for producing a structure for microelectronic device assembly | |

| JP2008135763A (ja) | 半導体モジュール、電子機器および半導体モジュールの製造方法 | |

| JP5775747B2 (ja) | 配線基板及びその製造方法 | |

| JP2010232400A (ja) | 半導体基板と半導体基板の製造方法および半導体パッケージ | |

| JP3735547B2 (ja) | 半導体装置及びその製造方法 | |

| TW202125757A (zh) | 線路基板 | |

| JP5873145B2 (ja) | 貫通配線基板の製造方法 | |

| JP2005123325A (ja) | 半導体装置、回路基板、及び電子機器 | |

| WO2019128398A1 (zh) | 影像传感芯片的封装结构及其制作方法 | |

| TWI512923B (zh) | 中介板及其製法 | |

| JP2013062296A (ja) | 配線基板、及び半導体パッケージ | |

| CN104716055B (zh) | 晶圆级封装方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140310 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140310 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140902 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140908 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5613620 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |