JP5494147B2 - パワー半導体モジュール及びそれを用いた電力変換装置 - Google Patents

パワー半導体モジュール及びそれを用いた電力変換装置 Download PDFInfo

- Publication number

- JP5494147B2 JP5494147B2 JP2010087471A JP2010087471A JP5494147B2 JP 5494147 B2 JP5494147 B2 JP 5494147B2 JP 2010087471 A JP2010087471 A JP 2010087471A JP 2010087471 A JP2010087471 A JP 2010087471A JP 5494147 B2 JP5494147 B2 JP 5494147B2

- Authority

- JP

- Japan

- Prior art keywords

- igbt

- terminal

- semiconductor module

- collector

- emitter

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 52

- 238000006243 chemical reaction Methods 0.000 claims description 29

- 230000015556 catabolic process Effects 0.000 claims description 5

- 239000003990 capacitor Substances 0.000 description 16

- 238000010586 diagram Methods 0.000 description 13

- 230000002457 bidirectional effect Effects 0.000 description 12

- 230000000903 blocking effect Effects 0.000 description 7

- 239000004020 conductor Substances 0.000 description 7

- 101100004279 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) BDS1 gene Proteins 0.000 description 2

- 230000000694 effects Effects 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/07—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L29/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/58—Structural electrical arrangements for semiconductor devices not otherwise provided for, e.g. in combination with batteries

- H01L23/64—Impedance arrangements

- H01L23/645—Inductive arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M7/00—Conversion of ac power input into dc power output; Conversion of dc power input into ac power output

- H02M7/003—Constructional details, e.g. physical layout, assembly, wiring or busbar connections

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Inverter Devices (AREA)

- Power Conversion In General (AREA)

Description

サージ電圧ΔV=(L1+L2+L3)・di/dt ・・・式(2)

Edp :直流電源1の直流電圧

di/dt :IGBTターンオフ時のIGBTの電流変化率

L1+L2+L3: 各配線のインダクタンス値

一例として100AクラスのIGBTの場合、そのdi/dtは最大で2000A/μs程度となるため、L1+L2+L3=30nHとすると、式(1)によるサージ分(L1+L2+L3)・di/dtは60Vとなる。

特に、モジュールの大電流化(大容量化)を図った場合、モジュールは体積的に大きくなるため、必然的にモジュール内の配線長は長くなり、その結果配線インダクタンス値も大きくなる。また、スイッチング時のdi/dtも電流値にほぼ比例して大きくなるため、上記式(2)によるサージ電圧ΔVは、モジュールの電流定格の増加に対して指数的に増加する。そのため、1モジュールにて大容量化を図るのには限界が生じる。一方モジュールの並列接続による大容量化は通常的に実施されるが、1モジュールで構成する場合と比較してコストアップとなることや、並列接続間の電流のアンバランスを考慮しなければならないため、設計上ディレーティングしなければならないといった課題がある。

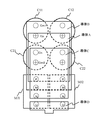

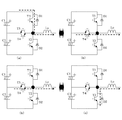

図1のモジュールMJ1は、コレクタが直流電源の正極に接続されるIGBTT1と、アノードが直流電源の負極に接続されるダイオードD2と、双方向スイッチ用逆阻止型IGBTT4を内蔵し、端子PにIGBTT1のコレクタが、端子Mに逆阻止型IGBTT4のコレクタが、端子Uに逆阻止型IGBTT1のエミッタとIGBTT1のエミッタとダイオードD2との接続点が、各々接続された構成である。

また、各モジュールの端子Uは導体Dで接続され、交流端子となる。

この構成を3個用いることにより、3相3レベルインバータや3相3レベルコンバータを構成できる。

図10の構成では、図1に示したパワー半導体モジュールMJ1と、図2に示したパワー半導体モジュールMJ2を用いて、最も高い電位Cp、最も低い電位Cn、及び中間の電位(Cm3、Cm4)をリアクトルLoに出力し、第2番目に高い電位(Cm5、Cm6)は双方向スイッチBDS2で、第4番目に高い電位(Cm1、Cm2)は双方向スイッチBDS1で、各々リアクトルLoに出力する構成である。モジュールMJ1とMJ2を隣接して配置することにより、3レベル変換回路と同様の効果が得られる。

また、3レベルインバータやコンバータと同様に、モジュールMJ1とMJ2の代わりに、モジュールMJ3とMJ4を、各々用いることができる。

3、5、7、8、T1、T2、T3a、T4a・・・IGBT

12、13、T3、T4・・・逆阻止型IGBT

BDS1、BDS2・・・双方向スイッチ

4、6、9、10、D1、D2、D3、D4・・・ダイオード

C1、C2、C3、C4、C11、C12、C21、C22・・・コンデンサ

Lo、Li・・・リアクトル 11・・・交流端子

CONV・・・コンバータ(PWM整流器) INV・・・インバータ

MJ0、MJ1、MJ2、MJ3、MJ4・・・半導体モジュール

導体A〜D・・・導体

Claims (10)

- 電圧形の3以上の多レベルの変換回路に適用するパワー半導体モジュールにおいて、第1のIGBTと、カソードが前記第1のIGBTのエミッタに接続されたダイオードと、エミッタが前記第1のIGBTのエミッタに接続された逆耐圧を有する第2のIGBTとを、一つのパッケージ内に収納し、前記第1のIGBTのコレクタと、前記第2のIGBTのコレクタと、前記第1のIGBTのエミッタと前記第2のIGBTのエミッタとの接続点と、前記ダイオードのアノードとを、各々外部端子としたことを特徴とするパワー半導体モジュール。

- 前記第1のIGBTのコレクタを直流電源の正極に接続する端子Pとし、前記第2のIGBTのコレクタを直流電源の中点に接続する端子Mとし、前記第1のIGBTのエミッタと前記第2のIGBTのエミッタとの接続点を出力端子Uとし、前記ダイオードのアノードを直流電源の負極に接続する端子Nとし、端子配列順序を、端子P、端子M、端子N、端子Uの順に直線状に配置したことを特徴とする請求項1に記載のパワー半導体モジュール。

- 電圧形の3以上の多レベルの変換回路に適用するパワー半導体モジュールにおいて、第1のIGBTと、アノードが前記第1のIGBTのコレクタに接続されたダイオードと、コレクタが前記第1のIGBTのコレクタに接続された逆耐圧を有する第2のIGBTとを、一つのパッケージ内に収納し、前記第1のIGBTのエミッタと、前記第2のIGBTのエミッタと、前記第1のIGBTのコレクタと前記第2のIGBTのコレクタとの接続点と、前記ダイオードのカソードとを、各々外部端子としたことを特徴とするパワー半導体モジュール。

- 前記第1のIGBTのエミッタを直流電源の負極に接続する端子Nとし、前記第2のIGBTのエミッタを直流電源の中点に接続する端子Mとし、前記第1のIGBTのコレクタと前記第2のIGBTのコレクタとの接続点を出力端子Uとし、前記ダイオードのカソードを直流電源の正極に接続する端子Pとし、端子配列順序を、端子P、端子M、端子N、端子Uの順に直線状に配置したことを特徴とする請求項3に記載のパワー半導体モジュール。

- 電圧形の3以上の多レベルの変換回路に適用するパワー半導体モジュールにおいて、第1のIGBTと、カソードが前記第1のIGBTのエミッタに接続された第1のダイオードと、一端が前記第1のIGBTのエミッタに接続された第2のダイオードと第2のIGBTとの直列回路とを、一つのパッケージ内に収納し、前記第1のIGBTのコレクタと、前記直列回路の他端と、前記第1のIGBTのエミッタと前記直列回路一端との接続点と、前記第1のダイオードのアノードとを、各々外部端子としたことを特徴とするパワー半導体モジュール。

- 前記第1のIGBTのコレクタを直流電源の正極に接続する端子Pとし、前記直列回路の他端を直流電源の中点に接続する端子Mとし、前記第1のIGBTのエミッタと前記直列回路の一端との接続点を出力端子Uとし、前記第1のダイオードのアノードを直流電源の負極に接続する端子Nとし、端子配列順序を、端子P、端子M、端子N、端子Uの順に直線状に配置したことを特徴とする請求項5に記載のパワー半導体モジュール。

- 電圧形の3以上の多レベルの変換回路に適用するパワー半導体モジュールにおいて、第1のIGBTと、アノードが前記第1のIGBTのコレクタに接続された第1のダイオードと、一端が前記第1のIGBTのコレクタに接続された第2のダイオードと第2のIGBTとの直列回路とを、一つのパッケージ内に収納し、前記第1のIGBTのエミッタと、前記直列回路の他端と、前記第1のIGBTのコレクタと前記直列回路との接続点と、前記第1のダイオードのカソードとを、各々外部端子としたことを特徴とするパワー半導体モジュール。

- 前記第1のIGBTのエミッタを直流電源の負極に接続する端子Nとし、前記直列回路の他端を直流電源の中点に接続する端子Mとし、前記第1のIGBTのコレクタと前記直列回路の一端との接続点を出力端子Uとし、前記第1のダイオードのカソードを直流電源の正極に接続する端子Pとし、端子配列順序を、端子P、端子M、端子N、端子Uの順に直線状に配置したことを特徴とする請求項7に記載のパワー半導体モジュール。

- 請求項2に記載したパワー半導体モジュールの端子配列と、請求項4に記載したパワー半導体モジュールの端子配列とが平行になるように前記二つのパワー半導体モジュールを隣接配置したことを特徴とする電力変換装置。

- 請求項6に記載したパワー半導体モジュールの端子配列と、請求項8に記載したパワー半導体モジュールの端子配列とが平行になるように前記二つのパワー半導体モジュールを隣接配置したことを特徴とする電力変換装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010087471A JP5494147B2 (ja) | 2010-04-06 | 2010-04-06 | パワー半導体モジュール及びそれを用いた電力変換装置 |

| CN201110051644.XA CN102214644B (zh) | 2010-04-06 | 2011-02-22 | 功率半导体器件及使用该器件的功率转换系统 |

| DE201110005184 DE102011005184A1 (de) | 2010-04-06 | 2011-03-07 | Leistungshalbleiterbauelement und dieses verwendendes Leistungsumformungssystem |

| US13/042,999 US8901602B2 (en) | 2010-04-06 | 2011-03-08 | Power semiconductor device and power conversion system using the device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010087471A JP5494147B2 (ja) | 2010-04-06 | 2010-04-06 | パワー半導体モジュール及びそれを用いた電力変換装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011223666A JP2011223666A (ja) | 2011-11-04 |

| JP2011223666A5 JP2011223666A5 (ja) | 2013-05-16 |

| JP5494147B2 true JP5494147B2 (ja) | 2014-05-14 |

Family

ID=44709495

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010087471A Active JP5494147B2 (ja) | 2010-04-06 | 2010-04-06 | パワー半導体モジュール及びそれを用いた電力変換装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US8901602B2 (ja) |

| JP (1) | JP5494147B2 (ja) |

| CN (1) | CN102214644B (ja) |

| DE (1) | DE102011005184A1 (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5493532B2 (ja) * | 2009-07-17 | 2014-05-14 | 富士電機株式会社 | 負荷駆動装置及びこれを使用した電気自動車 |

| JP5724314B2 (ja) * | 2010-11-16 | 2015-05-27 | 富士電機株式会社 | パワー半導体モジュール |

| JPWO2013099053A1 (ja) * | 2011-12-28 | 2015-04-30 | パナソニックIpマネジメント株式会社 | マルチレベルインバータ装置 |

| JP5891940B2 (ja) * | 2012-05-17 | 2016-03-23 | 富士電機株式会社 | 3レベルユニットインバータ |

| CN103904928A (zh) * | 2014-04-23 | 2014-07-02 | 西华大学 | 一种串并联混合三电平npp逆变拓扑单元及三电平逆变器 |

| CN105226975B (zh) * | 2014-06-06 | 2017-12-15 | 台达电子企业管理(上海)有限公司 | Tnpc逆变器装置及其桥臂短路检测方法 |

| JP6160780B2 (ja) * | 2014-08-26 | 2017-07-12 | 富士電機株式会社 | 3レベル電力変換装置 |

| JP6304017B2 (ja) * | 2014-12-18 | 2018-04-04 | 三菱電機株式会社 | 半導体装置 |

| CN109804465B (zh) | 2016-09-23 | 2022-11-29 | 三菱电机株式会社 | 电力用半导体模块以及电力用半导体装置 |

| JP6702429B2 (ja) * | 2016-11-16 | 2020-06-03 | 富士電機株式会社 | 半導体試験回路、半導体試験装置および半導体試験方法 |

| JP2018107857A (ja) * | 2016-12-22 | 2018-07-05 | 富士電機株式会社 | 電力変換装置 |

| JP2019180114A (ja) * | 2018-03-30 | 2019-10-17 | 本田技研工業株式会社 | 電力変換装置および電力変換装置用コンデンサ |

| CN108551159B (zh) * | 2018-04-08 | 2019-06-11 | 科华恒盛股份有限公司 | 逆阻型igbt短路保护电路、方法及系统和存储介质 |

| JP7039430B2 (ja) * | 2018-09-19 | 2022-03-22 | 株式会社東芝 | Ac/dcコンバータ |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3263317B2 (ja) * | 1996-06-18 | 2002-03-04 | 株式会社東芝 | スイッチングモジュールおよびモジュールを用いた電力変換器 |

| CN1242604A (zh) * | 1998-06-26 | 2000-01-26 | 株式会社东芝 | 半导体保护器件和功率转换器件 |

| JP2000216331A (ja) | 1999-01-25 | 2000-08-04 | Mitsubishi Electric Corp | パワ―半導体モジュ―ルおよびそれを用いた電力変換装置 |

| JP3873743B2 (ja) * | 1999-10-27 | 2007-01-24 | 株式会社日立製作所 | 電力変換装置 |

| JP2002026251A (ja) | 2000-07-11 | 2002-01-25 | Toshiba Corp | 半導体装置 |

| JP2002231883A (ja) | 2001-01-31 | 2002-08-16 | Hitachi Ltd | パワー半導体モジュールおよびそれを用いた電力変換装置 |

| JP2003018854A (ja) | 2001-07-02 | 2003-01-17 | Honda Motor Co Ltd | 共振形インバータ装置 |

| US6838925B1 (en) * | 2003-10-07 | 2005-01-04 | American Power Conversion Corporation | Three level inverter |

| US7289329B2 (en) * | 2004-06-04 | 2007-10-30 | Siemens Vdo Automotive Corporation | Integration of planar transformer and/or planar inductor with power switches in power converter |

| JP4728718B2 (ja) * | 2005-07-15 | 2011-07-20 | ローム株式会社 | 昇圧型スイッチングレギュレータおよびその制御回路ならびにそれを用いた電子機器 |

| JP2008193779A (ja) | 2007-02-02 | 2008-08-21 | Fuji Electric Systems Co Ltd | 半導体モジュール |

| JP2009022062A (ja) * | 2007-07-10 | 2009-01-29 | Fuji Electric Systems Co Ltd | 3レベル電力変換回路の配線構造 |

| JP5440335B2 (ja) * | 2010-04-06 | 2014-03-12 | 富士電機株式会社 | パワー半導体モジュール及びそれを用いた電力変換装置 |

| JP2012029429A (ja) * | 2010-07-22 | 2012-02-09 | Fuji Electric Co Ltd | 3レベル電力変換装置 |

| JP5724314B2 (ja) * | 2010-11-16 | 2015-05-27 | 富士電機株式会社 | パワー半導体モジュール |

-

2010

- 2010-04-06 JP JP2010087471A patent/JP5494147B2/ja active Active

-

2011

- 2011-02-22 CN CN201110051644.XA patent/CN102214644B/zh active Active

- 2011-03-07 DE DE201110005184 patent/DE102011005184A1/de active Pending

- 2011-03-08 US US13/042,999 patent/US8901602B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2011223666A (ja) | 2011-11-04 |

| US8901602B2 (en) | 2014-12-02 |

| DE102011005184A1 (de) | 2011-11-03 |

| CN102214644B (zh) | 2015-02-25 |

| CN102214644A (zh) | 2011-10-12 |

| US20110242860A1 (en) | 2011-10-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5494147B2 (ja) | パワー半導体モジュール及びそれを用いた電力変換装置 | |

| JP5440335B2 (ja) | パワー半導体モジュール及びそれを用いた電力変換装置 | |

| JP5369922B2 (ja) | 3レベル電力変換装置 | |

| JP5450635B2 (ja) | 電力変換装置 | |

| JP5457449B2 (ja) | 電力変換装置 | |

| JP5515386B2 (ja) | 3レベル電力変換器のスナバ回路 | |

| US20150155770A1 (en) | Five-level rectifier | |

| US10003280B2 (en) | Semiconductor module, upper and lower arm kit, and three-level inverter | |

| JP2008193779A (ja) | 半導体モジュール | |

| CN103797702A (zh) | 多电平功率转换电路 | |

| JP2015035902A (ja) | マルチレベル電力変換装置 | |

| JP2009022062A (ja) | 3レベル電力変換回路の配線構造 | |

| JP2011254672A (ja) | パワー半導体モジュール及びそれを用いた電力変換装置 | |

| JP5446541B2 (ja) | 電力変換装置 | |

| JP2015027170A (ja) | 直流/交流変換装置 | |

| KR20140110037A (ko) | 전력 변환 장치 | |

| JP5780907B2 (ja) | 電力変換装置 | |

| JP7446932B2 (ja) | 電力変換装置およびスイッチ装置 | |

| JP2011234544A (ja) | パワー半導体モジュール及びそれを用いた電力変換装置 | |

| JPWO2018127945A1 (ja) | 電力変換装置 | |

| JP5488244B2 (ja) | パワー半導体モジュール | |

| JP6175946B2 (ja) | 共振型インバータ装置 | |

| JP5423264B2 (ja) | 電力変換装置 | |

| JP2009005447A (ja) | 電力変換回路 | |

| JP5879705B2 (ja) | 電力変換装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130401 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130401 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131212 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140204 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140217 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5494147 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |