JP5459987B2 - 半導体基板及び半導体基板の作製方法、半導体装置、電子機器 - Google Patents

半導体基板及び半導体基板の作製方法、半導体装置、電子機器 Download PDFInfo

- Publication number

- JP5459987B2 JP5459987B2 JP2008166433A JP2008166433A JP5459987B2 JP 5459987 B2 JP5459987 B2 JP 5459987B2 JP 2008166433 A JP2008166433 A JP 2008166433A JP 2008166433 A JP2008166433 A JP 2008166433A JP 5459987 B2 JP5459987 B2 JP 5459987B2

- Authority

- JP

- Japan

- Prior art keywords

- single crystal

- crystal semiconductor

- layer

- substrate

- insulating

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 402

- 239000000758 substrate Substances 0.000 title claims description 321

- 238000004519 manufacturing process Methods 0.000 title claims description 37

- 239000013078 crystal Substances 0.000 claims description 285

- 238000000034 method Methods 0.000 claims description 90

- 230000001678 irradiating effect Effects 0.000 claims description 14

- 239000010410 layer Substances 0.000 description 466

- 239000010408 film Substances 0.000 description 85

- 239000012535 impurity Substances 0.000 description 84

- 150000002500 ions Chemical class 0.000 description 73

- 238000010438 heat treatment Methods 0.000 description 52

- 239000011521 glass Substances 0.000 description 41

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 36

- 239000000463 material Substances 0.000 description 31

- -1 hydrogen ions Chemical class 0.000 description 30

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 30

- 238000005530 etching Methods 0.000 description 29

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 28

- 239000010409 thin film Substances 0.000 description 28

- 229910052710 silicon Inorganic materials 0.000 description 27

- 239000010703 silicon Substances 0.000 description 27

- 229910052581 Si3N4 Inorganic materials 0.000 description 26

- 239000007789 gas Substances 0.000 description 26

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 26

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 23

- 229910052814 silicon oxide Inorganic materials 0.000 description 21

- 229920005989 resin Polymers 0.000 description 19

- 239000011347 resin Substances 0.000 description 19

- 230000008569 process Effects 0.000 description 18

- 239000001257 hydrogen Substances 0.000 description 17

- 229910052739 hydrogen Inorganic materials 0.000 description 17

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 14

- 238000005229 chemical vapour deposition Methods 0.000 description 14

- 230000004888 barrier function Effects 0.000 description 13

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 11

- 229910052731 fluorine Inorganic materials 0.000 description 11

- 239000011737 fluorine Substances 0.000 description 11

- 230000002093 peripheral effect Effects 0.000 description 11

- 239000010936 titanium Substances 0.000 description 11

- 230000004913 activation Effects 0.000 description 10

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 9

- 229920001940 conductive polymer Polymers 0.000 description 9

- 239000010949 copper Substances 0.000 description 9

- 150000001282 organosilanes Chemical class 0.000 description 9

- 239000001301 oxygen Substances 0.000 description 9

- 229910052760 oxygen Inorganic materials 0.000 description 9

- 238000000926 separation method Methods 0.000 description 9

- 229910052782 aluminium Inorganic materials 0.000 description 8

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 8

- 239000000460 chlorine Substances 0.000 description 8

- 229910052736 halogen Inorganic materials 0.000 description 8

- 239000011810 insulating material Substances 0.000 description 8

- 239000004973 liquid crystal related substance Substances 0.000 description 8

- 239000000203 mixture Substances 0.000 description 8

- 230000010355 oscillation Effects 0.000 description 8

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 8

- 239000002356 single layer Substances 0.000 description 8

- 239000000126 substance Substances 0.000 description 8

- 229910052783 alkali metal Inorganic materials 0.000 description 7

- 150000001340 alkali metals Chemical class 0.000 description 7

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 7

- 150000001342 alkaline earth metals Chemical class 0.000 description 7

- 230000008859 change Effects 0.000 description 7

- 150000001875 compounds Chemical class 0.000 description 7

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 7

- 229910052757 nitrogen Inorganic materials 0.000 description 7

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 6

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 6

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 6

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 6

- 239000003990 capacitor Substances 0.000 description 6

- 239000011651 chromium Substances 0.000 description 6

- 229910052802 copper Inorganic materials 0.000 description 6

- 229910003437 indium oxide Inorganic materials 0.000 description 6

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 6

- 238000010884 ion-beam technique Methods 0.000 description 6

- 229910052698 phosphorus Inorganic materials 0.000 description 6

- 239000011574 phosphorus Substances 0.000 description 6

- 229920001721 polyimide Polymers 0.000 description 6

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 5

- 239000004642 Polyimide Substances 0.000 description 5

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 5

- 239000000956 alloy Substances 0.000 description 5

- 230000015572 biosynthetic process Effects 0.000 description 5

- 239000010931 gold Substances 0.000 description 5

- 239000011261 inert gas Substances 0.000 description 5

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 5

- WZJUBBHODHNQPW-UHFFFAOYSA-N 2,4,6,8-tetramethyl-1,3,5,7,2$l^{3},4$l^{3},6$l^{3},8$l^{3}-tetraoxatetrasilocane Chemical compound C[Si]1O[Si](C)O[Si](C)O[Si](C)O1 WZJUBBHODHNQPW-UHFFFAOYSA-N 0.000 description 4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 4

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 4

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 4

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 4

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 4

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 4

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 4

- 239000002253 acid Substances 0.000 description 4

- 229910052786 argon Inorganic materials 0.000 description 4

- 239000012298 atmosphere Substances 0.000 description 4

- 125000004429 atom Chemical group 0.000 description 4

- 229910052796 boron Inorganic materials 0.000 description 4

- 229910052799 carbon Inorganic materials 0.000 description 4

- 239000004020 conductor Substances 0.000 description 4

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 4

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 4

- 239000002019 doping agent Substances 0.000 description 4

- 230000006870 function Effects 0.000 description 4

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 4

- 229910052737 gold Inorganic materials 0.000 description 4

- 229910052750 molybdenum Inorganic materials 0.000 description 4

- 239000011733 molybdenum Substances 0.000 description 4

- 229910052759 nickel Inorganic materials 0.000 description 4

- 239000010955 niobium Substances 0.000 description 4

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 4

- HMMGMWAXVFQUOA-UHFFFAOYSA-N octamethylcyclotetrasiloxane Chemical compound C[Si]1(C)O[Si](C)(C)O[Si](C)(C)O[Si](C)(C)O1 HMMGMWAXVFQUOA-UHFFFAOYSA-N 0.000 description 4

- 238000005498 polishing Methods 0.000 description 4

- 239000010979 ruby Substances 0.000 description 4

- 229910001750 ruby Inorganic materials 0.000 description 4

- 238000007789 sealing Methods 0.000 description 4

- 229910000077 silane Inorganic materials 0.000 description 4

- 230000003746 surface roughness Effects 0.000 description 4

- 229910052715 tantalum Inorganic materials 0.000 description 4

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 4

- 229910052719 titanium Inorganic materials 0.000 description 4

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- 229910052721 tungsten Inorganic materials 0.000 description 4

- 239000010937 tungsten Substances 0.000 description 4

- 229910001930 tungsten oxide Inorganic materials 0.000 description 4

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 3

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 3

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 3

- 229910045601 alloy Inorganic materials 0.000 description 3

- 239000002585 base Substances 0.000 description 3

- 229910052801 chlorine Inorganic materials 0.000 description 3

- 229910052804 chromium Inorganic materials 0.000 description 3

- 238000000576 coating method Methods 0.000 description 3

- 238000009826 distribution Methods 0.000 description 3

- 238000005401 electroluminescence Methods 0.000 description 3

- 229910052734 helium Inorganic materials 0.000 description 3

- 239000011229 interlayer Substances 0.000 description 3

- 239000011777 magnesium Substances 0.000 description 3

- 238000007726 management method Methods 0.000 description 3

- 229910052751 metal Inorganic materials 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 3

- 238000004806 packaging method and process Methods 0.000 description 3

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 3

- 229910052697 platinum Inorganic materials 0.000 description 3

- 238000003825 pressing Methods 0.000 description 3

- 238000011084 recovery Methods 0.000 description 3

- 229910052709 silver Inorganic materials 0.000 description 3

- 239000004332 silver Substances 0.000 description 3

- 239000002904 solvent Substances 0.000 description 3

- 125000001424 substituent group Chemical group 0.000 description 3

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 3

- 229910001868 water Inorganic materials 0.000 description 3

- QENGPZGAWFQWCZ-UHFFFAOYSA-N 3-Methylthiophene Chemical compound CC=1C=CSC=1 QENGPZGAWFQWCZ-UHFFFAOYSA-N 0.000 description 2

- PIGFYZPCRLYGLF-UHFFFAOYSA-N Aluminum nitride Chemical compound [Al]#N PIGFYZPCRLYGLF-UHFFFAOYSA-N 0.000 description 2

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 2

- 102100040844 Dual specificity protein kinase CLK2 Human genes 0.000 description 2

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- 101000749291 Homo sapiens Dual specificity protein kinase CLK2 Proteins 0.000 description 2

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 2

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 2

- 239000002841 Lewis acid Substances 0.000 description 2

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 2

- 229910052779 Neodymium Inorganic materials 0.000 description 2

- XYFCBTPGUUZFHI-UHFFFAOYSA-N Phosphine Chemical compound P XYFCBTPGUUZFHI-UHFFFAOYSA-N 0.000 description 2

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- 239000004952 Polyamide Substances 0.000 description 2

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 2

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 2

- 230000001133 acceleration Effects 0.000 description 2

- 239000005407 aluminoborosilicate glass Substances 0.000 description 2

- 239000005354 aluminosilicate glass Substances 0.000 description 2

- UBSJOWMHLJZVDJ-UHFFFAOYSA-N aluminum neodymium Chemical compound [Al].[Nd] UBSJOWMHLJZVDJ-UHFFFAOYSA-N 0.000 description 2

- 150000001408 amides Chemical class 0.000 description 2

- 238000004458 analytical method Methods 0.000 description 2

- 229910052788 barium Inorganic materials 0.000 description 2

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 2

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 2

- ILAHWRKJUDSMFH-UHFFFAOYSA-N boron tribromide Chemical compound BrB(Br)Br ILAHWRKJUDSMFH-UHFFFAOYSA-N 0.000 description 2

- WTEOIRVLGSZEPR-UHFFFAOYSA-N boron trifluoride Chemical compound FB(F)F WTEOIRVLGSZEPR-UHFFFAOYSA-N 0.000 description 2

- 239000005388 borosilicate glass Substances 0.000 description 2

- UIZLQMLDSWKZGC-UHFFFAOYSA-N cadmium helium Chemical compound [He].[Cd] UIZLQMLDSWKZGC-UHFFFAOYSA-N 0.000 description 2

- 239000000919 ceramic Substances 0.000 description 2

- 229910017052 cobalt Inorganic materials 0.000 description 2

- 239000010941 cobalt Substances 0.000 description 2

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 238000001816 cooling Methods 0.000 description 2

- 229920001577 copolymer Polymers 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 238000007872 degassing Methods 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 230000009977 dual effect Effects 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000001678 elastic recoil detection analysis Methods 0.000 description 2

- 230000002349 favourable effect Effects 0.000 description 2

- 125000001153 fluoro group Chemical group F* 0.000 description 2

- 235000013305 food Nutrition 0.000 description 2

- 229910052733 gallium Inorganic materials 0.000 description 2

- 229910052732 germanium Inorganic materials 0.000 description 2

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 2

- 150000002366 halogen compounds Chemical class 0.000 description 2

- 150000002367 halogens Chemical class 0.000 description 2

- 239000001307 helium Substances 0.000 description 2

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 2

- FFUAGWLWBBFQJT-UHFFFAOYSA-N hexamethyldisilazane Chemical compound C[Si](C)(C)N[Si](C)(C)C FFUAGWLWBBFQJT-UHFFFAOYSA-N 0.000 description 2

- 150000002431 hydrogen Chemical class 0.000 description 2

- 230000005660 hydrophilic surface Effects 0.000 description 2

- 238000002513 implantation Methods 0.000 description 2

- 229910052738 indium Inorganic materials 0.000 description 2

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 2

- 238000009616 inductively coupled plasma Methods 0.000 description 2

- 238000007689 inspection Methods 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 150000007517 lewis acids Chemical class 0.000 description 2

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 2

- 229910052749 magnesium Inorganic materials 0.000 description 2

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 2

- 229910052758 niobium Inorganic materials 0.000 description 2

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 239000012299 nitrogen atmosphere Substances 0.000 description 2

- RNVCVTLRINQCPJ-UHFFFAOYSA-N o-toluidine Chemical compound CC1=CC=CC=C1N RNVCVTLRINQCPJ-UHFFFAOYSA-N 0.000 description 2

- 125000000962 organic group Chemical group 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- VLTRZXGMWDSKGL-UHFFFAOYSA-N perchloric acid Chemical compound OCl(=O)(=O)=O VLTRZXGMWDSKGL-UHFFFAOYSA-N 0.000 description 2

- 238000001020 plasma etching Methods 0.000 description 2

- 238000009832 plasma treatment Methods 0.000 description 2

- 229920000058 polyacrylate Polymers 0.000 description 2

- 229920002647 polyamide Polymers 0.000 description 2

- 229920000767 polyaniline Polymers 0.000 description 2

- 229920000128 polypyrrole Polymers 0.000 description 2

- 229920001709 polysilazane Polymers 0.000 description 2

- 229920000123 polythiophene Polymers 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- 150000003254 radicals Chemical class 0.000 description 2

- 239000002994 raw material Substances 0.000 description 2

- 238000003303 reheating Methods 0.000 description 2

- 238000005001 rutherford backscattering spectroscopy Methods 0.000 description 2

- 229910052594 sapphire Inorganic materials 0.000 description 2

- 239000010980 sapphire Substances 0.000 description 2

- 239000000565 sealant Substances 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- 238000004381 surface treatment Methods 0.000 description 2

- 238000002834 transmittance Methods 0.000 description 2

- QQQSFSZALRVCSZ-UHFFFAOYSA-N triethoxysilane Chemical compound CCO[SiH](OCC)OCC QQQSFSZALRVCSZ-UHFFFAOYSA-N 0.000 description 2

- PQDJYEQOELDLCP-UHFFFAOYSA-N trimethylsilane Chemical compound C[SiH](C)C PQDJYEQOELDLCP-UHFFFAOYSA-N 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- 239000011787 zinc oxide Substances 0.000 description 2

- ZPOROQKDAPEMOL-UHFFFAOYSA-N 1h-pyrrol-3-ol Chemical compound OC=1C=CNC=1 ZPOROQKDAPEMOL-UHFFFAOYSA-N 0.000 description 1

- UCDCWSBXWOGCKR-UHFFFAOYSA-N 2-(2-methylpropyl)aniline Chemical compound CC(C)CC1=CC=CC=C1N UCDCWSBXWOGCKR-UHFFFAOYSA-N 0.000 description 1

- RUUWTSREEUTULQ-UHFFFAOYSA-N 2-octylaniline Chemical compound CCCCCCCCC1=CC=CC=C1N RUUWTSREEUTULQ-UHFFFAOYSA-N 0.000 description 1

- LGPVKMIWERPYIJ-UHFFFAOYSA-N 3,4-dibutyl-1h-pyrrole Chemical compound CCCCC1=CNC=C1CCCC LGPVKMIWERPYIJ-UHFFFAOYSA-N 0.000 description 1

- OJFOWGWQOFZNNJ-UHFFFAOYSA-N 3,4-dimethyl-1h-pyrrole Chemical compound CC1=CNC=C1C OJFOWGWQOFZNNJ-UHFFFAOYSA-N 0.000 description 1

- JSOMPMRZESLPSM-UHFFFAOYSA-N 3-(2-methylpropyl)aniline Chemical compound CC(C)CC1=CC=CC(N)=C1 JSOMPMRZESLPSM-UHFFFAOYSA-N 0.000 description 1

- ZAJAQTYSTDTMCU-UHFFFAOYSA-N 3-aminobenzenesulfonic acid Chemical compound NC1=CC=CC(S(O)(=O)=O)=C1 ZAJAQTYSTDTMCU-UHFFFAOYSA-N 0.000 description 1

- ATWNFFKGYPYZPJ-UHFFFAOYSA-N 3-butyl-1h-pyrrole Chemical compound CCCCC=1C=CNC=1 ATWNFFKGYPYZPJ-UHFFFAOYSA-N 0.000 description 1

- KPOCSQCZXMATFR-UHFFFAOYSA-N 3-butylthiophene Chemical compound CCCCC=1C=CSC=1 KPOCSQCZXMATFR-UHFFFAOYSA-N 0.000 description 1

- FFRZVVFLHHGORC-UHFFFAOYSA-N 3-decyl-1h-pyrrole Chemical compound CCCCCCCCCCC=1C=CNC=1 FFRZVVFLHHGORC-UHFFFAOYSA-N 0.000 description 1

- JAYBIBLZTQMCAY-UHFFFAOYSA-N 3-decylthiophene Chemical compound CCCCCCCCCCC=1C=CSC=1 JAYBIBLZTQMCAY-UHFFFAOYSA-N 0.000 description 1

- RFKWIEFTBMACPZ-UHFFFAOYSA-N 3-dodecylthiophene Chemical compound CCCCCCCCCCCCC=1C=CSC=1 RFKWIEFTBMACPZ-UHFFFAOYSA-N 0.000 description 1

- KEAYXGHOGPUYPB-UHFFFAOYSA-N 3-ethoxy-1h-pyrrole Chemical compound CCOC=1C=CNC=1 KEAYXGHOGPUYPB-UHFFFAOYSA-N 0.000 description 1

- OTODBDQJLMYYKQ-UHFFFAOYSA-N 3-methoxy-1h-pyrrole Chemical compound COC=1C=CNC=1 OTODBDQJLMYYKQ-UHFFFAOYSA-N 0.000 description 1

- FEKWWZCCJDUWLY-UHFFFAOYSA-N 3-methyl-1h-pyrrole Chemical compound CC=1C=CNC=1 FEKWWZCCJDUWLY-UHFFFAOYSA-N 0.000 description 1

- YIRWZHZOCIDDAH-UHFFFAOYSA-N 3-octoxy-1h-pyrrole Chemical compound CCCCCCCCOC=1C=CNC=1 YIRWZHZOCIDDAH-UHFFFAOYSA-N 0.000 description 1

- AUVZKIJQGLYISA-UHFFFAOYSA-N 3-octoxythiophene Chemical compound CCCCCCCCOC=1C=CSC=1 AUVZKIJQGLYISA-UHFFFAOYSA-N 0.000 description 1

- WFHVTZRAIPYMMO-UHFFFAOYSA-N 3-octyl-1h-pyrrole Chemical compound CCCCCCCCC=1C=CNC=1 WFHVTZRAIPYMMO-UHFFFAOYSA-N 0.000 description 1

- PRPLKAUMELMCKP-UHFFFAOYSA-N 4-methyl-1h-pyrrol-3-ol Chemical compound CC1=CNC=C1O PRPLKAUMELMCKP-UHFFFAOYSA-N 0.000 description 1

- FXPOCCDGHHTZAO-UHFFFAOYSA-N 4-methyl-1h-pyrrole-3-carboxylic acid Chemical compound CC1=CNC=C1C(O)=O FXPOCCDGHHTZAO-UHFFFAOYSA-N 0.000 description 1

- LRFIHWGUGBXFEC-UHFFFAOYSA-N 4-methylthiophene-3-carboxylic acid Chemical compound CC1=CSC=C1C(O)=O LRFIHWGUGBXFEC-UHFFFAOYSA-N 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229910021630 Antimony pentafluoride Inorganic materials 0.000 description 1

- 229910015900 BF3 Inorganic materials 0.000 description 1

- LSNNMFCWUKXFEE-UHFFFAOYSA-M Bisulfite Chemical compound OS([O-])=O LSNNMFCWUKXFEE-UHFFFAOYSA-M 0.000 description 1

- WKBOTKDWSSQWDR-UHFFFAOYSA-N Bromine atom Chemical compound [Br] WKBOTKDWSSQWDR-UHFFFAOYSA-N 0.000 description 1

- OYPRJOBELJOOCE-UHFFFAOYSA-N Calcium Chemical compound [Ca] OYPRJOBELJOOCE-UHFFFAOYSA-N 0.000 description 1

- 239000004215 Carbon black (E152) Substances 0.000 description 1

- 102100040862 Dual specificity protein kinase CLK1 Human genes 0.000 description 1

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 1

- 101000749294 Homo sapiens Dual specificity protein kinase CLK1 Proteins 0.000 description 1

- QZRGKCOWNLSUDK-UHFFFAOYSA-N Iodochlorine Chemical compound ICl QZRGKCOWNLSUDK-UHFFFAOYSA-N 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- 229920000877 Melamine resin Polymers 0.000 description 1

- 239000004640 Melamine resin Substances 0.000 description 1

- 241001465754 Metazoa Species 0.000 description 1

- 229910019015 Mg-Ag Inorganic materials 0.000 description 1

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 description 1

- 229920000571 Nylon 11 Polymers 0.000 description 1

- 229920000299 Nylon 12 Polymers 0.000 description 1

- 229920002292 Nylon 6 Polymers 0.000 description 1

- 229920002302 Nylon 6,6 Polymers 0.000 description 1

- CTQNGGLPUBDAKN-UHFFFAOYSA-N O-Xylene Chemical compound CC1=CC=CC=C1C CTQNGGLPUBDAKN-UHFFFAOYSA-N 0.000 description 1

- 239000002033 PVDF binder Substances 0.000 description 1

- 229920001609 Poly(3,4-ethylenedioxythiophene) Polymers 0.000 description 1

- 229920000280 Poly(3-octylthiophene) Polymers 0.000 description 1

- 239000004962 Polyamide-imide Substances 0.000 description 1

- 239000004721 Polyphenylene oxide Substances 0.000 description 1

- 229920002396 Polyurea Polymers 0.000 description 1

- 239000004372 Polyvinyl alcohol Substances 0.000 description 1

- 229910003902 SiCl 4 Inorganic materials 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 229910002808 Si–O–Si Inorganic materials 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- 238000005411 Van der Waals force Methods 0.000 description 1

- GDFCWFBWQUEQIJ-UHFFFAOYSA-N [B].[P] Chemical compound [B].[P] GDFCWFBWQUEQIJ-UHFFFAOYSA-N 0.000 description 1

- 125000000217 alkyl group Chemical group 0.000 description 1

- CSDREXVUYHZDNP-UHFFFAOYSA-N alumanylidynesilicon Chemical compound [Al].[Si] CSDREXVUYHZDNP-UHFFFAOYSA-N 0.000 description 1

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- VBVBHWZYQGJZLR-UHFFFAOYSA-I antimony pentafluoride Chemical compound F[Sb](F)(F)(F)F VBVBHWZYQGJZLR-UHFFFAOYSA-I 0.000 description 1

- 239000004760 aramid Substances 0.000 description 1

- 229920003235 aromatic polyamide Polymers 0.000 description 1

- 239000003849 aromatic solvent Substances 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- YBGKQGSCGDNZIB-UHFFFAOYSA-N arsenic pentafluoride Chemical compound F[As](F)(F)(F)F YBGKQGSCGDNZIB-UHFFFAOYSA-N 0.000 description 1

- 125000003118 aryl group Chemical group 0.000 description 1

- GPBUGPUPKAGMDK-UHFFFAOYSA-N azanylidynemolybdenum Chemical compound [Mo]#N GPBUGPUPKAGMDK-UHFFFAOYSA-N 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 239000005380 borophosphosilicate glass Substances 0.000 description 1

- GDTBXPJZTBHREO-UHFFFAOYSA-N bromine Substances BrBr GDTBXPJZTBHREO-UHFFFAOYSA-N 0.000 description 1

- 229910052794 bromium Inorganic materials 0.000 description 1

- 229910052791 calcium Inorganic materials 0.000 description 1

- 239000011575 calcium Substances 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 150000001735 carboxylic acids Chemical class 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 239000003985 ceramic capacitor Substances 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 125000004093 cyano group Chemical group *C#N 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- ZOCHARZZJNPSEU-UHFFFAOYSA-N diboron Chemical compound B#B ZOCHARZZJNPSEU-UHFFFAOYSA-N 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- JBTWLSYIZRCDFO-UHFFFAOYSA-N ethyl methyl carbonate Chemical compound CCOC(=O)OC JBTWLSYIZRCDFO-UHFFFAOYSA-N 0.000 description 1

- 239000000945 filler Substances 0.000 description 1

- 229910052735 hafnium Inorganic materials 0.000 description 1

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 1

- 229930195733 hydrocarbon Natural products 0.000 description 1

- 150000002430 hydrocarbons Chemical class 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- PNDPGZBMCMUPRI-UHFFFAOYSA-N iodine Chemical compound II PNDPGZBMCMUPRI-UHFFFAOYSA-N 0.000 description 1

- CBEQRNSPHCCXSH-UHFFFAOYSA-N iodine monobromide Chemical compound IBr CBEQRNSPHCCXSH-UHFFFAOYSA-N 0.000 description 1

- PDJAZCSYYQODQF-UHFFFAOYSA-N iodine monofluoride Chemical compound IF PDJAZCSYYQODQF-UHFFFAOYSA-N 0.000 description 1

- 150000002576 ketones Chemical class 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- SJCKRGFTWFGHGZ-UHFFFAOYSA-N magnesium silver Chemical compound [Mg].[Ag] SJCKRGFTWFGHGZ-UHFFFAOYSA-N 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 150000007522 mineralic acids Chemical class 0.000 description 1

- GALOTNBSUVEISR-UHFFFAOYSA-N molybdenum;silicon Chemical compound [Mo]#[Si] GALOTNBSUVEISR-UHFFFAOYSA-N 0.000 description 1

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 1

- 229910021334 nickel silicide Inorganic materials 0.000 description 1

- 229910017604 nitric acid Inorganic materials 0.000 description 1

- 238000007645 offset printing Methods 0.000 description 1

- 150000007524 organic acids Chemical class 0.000 description 1

- 235000005985 organic acids Nutrition 0.000 description 1

- 239000003960 organic solvent Substances 0.000 description 1

- 150000002902 organometallic compounds Chemical class 0.000 description 1

- YWXLYZIZWVOMML-UHFFFAOYSA-N oxirane-2,2,3,3-tetracarbonitrile Chemical compound N#CC1(C#N)OC1(C#N)C#N YWXLYZIZWVOMML-UHFFFAOYSA-N 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 239000005011 phenolic resin Substances 0.000 description 1

- OBCUTHMOOONNBS-UHFFFAOYSA-N phosphorus pentafluoride Chemical compound FP(F)(F)(F)F OBCUTHMOOONNBS-UHFFFAOYSA-N 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 229920002849 poly(3-ethoxythiophene) polymer Polymers 0.000 description 1

- 229920002850 poly(3-methoxythiophene) polymer Polymers 0.000 description 1

- 229920002493 poly(chlorotrifluoroethylene) Polymers 0.000 description 1

- 229920003207 poly(ethylene-2,6-naphthalate) Polymers 0.000 description 1

- 229920002037 poly(vinyl butyral) polymer Polymers 0.000 description 1

- 229920006122 polyamide resin Polymers 0.000 description 1

- 229920002312 polyamide-imide Polymers 0.000 description 1

- 229920001707 polybutylene terephthalate Polymers 0.000 description 1

- 239000005023 polychlorotrifluoroethylene (PCTFE) polymer Substances 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920001225 polyester resin Polymers 0.000 description 1

- 239000004645 polyester resin Substances 0.000 description 1

- 229920000570 polyether Polymers 0.000 description 1

- 239000011112 polyethylene naphthalate Substances 0.000 description 1

- 229920000139 polyethylene terephthalate Polymers 0.000 description 1

- 239000005020 polyethylene terephthalate Substances 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 229920005749 polyurethane resin Polymers 0.000 description 1

- 229920002689 polyvinyl acetate Polymers 0.000 description 1

- 239000011118 polyvinyl acetate Substances 0.000 description 1

- 229920002451 polyvinyl alcohol Polymers 0.000 description 1

- 239000004800 polyvinyl chloride Substances 0.000 description 1

- 229920000915 polyvinyl chloride Polymers 0.000 description 1

- 229920001289 polyvinyl ether Polymers 0.000 description 1

- 229920002620 polyvinyl fluoride Polymers 0.000 description 1

- 229920002981 polyvinylidene fluoride Polymers 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- 230000002250 progressing effect Effects 0.000 description 1

- DOYOPBSXEIZLRE-UHFFFAOYSA-N pyrrole-3-carboxylic acid Chemical compound OC(=O)C=1C=CNC=1 DOYOPBSXEIZLRE-UHFFFAOYSA-N 0.000 description 1

- 239000012495 reaction gas Substances 0.000 description 1

- 238000001953 recrystallisation Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000002310 reflectometry Methods 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 150000003376 silicon Chemical class 0.000 description 1

- 238000009751 slip forming Methods 0.000 description 1

- 125000006850 spacer group Chemical group 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- NLDYACGHTUPAQU-UHFFFAOYSA-N tetracyanoethylene Chemical group N#CC(C#N)=C(C#N)C#N NLDYACGHTUPAQU-UHFFFAOYSA-N 0.000 description 1

- PCCVSPMFGIFTHU-UHFFFAOYSA-N tetracyanoquinodimethane Chemical compound N#CC(C#N)=C1C=CC(=C(C#N)C#N)C=C1 PCCVSPMFGIFTHU-UHFFFAOYSA-N 0.000 description 1

- 229920005992 thermoplastic resin Polymers 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

- YNVOMSDITJMNET-UHFFFAOYSA-N thiophene-3-carboxylic acid Chemical compound OC(=O)C=1C=CSC=1 YNVOMSDITJMNET-UHFFFAOYSA-N 0.000 description 1

- FAQYAMRNWDIXMY-UHFFFAOYSA-N trichloroborane Chemical compound ClB(Cl)Cl FAQYAMRNWDIXMY-UHFFFAOYSA-N 0.000 description 1

- LEONUFNNVUYDNQ-UHFFFAOYSA-N vanadium atom Chemical compound [V] LEONUFNNVUYDNQ-UHFFFAOYSA-N 0.000 description 1

- 125000000391 vinyl group Chemical group [H]C([*])=C([H])[H] 0.000 description 1

- 229920002554 vinyl polymer Polymers 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

- 239000008096 xylene Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/1262—Multistep manufacturing methods with a particular formation, treatment or coating of the substrate

- H01L27/1266—Multistep manufacturing methods with a particular formation, treatment or coating of the substrate the substrate on which the devices are formed not being the final device substrate, e.g. using a temporary substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/20—Deposition of semiconductor materials on a substrate, e.g. epitaxial growth solid phase epitaxy

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/268—Bombardment with radiation with high-energy radiation using electromagnetic radiation, e.g. laser radiation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/322—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to modify their internal properties, e.g. to produce internal imperfections

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76251—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques

- H01L21/76254—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques with separation/delamination along an ion implanted layer, e.g. Smart-cut, Unibond

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02656—Special treatments

- H01L21/02664—Aftertreatments

- H01L21/02667—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth

- H01L21/02675—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth using laser beams

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

- H01L29/66772—Monocristalline silicon transistors on insulating substrates, e.g. quartz substrates

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- High Energy & Nuclear Physics (AREA)

- Toxicology (AREA)

- Health & Medical Sciences (AREA)

- Optics & Photonics (AREA)

- Electromagnetism (AREA)

- Thin Film Transistor (AREA)

- Recrystallisation Techniques (AREA)

Description

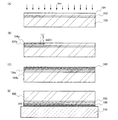

本実施の形態では、本発明の半導体基板の製造方法の一例について、図1乃至3を参照して説明する。

本実施の形態では、本発明の半導体基板の製造方法の別の一例について、図4乃至7を参照して説明する。具体的には、単結晶半導体層を、絶縁表面を有する基板に形成した後に、レーザー光の照射を行うものである。

本実施の形態では、本発明の半導体装置の製造方法の一例について、図7乃至10を参照して説明する。なお、本実施の形態においては、半導体装置の一例として液晶表示装置を挙げて説明するが、本発明の半導体装置は液晶表示装置に限られるものではない。

本実施の形態では、本発明に係る発光素子を有する半導体装置(エレクトロルミネッセンス表示装置)について説明する。なお、周辺駆動回路領域や画素領域等に用いられるトランジスタの作製方法は、実施の形態3を参照することができるため、詳細については省略する。

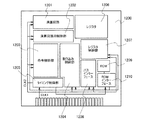

本実施の形態では、本発明に係る半導体装置の別の例について、図12及び13を参照して説明する。なお、本実施の形態においては、マイクロプロセッサ及び電子タグを例に挙げて説明するが、本発明の半導体装置はこれらに限られるものではない。

本実施の形態では、本発明の半導体装置、特に表示装置を用いた電子機器について、図14を参照して説明する。

本実施の形態では、本発明の半導体装置、特に無線タグの用途について、図15を参照して説明する。

102 損傷領域

104 単結晶半導体層

106 接合層

110 基板

300 バリア層

400 単結晶半導体基板

402 損傷領域

404 単結晶半導体層

406 接合層

410 基板

Claims (4)

- 単結晶半導体基板の表面にイオンを照射して、損傷領域を形成し、

前記単結晶半導体基板の表面に第1のレーザ光を照射して一部を再結晶化し、

前記単結晶半導体基板の表面に絶縁層を形成し、

前記絶縁層と、絶縁表面を有する基板を接合させ、

前記単結晶半導体基板を、前記損傷領域において分離することにより、前記絶縁表面を有する基板上に単結晶半導体層を形成し、

前記単結晶半導体層の分離した面側の表面に第2のレーザ光を照射して一部を再結晶化し、

前記単結晶半導体層のすべては前記第1及び前記第2のレーザ光により再結晶化されていることを特徴とする半導体基板の作製方法。 - 単結晶半導体基板の表面にイオンを照射して、損傷領域を形成し、

前記単結晶半導体基板の表面に第1のレーザ光を照射して一部を再結晶化し、

絶縁表面を有する基板の表面に絶縁層を形成し、

前記絶縁層と、前記単結晶半導体基板を接合させ、

前記単結晶半導体基板を、前記損傷領域において分離することにより、前記絶縁表面を有する基板上に単結晶半導体層を形成し、

前記単結晶半導体層の分離した面側の表面に第2のレーザ光を照射して一部を再結晶化し、

前記単結晶半導体層のすべては前記第1及び前記第2のレーザ光により再結晶化されていることを特徴とする半導体基板の作製方法。 - 単結晶半導体基板の表面にイオンを照射して、損傷領域を形成し、

前記単結晶半導体基板の表面に絶縁層を形成し、

前記絶縁層と、絶縁表面を有する基板を接合させ、

前記単結晶半導体基板を、前記損傷領域において分離することにより、前記絶縁表面を有する基板上に単結晶半導体層を形成し、

前記単結晶半導体層の表面側から一方の面に第1のレーザ光を照射して一部を再結晶化し、

前記単結晶半導体層の基板側から他方の面に第2のレーザ光を照射して一部を再結晶化し、

前記単結晶半導体層のすべては前記第1及び前記第2のレーザ光により再結晶化されていることを特徴とする半導体基板の作製方法。 - 単結晶半導体基板の表面にイオンを照射して、損傷領域を形成し、

絶縁表面を有する基板の表面に絶縁層を形成し、

前記絶縁層と、前記単結晶半導体基板を接合させ、

前記単結晶半導体基板を、前記損傷領域において分離することにより、前記絶縁表面を有する基板上に単結晶半導体層を形成し、

前記単結晶半導体層の表面側から一方の面に第1のレーザ光を照射して一部を再結晶化し、

前記単結晶半導体層の基板側から他方の面に第2のレーザ光を照射して一部を再結晶化し、

前記単結晶半導体層のすべては前記第1及び前記第2のレーザ光により再結晶化されていることを特徴とする半導体基板の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008166433A JP5459987B2 (ja) | 2007-06-26 | 2008-06-25 | 半導体基板及び半導体基板の作製方法、半導体装置、電子機器 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007167356 | 2007-06-26 | ||

| JP2007167356 | 2007-06-26 | ||

| JP2008166433A JP5459987B2 (ja) | 2007-06-26 | 2008-06-25 | 半導体基板及び半導体基板の作製方法、半導体装置、電子機器 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009033135A JP2009033135A (ja) | 2009-02-12 |

| JP2009033135A5 JP2009033135A5 (ja) | 2011-06-23 |

| JP5459987B2 true JP5459987B2 (ja) | 2014-04-02 |

Family

ID=40161087

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008166433A Expired - Fee Related JP5459987B2 (ja) | 2007-06-26 | 2008-06-25 | 半導体基板及び半導体基板の作製方法、半導体装置、電子機器 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7867873B2 (ja) |

| JP (1) | JP5459987B2 (ja) |

| KR (1) | KR101484296B1 (ja) |

Families Citing this family (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE10260149A1 (de) | 2002-12-20 | 2004-07-01 | BSH Bosch und Siemens Hausgeräte GmbH | Vorrichtung zur Bestimmung des Leitwertes von Wäsche, Wäschetrockner und Verfahren zur Verhinderung von Schichtbildung auf Elektroden |

| CN101281912B (zh) * | 2007-04-03 | 2013-01-23 | 株式会社半导体能源研究所 | Soi衬底及其制造方法以及半导体装置 |

| JP5527956B2 (ja) * | 2007-10-10 | 2014-06-25 | 株式会社半導体エネルギー研究所 | 半導体基板の製造方法 |

| JP5490393B2 (ja) * | 2007-10-10 | 2014-05-14 | 株式会社半導体エネルギー研究所 | 半導体基板の製造方法 |

| JP5503876B2 (ja) * | 2008-01-24 | 2014-05-28 | 株式会社半導体エネルギー研究所 | 半導体基板の製造方法 |

| JP5548395B2 (ja) * | 2008-06-25 | 2014-07-16 | 株式会社半導体エネルギー研究所 | Soi基板の作製方法 |

| US8741740B2 (en) * | 2008-10-02 | 2014-06-03 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing SOI substrate |

| JP2010114431A (ja) * | 2008-10-10 | 2010-05-20 | Semiconductor Energy Lab Co Ltd | Soi基板の作製方法 |

| JP5338396B2 (ja) * | 2009-03-12 | 2013-11-13 | パナソニック株式会社 | 弾性表面波デバイスの製造方法 |

| KR20120059509A (ko) * | 2009-08-25 | 2012-06-08 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제작 방법 |

| US8324084B2 (en) * | 2010-03-31 | 2012-12-04 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of semiconductor substrate and manufacturing method of semiconductor device |

| JP5917036B2 (ja) | 2010-08-05 | 2016-05-11 | 株式会社半導体エネルギー研究所 | Soi基板の作製方法 |

| JP5902917B2 (ja) | 2010-11-12 | 2016-04-13 | 株式会社半導体エネルギー研究所 | 半導体基板の作製方法 |

| JP2012156495A (ja) | 2011-01-07 | 2012-08-16 | Semiconductor Energy Lab Co Ltd | Soi基板の作製方法 |

| US8802534B2 (en) | 2011-06-14 | 2014-08-12 | Semiconductor Energy Laboratory Co., Ltd. | Method for forming SOI substrate and apparatus for forming the same |

| US8735219B2 (en) | 2012-08-30 | 2014-05-27 | Ziptronix, Inc. | Heterogeneous annealing method and device |

| JP5859497B2 (ja) * | 2013-08-22 | 2016-02-10 | 信越化学工業株式会社 | 界面近傍における欠陥密度が低いsos基板の製造方法 |

| JP5859496B2 (ja) * | 2013-08-22 | 2016-02-10 | 信越化学工業株式会社 | 表面欠陥密度が少ないsos基板の製造方法 |

| JP6454606B2 (ja) | 2015-06-02 | 2019-01-16 | 信越化学工業株式会社 | 酸化物単結晶薄膜を備えた複合ウェーハの製造方法 |

| JP6396852B2 (ja) * | 2015-06-02 | 2018-09-26 | 信越化学工業株式会社 | 酸化物単結晶薄膜を備えた複合ウェーハの製造方法 |

| JP6396853B2 (ja) | 2015-06-02 | 2018-09-26 | 信越化学工業株式会社 | 酸化物単結晶薄膜を備えた複合ウェーハの製造方法 |

| WO2020010056A1 (en) * | 2018-07-03 | 2020-01-09 | Invensas Bonding Technologies, Inc. | Techniques for joining dissimilar materials in microelectronics |

| US20230347622A1 (en) * | 2019-11-25 | 2023-11-02 | Corning Incorporated | Bonded articles and methods for forming the same |

| KR20230003471A (ko) | 2020-03-19 | 2023-01-06 | 아데이아 세미컨덕터 본딩 테크놀로지스 인코포레이티드 | 직접 결합된 구조체들을 위한 치수 보상 제어 |

| CN113541626A (zh) * | 2020-04-21 | 2021-10-22 | 济南晶正电子科技有限公司 | 一种复合单晶压电基板及制备方法 |

| CN111477543A (zh) * | 2020-04-23 | 2020-07-31 | 济南晶正电子科技有限公司 | 一种键合衬底晶圆与单晶压电晶圆的方法及复合单晶压电晶圆基板 |

| US20230231090A1 (en) * | 2022-01-18 | 2023-07-20 | Apple Inc. | System with One-Way Filter over Light-emitting Elements |

Family Cites Families (28)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0834198B2 (ja) * | 1990-11-28 | 1996-03-29 | 信越半導体株式会社 | Soi基板における単結晶薄膜層の膜厚制御方法 |

| FR2681472B1 (fr) | 1991-09-18 | 1993-10-29 | Commissariat Energie Atomique | Procede de fabrication de films minces de materiau semiconducteur. |

| JPH05335530A (ja) * | 1992-05-28 | 1993-12-17 | Sony Corp | Soi基板の製造方法 |

| US6534380B1 (en) * | 1997-07-18 | 2003-03-18 | Denso Corporation | Semiconductor substrate and method of manufacturing the same |

| US6014944A (en) * | 1997-09-19 | 2000-01-18 | The United States Of America As Represented By The Secretary Of The Navy | Apparatus for improving crystalline thin films with a contoured beam pulsed laser |

| JPH11163363A (ja) | 1997-11-22 | 1999-06-18 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP2000012864A (ja) | 1998-06-22 | 2000-01-14 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| US6271101B1 (en) | 1998-07-29 | 2001-08-07 | Semiconductor Energy Laboratory Co., Ltd. | Process for production of SOI substrate and process for production of semiconductor device |

| JP4476390B2 (ja) | 1998-09-04 | 2010-06-09 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2000124092A (ja) | 1998-10-16 | 2000-04-28 | Shin Etsu Handotai Co Ltd | 水素イオン注入剥離法によってsoiウエーハを製造する方法およびこの方法で製造されたsoiウエーハ |

| JP4379943B2 (ja) | 1999-04-07 | 2009-12-09 | 株式会社デンソー | 半導体基板の製造方法および半導体基板製造装置 |

| TW544743B (en) * | 1999-08-13 | 2003-08-01 | Semiconductor Energy Lab | Method of manufacturing a semiconductor device |

| JP4919530B2 (ja) | 1999-08-18 | 2012-04-18 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US6548370B1 (en) | 1999-08-18 | 2003-04-15 | Semiconductor Energy Laboratory Co., Ltd. | Method of crystallizing a semiconductor layer by applying laser irradiation that vary in energy to its top and bottom surfaces |

| US20010053559A1 (en) * | 2000-01-25 | 2001-12-20 | Semiconductor Energy Laboratory Co., Ltd. | Method of fabricating display device |

| JP4507395B2 (ja) * | 2000-11-30 | 2010-07-21 | セイコーエプソン株式会社 | 電気光学装置用素子基板の製造方法 |

| TW544938B (en) | 2001-06-01 | 2003-08-01 | Semiconductor Energy Lab | Method of manufacturing a semiconductor device |

| WO2003010825A1 (en) * | 2001-07-24 | 2003-02-06 | Seiko Epson Corporation | Transfer method, method of manufacturing thin film element, method of manufacturing integrated circuit, circuit substrate and method of manufacturing the circuit substrate, electro-optic device and method of manufacturing the electro-optic device, and ic card and electronic equipmen |

| US7119365B2 (en) | 2002-03-26 | 2006-10-10 | Sharp Kabushiki Kaisha | Semiconductor device and manufacturing method thereof, SOI substrate and display device using the same, and manufacturing method of the SOI substrate |

| JP2004087097A (ja) * | 2002-06-28 | 2004-03-18 | Victor Co Of Japan Ltd | 光記録媒体 |

| JP4328067B2 (ja) * | 2002-07-31 | 2009-09-09 | アプライド マテリアルズ インコーポレイテッド | イオン注入方法及びsoiウエハの製造方法、並びにイオン注入装置 |

| FR2847075B1 (fr) | 2002-11-07 | 2005-02-18 | Commissariat Energie Atomique | Procede de formation d'une zone fragile dans un substrat par co-implantation |

| JP4759919B2 (ja) | 2004-01-16 | 2011-08-31 | セイコーエプソン株式会社 | 電気光学装置の製造方法 |

| JP5110772B2 (ja) | 2004-02-03 | 2012-12-26 | 株式会社半導体エネルギー研究所 | 半導体薄膜層を有する基板の製造方法 |

| US7410882B2 (en) * | 2004-09-28 | 2008-08-12 | Palo Alto Research Center Incorporated | Method of manufacturing and structure of polycrystalline semiconductor thin-film heterostructures on dissimilar substrates |

| US7148124B1 (en) * | 2004-11-18 | 2006-12-12 | Alexander Yuri Usenko | Method for forming a fragile layer inside of a single crystalline substrate preferably for making silicon-on-insulator wafers |

| US20070281440A1 (en) * | 2006-05-31 | 2007-12-06 | Jeffrey Scott Cites | Producing SOI structure using ion shower |

| KR101440930B1 (ko) | 2007-04-20 | 2014-09-15 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | Soi 기판의 제작방법 |

-

2008

- 2008-06-03 KR KR20080052126A patent/KR101484296B1/ko not_active IP Right Cessation

- 2008-06-13 US US12/213,037 patent/US7867873B2/en not_active Expired - Fee Related

- 2008-06-25 JP JP2008166433A patent/JP5459987B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20090004822A1 (en) | 2009-01-01 |

| KR101484296B1 (ko) | 2015-01-19 |

| US7867873B2 (en) | 2011-01-11 |

| JP2009033135A (ja) | 2009-02-12 |

| KR20080114512A (ko) | 2008-12-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5459987B2 (ja) | 半導体基板及び半導体基板の作製方法、半導体装置、電子機器 | |

| US7763502B2 (en) | Semiconductor substrate, method for manufacturing semiconductor substrate, semiconductor device, and electronic device | |

| US8368082B2 (en) | Method for manufacturing semiconductor device, semiconductor device and electronic appliance | |

| US7947570B2 (en) | Manufacturing method and manufacturing apparatus of semiconductor substrate | |

| US8049253B2 (en) | Semiconductor device and method for manufacturing the same | |

| US7851332B2 (en) | Semiconductor device and method for manufacturing the same | |

| US8309429B2 (en) | Method for manufacturing semiconductor substrate and semiconductor device | |

| US7816232B2 (en) | Method for manufacturing semiconductor substrate and semiconductor substrate manufacturing apparatus | |

| US7816234B2 (en) | Method for manufacturing semiconductor device | |

| JP5322520B2 (ja) | 半導体装置、電子機器、及び半導体装置の作製方法 | |

| JP2009158937A (ja) | Soi基板の製造方法 | |

| US8236630B2 (en) | Manufacturing method of semiconductor device, semiconductor device, and electronic device | |

| JP5188355B2 (ja) | 半導体装置の作製方法、半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110511 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110511 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130529 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130530 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130614 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140107 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140114 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5459987 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |