KR20120059509A - 반도체 장치 및 그 제작 방법 - Google Patents

반도체 장치 및 그 제작 방법 Download PDFInfo

- Publication number

- KR20120059509A KR20120059509A KR1020127004336A KR20127004336A KR20120059509A KR 20120059509 A KR20120059509 A KR 20120059509A KR 1020127004336 A KR1020127004336 A KR 1020127004336A KR 20127004336 A KR20127004336 A KR 20127004336A KR 20120059509 A KR20120059509 A KR 20120059509A

- Authority

- KR

- South Korea

- Prior art keywords

- single crystal

- region

- layer

- crystal semiconductor

- photoelectric conversion

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 836

- 238000004519 manufacturing process Methods 0.000 title claims description 89

- 239000000758 substrate Substances 0.000 claims abstract description 397

- 239000013078 crystal Substances 0.000 claims abstract description 387

- 238000006243 chemical reaction Methods 0.000 claims abstract description 258

- 238000000034 method Methods 0.000 claims abstract description 156

- 230000000694 effects Effects 0.000 claims abstract description 48

- 239000012535 impurity Substances 0.000 claims description 133

- 230000015572 biosynthetic process Effects 0.000 claims description 39

- 150000002500 ions Chemical class 0.000 claims description 35

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical group O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 25

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 25

- 230000001678 irradiating effect Effects 0.000 claims description 16

- 230000000903 blocking effect Effects 0.000 claims description 13

- 150000001282 organosilanes Chemical class 0.000 claims 7

- 230000008569 process Effects 0.000 abstract description 91

- 239000010410 layer Substances 0.000 description 785

- 239000002585 base Substances 0.000 description 93

- 238000010438 heat treatment Methods 0.000 description 65

- 239000007789 gas Substances 0.000 description 49

- 239000000463 material Substances 0.000 description 41

- 238000011282 treatment Methods 0.000 description 40

- 238000005530 etching Methods 0.000 description 39

- 238000001312 dry etching Methods 0.000 description 35

- 239000012298 atmosphere Substances 0.000 description 31

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 26

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 26

- 229910052710 silicon Inorganic materials 0.000 description 26

- 239000010703 silicon Substances 0.000 description 26

- 229910052782 aluminium Inorganic materials 0.000 description 25

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 25

- 239000010936 titanium Substances 0.000 description 25

- 229910052581 Si3N4 Inorganic materials 0.000 description 23

- 239000011521 glass Substances 0.000 description 23

- 230000003287 optical effect Effects 0.000 description 23

- 239000001301 oxygen Substances 0.000 description 23

- 229910052760 oxygen Inorganic materials 0.000 description 23

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 23

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 22

- 229910052719 titanium Inorganic materials 0.000 description 20

- 238000001039 wet etching Methods 0.000 description 20

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 19

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 19

- CSDREXVUYHZDNP-UHFFFAOYSA-N alumanylidynesilicon Chemical compound [Al].[Si] CSDREXVUYHZDNP-UHFFFAOYSA-N 0.000 description 18

- 230000004888 barrier function Effects 0.000 description 18

- 230000007547 defect Effects 0.000 description 18

- 239000001257 hydrogen Substances 0.000 description 18

- 229910052739 hydrogen Inorganic materials 0.000 description 18

- 230000003647 oxidation Effects 0.000 description 18

- 238000007254 oxidation reaction Methods 0.000 description 18

- PXHVJJICTQNCMI-UHFFFAOYSA-N nickel Substances [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 17

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 15

- 229910052750 molybdenum Inorganic materials 0.000 description 15

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 15

- 229910052698 phosphorus Inorganic materials 0.000 description 15

- 239000011574 phosphorus Substances 0.000 description 15

- 239000002356 single layer Substances 0.000 description 15

- 238000004381 surface treatment Methods 0.000 description 15

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 14

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 14

- 239000011733 molybdenum Substances 0.000 description 14

- 238000000059 patterning Methods 0.000 description 14

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 14

- 239000000460 chlorine Substances 0.000 description 13

- 239000012495 reaction gas Substances 0.000 description 13

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 12

- 229910052757 nitrogen Inorganic materials 0.000 description 12

- 238000004151 rapid thermal annealing Methods 0.000 description 12

- 238000000926 separation method Methods 0.000 description 12

- 238000004544 sputter deposition Methods 0.000 description 12

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 11

- 229910052721 tungsten Inorganic materials 0.000 description 11

- 239000010937 tungsten Substances 0.000 description 11

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 9

- 230000001133 acceleration Effects 0.000 description 9

- 239000000956 alloy Substances 0.000 description 9

- 229910052796 boron Inorganic materials 0.000 description 9

- 238000005229 chemical vapour deposition Methods 0.000 description 9

- 239000010949 copper Substances 0.000 description 9

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 9

- 238000000206 photolithography Methods 0.000 description 9

- 239000011734 sodium Substances 0.000 description 9

- 239000000126 substance Substances 0.000 description 9

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 8

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 8

- 229910045601 alloy Inorganic materials 0.000 description 8

- 229910021419 crystalline silicon Inorganic materials 0.000 description 8

- -1 hydrochloric acid peroxide Chemical class 0.000 description 8

- 229910052759 nickel Inorganic materials 0.000 description 8

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 8

- 239000007790 solid phase Substances 0.000 description 8

- 229910052801 chlorine Inorganic materials 0.000 description 7

- 239000011368 organic material Substances 0.000 description 7

- 230000001590 oxidative effect Effects 0.000 description 7

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 6

- 229910052785 arsenic Inorganic materials 0.000 description 6

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 6

- QVQLCTNNEUAWMS-UHFFFAOYSA-N barium oxide Chemical compound [Ba]=O QVQLCTNNEUAWMS-UHFFFAOYSA-N 0.000 description 6

- 238000009792 diffusion process Methods 0.000 description 6

- 238000009832 plasma treatment Methods 0.000 description 6

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 6

- 239000011347 resin Substances 0.000 description 6

- 229920005989 resin Polymers 0.000 description 6

- 238000002834 transmittance Methods 0.000 description 6

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 5

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 5

- 230000009471 action Effects 0.000 description 5

- 229910052799 carbon Inorganic materials 0.000 description 5

- 125000001309 chloro group Chemical group Cl* 0.000 description 5

- 239000011651 chromium Substances 0.000 description 5

- 230000021615 conjugation Effects 0.000 description 5

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 5

- 239000010931 gold Substances 0.000 description 5

- 230000008018 melting Effects 0.000 description 5

- 238000002844 melting Methods 0.000 description 5

- 150000004767 nitrides Chemical class 0.000 description 5

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 5

- 230000005855 radiation Effects 0.000 description 5

- 230000035945 sensitivity Effects 0.000 description 5

- 229910052708 sodium Inorganic materials 0.000 description 5

- 229910052715 tantalum Inorganic materials 0.000 description 5

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 5

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 4

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 4

- 229910021417 amorphous silicon Inorganic materials 0.000 description 4

- 239000005380 borophosphosilicate glass Substances 0.000 description 4

- 229910052804 chromium Inorganic materials 0.000 description 4

- 150000001875 compounds Chemical class 0.000 description 4

- 229910052802 copper Inorganic materials 0.000 description 4

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 4

- 230000005684 electric field Effects 0.000 description 4

- 230000005283 ground state Effects 0.000 description 4

- 239000001307 helium Substances 0.000 description 4

- 229910052734 helium Inorganic materials 0.000 description 4

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 4

- 239000011572 manganese Substances 0.000 description 4

- 229910052751 metal Inorganic materials 0.000 description 4

- 239000002184 metal Substances 0.000 description 4

- 239000010955 niobium Substances 0.000 description 4

- 125000004430 oxygen atom Chemical group O* 0.000 description 4

- 239000005360 phosphosilicate glass Substances 0.000 description 4

- 238000007740 vapor deposition Methods 0.000 description 4

- 238000005406 washing Methods 0.000 description 4

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 3

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 3

- MWUXSHHQAYIFBG-UHFFFAOYSA-N Nitric oxide Chemical compound O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 3

- 238000005411 Van der Waals force Methods 0.000 description 3

- QGZKDVFQNNGYKY-UHFFFAOYSA-N ammonia Natural products N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 3

- 230000008901 benefit Effects 0.000 description 3

- KGBXLFKZBHKPEV-UHFFFAOYSA-N boric acid Chemical compound OB(O)O KGBXLFKZBHKPEV-UHFFFAOYSA-N 0.000 description 3

- 239000004327 boric acid Substances 0.000 description 3

- 239000000969 carrier Substances 0.000 description 3

- 238000011109 contamination Methods 0.000 description 3

- 238000005401 electroluminescence Methods 0.000 description 3

- 229910052731 fluorine Inorganic materials 0.000 description 3

- 239000011737 fluorine Substances 0.000 description 3

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 3

- 229910052737 gold Inorganic materials 0.000 description 3

- 229910052736 halogen Inorganic materials 0.000 description 3

- 150000002367 halogens Chemical class 0.000 description 3

- 229910001385 heavy metal Inorganic materials 0.000 description 3

- 238000005468 ion implantation Methods 0.000 description 3

- 239000004973 liquid crystal related substance Substances 0.000 description 3

- 238000005259 measurement Methods 0.000 description 3

- 238000002156 mixing Methods 0.000 description 3

- 229910052758 niobium Inorganic materials 0.000 description 3

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 3

- 150000003254 radicals Chemical class 0.000 description 3

- 230000009467 reduction Effects 0.000 description 3

- 230000002441 reversible effect Effects 0.000 description 3

- 239000004593 Epoxy Substances 0.000 description 2

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 2

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 2

- 229910052779 Neodymium Inorganic materials 0.000 description 2

- 206010034960 Photophobia Diseases 0.000 description 2

- 239000004952 Polyamide Substances 0.000 description 2

- 239000004642 Polyimide Substances 0.000 description 2

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 2

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 2

- 239000002253 acid Substances 0.000 description 2

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 2

- 238000011276 addition treatment Methods 0.000 description 2

- 229910052783 alkali metal Inorganic materials 0.000 description 2

- 150000001340 alkali metals Chemical class 0.000 description 2

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 2

- 150000001342 alkaline earth metals Chemical class 0.000 description 2

- 229910021529 ammonia Inorganic materials 0.000 description 2

- 229910052786 argon Inorganic materials 0.000 description 2

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 2

- 239000006229 carbon black Substances 0.000 description 2

- 238000004140 cleaning Methods 0.000 description 2

- 230000003749 cleanliness Effects 0.000 description 2

- 229910017052 cobalt Inorganic materials 0.000 description 2

- 239000010941 cobalt Substances 0.000 description 2

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 2

- 239000000356 contaminant Substances 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 229910001873 dinitrogen Inorganic materials 0.000 description 2

- 238000003618 dip coating Methods 0.000 description 2

- 239000000428 dust Substances 0.000 description 2

- 238000001678 elastic recoil detection analysis Methods 0.000 description 2

- 230000005281 excited state Effects 0.000 description 2

- 125000001153 fluoro group Chemical group F* 0.000 description 2

- 229910052733 gallium Inorganic materials 0.000 description 2

- 229910052732 germanium Inorganic materials 0.000 description 2

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 2

- 229910000449 hafnium oxide Inorganic materials 0.000 description 2

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 2

- 125000005843 halogen group Chemical group 0.000 description 2

- VEXZGXHMUGYJMC-UHFFFAOYSA-N hydrochloric acid Substances Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 2

- 150000002431 hydrogen Chemical class 0.000 description 2

- 238000009616 inductively coupled plasma Methods 0.000 description 2

- 239000011261 inert gas Substances 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 230000010354 integration Effects 0.000 description 2

- 208000013469 light sensitivity Diseases 0.000 description 2

- 239000007788 liquid Substances 0.000 description 2

- 229910052748 manganese Inorganic materials 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- QSHDDOUJBYECFT-UHFFFAOYSA-N mercury Chemical compound [Hg] QSHDDOUJBYECFT-UHFFFAOYSA-N 0.000 description 2

- 229910052753 mercury Inorganic materials 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 2

- 238000005121 nitriding Methods 0.000 description 2

- 239000012299 nitrogen atmosphere Substances 0.000 description 2

- 238000007645 offset printing Methods 0.000 description 2

- 230000010355 oscillation Effects 0.000 description 2

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 2

- 230000035515 penetration Effects 0.000 description 2

- 239000000049 pigment Substances 0.000 description 2

- 229910052697 platinum Inorganic materials 0.000 description 2

- 229920002647 polyamide Polymers 0.000 description 2

- 229920001721 polyimide Polymers 0.000 description 2

- 238000010248 power generation Methods 0.000 description 2

- 239000002244 precipitate Substances 0.000 description 2

- 230000001603 reducing effect Effects 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- 230000004043 responsiveness Effects 0.000 description 2

- 239000010979 ruby Substances 0.000 description 2

- 229910001750 ruby Inorganic materials 0.000 description 2

- 238000005001 rutherford backscattering spectroscopy Methods 0.000 description 2

- 229910052594 sapphire Inorganic materials 0.000 description 2

- 239000010980 sapphire Substances 0.000 description 2

- 238000007650 screen-printing Methods 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- 238000003746 solid phase reaction Methods 0.000 description 2

- 239000000243 solution Substances 0.000 description 2

- 238000004528 spin coating Methods 0.000 description 2

- 238000005507 spraying Methods 0.000 description 2

- QAOWNCQODCNURD-UHFFFAOYSA-N sulfuric acid Substances OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 2

- 230000003746 surface roughness Effects 0.000 description 2

- 229910001936 tantalum oxide Inorganic materials 0.000 description 2

- VZGDMQKNWNREIO-UHFFFAOYSA-N tetrachloromethane Chemical compound ClC(Cl)(Cl)Cl VZGDMQKNWNREIO-UHFFFAOYSA-N 0.000 description 2

- 230000008719 thickening Effects 0.000 description 2

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 2

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 2

- 229910021342 tungsten silicide Inorganic materials 0.000 description 2

- 229910052724 xenon Inorganic materials 0.000 description 2

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 2

- 229910052725 zinc Inorganic materials 0.000 description 2

- 239000011701 zinc Substances 0.000 description 2

- 229910052726 zirconium Inorganic materials 0.000 description 2

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- 229910002808 Si–O–Si Inorganic materials 0.000 description 1

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 238000010521 absorption reaction Methods 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 239000005354 aluminosilicate glass Substances 0.000 description 1

- 239000012300 argon atmosphere Substances 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 238000007664 blowing Methods 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- UIZLQMLDSWKZGC-UHFFFAOYSA-N cadmium helium Chemical compound [He].[Cd] UIZLQMLDSWKZGC-UHFFFAOYSA-N 0.000 description 1

- 239000012159 carrier gas Substances 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 229910001882 dioxygen Inorganic materials 0.000 description 1

- 230000005284 excitation Effects 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- QOSATHPSBFQAML-UHFFFAOYSA-N hydrogen peroxide;hydrate Chemical compound O.OO QOSATHPSBFQAML-UHFFFAOYSA-N 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- XEEYBQQBJWHFJM-UHFFFAOYSA-N iron Substances [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 1

- 229910052743 krypton Inorganic materials 0.000 description 1

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 239000007791 liquid phase Substances 0.000 description 1

- 229910001507 metal halide Inorganic materials 0.000 description 1

- 150000005309 metal halides Chemical class 0.000 description 1

- 239000011259 mixed solution Substances 0.000 description 1

- 150000002831 nitrogen free-radicals Chemical class 0.000 description 1

- GVGCUCJTUSOZKP-UHFFFAOYSA-N nitrogen trifluoride Chemical compound FN(F)F GVGCUCJTUSOZKP-UHFFFAOYSA-N 0.000 description 1

- 230000006911 nucleation Effects 0.000 description 1

- 238000010899 nucleation Methods 0.000 description 1

- 239000005416 organic matter Substances 0.000 description 1

- SOQBVABWOPYFQZ-UHFFFAOYSA-N oxygen(2-);titanium(4+) Chemical class [O-2].[O-2].[Ti+4] SOQBVABWOPYFQZ-UHFFFAOYSA-N 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 238000007517 polishing process Methods 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000002940 repellent Effects 0.000 description 1

- 239000005871 repellent Substances 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- FDNAPBUWERUEDA-UHFFFAOYSA-N silicon tetrachloride Chemical compound Cl[Si](Cl)(Cl)Cl FDNAPBUWERUEDA-UHFFFAOYSA-N 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000004611 spectroscopical analysis Methods 0.000 description 1

- 230000002269 spontaneous effect Effects 0.000 description 1

- 239000007858 starting material Substances 0.000 description 1

- SFZCNBIFKDRMGX-UHFFFAOYSA-N sulfur hexafluoride Chemical compound FS(F)(F)(F)(F)F SFZCNBIFKDRMGX-UHFFFAOYSA-N 0.000 description 1

- 229960000909 sulfur hexafluoride Drugs 0.000 description 1

- TXEYQDLBPFQVAA-UHFFFAOYSA-N tetrafluoromethane Chemical compound FC(F)(F)F TXEYQDLBPFQVAA-UHFFFAOYSA-N 0.000 description 1

- 150000003608 titanium Chemical class 0.000 description 1

- FAQYAMRNWDIXMY-UHFFFAOYSA-N trichloroborane Chemical compound ClB(Cl)Cl FAQYAMRNWDIXMY-UHFFFAOYSA-N 0.000 description 1

- 238000004506 ultrasonic cleaning Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/08—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof in which radiation controls flow of current through the device, e.g. photoresistors

- H01L31/10—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof in which radiation controls flow of current through the device, e.g. photoresistors characterised by at least one potential-jump barrier or surface barrier, e.g. phototransistors

- H01L31/101—Devices sensitive to infrared, visible or ultraviolet radiation

- H01L31/102—Devices sensitive to infrared, visible or ultraviolet radiation characterised by only one potential barrier or surface barrier

- H01L31/103—Devices sensitive to infrared, visible or ultraviolet radiation characterised by only one potential barrier or surface barrier the potential barrier being of the PN homojunction type

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/04—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof adapted as photovoltaic [PV] conversion devices

- H01L31/06—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof adapted as photovoltaic [PV] conversion devices characterised by at least one potential-jump barrier or surface barrier

- H01L31/075—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof adapted as photovoltaic [PV] conversion devices characterised by at least one potential-jump barrier or surface barrier the potential barriers being only of the PIN type

- H01L31/077—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof adapted as photovoltaic [PV] conversion devices characterised by at least one potential-jump barrier or surface barrier the potential barriers being only of the PIN type the devices comprising monocrystalline or polycrystalline materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/0248—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by their semiconductor bodies

- H01L31/036—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by their semiconductor bodies characterised by their crystalline structure or particular orientation of the crystalline planes

- H01L31/0392—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by their semiconductor bodies characterised by their crystalline structure or particular orientation of the crystalline planes including thin films deposited on metallic or insulating substrates ; characterised by specific substrate materials or substrate features or by the presence of intermediate layers, e.g. barrier layers, on the substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/08—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof in which radiation controls flow of current through the device, e.g. photoresistors

- H01L31/10—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof in which radiation controls flow of current through the device, e.g. photoresistors characterised by at least one potential-jump barrier or surface barrier, e.g. phototransistors

- H01L31/101—Devices sensitive to infrared, visible or ultraviolet radiation

- H01L31/102—Devices sensitive to infrared, visible or ultraviolet radiation characterised by only one potential barrier or surface barrier

- H01L31/105—Devices sensitive to infrared, visible or ultraviolet radiation characterised by only one potential barrier or surface barrier the potential barrier being of the PIN type

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/18—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof

- H01L31/1804—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof comprising only elements of Group IV of the Periodic System

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/18—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof

- H01L31/186—Particular post-treatment for the devices, e.g. annealing, impurity gettering, short-circuit elimination, recrystallisation

- H01L31/1864—Annealing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/18—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof

- H01L31/1892—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof methods involving the use of temporary, removable substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14643—Photodiode arrays; MOS imagers

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

- Y02E10/547—Monocrystalline silicon PV cells

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02P—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN THE PRODUCTION OR PROCESSING OF GOODS

- Y02P70/00—Climate change mitigation technologies in the production process for final industrial or consumer products

- Y02P70/50—Manufacturing or production processes characterised by the final manufactured product

Abstract

개시된 발명의 실시형태의 목적은, 우수한 특성을 갖는 광전 변환 소자를 포함하는 반도체 장치를 제공하는 것이다. 개시된 발명의 실시형태의 목적은 단순한 공정을 통해 우수한 특성을 갖는 광전 변환 장치를 포함하는 반도체 장치를 제공하는 것이다. 광 투과성 기판, 광 투과성 기판 위의 절연층, 및 절연층 위의 광전 변환 소자를 포함하는 반도체 장치가 제공된다. 광전 변환 소자는, 광전 변환의 효과를 갖는 반도체 영역, 제 1 도전형을 갖는 반도체 영역, 및 제 2 도전형을 갖는 반도체 영역을 포함하는 단결정 반도체층; 제 1 도전형을 갖는 반도체 영역에 전기적으로 접속된 제 1 전극; 및 제 2 도전형을 갖는 반도체 영역에 전기적으로 접속된 제 2 전극을 포함한다.

Description

본 발명은 SOI(siliicon on insulator) 기판을 포함하는 반도체 장치 및 이 반도체 장치의 제작 방법에 관한 것이다.

유리 기판 위에 광전 변환 소자(예를 들어, 광 센서)를 형성하는 경우, 몇몇 경우에서 광전 변환의 효과를 갖는 반도체층에 대해 다결정 실리콘이 사용된다(예를 들어, 특허문헌 1 참조). 다결정 실리콘은, 저온의 프로세스를 통해 형성될 수 있기 때문에, 유리 기판과 같은 내열성이 낮은 기판 위에 쉽게 형성된다는 이점을 갖는다.

그러나, 단결정 실리콘의 경우와 비교하여 다결정 실리콘의 경우에서는, 암전류(dark current)의 양이 큰 경향이 있다. 또한, 결함들로 인해 캐리어들이 트랩(trap)되고, 광 조사시의 전류가 감소된다는 문제가 존재한다. 따라서, 다결정 실리콘을 사용하는 경우에는, 충분한 광 감도를 가지는 광전 변환 소자를 제작하는 것이 어렵다.

상기 문제의 관점에서, 개시된 발명의 일 실시형태의 목적은, 뛰어난 특성을 갖는 광전 변환 소자를 포함하는 반도체 장치를 제공하는 것이다. 개시된 발명의 실시형태의 목적은, 간단한 공정을 통해 뛰어난 특성을 갖는 광전 변환 장치를 포함하는 반도체 장치를 제공하는 것이다.

개시된 발명의 실시형태에서, 광 투과성 기판 위의 단결정 반도체층을 이용하여 광전 변환 소자가 형성된다. 그 상세가 후술된다.

개시된 발명의 실시형태는, 광 투과성 기판; 광 투과성 기판 위의 절연층; 및 절연층 위의 광전 변환 소자를 포함하는 반도체 장치이다. 광전 변환 소자는 광전 변환의 효과를 갖는 반도체 영역, 제 1 도전형을 갖는 반도체 영역, 및 제 2 도전형을 갖는 반도체 영역을 포함하는 단결정 반도체층; 제 1 도전형을 갖는 반도체 영역에 전기적으로 접속된 제 1 전극; 및 제 2 도전형을 갖는 반도체 영역에 전기적으로 접속된 제 2 전극을 포함한다. 상기 구조에서, 광전 변환 소자에 추가하여 절연층 위에 트랜지스터가 제공될 수 있다.

개시된 본 발명의 다른 실시형태는, 광전 변환 소자를 형성하는 단계들을 포함하는 반도체 장치를 제작하는 방법이다. 광전 변환 소자는, 단결정 반도체 기판을 이온으로 조사하여 단결정 반도체 기판에 취화 영역(embrittled region)을 형성하는 단계; 절연층을 개재하여 단결정 반도체 기판 및 광 투과성 기판을 함께 접합하는 단계; 취화 영역에서 단결정 반도체 기판을 분리하여 광 투과성 기판 위에 단결정 반도체층을 형성하는 단계; 단결정 반도체층을 가공하여 섬형상 반도체층을 형성하는 단계; 섬형상 반도체층에 제 1 불순물 원소 및 제 2 불순물 원소를 선택적으로 첨가하여 광전 변환의 효과를 갖는 반도체 영역, 제 1 도전형을 갖는 반도체 영역, 및 제 2 도전형을 갖는 반도체 영역을 형성하는 단계; 제 2 도전형을 갖는 반도체 영역에 전기적으로 접속된 제 1 전극을 형성하는 단계; 및 제 1 도전형을 갖는 반도체 영역에 전기적으로 접속된 제 2 전극을 형성하는 단계를 포함하는 방법에 의해 형성된다. 상기 방법에서, 트랜지스터가 광전 변환 소자에 추가하여 절연층 위에 형성될 수 있다.

개시된 발명의 다른 실시형태는, 광 투과 기판; 광 투과성 기판 위의 제 1 절연층; 제 1 절연층 위에 선택적으로 형성된 차광층; 차광층 위의 제 2 절연층; 및 제 2 절연층 위의 광전 변환 소자를 포함하는 반도체 장치이다. 광전 변환 소자는, 광전 변환의 효과를 갖는 반도체 영역, 제 1 도전형을 갖는 반도체 영역, 및 제 2 도전형을 갖는 반도체 영역을 포함하는 단결정 반도체층; 제 1 도전형을 갖는 반도체 영역에 전기적으로 접속된 제 1 전극; 및 제 2 도전형을 갖는 반도체 영역에 전기적으로 접속된 제 2 전극을 포함한다. 상기 구조에서, 트랜지스터가 광전 변환 소자에 추가하여 제 2 절연층 위에 제공될 수 있다.

개시된 발명의 다른 실시형태는, 광전 변환 소자를 형성하는 단계들을 포함하는 반도체 장치를 제작하는 방법이다. 광전 변환 소자는, 단결정 반도체 기판을 이온으로 조사하여 단결정 반도체 기판에 취화 영역을 형성하는 단계; 광 투과성 기판 위에 제 1 절연층을 형성하고 제 1 절연층 위에 차광층을 형성하는 단계; 제 2 절연층을 개재하여 단결정 반도체 기판과, 차광층이 형성된 광 투과성 기판을 함께 접합하는 단계; 취화 영역에서 단결정 반도체 기판을 분리하여 광 투과성 기판 위에 단결정 반도체층을 형성하는 단계; 단결정 반도체층을 가공하여 섬형상 반도체층을 형성하는 단계; 섬형상 반도체층에 제 1 불순물 원소 및 제 2 불순물 원소를 선택적으로 첨가하여 광전 변환의 효과를 갖는 반도체 영역, 제 1 도전형을 갖는 반도체 영역, 및 제 2 도전형을 갖는 반도체 영역을 형성하는 단계; 제 1 도전형을 갖는 반도체 영역에 전기적으로 접속된 제 1 전극을 형성하는 단계; 및 제 2 도전형을 갖는 반도체 영역에 전기적으로 접속된 제 2 전극을 형성하는 단계를 포함하는 방법에 의해 형성된다. 상기 방법에서, 트랜지스터가 광전 변환 소자에 추가하여 제 2 절연층 위에 형성될 수 있다.

개시된 발명의 다른 실시형태는, 광전 변환 소자 및 트랜지스터를 형성하는 단계들을 포함하는 반도체 장치를 제작하는 방법이다. 광전 변환 소자 및 트랜지스터는, 단결정 반도체 기판을 이온으로 조사하여 단결정 반도체 기판에 취화 영역을 형성하는 단계; 광 투과성 기판 위에 제 1 절연층을 형성하고 제 1 절연층 위에 차광층을 형성하는 단계; 제 2 절연층을 개재하여 단결정 반도체 기판과 차광층이 형성된 광 투과성 기판을 함께 접합하는 단계; 취화 영역에서 단결정 반도체 기판을 분리하여 광 투과성 기판 위에 단결정 반도체층을 형성하는 단계; 단결정 반도체층을 가공하여 제 1 섬형상 반도체층 및 제 2 섬형상 반도체층을 형성하는 단계; 제 1 섬형상 반도체층에 제 1 불순물 원소 및 제 2 불순물 원소를 선택적으로 첨가하여 광전 변환의 효과를 갖는 반도체 영역, 제 1 도전형을 갖는 반도체 영역, 및 제 2 도전형을 갖는 반도체 영역을 형성하는 단계; 제 1 도전형을 갖는 반도체 영역에 전기적으로 접속된 제 1 전극을 형성하는 단계; 제 2 도전형을 갖는 반도체 영역에 전기적으로 접속된 제 2 전극을 형성하여, 광전 변환 소자를 형성하는 단계; 제 2 섬형상 반도체층에 제 1 불순물 원소 또는 제 2 불순물 원소를 선택적으로 첨가하여 채널 형성 영역, 소스 영역, 및 드레인 영역을 형성하는 단계; 제 2 섬형상 반도체층 위에 게이트 절연막을 형성하는 단계; 및 트랜지스터가 형성되도록 소스 영역에 전기적으로 접속된 소스 전극 및 드레인 영역에 전기적으로 접속된 드레인 전극을 형성하는 단계를 포함하는 방법에 의해 형성된다.

개시된 발명의 다른 실시형태는 광전 변환 소자 및 트랜지스터를 형성하는 단계들을 포함하는 반도체 장치를 제작하는 방법이다. 광전 변환 소자 및 트랜지스터는, 단결정 반도체 기판을 이온으로 조사하여 단결정 반도체 기판에 취화 영역을 형성하는 단계; 광 투과성 기판 위에 제 1 절연층을 형성하고 제 1 절연층 위에 차광층을 형성하는 단계; 차광층을 가공하여, 제 1 섬형상 차광층 및 제 2 섬형상 차광층을 포함하는 복수의 섬형상 차광층을 형성하는 단계; 평탄성을 갖는 제 2 절연층을 형성하여 복수의 섬형상 차광층을 커버하는 단계; 제 3 절연층을 개재하여 단결정 반도체 기판과 제 2 절연층이 형성된 광 투과성 기판을 함께 접합하는 단계; 취화 영역에서 단결정 반도체 기판을 분리하여 광 투과성 기판 위에 복수의 섬형상 차광층과 오버랩하는 섬형상 반도체층들을 형성하는 단계; 제 1 섬형상 차광층과 오버랩하는 섬형상 반도체층에 제 1 불순물 원소 및 제 2 불순물 원소를 선택적으로 첨가하여 광전 변환의 효과를 갖는 반도체 영역, 제 1 도전형을 갖는 반도체 영역, 및 제 2 도전형을 갖는 반도체 영역을 형성하는 단계; 제 1 도전형을 갖는 반도체 영역에 전기적으로 접속된 제 1 전극을 형성하는 단계; 제 2 도전형을 갖는 반도체 영역에 전기적으로 접속된 제 2 전극을 형성하여, 광전 변환 소자를 형성하는 단계; 제 2 섬형상 차광층과 오버랩하는 섬형상 반도체층에 제 1 불순물 원소 또는 제 2 불순물 원소를 선택적으로 첨가하여 채널 형성 영역, 소스 영역, 및 드레인 영역을 형성하는 단계; 제 2 섬형성 차광층과 오버랩하는 섬형상 반도체층 위에 게이트 절연막을 형성하는 단계; 및 게이트 절연막 위에 게이트 전극을 형성하는 단계; 및 트랜지스터가 형성되도록 소스 영역에 전기적으로 접속된 소스 전극 및 드레인 영역에 전기적으로 접속된 드레인 전극을 형성하는 단계를 포함하는 방법에 의해 형성된다.

개시된 발명의 다른 실시형태는, 광 투과성 기판, 광 투과성 기판 위의 절연층, 및 절연층 위의 광전 변환 소자와 트랜지스터를 포함하는 반도체 장치이다. 광전 변환 소자는, 광전 변환의 효과를 갖는 반도체 영역, 제 1 도전형의 반도체 영역, 및 제 2 도전형의 반도체 영역을 포함하는 제 1 단결정 반도체층; 제 1 도전형을 갖는 반도체 영역에 전기적으로 접속된 제 1 전극; 및 제 2 도전형을 갖는 반도체 영역에 전기적으로 접속된 제 2 전극을 포함한다. 트랜지스터는 채널 형성 영역, 소스 영역 및 드레인 영역을 포함하는 제 2 단결정 반도체층; 제 2 단결정 반도체층 위의 게이트 절연막; 게이트 절연막 위의 게이트 전극; 소스 영역에 전기적으로 접속된 소스 전극; 및 드레인 영역에 전기적으로 접속된 드레인 전극을 포함한다. 제 1 단결정 반도체층 및 제 2 단결정 반도체층은 절연층 위에 형성된다. 제 1 단결정 반도체층의 두께는 제 2 단결정 반도체층의 두께보다 크다.

개시된 발명의 다른 실시형태는, 광전 변환 소자 및 트랜지스터를 형성하는 단계들을 포함하는 반도체 장치를 제작하는 방법이다. 광전 변환 소자 및 트랜지스터는, 단결정 반도체 기판을 이온으로 조사하여 단결정 반도체 기판에 취화 영역을 형성하는 단계; 절연층을 개재하여 단결정 반도체 기판과 광 투과성 기판을 함께 접합하는 단계; 취화 영역에서 단결정 반도체 기판을 분리하여 광 투과성 기판 위에 단결정 반도체층을 형성하는 단계; 단결정 반도체층의 일부를 얇게 하여 제 1 단결정 반도체 영역 및 그 제 1 단결정 반도체 영역보다 작은 두께를 갖는 제 2 단결정 반도체 영역을 형성하는 단계; 제 1 단결정 반도체 영역을 가공하여 제 1 섬형상 반도체층을 형성하는 단계; 제 2 단결정 반도체 영역을 가공하여 제 2 섬형상 반도체층을 형성하는 단계; 제 1 섬형상 반도체층에 제 1 불순물 원소 및 제 2 불순물 원소를 선택적으로 첨가하여 광전 변환의 효과를 갖는 반도체 영역, 제 1 도전형을 갖는 반도체 영역, 및 제 2 도전형을 갖는 반도체 영역을 형성하는 단계; 제 1 도전형을 갖는 반도체 영역에 전기적으로 접속된 제 1 전극을 형성하는 단계; 제 2 도전형을 갖는 반도체 영역에 전기적으로 접속된 제 2 전극을 형성하여, 광전 변환 소자를 형성하는 단계; 제 2 섬형상 반도체층에 제 1 불순물 원소 또는 제 2 불순물 원소를 선택적으로 첨가하여 채널 형성 영역, 소스 영역, 및 드레인 영역을 형성하는 단계; 제 2 섬형성 반도체층 위에 게이트 절연막을 형성하는 단계; 게이트 절연막 위에 게이트 전극을 형성하는 단계; 및 트랜지스터가 형성되도록 소스 영역에 전기적으로 접속된 소스 전극 및 드레인 영역에 전기적으로 접속된 드레인 전극을 형성하는 단계를 포함하는 방법에 의해 형성된다.

개시된 발명의 다른 실시형태는, 광전 변환 소자 및 트랜지스터를 형성하는 단계들을 포함하는 반도체 장치를 제작하는 방법이다. 광전 변환 소자 및 트랜지스터는, 단결정 반도체 기판을 이온으로 조사하여 단결정 반도체 기판에 취화 영역을 형성하는 단계; 절연층을 개재하여 단결정 반도체 기판과 광 투과성 기판을 함께 접합하는 단계; 취화 영역에서 단결정 반도체 기판을 분리하여 광 투과성 기판 위에 단결정 반도체층을 형성하는 단계; 단결정 반도체층의 일부를 두껍게 하여 제 1 단결정 반도체 영역 및 그 제 1 단결정 반도체 영역보다 작은 두께를 갖는 제 2 단결정 반도체 영역을 형성하는 단계; 제 1 단결정 반도체 영역을 가공하여 제 1 섬형상 반도체층을 형성하는 단계; 제 2 단결정 반도체 영역을 가공하여 제 2 섬형상 반도체층을 형성하는 단계; 제 1 섬형상 반도체층에 제 1 불순물 원소 및 제 2 불순물 원소를 선택적으로 첨가하여 광전 변환의 효과를 갖는 반도체 영역, 제 1 도전형을 갖는 반도체 영역, 및 제 2 도전형을 갖는 반도체 영역을 형성하는 단계; 제 1 도전형을 갖는 반도체 영역에 전기적으로 접속된 제 1 전극을 형성하는 단계; 제 2 도전형을 갖는 반도체 영역에 전기적으로 접속된 제 2 전극을 형성하여, 광전 변환 소자를 형성하는 단계; 제 2 섬형상 반도체층에 제 1 불순물 원소 또는 제 2 불순물 원소를 선택적으로 첨가하여 채널 형성 영역, 소스 영역, 및 드레인 영역을 형성하는 단계; 제 2 섬형성 반도체층 위에 게이트 절연막을 형성하는 단계; 게이트 절연막 위에 게이트 전극을 형성하는 단계; 및 트랜지스터가 형성되도록 소스 영역에 전기적으로 접속된 소스 전극 및 드레인 영역에 전기적으로 접속된 드레인 전극을 형성하는 단계를 포함하는 방법에 의해 형성된다.

일반적으로, 용어 "SOI 기판"은 절연 표면 위에 실리콘 반도체층이 제공되는 반도체 기판을 의미한다. 본 명세서 등에서, 용어 "SOI 기판"은 또한, 절연 표면 위에 실리콘 이외의 재료를 사용하여 형성된 반도체층이 제공되는 반도체 기판을 포함한다. 즉, "SOI 기판"에 포함된 반도체층은 실리콘 반도체층에 한정되지 않는다. 또한, 본 명세서 등에서, 반도체 기판은, 반도체 재료만을 사용하여 형성된 기판 뿐만 아니라 반도체 재료를 포함하는 모든 기판들을 의미한다. 즉, 본 명세서 등에서, "SOI 기판"은 또한 반도체 기판의 카테고리에 포함된다.

본 명세서 등에서, 용어 "단결정"은, 특정 결정축이 포커싱될 때, 그 결정축의 방향이 시료의 어느 부분에 있어서도 동일한 방향으로 배향되는 결정을 의미한다. 즉, 단결정은 결정축들의 방향이 결정 결함 또는 댕글링 본드를 포함하더라도 상술한 바와 같이, 균일한 결정을 포함한다.

또한, 본 명세서 등에서, 용어 "반도체 장치"는, 반도체 특성을 이용함으로써 동작할 수 있는 모든 장치들을 의미한다. 예를 들어, 표시 장치 및 집적 회로가 반도체 장치의 카테고리에 포함된다. 또한, 본 명세서 등에서, 표시 장치는, 발광 표시 장치, 액정 표시 장치, 및 전기영동 소자를 포함하는 표시 장치를 포함한다. 발광 장치는 발광 소자를 포함하고, 액정 표시 장치는 액정 소자를 포함한다. 발광소자는, 전류 또는 전압에 의해 휘도가 제어되는 소자를 그 범주에 포함하고, 구체적으로는 무기 EL(Electro Luminescence), 유기 EL 등을 포함한다.

개시된 발명의 실시형태에서, 광전 변환 소자는 광 투과성 기판 위의 단결정 반도체층을 사용하여 형성된다. 따라서, 높은 광 감도를 갖는 광전 변환 소자가 광 투과성 기판 위에 제공되는 반도체 장치가 제공될 수 있다.

개시된 발명의 실시형태에서, 광전 변환 소자가 단결정 반도체의 단일층을 사용하여 형성된다. 따라서, 반도체 장치의 제작 공정들은, 광전 변환 소자가 반도체층들의 적층 구조로 형성되는 경우에 비교하여 간략화될 수 있다.

도 1a는 반도체 장치의 일례를 나타내는 평면도이고 도 1b는 단면도.

도 2a 내지 도 2f는 반도체 장치에 사용되는 SOI 기판의 제작 방법의 일례를 나타내는 단면도.

도 3a 내지 도 3c는 반도체 장치에 사용되는 SOI 기판의 제작 방법의 일례를 나타내는 단면도.

도 4a 내지 도 4h는 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

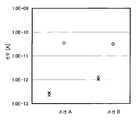

도 5는 광전 변환 소자의 도즈량과 전류 사이의 관계를 도시한 도면.

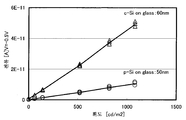

도 6은 광전 변환 소자의 휘도-전류 특성을 도시하는 그래프.

도 7a는 반도체 장치의 일례를 나타내는 평면도이고 도 7b는 단면도.

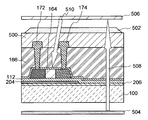

도 8은 반도체 장치의 일례를 나타내는 단면도.

도 9a 내지 도 9g는 반도체 장치에 사용되는 SOI 기판의 제작 방법의 일례를 나타내는 단면도.

도 10a 내지 도 10h는 SOI 기판 및 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 11a 내지 도 11h는 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 12a 및 도 12b는 반도체 장치의 일례를 나타내는 평면도.

도 13a 내지 도 13g는 반도체 장치에 사용되는 SOI 기판의 제작 방법의 일례를 나타내는 단면도.

도 14a 내지 도 14f는 SOI 기판 및 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 15a 내지 도 15g는 반도체 장치에 사용되는 SOI 기판의 제작 방법의 일례를 나타내는 단면도.

도 16a 내지 도 16h는 SOI 기판 및 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 17a 내지 도 17h는 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 18a는 반도체 장치의 일례를 나타내는 평면도이고 도 18b는 단면도.

도 19a 내지 도 19d는 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 20a 내지 도 20d는 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 21a 내지 도 21c는 SOI 기판 및 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

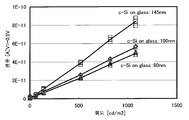

도 22는 광전 변환 소자의 휘도-전류 특성을 도시하는 그래프.

도 23a는 반도체 장치의 일례를 나타내는 평면도이고 도 23b는 단면도.

도 24a 내지 도 24c는 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 25a는 반도체 장치의 일례를 나타내는 평면도이고 도 25b는 단면도.

도 26a 내지 도 26d는 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 27a 내지 도 27d는 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 28a 내지 도 28c는 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 2a 내지 도 2f는 반도체 장치에 사용되는 SOI 기판의 제작 방법의 일례를 나타내는 단면도.

도 3a 내지 도 3c는 반도체 장치에 사용되는 SOI 기판의 제작 방법의 일례를 나타내는 단면도.

도 4a 내지 도 4h는 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 5는 광전 변환 소자의 도즈량과 전류 사이의 관계를 도시한 도면.

도 6은 광전 변환 소자의 휘도-전류 특성을 도시하는 그래프.

도 7a는 반도체 장치의 일례를 나타내는 평면도이고 도 7b는 단면도.

도 8은 반도체 장치의 일례를 나타내는 단면도.

도 9a 내지 도 9g는 반도체 장치에 사용되는 SOI 기판의 제작 방법의 일례를 나타내는 단면도.

도 10a 내지 도 10h는 SOI 기판 및 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 11a 내지 도 11h는 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 12a 및 도 12b는 반도체 장치의 일례를 나타내는 평면도.

도 13a 내지 도 13g는 반도체 장치에 사용되는 SOI 기판의 제작 방법의 일례를 나타내는 단면도.

도 14a 내지 도 14f는 SOI 기판 및 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 15a 내지 도 15g는 반도체 장치에 사용되는 SOI 기판의 제작 방법의 일례를 나타내는 단면도.

도 16a 내지 도 16h는 SOI 기판 및 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 17a 내지 도 17h는 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 18a는 반도체 장치의 일례를 나타내는 평면도이고 도 18b는 단면도.

도 19a 내지 도 19d는 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 20a 내지 도 20d는 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 21a 내지 도 21c는 SOI 기판 및 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 22는 광전 변환 소자의 휘도-전류 특성을 도시하는 그래프.

도 23a는 반도체 장치의 일례를 나타내는 평면도이고 도 23b는 단면도.

도 24a 내지 도 24c는 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 25a는 반도체 장치의 일례를 나타내는 평면도이고 도 25b는 단면도.

도 26a 내지 도 26d는 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 27a 내지 도 27d는 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

도 28a 내지 도 28c는 반도체 장치의 제작 방법의 일례를 나타내는 단면도.

이하, 실시형태들이 도면을 사용하여 상세하게 설명된다. 본 발명이 실시형태들의 설명에 한정되지 않고, 본 명세서 등에서 개시된 발명의 사상으로부터 일탈하는 일 없이 모드들 및 상세들이 다양한 방식으로 변경될 수 있다는 것이 당업자에게 있어 자명하다는 것에 유의한다. 상이한 실시형태의 구조가, 적절히 조합에 의해 구현될 수 있다. 이 도면들을 참조한 본 발명의 설명에 대해, 동일 부분을 나타내는 참조 부호가 상이한 도면 전반적으로 공통으로 사용되며, 반복되는 설명은 생략된다.

(실시형태 1)

이러한 실시형태에서, 반도체 장치 및 그 제작 방법이 도면들을 참조하여 설명될 것이다. 특히, 광전 변환 소자를 구비하는 반도체 장치 및 그 제작 방법이 설명될 것이다.

(구성)

개시된 발명의 실시형태에 관한 광전 변환 소자(180)는 광 투과성 베이스 기판(100) 위에 제공된(도 1a 및 도 1b 참조). 여기서, 도 1b는 도 1a의 라인 A-B를 따라 취해진 단면에 대응한다.

광전 변환 소자(180)는 광전 변환의 효과를 갖는 반도체 영역(164), 제 1 도전형(여기서는 p형 도전성)을 갖는 반도체 영역(158), 및 제 2 도전형(여기서는 n형 도전성)을 갖는 반도체 영역(162)을 포함하는 섬형상 단결정 반도체층; 섬형상 단결정 반도체층을 커버하도록 형성되는 절연층(154) 및 절연층(166); 제 1 도전형을 갖는 반도체 영역(158)에 전기적으로 접속된 제 1 전극(172); 및 제 2 도전형을 갖는 반도체 영역(162)에 전기적으로 접속된 제 2 전극(174)을 포함한다. 여기서, 제 1 도전형을 갖는 반도체 영역(158) 및 제 2 도전형을 갖는 반도체 영역(162)은 광전 변환의 효과를 갖는 반도체 영역(164)에 인접하고, 광전 변환의 효과를 갖는 반도체 영역(164)에 의해 서로 분리된다. 제 1 도전형과 제 2 도전형은 서로 교환가능할 수 있다.

또한, 베이스 기판(100)과 광전 변환 소자(180) 사이에는 절연층(112)이 형성된다. 이 절연층(112)은 광전 변환 소자(180)를 베이스 기판(100)에 고정시키는 기능을 갖는다.

광전 변환 소자(180)의 동작은 이하와 같다. 광전 변환 소자(180)에 있어서, 광전 변환의 효과를 갖는 반도체 영역(164)에 광이 입사하면, 이 반도체 영역에는 전자 및 정공이 생성된다. 제 1 도전형을 갖는 반도체 영역(158)과 제 2 도전형을 갖는 반도체 영역(162) 사이의 영역에 외부로부터 전압이 인가되어 있지 않은 경우에(무-바이어스(non-bias)의 경우에), 생성된 전자들은 자기-정합(self-aligned) 전기장의 영향으로 인해 n형 반도체 영역을 향한 방향으로 흐른다. 유사한 방식으로, 생성된 정공은, p형 반도체 영역을 향한 방향으로 흐른다. 외부로부터 전압이 인가되는 경우에(예를 들어, 역바이어스가 인가되는 경우에), 자기-정합 전기장 및 외부로부터의 전압의 영향으로 인해 전자 및 정공이 흐른다.

발생한 전류의 광 강도에 대한 의존성을 이용함으로써, 광 센서가 형성될 수 있다. 또한, 광에 의한 기전력을 광전 변환 소자의 외부로 추출함으로써, 발전 시스템이 획득될 수 있다.

여기서, 광전 변환 소자에 포함된 섬형상 반도체층의 결정성은 단결정인 것이 바람직하다. 특히, 광전 변환의 효과를 갖는 반도체 영역(164)의 결정성은 단결정이다. 단결정의 반도체 재료로서는, 예를 들어, 단결정 실리콘이 사용될 수 있다. 단결정 반도체가 광전 변환 소자에서 사용될 때, 비정질 반도체 또는 다결정 반도체를 사용하는 경우와 비교하여, 암전류(광 조사가 실시되지 않을 때의 전류)의 양이 감소될 수 있다. 또한, 단결정 반도체가 광전 변환 소자에서 사용될 때, 다결정 반도체를 사용하는 경우와 비교하여, 광 조사가 실시될 때의 전류가 증가될 수 있다. 따라서, 광 센서로서의 감도가 향상된다. 또한, 단결정 반도체를 이용하는 것에 따라, 광전 변환 효율이 향상된다. 이들의 효과는 결함 등으로 인한 광 생성 캐리어들의 트랩이 충분히 억제될 수 있기 때문에 획득된다.

또한, 여기서 나타내는 바와 같이, 베이스 기판의 광 투과성 때문에, 대상물로부터의 광(대상물로부터의 반사광 등)이 베이스 기판측으로부터 입사하는 구성(광이 베이스 기판측으로부터 검출되는 구성)이 이용될 수 있다. 이러한 경우에서, 대상물의 광이 전극(또는 배선) 측으로부터 입사하는 경우와 비교하여, 소자 레이아웃의 자유도가 향상된다. 이러한 방식으로, 베이스 기판이 광 투과성을 가질 때, 베이스 기판이 광 투과성을 가지지 않는 경우와 비교하여, 집적화가 용이하게 실시될 수 있다는 장점이 있다.

(제작 공정들)

다음으로, 광전 변환 소자의 제작 공정들에 대해 설명한다. 먼저, 광전 변환 소자의 제작에 사용될 수 있는 SOI 기판의 제작 공정들이 도 2a 내지 도 2f 및 도 3a 내지 도 3c를 참조하여 설명된다. 그 후, SOI 기판이 사용되는 광전 변환 소자의 제작 공정들이 도 4a 내지 도 4h를 참조하여 설명된다.

(SOI 기판의 제작 공정들 - 베이스 기판의 가공)

먼저, 광 투과성 베이스 기판(100)이 준비된다(도 2a 참조).

광 투과성 베이스 기판(100)으로서, 절연체로 형성된 기판이 사용될 수 있다. 그 특정한 예들이 다음과 같다: 알루미노실리케이트 유리, 알루미노보로실리케이트 유리, 및 바륨 보로실리케이트 유리와 같은 전자 산업에서 사용된 다양한 유리 기판; 석영 기판; 세라믹 기판; 및 사파이어 기판. 유리 기판이 붕산보다 더 많은 양의 산화 바륨을 포함할 때, 더욱 실용적인 내열 유리가 얻어질 수 있다는 것에 유의한다. 따라서, 유리 기판이 내열성을 가질 필요가 있을 때, 산화 바륨의 양이 붕산의 양보다 크도록 산화 바륨 및 붕산을 포함하는 유리 기판을 사용하는 것이 바람직하다. 이러한 실시형태에서, 베이스 기판(100)으로서 유리 기판이 사용되는 경우의 설명이 제공된다. 베이스 기판(100)으로서 더 큰 사이즈를 가질 수 있고 염가의 유리 기판이 사용될 때, 비용 절감이 달성될 수 있다.

베이스 기판(100)의 표면은 바람직하게는 미리 세정된다. 구체적으로는, 베이스 기판(100)에 대해, 염산 과수(HPM), 황산 과수(SPM), 암모니아과수(APM), 희불화수소산(DHF) 등을 사용함으로써 초음파 세정이 실시된다. 이와 같은 세정 처리를 통해, 베이스 기판(100)의 표면 평탄성이 향상될 수 있고, 베이스 기판(100)의 표면상에 잔존하는 연마 입자들이 제거될 수 있다.

또한, 베이스 기판(100)의 표면에는, 질소를 함유하는 절연층(예를 들어, 질화 실리콘(SiNx), 질화 산화 실리콘(SiNxOy)(x>y) 등을 포함하는 절연층)이 형성될 수 있다는 것에 유의한다. 이러한 방식으로, 질소를 함유하는 절연층이 형성될 때, 베이스 기판에 함유되는 나트륨(Na)과 같은 불순물 원소의 반도체에 대한 확산이 억제될 수 있다.

본 명세서 등에서, 산화 질화물은, 질소(원자수)보다 많은 산소(원자수)를 함유하는 물질을 칭한다는 것에 유의한다. 예를 들어, 산화 질화 실리콘은, 산소가 50 원자% 이상 70 원자% 이하, 질소가 0.5 원자% 이상 15 원자% 이하, 실리콘이 25 원자% 이상 35 원자% 이하, 수소가 0.1 원자% 이상 10 원자% 이하의 범위에서 함유되는 물질을 칭한다. 또한, 질화 산화물은, 질소 함유량(원자수)이 산소 함유량(원자수)을 초과하는 물질을 의미한다. 예를 들어, 질화 산화 실리콘이란, 산소가 5 원자% 이상 30 원자% 이하, 질소가 20 원자% 이상 55 원자% 이하, 실리콘이 25 원자% 이상 35 원자% 이하, 수소가 10 원자% 이상 30 원자% 이하의 범위에서 함유되는 물질을 칭한다. 상기 범위들은, 측정이 러더포드 후방 산란법(RBS:Rutherford Backscattering Spectrometry) 또는 수소 전방 산란법(HFS:Hydrogen Forward scattering Spectrometry)을 사용하여 실시된 경우의 범위들이라는 것에 유의한다. 또한, 구성 원소의 함유 비율의 합계는, 최대 100 원자%이다.

(SOI 기판의 제작 공정들: 단결정 반도체 기판의 가공)

다음으로, 본드 기판으로서 단결정 반도체 기판(110)이 준비된다(도 2b 참조). 이러한 실시형태에서, 베이스 기판(100)이 가공된 이후에, 본드 기판으로서 단결정 반도체 기판(110)이 가공되지만, 개시된 발명의 실시형태는 이에 한정되는 것으로 해석되지 않는다. 단결정 반도체 기판의 가공이 베이스 기판의 가공 이전에 실시될 수도 있다. 다르게는, 베이스 기판 및 본드 기판이 동시에 가공될 수도 있다.

단결정 반도체 기판(110)으로서, 단결정 실리콘 기판, 단결정 게르마늄 기판, 또는 단결정 실리콘 게르마늄 기판과 같은 주기율표의 제 14 족에 속하는 원소들로 형성된 단결정 반도체 기판이 사용될 수 있다. 다르게는, 갈륨 비소 기판, 인듐 인 기판 등의 화합물의 단결정 반도체 기판이 사용될 수도 있다. 시판되는 실리콘 기판들의 통상의 예들은 직경 5 인치(125 mm), 직경 6 인치(150 mm), 직경 8 인치(200 mm), 직경 12 인치(300 mm), 직경 16 인치(400 mm) 사이즈의 원형 실리콘 기판들이다. 단결정 반도체 기판(110)의 형상은 원형에 한정되지 않고, 단결정 반도체 기판(110)은 예를 들어, 직사각형 형상 등으로 가공된 기판일 수도 있다는 것에 유의한다. 다르게는, 단결정 반도체 기판(110)은, CZ법 또는 FZ(플로팅 존)법을 사용하여 제작될 수 있다.

이러한 실시형태에서, 본드 기판으로서 집적 회로에 대해 단결정 실리콘 기판을 사용하는 경우가 설명되지만, 개시된 발명의 실시형태는 이러한 구조에 한정되는 것으로 해석되지 않는다는 것에 유의한다. 예를 들어, 태양 전지급의 단결정 실리콘 기판이 사용될 수도 있다. 다르게는, 다결정 실리콘 기판을 포함하는 다결정 반도체 기판이 사용될 수 있다. 제작될 광전 변환 소자의 특성을 고려하면, 단결정 반도체 기판을 사용하는 것이 바람직하다는 것에 유의한다.

단결정 반도체 기판(110)의 표면상에 절연층(112)이 형성된다(도 2c 참조). 오염물 제거의 관점에서, 절연층(112)의 형성 이전에, 황산 과수(SPM), 암모니아 과수(APM), 염산 과수(HPM), 희불화수소산(DHF), FPM(불화수소산, 과산화수소수, 순수의 혼합액) 등으로 단결정 반도체 기판(110)의 표면을 세정하는 것이 바람직하다. 다르게는, 희불화수소산과 오존수가 세정을 위해 교대로 토출될 수도 있다.

절연층(112)은 산화 실리콘막, 산화 질화 실리콘막 등의 단층으로, 또는 이들 막들의 적층으로 형성될 수 있다. 절연층(112)을 제작하기 위해 열산화법, CVD법, 스퍼터링법 등이 이용될 수 있다. 절연층(112)이 CVD법에 의해 형성될 때,, 테트라에톡시실란(약칭: TEOS, 화학식 Si(OC2H5)4)과 같은 유기 실란을 사용하여 산화 실리콘막이 형성되는 것이 바람직하다.

이러한 실시형태에서, 단결정 반도체 기판(110)에 열산화 처리를 실시함으로써, 절연층(112)(여기서, 산화 실리콘막)이 형성된다.

열산화 처리는, 할로겐이 첨가된 산화 분위기에서 실시되는 것이 바람직하다. 예를 들어, 염소(Cl)가 첨가된 산화성 분위기에서 단결정 반도체 기판(110)에 열산화 처리를 실시함으로써, 절연층(112)이 염소 산화를 통해 형성된다. 이러한 경우에서, 절연층(112)은 염소 원자를 함유하는 절연층이다.

절연층(112)에 함유된 염소 원자는 절연층(112)에서 변형을 형성한다. 그 결과, 절연층(112)의 물 흡수율이 증가되고, 물의 확산 속도가 증가된다. 다시 말해, 절연층(112)의 표면에 물이 존재하는 경우에, 그 표면에 존재하는 물은 절연층(112)으로 빠르게 흡수될 수 있고, 거기로 확산될 수 있다. 따라서, 물에 의해 야기된 불량 본딩이 억제될 수 있다.

또한, 절연층(112)에 함유된 염소 원자로, 외인성의 불순물인 중금속(예를 들어, Fe, Cr, Ni, Mo 등)이 포집될 수 있어서, 단결정 반도체 기판(110)의 오염이 방지될 수 있다. 또한, 베이스 기판(100)에 접합한 이후에, 베이스 기판(100)으로부터의 나트륨(Na)과 같은 불순물이 고정될 수도 있어서, 단결정 반도체 기판(110)의 오염이 방지될 수 있다.

절연층(112)에 함유된 할로겐 원자는 염소 원자에 한정되지 않는다는 것에 유의한다. 절연층(112)에는 불소 원자가 함유될 수도 있다. 예를 들어, 단결정 반도체 기판(110)의 표면이 불소로 산화되는 방법이 사용될 수 있다. 불소 산화의 예로서, 단결정 반도체 기판(110)이 HF 용액에 침지되고, 그 후 산화성 분위기에서 열산화 처리가 실시되는 방법, NF3를 산화성 분위기에 첨가하여 열산화 처리를 실시하는 방법 등이 제공된다.

다음으로, 전계에 의해 가속된 이온이 단결정 반도체 기판(110)에 첨가됨으로써, 단결정 반도체 기판(110)의 소정의 깊이에서 결정 구조가 손상되는 취화 영역(114)이 형성된다(도 2d 참조)는 것에 유의한다. 또한, 이온의 첨가 처리 이전에, 단결정 반도체 기판(110)의 표면 및 절연층(112)의 표면이 세정되는 것이 바람직하다.

취화 영역(114)이 형성되는 깊이는, 이온의 운동 에너지, 질량, 전하, 이온의 입사각 등에 의해 조절될 수 있다. 취화 영역(114)은, 이온의 평균 침입 깊이와 거의 동일한 깊이에 형성된다. 따라서, 이온이 첨가되는 깊이로, 단결정 반도체 기판(110)으로부터 분리될 단결정 반도체층의 두께가 조절될 수 있다. 예를 들어, 단결정 반도체층의 두께가, 대략 10 nm 이상 1μm 이도록 평균 침입 깊이가 조절될 수도 있다. 광전 변환 장치의 특징은, 단결정 반도체층의 두께가 소정의 두께이상일 때 대폭 향상되는 경향이 있다. 따라서, 예를 들어, 단결정 반도체층은 100 nm 이상의 두께로 형성되는 것이 바람직하다.

상기 이온의 조사 처리는, 이온 도핑 장치 또는 이온 주입 장치로 실시될 수 있다. 이온 도핑 장치의 통상의 예로서, 프로세스 가스의 플라즈마 여기가 실시되고 피처리체가 생성된 모든 종류의 이온종들에 의해 조사되는 비질량 분리형의 장치가 있다. 이러한 장치에서, 피처리체는 질량 분리하지 않고 플라즈마의 이온종으로 조사된다. 이와 반대로, 이온 주입 장치는 질량 분리 장치이다. 이온 주입 장치에서, 플라즈마의 이온종의 질량 분리가 실시되고, 소정의 질량들을 갖는 이온종으로 피처리체가 조사된다.

이러한 실시형태에서, 이온 도핑 장치가 수소를 단결정 반도체 기판(110)에 첨가하기 위해 사용되는 예가 설명된다. 소스 가스로서 수소를 함유하는 가스가 사용된다. 조사를 위해 사용된 이온에 대해서는, H3 +의 비율이 높게 설정되는 것이 바람직하다. 구체적으로는, H+, H2 +, H3 +의 총량에 대해 H3 +의 비율이 50% 이상(보다 바람직하게는 80% 이상)이 되도록 설정되는 것이 바람직하다. H3 +의 비율을 높이는 것으로, 이온 조사의 효율이 향상될 수 있다.

첨가될 이온은 수소의 이온으로 한정되지 않는다는 것에 유의한다. 헬륨 등의 이온이 첨가될 수도 있다. 또한, 첨가될 이온은 하나의 종류의 이온으로 한정되지 않고, 복수의 종류의 이온이 첨가될 수도 있다. 예를 들어, 이온 도핑 장치를 이용하여 수소와 헬륨으로 동시에 조사를 실시하는 경우에, 다른 공정들에서 수소 및 헬륨의 조사를 실시하는 경우에 비교하여 공정들의 수가 감소될 수 있고, 이후에 형성될 단결정 반도체층의 표면 거칠기의 증가가 억제될 수 있다.

이온 도핑 장치를 이용하여 취화 영역(114)이 형성될 때, 중금속이 또한 첨가될 수도 있지만, 할로겐 원자를 함유하는 절연층(112)을 통해 이온 조사가 실시됨으로써, 중금속으로 인한 단결정 반도체 기판(110)의 오염이 방지될 수 있다는 것에 유의한다.

(SOI 기판의 제작 공정들: 기판의 접합)

다음으로, 베이스 기판(100)의 표면과 단결정 반도체 기판(110)의 표면이 서로 대향하고, 베이스 기판(100)의 표면과 절연층(112)의 표면이 서로 밀착된다는 것에 유의한다. 따라서, 베이스 기판(100)과 단결정 반도체 기판(110)이 함께 접합된다(도 2e 참조).

접합이 실시될 때, 베이스 기판(100)의 일부 또는 단결정 반도체 기판(110)의 일부에 0.001 N/cm2 이상 100 N/cm2 이하의 압력이 인가되는 것이 바람직하다. 특히, 1 N/cm2 이상 20 N/cm2 이하의 압력이 인가되는 것이 바람직하다. 압력이 인가되는 부분에서 베이스 기판(100)과 절연층(112) 사이의 접합이 생성되고, 그 부분으로부터 자발적인 접합이 전체 표면 전반적으로 진행된다. 이러한 접합은, 반 데르 발스의 힘 또는 수소 접합의 작용하에서 실행되고, 실온에서 실시될 수 있다.

단결정 반도체 기판(110) 및 베이스 기판(100)이 함께 접합되기 이전에, 함께 접합될 표면들에 대해 표면 처리를 실시하는 것이 바람직하다는 것에 유의한다. 표면 처리에 의해, 함께 접합될 표면들 사이의 계면에서의 접합 강도가 향상될 수 있다.

표면 처리로서, 웨트 처리, 드라이 처리, 또는 웨트 처리와 드라이 처리의 조합이 사용될 수 있다. 다르게는, 상이한 웨트 처리와 조합하여 웨트 처리가 사용될 수도 있거나, 상이한 드라이 처리와 조합하여 드라이 처리가 사용될 수도 있다.

웨트 처리의 예들로서, 오존수를 사용한 오존 처리(오존수 세정), 메가소닉 세정, 또는 2-유체 세정(순수나 수소 첨가 물과 같은 기능성 물 및 질소와 같은 캐리어 가스가 함께 스프레이되는 방법) 등이 제공될 수 있다. 드라이 처리의 예들로서, 자외선 처리, 오존 처리, 플라즈마 처리, 바이어스 인가 플라즈마 처리, 또는 라디칼 처리 등이 제공될 수 있다. 피처리체(단결정 반도체 기판, 단결정 반도체 기판상에 형성된 절연층, 지지 기판, 또는 지지 기판상에 형성된 절연층)에 대한 상술한 표면 처리는 피처리체의 표면상의 친수성 및 청정성을 향상시키는 효과를 갖는다. 그 결과, 기판들 사이의 접합 강도가 향상될 수 있다.

웨트 처리는 피처리체의 표면에 부착하는 큰 먼지 등의 제거에 효과적이다. 드라이 처리는 피처리체의 표면에 부착하는 유기 물질과 같은 미소한 먼지의 제거 또는 분해에 효과적이다. 자외선 처리와 같은 드라이 처리가 실시된 후, 세정과 같은 웨트 처리가 실시되는 경우가 피처리체의 표면이 청정화 및 친수화될 수 있고, 피처리체의 표면의 워터마크의 생성이 억제될 수 있기 때문에 바람직하다.

드라이 처리로서, 오존 또는 일중항산소(singlet oxygen)와 같은 활성 상태에 있는 산소를 사용하여 표면 처리를 실시하는 것이 바람직하다. 오존 또는 일중항산소와 같은 활성 상태에 있는 산소는 피처리체 표면에 접합된 유기 물질이 효과적으로 제거 또는 분해될 수 있게 한다. 또한, 오존 또는 일중항산소와 같은 활성 상태에 있는 산소를 사용하는 처리는 200 nm 미만의 파장을 갖는 자외광을 사용하는 처리와 조합될 수 있어서, 피처리체 표면에 접합된 유기 물질이 더욱 효과적으로 제거될 수 있다. 이하, 이에 대한 특정한 설명이 이루어진다.

예를 들어, 산소를 함유하는 분위기하에서 자외광을 이용한 조사는, 피처리체의 표면 처리를 실시하기 위해 실시된다. 산소를 함유하는 분위기하에서, 200 nm미만의 파장을 갖는 자외광 및 200 nm 이상의 파장을 갖는 자외광을 이용한 조사가 실시될 수도 있어서, 오존 및 일중항산소가 생성될 수 있다. 다르게는, 180 nm미만의 파장을 갖는 자외광을 이용한 조사가 실시될 수도 있어서, 오존 및 일중항산소가 생성될 수 있다.

산소를 함유하는 분위기하에서, 200 nm 미만의 파장을 포함하는 광 및 200 nm 이상의 파장을 포함하는 광으로 조사를 실시함으로써 발생하는 반응들의 예들이 설명된다.

상기 반응식 (1)에서, 산소(O2)를 함유하는 분위기하에서 200 nm 미만의 파장(λ1 nm)을 포함하는 광을 이용한 조사가 실시되어, 기저 상태의 산소 원자(O(3P))를 생성한다. 다음으로, 반응식 (2)에서, 기저 상태의 산소 원자(O(3P))와 산소(O2)가 서로 반응하여 오존(O3)을 생성한다. 그 후, 반응식 (3)에서, 생성된 오존(O3)을 함유하는 분위기하에서 200 nm 이상의 파장(λ2 nm)을 갖는 광을 이용한 조사가 실시되어, 여기 상태의 일중항산소(O(1D))를 생성한다. 산소를 함유하는 분위기하에서, 자외선중 200 nm 미만의 파장을 포함하는 광을 이용한 조사가 실시되어, 오존을 생성하면서, 자외선중 200 nm 이상의 파장을 포함하는 광을 이용한 조사가 실시되어, 오존을 분해함으로써 일중항산소를 생성한다. 상술한 표면 처리는, 예를 들어, 산소를 함유하는 분위기하에서 저압 수은 램프를 이용한 조사(λ1=185 nm,λ2=254 nm)에 의해 실시될 수 있다.

산소를 함유하는 분위기하에서, 180 nm 미만의 파장을 갖는 자외광을 이용한 조사에 의해 야기되는 반응의 예가 아래에 설명된다.

상기 반응식 (4)에서, 산소(O2)를 함유하는 분위기하에서 180 nm 미만의 파장(λ3 nm)을 갖는 광을 이용한 조사가 실시되어, 여기 상태의 일중항산소 (O(1D))와 기저 상태의 산소 원자(O(3P))를 생성한다. 다음으로, 반응식 (5)에서, 기저 상태의 산소 원자(O(3P))와 산소(O2)가 서로 반응하여, 오존(O3)을 생성한다. 반응식 (6)에서, 생성된 오존(O3)을 함유하는 분위기하에서 180 nm 미만의 파장(λ3 nm)을 포함하는 광을 이용한 조사가 실시되어, 여기 상태의 일중항산소와 산소를 생성한다. 산소를 함유하는 분위기하에서, 자외선중 180 nm 미만의 파장을 포함하는 광을 이용한 조사가 실시되어, 오존을 생성하고 오존 또는 산소를 분해함으로써 일중항산소를 생성한다. 상술한 표면 처리는, 예를 들어, 산소를 함유하는 분위기하에서 Xe 엑시머 UV 램프를 이용한 조사에 의해 실시될 수 있다.

200 nm 미만의 파장을 갖는 자외광에 의해 피처리체 표면에 접합된 유기 물질의 화학 결합이 절단되고, 오존 또는 일중항산소에 의해 피처리체 표면에 접합된 유기 물질 또는 화학 결합이 절단된 유기 물질이 산화 분해되어 제거될 수 있다. 상술한 바와 같은 표면 처리는, 피처리체 표면의 친수성 및 청정성을 강화할 수 있고, 접합을 바람직하게 만들 수 있다.

접합이 실시된 이후에, 접합 강도를 향상시키기 위한 열처리가 실시될 수도 있다. 이러한 열처리는, 취화 영역(114)에서 분리가 발생하지 않는 온도(예를 들어, 실온 이상 400℃ 미만)에서 실시된다는 것에 유의한다. 이러한 온도 범위의 온도에서 가열하면서, 베이스 기판(100) 및 절연층(112)이 함께 접합될 수도 있다. 열처리는, 확산노, 저항 가열노와 같은 가열노, RTA(순간 열 어닐링; rapid thermal annealing) 장치, 마이크로파 가열 장치 등을 사용하여 실시될 수 있다. 상기 온도 조건은 단지 예이고, 개시된 발명의 실시형태가 이러한 예에 한정되는 것으로서 해석되어서는 안된다.

(SOI 기판의 제작 공정들: 단결정 반도체층의 형성)

다음으로, 예를 들어, 400℃ 이상 또는 베이스 기판(100)의 내열 온도 이하의 온도에서 열 처리가 실시되어, 단결정 반도체 기판(110)을 취화 영역(114)에서 분리함으로써, 베이스 기판(100)상에, 절연층(112)을 개재하여 단결정 반도체층 (116)이 형성된다(도 2f 및 도 3a 참조).

열 처리가 실시될 때, 취화 영역(114)에 형성되는 마이크로보이드에는 첨가된 원소가 분자로서 석출되어, 마이크로보이드의 내부 압력이 상승된다. 상승된 압력은, 취화 영역(114)에서 크랙을 발생시켜, 취화 영역(114)을 따라 단결정 반도체 기판(110)이 분리된다. 절연층(112)이 베이스 기판(100)에 접합되기 때문에, 베이스 기판(100) 위에는 단결정 반도체 기판(110)으로부터 분리된 단결정 반도체층(116)이 잔존한다.

다음으로, 단결정 반도체층(116)의 표면이 레이저 빔(130)으로 조사됨으로써, 표면의 평탄성이 향상되고, 결함의 수가 저감된 단결정 반도체층(118)이 형성된다(도 3b 및 도 3c 참조).

레이저 빔(130)을 이용한 조사에 의해 단결정 반도체층(116)이 부분적으로 용융되는 것이 바람직하다는 것에 유의한다. 단결정 반도체층(116)이 완전하게 용융된 경우에는, 액상이 된 이후에 무질서한 핵 생성으로 인해 미결정화되어, 그것의 결정성이 저하하기 때문이다. 한편, 부분 용융함으로써, 용융되어 있지 않은 고상 부분에 기초하여 결정 성장이 진행한다. 따라서, 단결정 반도체층(116)이 완전하게 용융되는 경우와 비교하여 결정 품질이 향상될 수 있다. 또한, 절연층(112)으로부터의 산소, 질소 등의 혼합이 억제될 수 있다. 상기 설명에서의 "부분 용융"은, 단결정 반도체층(116)의 상면으로부터 절연층(112)의 계면의 상부측까지의 레이저 빔의 조사를 이용한 단결정 반도체층(116)의 용융을 의미한다(즉, 단결정 반도체층(116)의 두께보다 작다)는 것에 유의한다. 다시 말해, 이것은 단결정 반도체층(116)의 상위 부분이 액상으로 용융되지만, 하위 부분은 용융되지 않고 고상으로 남아 있다는 것을 칭한다. 또한, 용어 "완전 용융"은, 단결정 반도체층(116)이 단결정 반도체층(116)과 절연층(112) 사이의 계면까지 용융되어 액체 상태에 있다는 것을 의미한다.

상술한 레이저 빔의 조사에 대해, 펄스 발진 레이저를 사용하는 것이 바람직하다. 이것은, 고에너지 펄스 레이저 빔이 부분적으로 용융된 상태를 용이하게 생성할 수 있기 때문이다. 발진 주파수는, 1 Hz 이상 10 MHz 이하가 바람직하지만 이에 한정되지 않는다. 펄스 레이저의 예들로는, Ar 레이저, Kr 레이저, 엑시머(ArF, KrF, XeCl) 레이저, CO2 레이저, YAG 레이저, YVO4 레이저, YLF 레이저, YAlO3 레이저, GdVO4 레이저, Y2O3 레이저, 루비 레이저, 알렉산드라이트 레이저, Ti:사파이어 레이저, 구리 증기 레이저, 금 증기 레이저 등을 포함한다. 부분 용융을 초래할 수 있으면, 연속파 레이저가 사용될 수도 있다. 연속파 레이저의 예는, Ar 레이저, Kr 레이저, CO2 레이저, YAG 레이저, YVO4 레이저, YLF 레이저, YAlO3 레이저, GdVO4 레이저, Y2O3 레이저, 루비 레이저, 알렉산드라이트 레이저, Ti:사파이어 레이저, 헬륨 카드뮴 레이저 등을 포함한다.

레이저 빔(130)의 파장은, 단결정 반도체층(116)에 의해 레이저 빔이 흡수되도록 파장이 선택될 필요가 있다. 그 파장은, 레이저 빔의 표피 깊이(skin depth) 등을 고려하여 결정될 수도 있다. 예를 들어, 파장은 250 nm 이상 700 nm 이하의 범위에서 설정될 수 있다. 또한, 레이저 빔(130)의 에너지 밀도는, 레이저 빔(130)의 파장, 레이저 빔(130)의 표피 깊이, 단결정 반도체층(116)의 막 두께 등을 고려하여 결정될 수 있다. 레이저 빔(130)의 에너지 밀도는, 예를 들어, 300 mJ/cm2 이상 800 mJ/cm2 이하의 범위에서 설정될 수도 있다. 상기 에너지 밀도의 범위는, 펄스 레이저로서 XeCl 엑시머 레이저(파장:308 nm)가 사용될 때의 일례라는 것에 유의한다.

레이저 빔(130)을 이용한 조사는, 대기 분위기와 같은 산소를 함유하는 분위기, 또는 질소 분위기나 아르곤 분위기와 같은 불활성 분위기에서 실시될 수 있다. 불활성 분위기중에서 레이저 빔(130)을 이용한 조사를 실시하기 위해, 레이저 빔(130)을 이용한 조사는 기밀성 챔버에서 실시될 수도 있고 이 챔버내의 분위기는 제어될 수도 있다. 챔버가 사용되지 않는 경우에서, 레이저 빔(130)으로 조사되는 표면에 질소 가스와 같은 불활성 가스를 내뿜는 것으로, 불활성 분위기가 얻어질 수 있다.

질소 분위기와 같은 불활성 분위기에서의 조사가, 대기 분위기에서의 조사보다 단결정 반도체층(116)의 평탄성을 향상시키는데 더욱 효과적이라는 것에 유의한다. 또한, 불활성 분위기가 대기 분위기보다 크랙 또는 리지의 발생을 억제하는 효과가 높고, 레이저 빔(130)에 적용가능한 에너지 밀도의 범위가 넓어진다. 레이저 빔(130)을 이용한 조사는, 감압 분위기에서 실시될 수도 있다는 것에 유의한다. 감압 분위기에서 레이저 빔(130)을 이용한 조사가 실시되는 경우에, 불활성 분위기에서의 조사에 의해 획득된 바와 동일한 효과가 획득될 수 있다.

이러한 실시형태에서는, 단결정 반도체층(116)의 분리를 위한 열처리 이후에, 레이저 빔(130)을 이용한 조사 처리가 실시되지만, 개시된 발명의 실시형태는 이것에 한정되는 것으로서 해석되지 않는다. 단결정 반도체층(116)의 분리를 위한 열처리 이후에, 단결정 반도체층(116)의 표면에서 다수의 결함을 포함하는 영역을 제거하기 위해 에칭 처리가 실시될 수도 있다. 그 후, 레이저 빔(130)을 이용한 조사 처리가 실시될 수도 있다. 다르게는, 단결정 반도체층(116) 표면의 평탄성이 향상된 이후에, 레이저 빔(130)을 이용한 조사 처리가 실시될 수도 있다. 에칭 처리는, 웨트 에칭 또는 드라이 에칭일 수도 있다는 것에 유의한다.

또한, 레이저 빔(130)을 이용한 조사 처리 이전에, 단결정 반도체층(116)의 표면이 세정되는 것이 바람직하다.

레이저 빔(130)을 이용한 조사가 상술한 바와 같이 실시된 이후에, 단결정 반도체층(116)을 박막화하는 공정이 실시될 수도 있다. 단결정 반도체층(116)을 박막화하기 위해, 드라이 에칭 및 웨트 에칭 중 일방, 또는 양자의 조합이 이용될 수도 있다.

상기 공정들을 통해, 표면의 거칠기가 저감된 단결정 반도체층(118)을 갖는 SOI 기판이 획득될 수 있다(도 3c 참조).

(광전 변환 소자의 제작 공정들)

다음으로, SOI 기판을 이용해 광전 변환 소자(180)를 제작하는 공정들이 설명될 것이다. 먼저, 상기 공정들에 따라, 베이스 기판(100) 위에 절연층(112) 및 단결정 반도체층(118)이 제공되는 구조를 갖는 SOI 기판이 준비된다(도 4a 참조).

단결정 반도체층(118)에는, 붕소, 알루미늄, 갈륨과 같은 소량의 p형 불순물 원소, 또는 인, 비소와 같은 소량의 n형 불순물 원소가 첨가될 수도 있다. 불순물 원소가 첨가되는 영역, 및 첨가될 불순물 원소의 종류는, 적절히 변경될 수 있다.

그 후, 마스크(150)가 단결정 반도체층(118) 위에 형성된다. 단결정 반도체층(118)이 마스크(150)를 사용하여 패터닝되어서, 광전 변환 소자에 사용되는 섬형상 반도체층(152)이 형성된다(도 4b 참조). 마스크(150)는, 레지스트 재료를 사용하여 포토리소그래피 등에 의해 형성될 수 있다. 또한, 패터닝시의 에칭 처리로서, 웨트 에칭 또는 드라이 에칭이 이용될 수 있다.

다음으로, 반도체층(152)을 커버하도록 절연층(154)이 형성된다(도 4c 참조). 절연층(154)은 반드시 형성되지 않아도 되지만, 절연층(154)이 형성되는 경우에, 이후에 실시되는 불순물 원소의 첨가시에 반도체층(152)에 대한 손상을 억제할 수 있다. 이러한 실시형태에서, 플라즈마 CVD법에 의해, 단층의 산화 실리콘막이 형성된다는 것에 유의한다. 다르게는, 산화 질화 실리콘, 질화 산화 실리콘, 질화 실리콘, 산화 하프늄, 산화 알루미늄, 산화 탄탈 등을 포함하는 막이, 단층 구조 또는 적층 구조를 갖도록 형성될 수 있다.

플라즈마 CVD법 이외의 제작 방법으로서, 스퍼터링법 또는 고밀도 플라즈마 처리에 의한 산화 또는 질화를 사용하는 방법이 제공될 수 있다. 고밀도 플라즈마 처리는, 예를 들어, 헬륨, 아르곤, 크립톤, 또는 크세논과 같은 희가스, 산소 가스, 산화 질소 가스, 암모니아 가스, 질소 가스, 수소 가스 등과 같은 혼합 가스를 사용하여 실시된다. 이러한 경우에서, 마이크로파의 도입에 의해 플라즈마를 여기함으로써, 저전자 온도 및 고밀도를 갖는 플라즈마가 생성될 수 있다. 이와 같은 고밀도의 플라즈마에 의해 생성된 산소 라디칼(OH 라디칼이 포함될 수도 있음) 또는 질소 라디칼(NH 라디칼이 포함될 수도 있음)에 의해, 반도체층(152)의 표면이 산화 또는 질화될 때, 1 nm 이상 20 nm 이하, 바람직하게는 2 nm 이상 10 nm 이하의 두께를 갖는 절연층(154)이 형성될 수 있다.

고밀도 플라즈마 처리에 의한 반도체층의 산화 또는 질화는 고상 반응이기 때문에, 절연층(154)과 반도체층(152) 사이의 계면 준위 밀도가 충분히 감소될 수 있다. 특히, 반도체층이 단결정인 경우에는, 고밀도 플라즈마 처리를 사용함으로써 반도체층의 표면이 고상 반응에 의해 산화되더라도, 높은 균일성 및 충분히 낮은 계면 준위 밀도를 갖는 절연층(154)이 형성될 수 있다.

다르게는, 반도체층(152)을 열산화함으로써, 절연층(154)이 형성될 수도 있다. 이러한 열 산화의 경우에서, 어느 정도의 내열성을 갖는 베이스 기판(100)을 사용하는 것이 필요하다.

또한, 절연층(154)에 함유된 수소가, 수소를 함유하는 절연층(154)의 형성 이후에, 350℃ 이상 450℃ 이하의 온도에서 열처리를 실시함으로써, 반도체층(152)으로 확산될 수도 있다. 이러한 경우에서, 절연층(154)은 플라즈마 CVD법에 의해 질화 실리콘 또는 질화 산화 실리콘을 사용하여 형성될 수 있다. 또한, 프로세스 온도는 350℃ 이하로 설정되는 것이 바람직하다. 이러한 방식으로, 반도체층(152)에 수소를 공급함으로써, 반도체층(152)에서의 결함, 및 절연층(154)과 반도체층(152) 사이의 계면에 있어서의 결함이 효과적으로 저감될 수 있다.

다음으로, 마스크(156)가 절연층(154) 위에 선택적으로 형성되고, 반도체층(152)의 일부에 제 1 도전형을 부여하는 불순물 원소가 첨가된다. 따라서, 제 1 도전형을 갖는 반도체 영역(158)이 형성된다(도 4d 참조). 여기에서, 제 1 도전형을 부여하는 불순물 원소로서 붕소가 이용되고 제 1 도전형은 p형 도전형이지만, 개시된 발명의 실시형태에 이에 한정되지 않는다. 제 1 도전형을 부여하는 불순물 원소로서 알루미늄 등이 사용될 수도 있다. 또한, 제 1 도전형이 n형 도전형인 경우에서, 인이나 비소 등이 사용될 수도 있다. 마스크(156)는, 마스크(150)와 유사한 방식으로 형성될 수도 있다.

구체적으로는, 예를 들어, 대략 3.0×1014 cm-2 내지 1.0×1017 cm- 2 의 도즈량으로 10kV 내지 40kV의 가속 전압에서 원료 가스로서 B2H6를 사용하여 붕소가 첨가될 수도 있다. 불순물 원소의 첨가의 조건은, 요구되는 특성에 따라 적절히 변경될 수 있다. 도즈량이 감소될 때, 암전류가 감소되는 경향이 있다. 이것은, 저도즈량 조건하에 불순물이 첨가될 때 반도체층(152)에 대한 손상이 작아서, 결함으로 인한 전류가 생성되지 않고, 고도즈량 조건으로 불순물이 첨가될 때 반도체층(152)의 손상이 커져서 결함으로 인한 캐리어 트랩이 생성되기 때문이다. 제 1 도전형을 갖는 반도체 영역(158)의 형성 이후에, 마스크(156)가 제거된다는 것에 유의한다.

그 후, 마스크(160)가 절연층(154) 위에 선택적으로 형성되고, 반도체층(152)의 일부에 제 2 도전형을 부여하는 불순물 원소가 첨가된다. 따라서, 제 2 도전형을 갖는 반도체 영역(162)이 형성되고, 제 1 도전형을 부여하는 불순물 원소 및 제 2 도전형을 부여하는 불순물 원소가 첨가되지 않은 광전 변환의 효과를 갖는 반도체 영역(164)이 형성된다(도 4e 참조). 제 2 도전형은 제 1 도전형과는 상이하다. 즉, 제 1 도전형이 p형일 때, 제 2 도전형은 n형이며, 제 1 도전형이 n형일 때, 제 2 도전형은 p형이다. 여기에서, 제 2 도전형을 부여하는 불순물 원소로서 인이 사용되고 제 2 도전형은 n형이다. 다르게는, n형을 부여하는 불순물 원소로서, 비소 등이 사용될 수 있다. 마스크(160)는, 마스크(150) 또는 마스크(156)와 유사한 방식으로 형성된다.

구체적으로는, 예를 들어, 대략 1.0×1014cm-2 내지 5.0×1016 cm-2의 도즈량으로 10kV 내지 40kV의 가속 전압에서 원료 가스로서 PH3를 사용하여 인이 첨가될 수도 있다. 불순물 원소의 첨가의 조건은, 요구되는 특성에 따라 적절히 변경될 수 있다. 제 1 도전형을 부여하는 불순물 원소를 첨가하는 경우와 유사한 방식으로, 도즈량이 감소될 때 암전류가 억제될 수 있다. 제 2 도전형을 갖는 반도체 영역(162)의 형성 이후에, 마스크(160)는 제거된다.

제 1 도전형을 부여하는 불순물 원소 및 제 2 도전형을 부여하는 불순물 원소의 첨가는, 광전 변환의 효과를 갖는 반도체 영역(164)의 폭이 0.1μm 내지 20μm, 바람직하게는 3μm 내지 10μm가 되도록 실시된다는 것에 유의한다. 물론, 마스크(156) 및 마스크(160)의 가공 정밀도가 허용하면, 반도체 영역(164)의 폭은 0.1μm 이하일 수 있다.

여기서, 도즈량이 변화되는 경우에서의 광전 변환 소자의 특성이 도 5에 예시되어 있다. 도 5에서, 세로축은 전류(A)를 나타낸다. 원은 1000 cd/m2의 광 조사시의 전류(광전류)를 나타내고, X 마크는 광 조사가 실시되지 않을 때의 전류(암전류)를 나타낸다. 도 5의 좌측(조건 A)에서, 제 1 도전형을 부여하는 불순물 원소(여기서는 붕소)의 도즈량은 3.0×1015cm-2이고, 제 2 도전형을 부여하는 불순물 원소(여기서는 인)의 도즈량은 1.0×1015cm-2이다. 도 5의 우측(조건 B)에서는, 제 1 도전형을 부여하는 불순물 원소의 도즈량을 1.0×1016cm-2이고, 제 2 도전형을 부여하는 불순물 원소의 도즈량을 5.0×1015cm-2이다. 조건들 양자에서, 가속 전압은 20 kV라는 것에 유의한다. 또한, 다른 파라미터들은 조건 A 및 조건 B 양자에서 동일하다.

도 5로부터, 첨가된 불순물의 도즈량이 큰 도즈량의 경우(조건 B)와 비교하여 어느 정도 작은 경우(조건 A)에, 암전류가 억제된다는 것이 발견될 수 있다.

그 후, 반도체층(152) 및 절연층(154)을 커버하도록 절연층(166)이 형성된다(도 4f 참조). 절연층(166)이 반드시 제공되지 않더라도, 절연층(166)이 형성될 때, 알칼리 금속 또는 알칼리 토금속과 같은 불순물 원소가 반도체층(152)에 침입하는 것이 방지될 수 있다. 또한, 형성될 광전 변환 소자의 표면을 평탄화될 수 있다.

절연층(166)은, 예를 들어, 산화 실리콘, 질화 실리콘, 산화 질화 실리콘, 질화 산화 실리콘, 질화 알루미늄, 산화 알루미늄과 같은 재료를 사용하여 형성될 수 있다. 이러한 실시형태에서, 절연층(166)은, CVD법에 의해 형성되는 대략 300 nm의 두께의 산화 질화 실리콘막과 대략 600 nm의 두께의 산화 실리콘막의 적층 구조로 형성된다. 물론, 개시된 발명의 실시형태는 이에 한정되지 않는다. 단층 구조 또는 3층 이상의 적층 구조가 이용될 수 있다.

상기 재료들 이외에, 절연층(166)은, 폴리이미드, 아크릴, 벤조사이클로부텐, 폴리아미드, 에폭시와 같은 내열성을 갖는 유기 재료를 사용하여 형성될 수 있다. 이러한 유기 재료 이외에, 예를 들어, 저유전율 재료(low-k 재료), 실록산계 수지, PSG(포스포실리케이트 유리), BPSG(보로포스포실리케이트 유리)를 사용하는 것이 또한 가능하다. 여기서, 실록산계 수지란, 실록산계 재료를 출발 재료로서 사용하여 형성된 Si-O-Si 결합을 포함하는 수지에 대응한다. 아래의 방법들 : CVD법, 스퍼터링 법, SOG법, 스핀 코팅, 딥 코팅, 스프레이 코팅, 또는 액적 토출법(잉크젯법, 스크린 인쇄법, 오프셋 인쇄법)과 같은 방법, 또는 닥터 나이프, 롤 코터, 커튼 코터, 또는 나이프 코터와 같은 도구(장비)가 그 재료에 따라, 적절하게 이용될 수 있다.

다음으로, 반도체층(152)이 부분적으로 노출되도록 절연층(154) 및 절연층(166)에 콘택트홀(168) 및 콘택트홀(170)이 형성된다(도 4g 참조). 여기서 구체적으로, 제 1 도전형을 갖는 반도체 영역(158) 및 제 2 도전형을 갖는 반도체 영역(162)이 부분적으로 노출되도록, 콘택트홀(168) 및 콘택트홀(170)이 형성된다. 콘택트홀(168) 및 콘택트홀(170)은 마스크의 선택적 형성 이후에 에칭 처리 등에 의해 형성될 수 있다. 에칭 처리로서, 에칭 가스로서 CHF3와 He의 혼합 가스를 사용한 드라이 에칭이 이용될 수 있지만, 개시된 발명의 실시형태는 이에 한정되지 않는다.

콘택트홀을 통해 반도체층(152)과 접촉하는 도전층이 형성되고, 그 후, 제 1 전극(172) 및 제 2 전극(174)이 형성되도록 패터닝된다(도 4h 참조). 제 1 전극(172) 및 제 2 전극(174)이 형성되는 도전층은, CVD법, 스퍼터링법, 증착법 등에 의해 형성될 수 있다. 구체적으로는, 도전층의 재료로서, 알루미늄(Al), 텅스텐(W), 티타늄(Ti), 탄탈(Ta), 몰리브덴(Mo), 니켈(Ni), 백금(Pt), 구리(Cu), 금(Au), 은(Ag), 망간(Mn), 네오디뮴(Nd), 탄소(C), 규소(Si) 등이 사용될 수 있다. 다르게는, 상술한 재료를 주성분으로 함유하는 합금 또는 상술한 재료를 함유하는 화합물이 사용될 수도 있다. 도전층은 단층 구조 또는 적층 구조를 가질 수도 있다는 것에 유의한다.

알루미늄을 주성분으로서 함유하는 합금의 예로서, 알루미늄을 주성분으로서 함유하고 니켈을 또한 함유하는 합금이 제공될 수 있다. 또한, 알루미늄을 주성분으로서 함유하고, 또한 니켈과 탄소 또는 규소의 하나 또는 둘을 함유하는 합금이 그 예로서 또한 제공될 수 있다. 알루미늄 및 알루미늄 실리콘(Al-Si)은 낮은 저항값을 갖고, 저렴하기 때문에, 알루미늄 및 알루미늄 실리콘은 제 1 전극(172) 및 제 2 전극(174)을 형성하는 재료로서 적합하다. 특히, 알루미늄 실리콘은, 패터닝시에 레지스트 베이킹(resist baking)으로 인한 힐록(hillock)의 생성이 억제될 수 있기 때문에 바람직하다. 또한, 규소 대신에, 알루미늄에 대략 0.5%의 Cu가 혼합된 재료가 사용될 수도 있다.

제 1 전극(172) 및 제 2 전극(174) 각각이 적층 구조를 갖도록 도전층이 적층구조로 형성되는 경우에, 예를 들어, 배리어막, 알루미늄 실리콘막, 및 배리어막의 적층 구조; 배리어막, 알루미늄 실리콘막, 질화 티타늄막, 및 배리어막의 적층 구조 등이 사용될 수 있다. 배리어막은 티타늄, 티타늄의 질화물, 몰리브덴 또는 몰리브덴의 질화물 등을 사용하여 형성된 막을 칭한다는 것에 유의한다. 배리어막들의 사이에 알루미늄 실리콘막이 개재되도록 도전막을 형성함으로써, 알루미늄 또는 알루미늄 실리콘의 힐록의 발생이 더 방지될 수 있다. 높은 환원성을 갖는 원소인 티타늄을 사용하여 배리어막이 형성될 때, 제 1 도전형을 갖는 반도체 영역(158) 및 제 2 도전형을 갖는 반도체 영역(162) 위에 얇은 산화막이 형성되더라도, 배리어막에 함유된 티타늄에 의해 그 산화막이 환원되어서, 제 1 도전형을 갖는 반도체 영역(158)과 제 1 전극(172) 사이, 및 제 2 도전형을 갖는 반도체 영역(162)과 제 2 전극(174) 사이의 양호한 콘택트가 획득될 수 있다. 다르게는, 복수의 배리어막을 적층하는 것이 또한 가능하다. 그 경우에서, 예를 들어, 바닥으로부터 티타늄, 질화 티타늄, 알루미늄 실리콘, 티타늄, 및 질화 티타늄의 5개 층 구조, 또는 5개보다 많은 층들의 적층 구조가 이용될 수 있다.

도전층으로서, WF6 가스와 SiH4 가스를 사용하여 화학 기상 성장법에 의해 형성된 텅스텐 실리사이드가 사용될 수도 있다. 다르게는, WF6의 수소 환원에 의해 형성된 텅스텐이 도전층으로 사용될 수도 있다.

이러한 방식으로, 광 투과성 베이스 기판(100)상에, 광전 변환 소자(180)가 형성된다.

(광전 변환 소자의 특성)

다음으로, 상기 방법에 따라 얻어진 광전 변환 소자의 특성(휘도-전류 특성)의 일례가 설명될 것이다(도 6 참조). 도 6에서, 세로축은 소자의 전류(A)를 나타내고, 가로축은 소자에 조사되는 광의 휘도(cd/m2)를 나타낸다.

여기에서, 아래의 2개의 종류의 광전 변환 소자 : 이러한 실시형태에 설명된 방법에 의해 형성된 광전 변환 소자(특히, 베이스 기판으로서 유리 기판이 사용된 광전 변환 소자:c-Si on glass), 및 유리 기판 위의 다결정 실리콘(p-Si on glass)을 사용하여 형성된 광전 변환 소자가 조사 대상이다. 광전 변환 소자의 반도체층의 두께가 서로 약간 상이하고, 이것은 60 nm(c-Si on glass) 및 50 nm(p-Si on glass)이고, 다른 조건은 동일하다. 또한, 측정은 0.5 V의 역바이어스 전압이 인가되면서 실시된다.

도 6으로부터, 이러한 실시형태에 따라 형성된 광전 변환 소자로 획득된 전류가 유리 기판 위의 다결정 실리콘을 사용하여 형성된 광전 변환 소자로 획득된 것보다 대략 5배 크다는 것이 발견된다.

이러한 방식으로, 광 투과성 베이스 기판 위에 형성된 단결정 반도체층을 사용하여 광전 변환 소자가 형성될 때, 다결정 실리콘을 사용하여 광전 변환 소자가 형성되는 경우와 비교하여, 소자 특성이 향상될 수 있다. 또한, 광 투과성 베이스 기판 위에 형성된 단결정 반도체층이 사용될 때, 기판측으로부터 광이 입사할 수 있어서, 우수한 특성의 광전 변환 소자가 형성될 수 있다.

이러한 실시형태에서 설명된 구조는 다른 실시형태에 설명된 임의의 다른 구조와 적절히 조합됨으로써 구현될 수 있다는 것에 유의한다.

(실시형태 2)

이러한 실시형태에서, 반도체 장치 및 그 제작 방법의 일례가 도면을 참조하여 설명된다. 구체적으로는, 광전 변환 소자의 하방에 광전 변환 소자와 오버랩하는 차광층을 구비하는 반도체 장치 및 그 제작 방법이 설명될 것이다.

개시된 발명의 실시형태에 관련된 광전 변환 소자(180)는, 광 투과성 기판(100) 위에 제공된 차광층(204) 위에 형성된다(도 7 참조). 여기서, 도 7b는 도 7a의 라인 A-B를 따른 단면에 대응한다.

광전 변환 소자(180)는, 횡접합 핀(pin) 다이오드이며, 광전 변환의 효과를 갖는 반도체 영역(164), 제 1 도전형을 갖는 반도체 영역(158), 및 제 2 도전형을 갖는 반도체 영역(162)을 포함하는 섬형상 단결정 반도체층; 제 1 도전형을 갖는 반도체 영역(158)에 전기적으로 접속된 제 1 전극(172); 및 제 2 도전형을 갖는 반도체 영역(162)에 전기적으로 접속된 제 2 전극(174)을 포함한다. 제 1 전극(172) 및 제 2 전극(174)은, 콘택트홀을 통해 제 1 도전형을 갖는 반도체 영역(158) 및 제 2 도전형을 갖는 반도체 영역(162) 각각에 전기적으로 접속된다. 콘택트홀은 섬형상 산화 반도체층을 커버하도록 형성되는 절연층(154) 및 절연층(166)에 형성된다. 이전의 실시형태는 광전 변환 소자, 절연층, 기판의 특정한 구조 및 그 제작 공정을 참조할 수 있다. 이러한 실시형태에서는, 광 투과성 기판(100) 위에 절연층(206)을 개재하여 광을 차단할 수 있는 차광층(204)이 제공되고, 광전 변환 소자(180)가 차광층(204) 위에 제공되고, 이 광전 변환 소자는 절연층(112)을 개재하여 차광층(204)과 오버랩한다.

광전 변환 소자(180)와 오버랩하도록 차광층(204)을 제공함으로써, 광 투과성 기판(100)에 대해 제공된 광원으로부터의 광이, 광 센서로서 기능하는 광전 변환 소자(180)와 직접적으로 부딪히는 것이 방지될 수도 있다. 광전 변환 소자(180)에 포함된 섬형상 단결정 반도체층보다 큰 폭을 갖는 차광층(204)이 형성될 때, 광전 변환 소자(180)에 광이 직접적으로 부딪히는 것이 더욱 확실하게 방지될 수 있다.

도 8은 광전 변환 소자(180)와 광의 입사 방향 사이의 관계를 예시한다. 절연층(166) 및 절연층(500) 위에 컬러 필터(502)가 제공된다. 광원(504)이 광 투과성 기판(100) 측에 제공되고, 피검출물(506)이 대향하는 기판(도시 생략) 측에 배열될 때, 대향하는 기판측 상의 피검출물(506)은 광원(504)으로부터의 광(508)으로 조사된다. 그 후, 광전 변환 소자(광 센서)는 피검출물(506)으로부터의 반사광(510)을 수광한다. 이러한 경우에서, 광원(504), 컬러 필터(502), 및 차광층(204)이 대향 기판측에 제공되고, 피검출물이 광 투과성 기판(100)측 상에 제공되는 경우와 비교하여, 컬러 필터와 광전 변환 소자 사이에서 광이 전달되는 거리가 감소될 수도 있다. 따라서, 컬러 혼합이 억제될 수 있다.

차광층(204)이 광 투과성 기판(100)측 상에 제공되는 구조가, 이미지들을 캡처하는 접촉 영역 센서들이 터치 패널의 전체 표시 스크린에 배열되는 표시 장치에서의 이미지 캡처의 해상도를 향상시키기 위해, 작은 피치를 갖는 더욱 소형화된 화소들이 필요할 때, 더욱 효율적이다.

또한, 제 1 전극(172) 및 제 2 전극(174)은, 절연층(154) 및 절연층(166)에 형성된 콘택트홀을 통해 제 1 도전형을 갖는 반도체 영역(158) 및 제 2 도전형을 갖는 반도체 영역(162)에 각각 전기적으로 접속된다, 즉, 제 1 전극(172) 및 제 2 전극(174)은 광전 변환의 효과를 갖는 반도체 영역(164)을 사이에 두고 차광층(204)에 대향하는 측면 상에 차광벽이 되도록 제공된다. 따라서, 상이한 컬러로 인접하는 컬러 필터를 투과한 경사 방향으로부터의 광이 방지될 수 있어서, 컬러 분리가 양호하게 실시될 수 있고 컬러 혼합이 더 억제될 수 있다.

또한, 전압이 차광층(204)에 인가되는 구조가 이용될 수도 있다. 차광층(204)에 인가되는 전압을 제어함으로써, 광전 변환 소자(180)의 전극으로서 차광층(204)이 사용될 수 있다. 따라서, 전자 및 정공의 발생 또는 흐름이 제어될 수 있다.

다음으로, 기판 위에 광전 변환 소자 및 트랜지스터를 제작하는 공정들이 도 9a 내지 도 9g 및 도 10a 내지 도 10h를 참조하여 설명될 것이다.

먼저, 광 투과성 베이스 기판(100)과 본드 기판으로서 기능하는 단결정 반도체 기판(110)이 준비된다(도 9a 및 도 9b 참조). 상기 실시형태를 참조할 수 있는 베이스 기판(100) 및 단결정 반도체 기판(110)의 상세는 여기에서 생략된다.

다음으로, 베이스 기판(100) 표면상에, 절연층(202), 차광층(204), 및 절연층(206)이 이러한 순서로 적층된다(도 9c 참조).

절연층(202)은 예를 들어, 산화 실리콘막, 질화 실리콘막, 질화 산화 실리콘막, 산화 질화 실리콘막, 질화 알루미늄막, 산화 알루미늄막 등을 사용하여 단층으로, 또는 적층으로 형성될 수 있다. 절연층(202)으로서 질소를 함유하는 절연층이 형성될 때, 베이스 기판에 포함되는 나트륨(Na)과 같은 불순물 원소의 반도체에 대한 확산이 억제될 수 있다. 열산화법, CVD법, 스퍼터링법 등이 절연층(202)을 제작하기 위해 사용될 수 있다.

차광층(204)은 텅스텐, 몰리브덴, 탄탈, 티타늄, 니오븀, 니켈, 코발트, 지르코늄, 또는 아연과 같은 내열성을 갖는 금속막으로 형성되는 것이 바람직하다. 특히, 몰리브덴 또는 텅스텐을 사용하는 것이 바람직하다. 다르게는, 카본 블랙, 저차 산화 티타늄과 같은 흑색 안료를 포함하는 유기 수지가 사용될 수 있다. 다르게는, 크롬을 사용하는 막이, 차광층(204)으로서 사용될 수 있다. 또한, 내열성 이외에 내산화성을 갖는 재료가 차광층(204)으로서 사용되는 것이 바람직하다. 차광층(204)은, 스퍼터링법, 증착법 등을 사용하여 형성될 수 있다.

차광층(204) 위에 형성된 절연층(206)은, 예를 들어, 산화 실리콘막, 질화 실리콘막, 질화 산화 실리콘막, 산화 질화 실리콘막, 질화 알루미늄막, 산화 알루미늄막 등을 사용하여 단층으로, 또는 적층으로 형성될 수 있다. 특히, 산화 알루미늄이 절연층(206)으로 사용되는 것이 바람직하다. 이것은, 산화 알루미늄이 차광층(204)과의 양호한 밀착성을 갖기 때문이다. 또한, 산화 알루미늄은 양호한 평탄성을 갖고, 차광층(204)의 표면의 요철을 완화시킬 수 있다. 따라서, 산화 알루미늄의 사용은 베이스 기판(100)과 단결정 반도체 기판(110) 사이의 양호한 접합을 가능하게 한다. 절연층(206)을 제작하기 위해 열산화법, CVD법, 스퍼터링법 등이 이용될 수 있다.

취화 영역(114)이 단결정 반도체 기판(110)의 표면으로부터 소정의 깊이에 형성되고, 베이스 기판(100) 및 단결정 반도체 기판(110)은 절연층(202), 차광층(204), 절연층(206), 및 절연층(112)을 개재하여 접합된다(도 9d 및 도 9e 참조).

절연층(112)은 예를 들어, 산화 실리콘막, 산화 질화 실리콘막 등의 단층으로 또는 적층으로 형성될 수 있다. 그 상세한 설명에 대해서는 상기 언급한 실시형태를 참조할 수 있다. 여기서는, 단결정 반도체 기판(110) 위에 절연층(112)이 형성되지만, 절연층(112)은 단결정 반도체 기판을 커버하도록 열산화법에 의해 형성될 수도 있다.

취화 영역(114)은, 운동 에너지를 갖는 수소 등의 이온을 단결정 반도체 기판(110)에 첨가함으로써 형성될 수 있다. 그 상세한 설명에 대하여는 상기 언급한 실시형태를 참조할 수 있다.

접합은, 베이스 기판(100) 및 단결정 반도체 기판(110)이, 절연층(202), 차광층(204), 절연층(206), 및 절연층(112)을 개재하여 서로 밀착하게 배치된 후, 베이스 기판(100) 또는 단결정 반도체 기판(110)의 일부에 1 N/cm2 이상 500 N/cm2 이하의 압력이 인가되는 것으로 실시된다. 그 후, 절연층(206) 및 절연층(112)은 압력인가부로부터 함께 접합되기 시작되고, 접합이 자발적으로 전체 영역으로 확산된다. 이러한 접합은, 반 데르 발스력 또는 수소 결합의 작용하에서 실시되고, 실온에서 실시될 수 있다.

단결정 반도체 기판(110) 및 베이스 기판(100)이 함께 접합되기 이전에, 함께 접합될 표면이 표면 처리되는 것이 바람직하다는 것에 유의한다. 표면 처리는, 단결정 반도체 기판(110)과 베이스 기판(100) 사이의 접합 계면에서의 접합 강도를 향상시킬 수 있다. 표면 처리의 상세에 대해서는 상기 실시형태가 참조될 수 있다.

접합이 실시된 이후에, 접합 강도를 향상시키기 위한 열처리가 실시될 수도 있다는 것에 유의한다. 이러한 열처리는, 취화 영역(114)에서의 분리가 생기지 않는 온도(예를 들어, 실온 이상 및 400℃ 미만)에서 실시된다. 다르게는, 이러한 온도 범위의 온도에서 가열되면서, 베이스 기판(100) 위의 절연층(206) 및 절연층(112)이 함께 접합될 수도 있다. 열처리는, 확산노, 저항 가열노등의 가열노, RTA(rapid thermal annealing) 장치, 마이크로파 가열 장치 등을 사용하여 실시될 수 있다.