JP4919530B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP4919530B2 JP4919530B2 JP2000242575A JP2000242575A JP4919530B2 JP 4919530 B2 JP4919530 B2 JP 4919530B2 JP 2000242575 A JP2000242575 A JP 2000242575A JP 2000242575 A JP2000242575 A JP 2000242575A JP 4919530 B2 JP4919530 B2 JP 4919530B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- island

- semiconductor layer

- film

- laser light

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

【発明の属する技術分野】

本発明はレーザー光を用いた半導体膜のアニール(以下、レーザーアニールという)の方法及びそれを行うためのレーザー装置(レーザーと該レーザーから出力されるレーザー光を被処理体まで導くための光学系を含む装置)に関する。さらに、そのようなレーザーアニール方法によって形成される半導体装置及びその作製方法に関する。

【0002】

【従来の技術】

近年、薄膜トランジスタ(以下、TFTという)の開発が進められ、結晶質半導体膜として多結晶シリコン膜(ポリシリコン膜)を用いたTFTが注目されている。特に、液晶表示装置(液晶ディスプレイ)やEL(エレクトロルミネッセンス)表示装置(ELディスプレイ)においては、画素をスイッチングする素子やその画素を制御するための駆動回路を形成する素子として用いられる。

【0003】

ポリシリコン膜を得る手段としては、非晶質シリコン膜(アモルファスシリコン膜)を結晶化させてポリシリコン膜とする技術が一般的である。特に、最近ではレーザー光を用いてアモルファスシリコン膜を結晶化する方法が注目されている。本明細書中では、非晶質半導体膜をレーザー光で結晶化し、結晶質半導体膜を得る手段をレーザー結晶化という。

【0004】

レーザー結晶化は、半導体膜の瞬間的な加熱が可能であり、ガラス基板やプラスチック基板等の耐熱性の低い基板上に形成された半導体膜のアニール手段として有効な技術である。また、従来の電熱炉を用いた加熱手段(以下、ファーネスアニールという)に比べて格段にスループットが高い。

【0005】

レーザー光にも様々な種類があるが、一般的にはパルス発振型のエキシマレーザーを発振源とするレーザー光(以下、エキシマレーザー光という)を用いたレーザー結晶化が用いられている。エキシマレーザーは出力が大きく、高周波数での繰り返し照射が可能であるという利点を有し、さらにエキシマレーザー光はシリコン膜に対しての吸収係数が高いという利点を有する。

【0006】

現在、最も注目されている問題はレーザー光で結晶化された結晶質半導体膜の結晶粒径を如何に大きくするかである。当然のことながら、一つの結晶粒(グレインともいう)が大きくなれば、TFTの特にチャネル形成領域を横切る結晶粒界の数が減る。そのため、電界効果移動度やしきい値電圧といったTFTの代表的な電気特性のばらつきを改善することが可能となる。

【0007】

また、各結晶粒の内部は、比較的きれいな結晶性を維持しており、上述のTFTの諸特性を向上させるためには、一つの結晶粒の内部に完全にチャネル形成領域が収まるようにしてTFTを形成することが望ましい。

【0008】

しかしながら、現在の技術では結晶粒径の十分に大きな結晶質半導体膜を得ることは困難であり、実験的に得られたという報告はあるものの、実用化レベルには達していないのが現状である。

【0009】

実験的には「"High-Mobility Poly-Si Thin-Film Transistors Fabricated by a Novel Excimer Laser Crystallization Method", K.Shimizu, O.Sugiura and M.Matumura, IEEE Transactions on Electron Devices vol.40, No.1, pp112-117,1993」に示されるような結果が得られている。同文献は、基板上にSi/SiO2/n+Siの3層構造を形成し、エキシマレーザー光をSi側とn+Si側の両方向から照射している。そして、このような構成により結晶粒径を大きくできる旨が示されている。

【0010】

【発明が解決しようとする課題】

本発明は、上記問題点を解決するための技術であり、結晶粒径の大きい結晶質半導体膜を得るためのレーザーアニール方法及びそのレーザーアニール方法に用いるレーザー装置を提供することを課題とする。また、そのようなレーザーアニール方法を用いた半導体装置及びその作製方法を提供することを課題とする。

【0011】

【課題を解決するための手段】

本発明の要旨は、非晶質半導体膜を結晶化するにあたって、レーザー光を非晶質半導体膜の表面(上に薄膜が重ねられていく面)及び裏面(表面とは反対側の面)に同時に照射し、且つ、その表面に照射されたレーザー光(以下、第一次レーザー光という)の実効エネルギー強度と裏面に照射されるレーザー光(以下、第二次レーザー光という)の実効エネルギー強度とを異なるものとする点にある。

【0012】

即ち、第一次レーザー光の実効エネルギー強度を(I0)とし、第二次レーザー光の実効エネルギー強度を(I0')とした時、実効エネルギー強度比(I0'/I0)に「0<I0'/I0<1」または「1<I0'/I0」の関係が成り立つようにレーザー光を照射することを特徴とする。勿論、I0・I0'≠0である。

【0013】

なお、本明細書中において、「実効エネルギー強度」とはレーザー光が非晶質半導体膜の表面または裏面に達した時に有するエネルギー強度であり、反射等によるエネルギー損失を考慮したエネルギー強度(ここでは、単位は密度:mJ/cm2で表す)と定義する。測定することはできないが、レーザー光の経路に存在する媒質が判れば反射率や透過率の計算から求めることができる。

【0014】

例えば、図6に示す構造に本発明を実施した場合について、実効エネルギー強度の具体的な算出方法を説明する。図6において、601はアルミニウムでなる反射体、602はコーニング社#1737基板(厚さ0.7mm)、603は200nm厚の窒化酸化シリコン膜(以下、SiON膜という)、604は55nm厚のアモルファスシリコン膜である。このような試料に対して空気中で、波長308nmのXeClエキシマレーザー光を照射する場合を例にとる。

【0015】

アモルファスシリコン膜604に到達する直前のレーザー光(波長308nm)のエネルギー強度を(Ia)とする。このとき、第一次レーザー光の実効エネルギー強度(I0)は、アモルファスシリコン膜の表面におけるレーザー光の反射を考慮して、I0=Ia(1−RSi)で表される。但し、RSiはレーザー光の反射率である。この場合、計算ではI0=0.45Iaとなる。

【0016】

また、第二次レーザー光の実効エネルギー強度(I0')は、I0'=IaT1737RAlT1737(1−RSiON-Si)で表される。但し、T1737は#1737基板の透過率、RAlはアルミニウム表面での反射率、RSiON-SiはSiON膜中からアモルファスシリコン膜へ入射する際の反射率である。なお、空気中からSiON膜へ入射する際の反射率、SiON膜中の透過率、SiON膜中から#1737基板へ入射する際の反射率及び#1737基板中からSiON膜へ入射する際の反射率は、実験的に無視しうることが判明したので計算に含めなかった。この場合、計算ではI0'=0.13Iaとなる。

【0017】

従って、図6の構造の場合、第一次レーザー光の実効エネルギー強度(I0)は0.45Ia、第二次レーザー光の実効エネルギー強度(I0')は0.13Iaと求められる。即ち、実効エネルギー強度比(I0'/I0)は0.29である。以上のようにして求められる実効エネルギー強度比が、0<I0'/I0<1を満たすという点が本発明の特徴の一つである。

【0018】

また、第一次レーザー光の強度が第二次レーザー光の強度よりも小さい場合においても本発明は成り立つ。即ち、実効エネルギー強度比が1<I0'/I0を満たす場合においても本発明が成り立つ。

【0019】

第一次レーザー光と第二次レーザー光の実効エネルギー強度を異なるものとするためには、以下の方法が挙げられる。

1)基板の下に設けた反射体を用いて非晶質半導体膜の表面及び裏面にレーザー光を照射する際に、反射体の反射率を調節することで第二次レーザー光の実効エネルギー強度を減衰させ、相対的に第一次レーザー光の実効エネルギー強度よりも小さくする方法。

2)第一次レーザー光を途中で分割して第二次レーザー光を形成し、第一次レーザー光の実効エネルギー強度もしくは第二次レーザー光の実効エネルギー強度をフィルター(バリアブルアッテネータ等)で減衰させ、相対的に両者の実効エネルギー強度を異なるものとする方法。

3)非晶質半導体膜を形成する基板の材質によって、第二次レーザー光の実効エネルギー強度を減衰させ、相対的に第一次レーザー光の実効エネルギー強度よりも小さくする方法。

4)基板と非晶質半導体膜の間に絶縁膜を挟み、第二次レーザー光の実効エネルギー強度をその絶縁膜で減衰させ、相対的に第一次レーザー光の実効エネルギー強度よりも小さくする方法。

5)非晶質半導体膜の表面を絶縁膜で覆っておき、非晶質半導体膜の表面における第一次レーザー光の反射率を小さくすることで、第一次レーザー光の実効エネルギー強度を相対的に第二次レーザー光の実効エネルギー強度よりも大きくなるようにする方法。

6)非晶質半導体膜を絶縁膜で覆っておき、第一次レーザー光の実効エネルギーをその絶縁膜で減衰させ、相対的に第二次レーザー光の実効エネルギーよりも小さくなるようにする方法。

7)第一次レーザー光と第二次レーザー光をそれぞれ別のレーザーを発振源として形成し、両者の実効エネルギー強度を異なるものとする方法。

【0020】

また、本発明はレーザーの種類によるものではなく、一般的に知られるエキシマレーザー(代表的にはKrFレーザーもしくはXeClレーザー)、固体レーザー(代表的にはNd:YAGレーザーもしくはルビーレーザー)、ガスレーザー(代表的にはアルゴンレーザーもしくはヘリウム・ネオンレーザー)、金属蒸気レーザー(代表的には銅蒸気レーザーもしくはヘリウム・カドミウムレーザー)または半導体レーザーを用いることができる。

【0021】

なお、Nd:YAGレーザーのように基本波(第1高調波:波長1064nm)の波長が長いレーザー光を用いる場合は、第2高調波、第3高調波もしくは第4高調波を用いるのが好ましい。これらの高調波は非線形結晶(非線形素子)を用いて得ることができる。また、公知のQスイッチ方式を用いても良い。

【0022】

〔発明に至るまでの経緯〕

ここで、本出願人が本発明に想到した経緯について、実験結果に基づいて説明する。図7に示すSEM(Scanning Electron Microscopy)写真はレーザー結晶化により形成したポリシリコン膜にセコ・エッチングを施した後の写真である。セコ・エッチング技術に関する詳細は、「F.Secco d' Aragona:"Dislocation Etch for (100) Planes in Silicon".J.Electrochem.soc.Vol.119.No.7.pp.948-950(1972)」を参考にすれば良い。

【0023】

どちらもコーニング社製#1737基板(厚さ0.7mm)の上に酸化シリコン膜(厚さ200nm)を介してアモルファスシリコン膜(厚さ55nm)を形成し、エキシマレーザー光を照射して得ている。なお、この実験で用いたエキシマレーザー光は、励起ガスとしてXeClガスを用いた波長308nmのパルスレーザー光であり、パルス幅は30ns、ショット数は20ショット、エネルギー密度は370mJ/cm2とした。

【0024】

図7(A)はアモルファスシリコン膜の表面のみにレーザー光を照射して得たポリシリコン膜(平均結晶粒径は約0.3μm)であり、図7(B)はアモルファスシリコン膜の表面及び裏面にレーザー光を照射して得たポリシリコン膜(平均結晶粒径は約1.5μm)である。これによればアモルファスシリコン膜の表面及び裏面にレーザー光を照射して得たポリシリコン膜の方が結晶粒径は約5倍も大きく、両面からの照射が非常に効果的であることが確認された。

【0025】

なお、本明細書中において、平均結晶粒径の定義は特開平11−219133号出願の明細書中における「結晶粒領域の平均径の定義」に準ずるものとする。

【0026】

以上のように、非晶質半導体膜の表面及び裏面にレーザー光を照射することで結晶粒径を大きくできることが確認された。なお、従来例で示した文献中の実験は、結晶化させようとする半導体膜の裏面に直接レーザー光は照射されず、n+Siの余熱を利用して蓄熱効果を狙っており、本出願人が行った実験とは全く構成が異なっている。

【0027】

次に、本出願人は、ガラス基板の代わりに石英基板を用いて同様の実験(但し、レーザー光のエネルギー密度は200mJ/cm2とした。)を行った。その結果、図8に示すような結果(セコ・エッチング後のSEM写真)が得られた。

【0028】

図8(A)はアモルファスシリコン膜の表面のみにレーザー光を照射して得られたポリシリコン膜であり、図8(B)はアモルファスシリコン膜の表面及び裏面にレーザー光を照射して得られたポリシリコン膜である。これによれば基板として石英基板を用いた場合、平均結晶粒径はせいぜい0.4〜0.5μm程度であり、図7(B)に示したような大粒径化は確認できなかった。また、基板の片面から照射しても両面から照射しても結晶粒径に差は見られなかった。即ち、前述と同様に、非晶質半導体膜の表面及び裏面にレーザー光を照射したにも拘わらず、平均結晶粒径の増大という効果は確認されなかった。

【0029】

そこで本出願人は、以上の実験結果について考察し、図7及び図8に示した実験の差は、ガラス基板の透過率(約50%)と石英基板の透過率(約93%)の差、即ち、非晶質半導体膜の裏面に照射されるレーザー光の実効エネルギー強度の差であると予想した。そして、確認のため以下のような実験を行った。

【0030】

まず、本実験では図6に示した構造の試料を、基板602に石英基板を用い、反射体601に窒化タンタル膜を用いて作製した。そして、この試料に対して図7(B)の写真を得たのと同一条件でXeClエキシマレーザー光を照射し、得られたポリシリコン膜の平均結晶粒径をセコ・エッチング後のSEM写真にて確認した。この結果を図9に示す。

【0031】

図9を見れば判るように、得られたポリシリコン膜の結晶粒は、図7(B)のポリシリコン膜とほぼ同じ様な状態で分布していることが確認された。また、図7(B)の写真を得た試料の場合、第一次レーザー光と第二次レーザー光の実効エネルギー強度比が0.29であることは既に述べた。これは実質的にガラス基板で第二次レーザー光が減衰した結果である。これと同じように本実験の試料について実効エネルギー強度比を計算した結果、0.33という値が得られた。これは実質的に反射体で第二次レーザー光が減衰した結果である。

【0032】

また、図8(B)の試料(石英とアルミニウムでなる反射体の組み合わせ)と図9の試料(石英と窒化タンタルでなる反射体の組み合わせ)は反射体表面の材質が異なる以外同一構造であり、異なる点は図9の試料では反射体表面の反射率が図8(B)の試料よりも小さい点のみである。

【0033】

以上の結果を考察すると、非晶質半導体膜の表面及び裏面にレーザー光を照射して結晶化する場合、表面側のレーザー光(第一次レーザー光)の実効エネルギー強度よりも、裏面側のレーザー光(第二次レーザー光)の実効エネルギー強度が小さい場合において平均結晶粒径の増加が確認されることが判った。

【0034】

【発明の実施の形態】

〔実施形態1〕

本発明の実施形態の一つについて説明する。図1(A)は本発明のレーザー装置の構成を示す図である。このレーザー装置は、レーザー101、レーザー101を発振源とするレーザー光を線状に変形する光学系201、透光性基板を固定するステージ102を有し、ステージ102にはヒータ103とヒータコントローラー104が具備されて、基板を室温〜550℃の範囲の温度に保持することができる。また、ステージ102上には反射体105が設けられ、その上に非晶質半導体膜が形成された基板106が設置される。

【0035】

次に、図1(A)のような構成のレーザー装置において、基板106の保持方法を図1(B)を用いて説明する。ステージ102に保持された基板106は、反応室107に設置され、レーザー101を発振源とする線状のレーザー光が照射される。反応室内は図示されていない排気系またはガス系により減圧状態または不活性ガス雰囲気とすることができ、半導体膜を汚染させることなく100〜450℃まで加熱することができる。

【0036】

また、ステージ102はガイドレール108に沿って反応室内を移動することができ、基板の全面に線状のレーザー光を照射することができる。レーザー光は基板106の上面に設けられた図示されていない石英製の窓から入射する。また、図1(B)ではこの反応室107にトランスファー室109、中間室110、ロード・アンロード室111が接続され、それぞれの室は仕切弁112、113で分離されている。

【0037】

ロード・アンロード室111には複数の基板を保持することが可能なカセット114が設置され、トランスファー室109に設けられた搬送ロボット115により基板が搬送される。基板106'は搬送中の基板を表す。このような構成とすることによりレーザーアニールを減圧下または不活性ガス雰囲気中で連続して処理することができる。

【0038】

次に、レーザー光を線状にする光学系201の構成について図2を用いて説明する。図2(A)は光学系201を側面から見た図であり、図2(B)は光学系201を上面から見た図である。

【0039】

レーザー101を発振源とするレーザー光はシリンドリカルレンズアレイ202により縦方向に分割される。この分割されたレーザー光はシリンドリカルレンズ203によりさらに横方向に分割される。即ち、レーザー光はシリンドリカルレンズアレイ202、203によって最終的にはマトリクス状に分割されることになる。

【0040】

そして、レーザー光はシリンドリカルレンズ204により一旦集光される。その際、シリンドリカルレンズ204の直後にシリンドリカルレンズ205を通る。その後、ミラー206で反射され、シリンドリカルレンズ207を通った後、照射面208に達する。

【0041】

このとき、照射面208に投影されたレーザー光は線状の照射面を示す。即ち、シリンドリカルレンズ207を透過したレーザー光の断面形状は線状になっていることを意味する。この線状に変形されたレーザー光の幅方向(短い方向)の均質化は、シリンドリカルレンズアレイ202、シリンドリカルレンズ204及びシリンドリカルレンズ207で行われる。また、上記レーザー光の長さ方向(長い方向)の均質化は、シリンドリカルレンズアレイ203及びシリンドリカルレンズ205で行われる。

【0042】

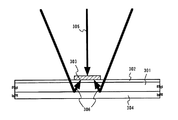

次に、基板上に形成された被処理膜の表面及び裏面からレーザー光を照射するための構成について図3を用いて説明する。図3に示したのは、図1における基板106と反射体105との位置関係を示す図である。

【0043】

図3において、301は透光性基板であり、その表面(薄膜または素子が形成される側の面)には絶縁膜302、非晶質半導体膜(または微結晶半導体膜)303が形成されている。また、透光性基板301の下にはレーザー光を反射させるための反射体304が配置される。

【0044】

透光性基板301はガラス基板、石英基板、結晶化ガラス基板若しくはプラスチック基板が用いられる。この透光性基板301自体で第二次レーザー光の実効エネルギー強度を調節することが可能である。また、絶縁膜302は酸化シリコン膜や窒化酸化シリコン膜(SiOxNy)などの珪素を含む絶縁膜を用いれば良く、この絶縁膜302で第二次レーザー光の実効エネルギー強度を調節しても良い。また、非晶質半導体膜303はアモルファスシリコン膜の他に、アモルファスシリコンゲルマニウム膜などの化合物半導体膜も含む。

【0045】

また、反射体304は表面(レーザー光の反射面)に金属膜を形成した基板であっても良いし、金属元素でなる基板であっても良い。この場合、金属膜としては如何なる材料を用いても良い。代表的には、シリコン(Si)、アルミニウム(Al)、銀(Ag)、タングステン(W)、チタン(Ti)、タンタル(Ta)のいずれかの元素を含む金属膜を用いる。例えば、窒化タングステン(WN)、窒化チタン(TiN)、窒化タンタル(TaN)を用いても良い。

【0046】

さらに、この反射体304は透光性基板301に接して設けても良いし、離して設けても良い。また、反射体304を配置する代わりに、基板301の裏面(表面の反対側の面)に直接上述のような金属膜を形成し、そこでレーザー光を反射させることも可能である。いずれにしても、この反射体304の反射率で第二次レーザー光の実効エネルギー強度を調節することができる。また、反射体304を透光性基板301と離して設置する場合、その隙間に充填する気体(ガス)で第二次レーザー光のエネルギー強度を制御することも可能である。

【0047】

そして、図2で説明した光学系201を経由して線状に変形されたレーザー光が、非晶質半導体膜303に照射される。この線状に変形されたレーザー光の照射はレーザー光を走査することによって行われる。

【0048】

いずれにしても、シリンドリカルレンズ207を透過して非晶質半導体膜303の表面に照射される第一次レーザー光305と、反射体304で一旦反射されて非晶質半導体膜303の裏面に照射される第二次レーザー光306との実効エネルギー強度比(I0'/I0)が、0<I0'/I0<1または1<I0'/I0の関係を満たすことが重要である。このためには、反射体304のレーザー光に対する反射率は20〜80%であることが好ましい。また、このとき、本実施形態でいくつか述べた第二次レーザー光の実効エネルギー強度を減衰させる手段を、複数組み合わせて所望の強度比としても良い。

【0049】

また、シリンドリカルレンズ207を通過したレーザー光は、集光される過程で基板表面に対して45〜90°の入射角を持つ。そのため、第二次レーザー光306は非晶質半導体膜303の裏面側にも回り込んで照射される。また、反射体304の反射面に起伏部を設けてレーザー光を乱反射させることで、第二次レーザー光306をさらに効率良く得ることができる。

【0050】

〔実施形態2〕

本実施形態ではの実施形態1と異なる実施の形態について説明する。本実施形態では、実施形態1のような反射体を用いず、光学系の途中で分光した二系統のレーザー光を非晶質半導体膜の表面及び裏面から照射する例を示す。

【0051】

図4(A)は本実施形態のレーザー装置の構成を示す図である。基本的な構成は実施形態1で説明した図1のレーザー装置と同様であるので異なる部分の符号を変えて説明する。

【0052】

このレーザー装置は、レーザー101、レーザー101を発振源とするレーザー光を線状に変形し、且つ、二系統に分光する光学系401、透光性基板を固定する透光性のステージ402を有する。また、ステージ402上には基板403aが設置され、その上に非晶質半導体膜403bが形成されている。

【0053】

本実施形態の場合、ステージ402を透過したレーザー光を非晶質半導体膜403bに照射するため、ステージ402は透光性を有してなければならない。また、ステージ402側から照射されるレーザー光(第二次レーザー光)はステージ402を透過するので、その実効エネルギー強度はステージ402を透過する際の減衰を考慮しなければならない。

【0054】

また、図4(B)は図4(A)に示したレーザー装置における基板403aの保持方法を説明する図面であるが、透光性ステージ402を用いること以外は図1(B)に示した構成と同一であるので説明は省略する。

【0055】

次に、図4(A)に示した光学系401の構成について図5を用いて説明する。図5は光学系401を側面から見た図である。レーザー501を発振源とするレーザー光はシリンドリカルレンズアレイ502により縦方向に分割される。この分割されたレーザー光はシリンドリカルレンズ503によりさらに横方向に分割される。こうしてレーザー光はシリンドリカルレンズアレイ502、503によってマトリクス状に分割される。

【0056】

そして、レーザー光はシリンドリカルレンズ504により一旦集光される。その際、シリンドリカルレンズ504の直後にシリンドリカルレンズ505を通る。ここまでは図2に示した光学系と同様である。

【0057】

その後、レーザー光はハーフミラー506に入射し、ここでレーザー光は第一次レーザー光507と第二次レーザー光508とに分光される。そして、第一次レーザー光507はミラー509、510で反射され、シリンドリカルレンズ511を通った後、非晶質半導体膜403bの表面に達する。

【0058】

また、ハーフミラー506で分光された第二次レーザー光508はミラー512、513、514で反射され、シリンドリカルレンズ515を通った後、基板403aを透過して非晶質半導体膜403bの裏面に達する。

【0059】

このとき、実施形態1と同様に基板の照射面に投影されたレーザー光は線状の照射面を示す。また、この線状に変形されたレーザー光の幅方向(短い方向)の均質化は、シリンドリカルレンズアレイ502、シリンドリカルレンズ504及びシリンドリカルレンズ515で行われる。また、上記レーザー光の長さ方向(長い方向)の均質化は、シリンドリカルレンズアレイ503、シリンドリカルレンズ505及びシリンドリカルレンズ511で行われる。

【0060】

いずれにしても、シリンドリカルレンズ511を透過して非晶質半導体膜403bの表面に照射される第一次レーザー光と、シリンドリカルレンズ515を透過して非晶質半導体膜403bの裏面に照射される第二次レーザー光との実効エネルギー強度比(I0'/I0)が、0<I0'/I0<1または1<I0'/I0の関係を満たすことが重要である。

【0061】

本実施形態では基板403aとしてガラス基板(ここで用いるレーザー光の透過率が約50%の材料でなるもの)を用いることで、上述の関係式を満たすようにしている。勿論、基板以外にも基板403a上に設けた絶縁膜(図示せず)や、基板403aを設置するステージ(図示せず)の透過率や界面の反射率を調節して第二次レーザー光の実効エネルギー強度を減衰させても良い。

【0062】

また、光学系401の第二次レーザー光の光路において、任意の場所に減光フィルターを設けて、第二次レーザー光の実効エネルギー強度を減衰させることも可能であるし、逆に光学系401の第一次レーザー光の光路において、任意の場所に減光フィルターを設けて、第一次レーザー光の実効エネルギー強度を減衰させることも可能である。

【0063】

また、本実施形態でいくつか述べた第一次レーザー光もしくは第二次レーザー光の実効エネルギー強度を減衰させる手段を、複数組み合わせて所望の強度比としても良い。

【実施例】

〔実施例1〕

本実施例では、実施形態1に示した構成でアモルファスシリコン膜の結晶化を行った例を示す。説明には図3を用いる。

【0064】

本実施例では、基板301として1.1mm厚の石英基板、絶縁膜302として200nm厚の窒化酸化シリコン膜(SiON膜)、非晶質半導体膜303としてアモルファスシリコン膜を用いた。このとき、SiON膜302とアモルファスシリコン膜303はプラズマCVD法を用いて形成した。

【0065】

本実施例では、まずSiH4を4SCCM、N2Oを400SCCMとして反応室に導入し、成膜温度400℃、反応圧力30Pa、放電電力密度0.41W/cm2、放電周波数60MHzとしてSiON膜302を形成した。次に、SiH4を100SCCMで反応室に導入し、成膜温度300℃、反応圧力45Pa、放電電力密度0.037W/cm2、放電周波数13.56MHzとしてアモルファスシリコン膜303を形成した。なお、実際にはアモルファスシリコン膜をパターニングして島状パターンとした。

【0066】

次に、図1(B)に示したようなエキシマレーザー装置を用いてアモルファスシリコン膜303のレーザー結晶化を行った。このとき、図3の反射体304としては、シリコン基板上に窒化タングステン膜を形成したものを用いた。また、反射体304と石英基板301との間には150μmの隙間を空けた。

【0067】

この状態で図3に示すようにエキシマレーザー光(第一次レーザー光305と第二次レーザー光306)をアモルファスシリコン膜303に対して室温、大気雰囲気中で照射した。エキシマレーザー光は図2に示した光学系により断面形状を線状(0.4mm×160mm)に変形し、基板の一端から他端まで走査した。また、走査速度は1mm/sとし、エネルギー密度(図6のIaに想到するエネルギー強度)は336mJ/cm2、パルス幅は30ns、繰り返し周波数は30Hz、重ね合わせ率は90%とした。これにより一カ所に20ショットのレーザー光を照射することができた。

【0068】

なお、本実施例の構成でレーザー結晶化を行う場合、第一次レーザー光の実効エネルギー強度(I0)は151.2mJ/cm2であり、第二次レーザー光の実効エネルギー強度(I0')は77.3mJ/cm2であった。従って、実効エネルギー強度比(I0'/I0)は0.51であった。

【0069】

ここで本実施例に従って結晶化させたポリシリコン膜のSEM写真を図10に示す。なお、図10はセコ・エッチング後の状態である。このセコ・エッチングはフッ化水素酸溶液50ccと水25ccと1.14gのクロム酸カリウム(二価)とを加えた室温のエッチャントを用いた。

【0070】

その結果、図10に示すように、島状パターンの中心付近に平均結晶粒径が0.5〜0.6μm程度の比較的大きな結晶粒が確認できた。島状パターンの端部には結晶粒径の小さな結晶粒が存在するが、レーザーエネルギー密度を変えることで形成される位置が変化する。実際に本実施例によって形成したポリシリコン膜をTFTの活性層として用いる場合には、このような結晶粒径の小さな部分がチャネル形成領域に当たらないように設計すれば良い。

【0071】

〔実施例2〕

本実施例では、実施形態1に示した構成でアモルファスシリコン膜の結晶化を行った例を示す。なお、本実施例で行ったレーザー結晶化は実施例1において反射体304の表面に形成する膜をタングステン膜に、レーザーエネルギー密度を369mJ/cm2に変更しただけであるので、他の条件の詳細な説明は実施例1を参考にすれば良い。

【0072】

本実施例に従って結晶化させたポリシリコン膜のSEM写真を図11に示す。なお、実施例1と同様に図11はセコ・エッチング後の状態である。セコ・エッチングの条件は実施例1を参考にすれば良い。

【0073】

なお、本実施例の構成でレーザー結晶化を行う場合、第一次レーザー光の実効エネルギー強度(I0)は166.1mJ/cm2であり、第二次レーザー光の実効エネルギー強度(I0')は88.6mJ/cm2であった。従って、実効エネルギー強度比(I0'/I0)は0.53であった。

【0074】

その結果、図11に示すように、島状パターン全体に平均結晶粒径が0.6〜0.7μm程度の比較的大きな結晶粒が確認できた。なお、図11では図10に見られたような島状パターンの端部の小さな結晶粒は顕著に見られなかった。しかしながら、レーザーエネルギー密度を変えることで顕著に見られる条件もあったため、レーザーエネルギー密度の最適化が必要である。また、結晶粒径の小さな部分があっても、実施例1と同様にTFTのチャネル形成領域に当たらないように設計すれば問題はない。

【0075】

〔実施例3〕

本実施例では、実施形態1に示した構成でアモルファスシリコン膜の結晶化を行った例を示す。なお、本実施例で行ったレーザー結晶化は実施例1において反射体304の表面に形成する膜を窒化チタン膜に、レーザーエネルギー密度を384mJ/cm2に変更しただけであるので、他の条件の詳細な説明は実施例1を参考にすれば良い。

【0076】

本実施例に従って結晶化させたポリシリコン膜のSEM写真を図12に示す。なお、実施例1と同様に図12はセコ・エッチング後の状態である。セコ・エッチングの条件は実施例1を参考にすれば良い。

【0077】

なお、本実施例の構成でレーザー結晶化を行う場合、第一次レーザー光の実効エネルギー強度(I0)は172.8mJ/cm2であり、第二次レーザー光の実効エネルギー強度(I0')は57.6mJ/cm2であった。従って、実効エネルギー強度比(I0'/I0)は0.33であった。

【0078】

その結果、図12に示すように、島状パターン全体に平均結晶粒径が0.8〜1.0μm程度の大きな結晶粒が確認できた。この結晶粒は紙面に向かって横方向に長い形状であり、島状パターンの横方向の端部から結晶化が進行した可能性を示唆するものと思われる。この傾向は図11においても若干確認される。

【0079】

また、やはりレーザーエネルギー密度を変えることで顕著に見られる条件もあったため、レーザーエネルギー密度の最適化が必要である。また、結晶粒径の小さな部分があっても、実施例1と同様にTFTのチャネル形成領域に当たらないように設計すれば問題はない。

【0080】

〔実施例4〕

本実施例では、実施形態1または実施形態2の方法により、TFTの活性層となるポリシリコン膜を形成する例について説明する。説明には図13を用いる。

【0081】

まず、ガラス基板上に厚さ200nmの窒化酸化シリコン膜(図示せず)を形成し、その上に50nm厚のアモルファスシリコン膜(図示せず)を形成する。次に、アモルファスシリコン膜をパターニングしてアモルファスシリコン膜でなる島状パターン1301a、1301bを形成する。(図13(A))

【0082】

次に、島状パターン1301a、1301bを、実施形態1または実施形態2の方法によってレーザー結晶化する。レーザー結晶化によって得られたポリシリコン膜でなる島状パターン1302a、1302bは端部に結晶粒の小さな領域1303a、1303bを有することがある。また、島状パターン1302a、1302bの端部は結晶欠陥や格子歪みを多く含む領域でもある。(図13(B))

【0083】

なお、1304a、1304bで示された点線は、アモルファスシリコン膜でなる島状パターン1301a、1301bの跡であり、レーザー結晶化によって島状パターンが1〜15%ほど縮小化することを意味する。この縮小化はシリコン膜の緻密化と気化によって起こると考えられるが詳細は明らかではない。

【0084】

また、この島状パターン1301a、1301bの跡1304a、1304bは、下に形成された窒化酸化シリコン膜(図示せず)の段差となって残る。

【0085】

次に、ポリシリコン膜でなる島状パターン1302a、1302bを再びパターニングして活性層1305a、1305bを形成する。なお、1306a、1306bで示された点線は結晶粒の小さな領域1303a、1303bの跡である。また、活性層1305a、1305bを形成することによって下に形成された窒化酸化シリコン膜(図示せず)には再び段差が形成される。

(図13(C))

【0086】

即ち、前工程で形成された島状パターン1301a、1301bの形状に沿って形成された第1の段差と、活性層1305a、1305bの形状に沿って形成された第2の段差とが、ガラス基板上の窒化酸化シリコン膜に形成されることになる。このように、まず第1の形状の半導体パターンを形成した後にレーザー結晶化し、第1の形状の半導体パターンをさらにパターニングして第2の形状の半導体パターンを形成する技術は特開平8−228006号公報に開示されている。この技術を使うと上述のような二つの段差が残る。

【0087】

次に、活性層1305a、1305bを覆って80nm厚の窒化酸化シリコン膜でなるゲート絶縁膜を形成し、その上にゲート電極1307を形成する。ゲート電極1307は窒化タングステン膜とタングステン膜との積層構造で形成し、膜厚は300nmとする。(図13(D))

【0088】

ゲート電極1307を形成したら、n型を付与する不純物元素の添加工程を行い、ソース領域1308a、ドレイン領域1309a、LDD領域1310を形成する。さらに、選択的にp型を付与する不純物元素の添加工程を行い、ソース領域1308b、ドレイン領域1309bを形成する。また同時に、チャネル形成領域1311a、1311b(活性層のうち不純物元素が添加されなかった領域)が形成される。

【0089】

次に、酸化シリコン膜でなる層間絶縁膜(図示せず)を1μmの厚さに形成した後、コンタクトホールを開けて、ソース配線1312a、1312b、ドレイン配線1313を形成する。これら配線はアルミニウム膜を主体とする低抵抗な導電膜で形成すれば良い。(図13(E))

【0090】

以上の工程によって、図13(E)に示すような構造のnチャネル型TFT1314及びpチャネル型TFT1315を相補的に組み合わせたCMOS回路1316が形成される。

【0091】

なお、本実施例は本発明をTFTの活性層を形成する際に実施した一実施例であり、この作製工程に限定する必要はない。本発明は、公知のあらゆるTFTの作製工程に用いることができる。但し、活性層の下に遮光膜等を設ける場合、即ち、非晶質半導体膜の表面及び裏面を同時にレーザーアニールすることが不可能な場合を除く。

【0092】

また、本実施例ではCMOS回路を形成する例を示しているが、アクティブマトリクス型画像表示装置の画素部に設けられる画素TFTも、公知の技術を用いれば容易に作製することが可能である。

【0093】

〔実施例5〕

本実施例では、実施形態1または実施形態2によって形成した結晶質半導体膜を、TFTの活性層として用いる場合の配置について説明する。

【0094】

実施例2の条件において、レーザー密度を384mJ/cm2に変更してレーザーアニールを行って得たポリシリコン膜は、図26に示すような状態で結晶粒が分布していることが確認できた。即ち、島状パターンの端部に平均結晶粒径の大きな第1の領域が形成され、中央部に第1の領域よりも平均結晶粒径の小さな第2の領域が形成される。なお、第2の領域の平均結晶粒径は第1の平均結晶粒径に比べて1/3以下である。このような場合、図14(A)に示すように中心部の第2の領域を使わないように活性層の配置を設計する必要がある。

【0095】

図14(A)において、1401は本実施例の条件で形成された島状パターンの模式図であり、1402は第2の領域である。また、1403a、1403bは第1の領域(活性層として用いる領域)であり、1404a、1404bで示される点線は活性層が形成される部分に対応する。

【0096】

また、図14(B)のように、図14(A)のように配置された活性層を有する二種類のTFT(nチャネル型TFTとpチャネル型TFT)を組み合わせてCMOS回路を形成することも可能である。

【0097】

図14(B)において、nチャネル型TFT1405は、ゲート電極1406、ソース領域1407a、ドレイン領域1408a、LDD領域1409、チャネル形成領域1410a、ソース配線1411a及びドレイン配線1412で構成される。また、pチャネル型TFT1413は、ゲート電極1406、ソース領域1407b、ドレイン領域1408b、チャネル形成領域1410b、ソース配線1411b及びドレイン配線1412で構成される。

【0098】

そして、nチャネル型TFT1405とpチャネル型TFT1413とでゲート電極1406及びドレイン配線1412を共通化して、CMOS回路を形成することができる。勿論、これ以外の電気回路または電気素子を形成することも可能である。

【0099】

なお、実施例4でも述べたように、本実施例を実施すると島状パターン1401に対応する段差及び活性層1404a、1404bに対応する段差が、ポリシリコン膜の下地となる絶縁膜(または基板)に形成される。これは本実施例を実施した場合の特徴と言える。

【0100】

図14(A)と図14(B)に共通な概念は、結晶粒径の大きな第1の領域に少なくともチャネル形成領域が形成されるように活性層を配置することである。チャネル形成領域に含まれる結晶粒界が1本、好ましくは0本となるように配置することが最も好ましい。そうすることでTFTの電界効果移動度やしきい値電圧といった代表的な電気特性を改善することが可能である。

【0101】

〔実施例6〕

本実施例では、実施例5の図26で説明したような結晶状態の島状パターンから活性層を切り出してTFTを作製する場合について説明する。具体的には画素部の画素TFTおよび保持容量と、画素部の周辺に設けられる駆動回路のnチャネル型TFTとpチャネル型TFTとを同時に作製する方法について説明する。説明には図15〜図17を用いる。

【0102】

図15(A)において、基板701にはコーニング社の#7059ガラスや#1737ガラスなどに代表されるバリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板の他に、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルフォン(PES)など光学的異方性を有しないプラスチック基板を用いることができる。また、石英基板や結晶化ガラス基板を用いても良い。

【0103】

そして、基板701のTFTを形成する表面に、基板701からの不純物拡散を防ぐために、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの下地膜702を形成する。本実施例ではプラズマCVD法でSiH4、NH3、N2Oから作製される酸化窒化シリコン膜702aを10〜200nm(好ましくは50〜100nm)、同様にSiH4、N2Oから作製される酸化窒化水素化シリコン膜702bを50〜200nm(好ましくは100〜150nm)の厚さに積層形成する。

【0104】

酸化窒化シリコン膜は従来の平行平板型のプラズマCVD法を用いて形成する。酸化窒化シリコン膜702aは、SiH4を10SCCM、NH3を100SCCM、N2Oを20SCCMとして反応室に導入し、基板温度325℃、反応圧力40Pa、放電電力密度0.41W/cm2、放電周波数60MHzとする。一方、酸化窒化水素化シリコン膜702bは、SiH4を5SCCM、N2Oを120SCCM、H2を125SCCMとして反応室に導入し、基板温度400℃、反応圧力20Pa、放電電力密度0.41W/cm2、放電周波数60MHzとする。これらの膜は、基板温度を変化させ、反応ガスの切り替えのみで連続して形成することもできる。

【0105】

また、酸化窒化シリコン膜702aは基板を中心に考えて、その内部応力が引張り応力となるように形成する。酸化窒化シリコン膜702bも同様な方向に内部応力を持たせるが、酸化窒化シリコン膜702aよりも絶対値で比較して小さい応力となるようにする。

【0106】

次に、25〜80nm(好ましくは30〜60nm)の厚さで非晶質半導体膜703を、プラズマCVD法やスパッタ法などの公知の方法で形成する。例えば、プラズマCVD法で非晶質シリコン膜を55nmの厚さに形成する。このとき、下地膜702と非晶質半導体膜703とは両者を連続形成することも可能である。例えば、前述のように酸化窒化シリコン膜702aと酸化窒化水素化シリコン膜702bをプラズマCVD法で連続して成膜後、反応ガスをSiH4、N2O、H2からSiH4とH2或いはSiH4のみに切り替えれば、一旦大気雰囲気に晒すことなく連続形成できる。その結果、酸化窒化水素化シリコン膜702bの表面の汚染を防ぐことが可能となり、作製するTFTの特性バラツキやしきい値電圧の変動を低減させることができる。

【0107】

そして、まず非晶質構造を有する半導体層703から、図15(B)で点線で示すように第1の形状を有する島状半導体層704〜706を形成する。図18(A)はこの状態における島状半導体層704の上面図であり、同様に図19(A)は島状半導体層706の上面図を示す。

【0108】

図18および図19において、島状半導体層は長方形とし一辺が50μm以下となるように形成するが、島状半導体層の形状は任意なものとすることが可能で、好ましくはその中心部から端部までの最小距離が50μm以下となるような形態であればどのような多角形、或いは円形とすることもできる。

【0109】

次に、このような島状半導体層704〜706に対して結晶化の工程を行う。結晶化の工程は、実施形態1または2で説明したどちらの方法を用いることも可能であるが、本実施例では実施形態1の方法で島状半導体層704〜706にレーザーアニールを行う。こうして図15(B)の実線で示す結晶質シリコン膜から成る島状半導体層707〜711が形成される。

【0110】

なお、本実施例では二つのTFTに対応して一つの島状半導体層を形成する例を示しているが、島状半導体層の専有面積が大きくなる場合(一つのTFTの大きさが大きくなる場合)には、複数の島状半導体層に分割し、複数のTFTを直列に接続したものを一つのTFTとして機能させることも可能である。

【0111】

このとき、非晶質シリコン膜の結晶化に伴って膜が緻密化し、1〜15%程度収縮する。そして、島状半導体層の端部には収縮により歪みが発生した領域712が形成される。さらに、島状半導体層の中央部には結晶粒の小さな領域(平均結晶粒径の小さな領域)713が形成される。図18(B)および図19(B)は、それぞれこの状態の島状半導体層の上面図を示す。同図中で点線で示す領域704、706は元々あった島状半導体層704、706の大きさを示す。

【0112】

このように歪みが蓄積した領域712や結晶粒が小さい領域713がチャネル形成領域に含まれてしまうと、多数の欠陥準位によりTFTの特性を劣化させる原因となる。例えば、オフ電流値が増大したり、この領域に電流が集中して局部的に発熱したりするため好ましくない。

【0113】

従って、図15(C)で示すように、上述のような領域が除去されるように第2の形状の島状半導体層715、716を形成する。但し、図19に示すように画素TFTの活性層となる島状半導体層719の場合、ソース領域、ドレイン領域及び保持容量の電極として働く領域に、上述の結晶粒が小さい領域713が含まれている。このような結晶粒が小さい領域はチャネル形成領域にさえ含まれていなければ問題とはならない。

【0114】

なお、図中点線で示す714'は歪みが蓄積した領域712や結晶粒が小さい領域713が存在していた領域であり、その領域より内側に第2の形状の島状半導体層715、716、719を形成する状態を示している。この第2の形状の島状半導体層715、716、719の形状は任意な形状のものとすれば良い。図18(C)にはこの状態における島状半導体層715、716の上面図を示す。また、同様に図19(C)には島状半導体層719の上面図を示す。

【0115】

その後、この島状半導体層715〜719を覆って、プラズマCVD法またはスパッタ法により50〜100nmの厚さの酸化シリコン膜によるマスク層720を形成する。この状態で島状半導体層に対し、TFTのしきい値電圧(Vth)を制御する目的でp型を付与する不純物元素を1×1016〜5×1017atoms/cm3程度の濃度で島状半導体層の全面に添加しても良い。

【0116】

半導体に対してp型を付与する不純物元素には、ホウ素(B)、アルミニウム(Al)、ガリウム(Ga)など周期律表第13族の元素が知られている。その方法として、イオン注入法やイオンドープ法を用いることができるが、大面積基板を処理するにはイオンドープ法が適している。イオンドープ法ではジボラン(B2H6)をソースガスとして用いホウ素(B)を添加する。このような不純物元素の注入は必ずしも必要でなく省略しても差し支えないが、特にnチャネル型TFTのしきい値電圧を所定の範囲内に収めるためには有効である。

【0117】

駆動回路のnチャネル型TFTのLDD領域を形成するために、n型を付与する不純物元素を島状半導体層716、718に選択的に添加する。そのため、あらかじめレジストマスク721a〜721eを形成する。n型を付与する不純物元素としては、リン(P)や砒素(As)を用いれば良く、ここではリン(P)を添加すべく、フォスフィン(PH3)を用いたイオンドープ法を用いる。

【0118】

形成された不純物領域は低濃度n型不純物領域722、723として、このリン(P)濃度は2×1016〜5×1019atoms/cm3の範囲とすれば良い。本明細書中では、ここで形成された不純物領域722、723に含まれるn型を付与する不純物元素の濃度を(n-)と表す。また、不純物領域724は、画素部の保持容量を形成するための半導体層であり、この領域にも同じ濃度でリン(P)が添加される(図15(D))。

【0119】

次に、添加した不純物元素を活性化させる工程を行う。活性化は、窒素雰囲気中で500〜600℃で1〜4時間の熱処理や、レーザー活性化の方法により行うことができる。また、両者を併用して行っても良い。レーザー活性化の方法による場合、KrFエキシマレーザー光(波長248nm)を用い、線状ビームを形成して、発振周波数5〜50Hz、エネルギー密度100〜500mJ/cm2として線状ビームのオーバーラップ割合を80〜98%として走査して、島状半導体層が形成された基板全面を処理する。尚、レーザー光の照射条件には何ら限定される事項はなく、実施者が適宣決定すれば良い。この工程は、マスク層720を残して行っても良いし、除去してから行っても良い。

【0120】

図15(E)において、ゲート絶縁膜725はプラズマCVD法またはスパッタ法を用い、膜厚を40〜150nmとしてシリコンを含む絶縁膜で形成する。例えば、120nmの厚さで酸化窒化シリコン膜から形成すると良い。また、SiH4とN2OにO2を添加させて作製された酸化窒化シリコン膜は、膜中の固定電荷密度が低減されているのでこの用途に対して好ましい材料となる。勿論、ゲート絶縁膜725はこのような酸化窒化シリコン膜に限定されるものでなく、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い。いずれにしても、ゲート絶縁膜725は基板を中心に考え圧縮応力となるように形成する。

【0121】

そして、図15(E)に示すように、ゲート絶縁膜725上にゲート電極を形成するための耐熱性導電層を形成する。耐熱性導電層は単層で形成しても良いが、必要に応じて二層あるいは三層といった複数の層から成る積層構造としても良い。このような耐熱性導電性材料を用い、例えば、導電性の窒化物金属膜から成る導電層(A)726と金属膜から成る導電層(B)727とを積層した構造とすると良い。

【0122】

導電層(B)727はタンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タングステン(W)から選ばれた元素、または前記元素を主成分とする合金か、前記元素を組み合わせた合金膜(代表的にはMo−W合金膜、Mo−Ta合金膜)で形成すれば良く、導電層(A)726は窒化タンタル(TaN)、窒化タングステン(WN)、窒化チタン(TiN)膜、窒化モリブデン(MoN)などで形成する。また、導電層(A)726はタングステンシリサイド、チタンシリサイド、モリブデンシリサイドを適用しても良い。

【0123】

また、導電層(B)727は低抵抗化を図るために含有する不純物濃度を低減させることが好ましく、特に酸素濃度に関しては30ppm以下とすることが好ましい。例えば、タングステン(W)は酸素濃度を30ppm以下とすることで20μΩcm以下の比抵抗値を実現することができる。

【0124】

導電層(A)726は10〜50nm(好ましくは20〜30nm)とし、導電層(B)727は200〜400nm(好ましくは250〜350nm)とすれば良い。Wをゲート電極とする場合には、Wをターゲットとしたスパッタ法で、アルゴン(Ar)ガスと窒素(N2)ガスを導入して導電層(A)726を窒化タングステン(WN)で50nmの厚さに形成し、導電層(B)727をWで250nmの厚さに形成する。その他の方法として、W膜は6フッ化タングステン(WF6)を用いて熱CVD法で形成することもできる。

【0125】

いずれにしてもゲート電極として使用するためには低抵抗化を図る必要があり、W膜の抵抗率は20μΩcm以下にすることが望ましい。W膜は結晶粒を大きくすることで低抵抗率化を図ることができるが、W中に酸素などの不純物元素が多い場合には結晶化が阻害され高抵抗化する。このことより、スパッタ法による場合、純度99.9999%のWターゲットを用い、さらに成膜時に気相中からの不純物の混入がないように十分配慮してW膜を形成することにより、抵抗率9〜20μΩcmを実現することができる。

【0126】

一方、導電層(A)726にTaN膜を、導電層(B)727にTa膜を用いる場合には、同様にスパッタ法で形成することが可能である。TaN膜はTaをターゲットとしてスパッタガスにArと窒素との混合ガスを用いて形成し、Ta膜はスパッタガスにArを用いる。また、これらのスパッタガス中に適量のXeやKrを加えておくと、形成する膜の内部応力を緩和して膜の剥離を防止することができる。α相のTa膜の抵抗率は20μΩcm程度でありゲート電極に使用することができるが、β相のTa膜の抵抗率は180μΩcm程度でありゲート電極とするには不向きである。TaN膜はα相に近い結晶構造を持つので、この上にTa膜を形成すればα相のTa膜が容易に得られる。

【0127】

なお、図示しないが、導電層(A)726の下に2〜20nm程度の厚さでリン(P)をドープしたシリコン膜を形成しておくことは有効である。これにより、その上に形成される導電膜の密着性向上と酸化防止を図ると同時に、導電層(A)726または導電層(B)727が微量に含有するアルカリ金属元素がゲート絶縁膜725に拡散するのを防ぐことができる。いずれにしても、導電層(B)727は抵抗率を10〜50μΩcmの範囲とすることが好ましい。

【0128】

次に、フォトマスクを用い、フォトリソグラフィーの技術を使用してレジストマスク728a〜728fを形成し、導電層(A)726と導電層(B)727とを一括でエッチングしてゲート電極729〜733と容量配線734を形成する。ゲート電極729〜733と容量配線734は、導電層(A)から成る729a〜733aと、導電層(B)から成る729b〜733bとが一体として形成されている(図16(A))。

【0129】

また、この状態における島状半導体層715、716とゲート電極729、730との位置関係を図18(D)に示す。同様に島状半導体層719とゲート電極733、容量配線734の関係を図19(D)に示す。図18(D)および図19(D)において、ゲート絶縁膜725は省略する。

【0130】

導電層(A)および導電層(B)をエッチングする方法は実施者が適宣選択すれば良いが、前述のようにWを主成分とする材料で形成されている場合には、高速でかつ精度良くエッチングを実施するために高密度プラズマを用いたドライエッチング法を適用することが望ましい。高密度プラズマを得る方法として、マイクロ波プラズマや誘導結合プラズマ(Inductively Coupled Plasma:ICP)エッチング装置を用いると良い。

【0131】

例えば、ICPエッチング装置を用いたWのエッチング法は、エッチングガスにCF4とCl2の2種のガスを反応室に導入し、圧力0.5〜1.5Pa(好ましくは1Pa)とし、誘導結合部に200〜1000Wの高周波(13.56MHz)電力を印加する。この時、基板が置かれたステージには20Wの高周波電力が印加され、自己バイアスで負電位に帯電することにより、正イオンが加速されて異方性のエッチングを行うことができる。ICPエッチング装置を使用することにより、Wなどの硬い金属膜も2〜5nm/秒のエッチング速度を得ることができる。また、残渣を残すことなくエッチングするためには、10〜20%程度の割合でエッチング時間を増しオーバーエッチングをすると良い。しかし、この時に下地とのエッチングの選択比に注意する必要がある。例えば、W膜に対する酸化窒化シリコン膜(ゲート絶縁膜725)の選択比は2.5〜3であるので、このようなオーバーエッチング処理により、酸化窒化シリコン膜が露出した面は20〜50nm程度エッチングされて実質的に薄くなる。

【0132】

そして、画素TFTのnチャネル型TFTにLDD領域を形成するために、n型を付与する不純物元素添加の工程(n--ドープ工程)を行う。ゲート電極729〜733をマスクとして自己整合的にn型を付与する不純物元素をイオンドープ法で添加すればよい。n型を付与する不純物元素として添加するリン(P)の濃度は1×1016〜5×1019atoms/cm3の濃度範囲で添加する。このようにして、図16(B)に示すように島状半導体層に低濃度n型不純物領域735〜739を形成する。

【0133】

次に、nチャネル型TFTにおいて、ソース領域またはドレイン領域として機能する高濃度n型不純物領域の形成を行う(n+ドープ工程)。まず、フォトマスクを用い、レジストのマスク740a〜740dを形成し、n型を付与する不純物元素を添加して高濃度n型不純物領域741〜746を形成する。n型を付与する不純物元素にはリン(P)を用い、その濃度が1×1020〜1×1021atoms/cm3の濃度範囲となるようにフォスフィン(PH3)を用いたイオンドープ法で行う(図16(C))。

【0134】

そして、pチャネル型TFTを形成する島状半導体層715、717にソース領域およびドレイン領域とする高濃度p型不純物領域748、749を形成する。ここでは、ゲート電極729、731をマスクとしてp型を付与する不純物元素を添加し、自己整合的に高濃度p型不純物領域を形成する。このとき、nチャネル型TFTを形成する島状半導体膜716、718、719は、フォトマスクを用いてレジストマスク747a〜747cを形成し全面を被覆しておく。

【0135】

高濃度p型不純物領域748、749はジボラン(B2H6)を用いたイオンドープ法で形成する。この領域のボロン(B)濃度は3×1020〜3×1021atoms/cm3となるようにする(図16(D))。

【0136】

この高濃度p型不純物領域748、749には、前工程においてリン(P)が添加されていて、高濃度p型不純物領域748a、749aには1×1020〜1×1021atoms/cm3の濃度で、高濃度p型不純物領域748b、749bには1×1016〜5×1019atoms/cm3の濃度でリンが含まれるが、この工程で添加するボロン(B)の濃度を、含まれるリンの濃度の1.5から3倍とすることでpチャネル型TFTのソース領域およびドレイン領域として問題なく機能させることができる。

【0137】

その後、図17(A)に示すように、ゲート電極およびゲート絶縁膜上から保護絶縁膜750を形成する。保護絶縁膜は酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜、またはこれらを組み合わせた積層膜で形成すれば良い。いずれにしても保護絶縁膜750は無機絶縁物材料から形成する。保護絶縁膜750の膜厚は100〜200nmとする。

【0138】

ここで、酸化シリコン膜を用いる場合には、プラズマCVD法で、オルトケイ酸テトラエチル(Tetraethyl Orthosilicate:TEOS)とO2とを混合し、反応圧力40Pa、基板温度300〜400℃とし、高周波(13.56MHz)電力密度0.5〜0.8W/cm2で放電させて形成することができる。酸化窒化シリコン膜を用いる場合には、プラズマCVD法でSiH4、N2O、NH3から作製される酸化窒化シリコン膜、またはSiH4、N2Oから作製される酸化窒化シリコン膜で形成すれば良い。この場合の作製条件は反応圧力20〜200Pa、基板温度300〜400℃とし、高周波(60MHz)電力密度0.1〜1.0W/cm2で形成することができる。また、SiH4、N2O、H2から作製される酸化窒化水素化シリコン膜を適用しても良い。窒化シリコン膜も同様にプラズマCVD法でSiH4、NH3から作製することが可能である。このような保護絶縁膜は、基板を中心に考えて圧縮応力となるように形成する。

【0139】

その後、それぞれの濃度で添加されたn型またはp型を付与する不純物元素を活性化する工程を行う。この工程は電熱炉を用いるファーネスアニール法で行う。その他に、レーザーアニール法、またはラピッドサーマルアニール法(RTA法)を適用することができる。ファーネスアニール法では酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400〜700℃、代表的には500〜600℃で行うことが好ましく、本実施例では550℃で4時間の熱処理を行う。また、基板701に耐熱温度が低いプラスチック基板を用いる場合にはレーザーアニール法を用いる(図17(B))。

【0140】

活性化の工程の後、さらに、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜12時間の熱処理を行い、島状半導体層を水素化する工程を行う。この工程は熱的に励起された水素により島状半導体層のダングリングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化(プラズマにより励起された水素を用いる)を行っても良い。また、基板701の耐熱性が許せば300〜450℃の加熱処理により下地膜702の酸化窒化水素化シリコン膜702b、保護絶縁膜750の酸化窒化シリコン膜の水素をに拡散させて島状半導体層を水素化しても良い。

【0141】

活性化および水素化の工程が終了したら、有機絶縁物からなる層間絶縁膜751を1.0〜2.0μmの平均厚を有して形成する。有機絶縁物としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、BCB(ベンゾシクロブテン)等を使用することができる。例えば、基板に塗布後、熱重合するタイプのポリイミドを用いる場合には、クリーンオーブンで300℃で焼成して形成する。また、アクリルを用いる場合には、2液性のものを用い、主材と硬化剤を混合した後、スピナーを用いて基板全面に塗布した後、ホットプレートで80℃で60秒の予備加熱を行い、さらにクリーンオーブンで250℃で60分焼成して形成することができる。

【0142】

層間絶縁膜を有機絶縁物で形成することにより、表面を良好に平坦化させることができる。また、有機絶縁物は一般に誘電率が低いので、寄生容量を低減するできる。しかし、吸湿性があり保護膜としての効果は弱いので、本実施例のように、保護絶縁膜750として形成した酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜などと組み合わせて用いることが好ましい。

【0143】

その後、フォトマスクを用い、所定のパターンのレジストマスクを形成し、それぞれの島状半導体膜に形成されたソース領域またはドレイン領域に達するコンタクトホールを形成する。コンタクトホールの形成はドライエッチング法により行う。この場合、エッチングガスにCF4、O2、Heの混合ガスを用い有機絶縁物から成る層間絶縁膜751をまずエッチングし、その後、続いてエッチングガスをCF4、O2として保護絶縁膜750をエッチングする。さらに、島状半導体層との選択比を高めるために、エッチングガスをCHF3に切り替えてゲート絶縁膜725をエッチングすることにより、良好にコンタクトホールを形成することができる。

【0144】

そして、導電性の金属膜をスパッタ法や真空蒸着法で形成し、フォトマスクによりレジストマスクを形成し、エッチングによってソース配線752〜756とドレイン配線757〜761を形成する。ドレイン配線762は隣接する画素のドレイン配線を示す。ここで、ドレイン配線761は画素電極として機能するものである。図示していないが、本実施例ではこの電極を、Ti膜を50〜150nmの厚さで形成し、島状半導体層のソースまたはドレイン領域を形成する半導体膜とコンタクトを形成し、そのTi膜上に重ねてアルミニウム(Al)を300〜400nmの厚さで形成して配線とする。

【0145】

図18(E)はこの状態における島状半導体層715、716、ゲート電極729、730、ソース配線752、753およびドレイン配線757、758の上面図を示す。ソース配線752、753は図示されていない層間絶縁膜および保護絶縁膜に設けられたコンタクトホールによって、島状半導体層715、716とそれぞれ830、833で接続している。また、ドレイン配線757、758は831、832で島状半導体層715、716と接続している。

【0146】

同様に、図19(E)では島状半導体層719、ゲート電極733、容量配線734、ソース配線756およびドレイン配線761の上面図を示し、ソース配線756はコンタクト部834で、ドレイン配線761はコンタクト部835でそれぞれ島状半導体層719と接続している。

【0147】

いずれにしても、第1の形状を有する島状半導体層の内側の領域に、歪みが残留している領域を除去して、第2の形状を有する島状半導体層を形成し、TFTを形成する。

【0148】

この状態で水素化処理を行うとTFTの特性向上に対して好ましい結果が得られる。例えば、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜12時間の熱処理を行うと良く、あるいはプラズマ水素化法を用いても同様の効果が得られる。また、このような熱処理により保護絶縁膜750や、下地膜702にに存在する水素を島状半導体膜715〜719に拡散させ水素化をすることもできる。いずれにしても、島状半導体層715〜719中の欠陥密度を1016/cm3以下とすることが望ましく、そのためには水素を5×1018〜5×1019atoms/cm3程度付与することが好ましい。(図17(C))。

【0149】

こうして同一の基板上に、駆動回路のTFTと画素部の画素TFTとを有した基板を完成させることができる。駆動回路には第1のpチャネル型TFT800、第1のnチャネル型TFT801、第2のpチャネル型TFT802、第2のnチャネル型TFT803、画素部には画素TFT804、保持容量805が形成されている。本明細書では便宜上このような基板をアクティブマトリクス基板と呼ぶ。

【0150】

駆動回路の第1のpチャネル型TFT800には、島状半導体膜715にチャネル形成領域806、高濃度p型不純物領域から成るソース領域807a、807b、ドレイン領域808a、808bを有した構造となっている。

【0151】

第1のnチャネル型TFT801には、島状半導体膜716にチャネル形成領域809、ゲート電極730と重なるLDD領域810、ソース領域812、ドレイン領域811を有している。このLDD領域において、ゲート電極730と重なるLDD領域のチャネル長方向の長さは0.5〜3.0μm、好ましくは1.0〜2.0μmとする。nチャネル型TFTにおけるLDD領域の長さをこのようにすることにより、ドレイン領域近傍に発生する高電界を緩和して、ホットキャリアの発生を防ぎ、TFTの劣化を防止することができる。

【0152】

駆動回路の第2のpチャネル型TFT802は同様に、島状半導体膜717にチャネル形成領域813、高濃度p型不純物領域から成るソース領域814a、814b、ドレイン領域815a、815bを有したシングルドレインの構造を有している。

【0153】

第2のnチャネル型TFT803には、島状半導体膜718にチャネル形成領域816、ゲート電極732と一部が重なるLDD領域817、818、ソース領域820、ドレイン領域819が形成されている。このTFTのゲート電極732と重なるLDD領域の長さも0.5〜3.0μm、好ましくは1.0〜2.0μmとする。また、ゲート電極と重ならないLDD領域のチャネル長方向の長さは0.5〜4.0μm、好ましくは1.0〜2.0μmとする。

【0154】

画素TFT804には、島状半導体膜719にチャネル形成領域821、822、LDD領域823〜825、ソースまたはドレイン領域826〜828を有している。LDD領域のチャネル長方向の長さは0.5〜4.0μm、好ましくは1.5〜2.5μmである。さらに、容量配線734と、ゲート絶縁膜と同じ材料から成る絶縁膜と、画素TFT804のドレイン領域828に接続する半導体層829とから保持容量805が形成されている。図17(C)では画素TFT804をダブルゲート構造としたが、シングルゲート構造でも良いし、複数のゲート電極を設けたマルチゲート構造としても差し支えない。

【0155】

図20は画素部のほぼ一画素分を示す上面図である。図中に示すA−A'断面が図17(C)に示す画素部の断面図に対応している。画素TFT804のゲート電極733は、図示されていないゲート絶縁膜を介してその下の島状半導体層719と交差している。図示はしていないが、島状半導体層には、ソース領域、ドレイン領域、LDD領域が形成されている。また、834はソース配線756とソース領域826とのコンタクト部、835はドレイン配線761とドレイン領域828とのコンタクト部である。保持容量805は、画素TFT804のドレイン領域828から延在する半導体層829がゲート絶縁膜を介して容量配線734と重なる領域で形成されている。

【0156】

以上のようにしてアクティブマトリクス基板が完成する。本実施例に従って作製されたアクティブマトリクス基板は、画素部および駆動回路の仕様に応じて適切な構造のTFTを配置している。そのため、このアクティブマトリクス基板を用いた電気光学装置の動作性能と信頼性を向上させることを可能としている。

【0157】

なお、本実施例では画素TFT804のドレイン配線761をそのまま画素電極として用いており、反射型液晶表示装置に対応した構造となっている。しかし、ドレイン配線761に電気的に接続されるように透明導電膜でなる画素電極を形成することで透過型液晶表示装置にも対応できる。

【0158】

また、本実施例は本発明を用いた半導体装置の作製工程の一例であり、本実施例に示した材料や数値範囲に限定する必要はない。さらに、LDD領域の配置なども実施者が適宜決定すれば良い。

【0159】

〔実施例7〕

本実施例では実施例6に従って作製したアクティブマトリクス基板から、アクティブマトリクス型液晶表示装置を作製する工程を説明する。まず、図21(A)に示すように、図17(C)の状態のアクティブマトリクス基板にパターニングにより樹脂材料でなるスペーサ901a〜901fを形成する。なお、スペーサとして公知の球状シリカ等を散布して用いることもできる。

【0160】

本実施例では、樹脂材料でなるスペーサ901a〜901fとしてJSR社製のNN700を用い、スピナーで塗布した後、露光と現像処理によって所定のパターンに形成する。さらにクリーンオーブンなどで150〜200℃で加熱して硬化させる。このようにして作製されるスペーサは露光と現像処理の条件によって形状を異ならせることができるが、好ましくは、柱状で頂部が平坦な形状となるようにすると、対向側の基板を合わせたときに液晶表示パネルとしての機械的な強度を確保することができる。

【0161】

また、形状は円錐状、角錐状など特別の限定はないが、例えば円錐状としたときに具体的には、高さHを1.2〜5μmとし、平均半径L1を5〜7μm、平均半径L1と底部の半径L2との比を1対1.5とする。このとき側面のテーパー角は±15°以下とする。

【0162】

スペーサ901a〜901fの配置は任意に決定しても良いが、好ましくは、図21(A)で示すように、画素部においてはドレイン配線761(画素電極)のコンタクト部835と重ねてその部分を覆うように形成すると良い。コンタクト部835は平坦性が損なわれこの部分では液晶がうまく配向しなくなるので、コンタクト部835にスペーサ用の樹脂を充填することでディスクリネーションなどを防止することができる。

【0163】

その後、配向膜902を形成する。通常液晶表示素子の配向膜にはポリイミド樹脂を用いる。配向膜を形成した後、ラビング処理を施して液晶分子がある一定のプレチルト角を持って配向するようにする。画素部に設けたスペーサ901a〜901fの端部からラビング方向に対してラビングされない領域が2μm以下となるようにすることが好ましい。また、ラビング処理では静電気の発生がしばしば問題となるが、駆動回路のTFT上において、少なくともソース配線およびドレイン配線上にもスペーサ901a〜901eを形成しておくと、ラビング工程におけるスペーサとしての本来の役割と、静電気からTFTを保護する効果を得ることができる。

【0164】

対向基板903には、遮光膜904、透明導電膜でなる対向電極905および配向膜906を形成する。遮光膜904はTi、Cr、Alなどを150〜300nmの厚さで形成する。そして、画素部と駆動回路が形成されたアクティブマトリクス基板と対向基板とをシール剤907で貼り合わせる。シール剤907にはフィラー908が混合されていて、このフィラー908とスペーサ901a〜901fによって均一な間隔を持って対向基板とアクティブマトリクス基板とが貼り合わせられる。

【0165】

その後、両基板の間に液晶材料909を注入し、封止剤(図示せず)によって完全に封止する。液晶材料には公知の液晶材料を用いれば良い。例えば、TN液晶の他に、電場に対して透過率が連続的に変化する電気光学応答性を示す無しきい値反強誘電性混合液晶を用いることもできる。無しきい値反強誘電性混合液晶にはV字型の電気光学応答特性を示すものもある。詳細は「H.Furue et al.;Charakteristics and Drivng Scheme of Polymer-Stabilized Monostable FLCD Exhibiting Fast Response Time and High Contrast Ratio with Gray-Scale Capability,SID,1998」、「T.Yoshida et al.;A Full-Color Thresholdless Antiferroelectric LCD Exhibiting Wide Viewing Angle with Fast Response Time,841,SID97DIGEST,1997」、「S.Inui et al.;Thresholdless antiferroelectricity in liquid crystals and its application to displays,671-673,J.Mater.Chem.6(4),1996」、または米国特許第5,594,569号を参照すれば良い。

【0166】

このようにして図21(B)に示すアクティブマトリクス型液晶表示装置が完成する。図21ではスペーサ901a〜901eを駆動回路のTFT上の少なくともソース配線およびドレイン配線上にに分割して形成したが、その他に、駆動回路の全面を覆って形成しても差し支えない。

【0167】

図22はアクティブマトリクス基板の上面図を示し、画素部および駆動回路部とスペーサおよびシール剤の位置関係を示す上面図である。画素部1500の周辺に駆動回路として走査信号駆動回路1501と画像信号駆動回路1502が設けられている。さらに、その他CPUやメモリなどの信号処理回路1503も付加されていても良い。

【0168】

そして、これらの駆動回路は接続配線1511によって外部入出力端子1510と接続されている。画素部1500では走査信号駆動回路1501から延在するゲート配線群1504と画像信号駆動回路1502から延在するソース配線群1505がマトリクス状に交差して画素を形成し、各画素にはそれぞれ画素TFT804と保持容量805が設けられている。

【0169】

画素部において設けられるスペーサ1506は、図21で示したスペーサ901fに対応するもので、すべての画素に対して設けても良いが、マトリクス状に配列した画素の数個から数十個おきに設けても良い。即ち、画素部を構成する画素の全数に対するスペーサの数の割合は20〜100%とすると良い。また、駆動回路部に設けるスペーサ1507〜1509はその全面を覆うように設けても良いし、図21で示したように各TFTのソースおよびドレイン配線の位置にあわせて複数個に分割して設けても良い。

【0170】

シール剤907は、基板701上の画素部1500および走査信号制御回路1501、画像信号制御回路1502、その他の信号処理回路1503の外側であって、外部入出力端子1510よりも内側に形成する。

【0171】

このようなアクティブマトリクス型液晶表示装置の構成を図23の斜視図を用いて説明する。図23においてアクティブマトリクス基板は、ガラス基板701上に形成された、画素部1500と、走査信号駆動回路1501と、画像信号駆動回路1502とその他の信号処理回路1503とで構成される。

【0172】

画素部1500には画素TFT804と保持容量805が設けられ、画素部の周辺に設けられる駆動回路はCMOS回路を基本として構成されている。走査信号駆動回路1501と、画像信号駆動回路1502はそれぞれゲート配線733とソース配線756で画素TFT804に接続している。また、フレキシブルプリントサーキット(Flexible Printed Circuit:FPC)1513が外部入力端子1510に接続していて画像信号などを入力するのに用いる。フレキシブルプリントサーキット1513は補強樹脂1512で接着強度を高めて固定されている。そして接続配線1511でそれぞれの駆動回路に接続している。また、対向基板903には図示していないが、遮光膜や透明電極が設けられている。

【0173】

このような構成の液晶表示装置は、実施例6で示したアクティブマトリクス基板を用いて形成することができる。例えば、図17(C)の構造のアクティブマトリクス基板を用いれば反射型の液晶表示装置が得られ、実施例6で述べたように画素電極として透明導電膜を用いたアクティブマトリクス基板を用いれば透過型の液晶表示装置を得ることができる。

【0174】

〔実施例8〕

実施例1では、非晶質半導体膜に対して実施形態1または実施形態2に示した方法でレーザーアニールを施して結晶化する例を示しているが、ある程度まで結晶化が進んだ段階の半導体膜に対してレーザーアニールを行うこともできる。

【0175】

即ち、ファーネスアニールにより非晶質半導体膜を結晶化させて得た結晶質半導体膜に、さらにレーザーアニールを施して結晶性を改善する場合においても本発明のレーザーアニールは有効である。

【0176】

具体的には、特開平7−161634号公報、特開平7−321339号公報または特開平7−131034号公報等の出願におけるレーザー照射工程(レーザーアニール工程)に、実施形態1乃至実施形態3のレーザーアニール方法を用いることが可能である。

【0177】

なお、上記公報に本発明を用いた後、形成された結晶質半導体膜を用いたTFTを作製することができる。即ち、本実施例と実施例4乃至実施例7とを組み合わせることが可能である。

【0178】

〔実施例9〕

実施例1〜実施例3では、本発明を液晶表示装置に対して用いた例を示しているが、本発明はTFTを用いる半導体装置であれば如何なるものにも実施することが可能である。

【0179】

具体的には、アクティブマトリクス型のEL(エレクトロルミネッセンス)表示装置やアクティブマトリクス型のEC(エレクトロクロミクス)表示装置を作製する場合に、半導体膜のレーザーアニール工程において本発明を実施することが可能である。その際、実施形態1または2のどちらの構成を用いても良い。

【0180】

さらに、ICやLSIに使われるSRAMの負荷トランジスタを形成する際に本発明を実施することもできるし、ICやLSIの上に三次元構造でTFTを形成する場合においても本発明は有効である。

【0181】

本発明はレーザーアニール工程の部分の発明であるので、その他の部分は公知のTFT作製プロセスが適用できる。従って、アクティブマトリクス型EL表示装置やアクティブマトリクス型EC表示装置を作製する場合には、公知の技術に本発明を適用すれば良い。勿論、図15〜17で説明した作製工程を参考にして作製することも可能である。

【0182】

〔実施例10〕

本発明は、アクティブマトリクス型液晶表示装置やアクティブマトリクス型EL表示装置などの電気光学装置を表示ディスプレイとして有する電子装置(電子機器ともいう)に対して実施することが可能である。電子装置としては、パーソナルコンピュータ、デジタルカメラ、ビデオカメラ、携帯情報端末(モバイルコンピュータ、携帯電話、電子書籍など)、ナビゲーションシステムなどが上げられる。

【0183】

図24(A)はパーソナルコンピュータであり、マイクロプロセッサやメモリーなどを備えた本体2001、画像入力部2002、表示部2003、キーボード2004で構成される。本発明は表示部2003やその他の信号処理回路の作製に際して実施することができる。

【0184】

図24(B)はビデオカメラであり、本体2101、表示部2102、音声入力部2103、操作スイッチ2104、バッテリー2105、受像部2106で構成される。本発明は表示部2102やその他の信号制御回路の作製に際して実施することができる。

【0185】

図24(C)はゴーグル型ディスプレイであり、本体2201、表示部2202、アーム部2203から成っている。本発明は表示部2202やその他図示されていない信号制御回路の作製に際して実施することができる。。

【0186】

図24(D)はテレビゲームまたはビデオゲームなどの電子遊技機器であり、CPU等の電気回路2308、記録媒体2304などが搭載された本体2301、コントローラ2305、表示部2303、本体2301に組み込まれた表示部2302で構成される。表示部2303と本体2301に組み込まれた表示部2302とは、同じ情報を表示しても良いし、前者を主表示部とし、後者を副表示部として記録媒体2304の情報を表示したり、機器の動作状態を表示したり、或いはタッチセンサーの機能を付加して操作盤とすることもできる。また、本体2301とコントローラ2305と表示部2303とは、相互に信号を伝達するために有線通信としても良いし、センサ部2306、2307を設けて無線通信または光通信としても良い。本発明は、表示部2302、2303の作製に際して実施することができる。また、表示部2303は従来のCRTを用いることもできる。

【0187】

図24(E)はプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレーヤーであり、本体2401、表示部2402、スピーカー部2403、記録媒体2404、操作スイッチ2405で構成される。なお、記録媒体にはDVD(Digital Versatile Disc)やコンパクトディスク(CD)などを用い、音楽プログラムの再生や映像表示、ビデオゲーム(またはテレビゲーム)やインターネットを介した情報表示などを行うことができる。本発明は表示部2402やその他の信号制御回路の作製に際して実施することができる。

【0188】

図24(F)はデジタルカメラであり、本体2501、表示部2502、接眼部2503、操作スイッチ2504、受像部(図示しない)で構成される。本発明は表示部2502やその他の信号制御回路の作製に際して実施することができる。

【0189】

図25(A)はフロント型プロジェクターであり、光学エンジン2601、スクリーン2602で構成される。図25(B)はリア型プロジェクターであり、本体2701、光学エンジン2702、ミラー2703、スクリーン2704で構成される。

【0190】

なお、図25(C)に、図25(A)および図25(B)における光学エンジン(光源光学系および表示装置を含むシステム)2601、2702の構造の一例を示す。光学エンジン2601、2702は光源光学系2801、ミラー2802、2804〜2806、ダイクロイックミラー2803、ビームスプリッター2807、液晶表示装置2808、位相差板2809、投射光学系2810で構成される。投射光学系2810は複数の光学レンズで構成される。

【0191】

図25(C)では液晶表示装置2808を三つ使用する三板式の例を示したが、このような方式に限定されず、単板式の光学系で構成しても良い。また、図25(C)中で矢印で示した光路には適宣光学レンズや偏光機能を有するフィルムや位相を調節するためのフィルムや、IRフィルムなどを設けても良い。

【0192】

また、図25(D)は図25(C)における光源光学系2801の構造の一例を示した図である。本実施例では、光源光学系2801はリフレクター2811、光源2812、レンズアレイ2813、2814、偏光変換素子2815、集光レンズ2816で構成される。なお、図25(D)に示した光源光学系は一例であって図示した構成に限定されるものではない。

【0193】

また、ここでは図示しなかったが、本発明はその他にも、ナビゲーションシステムやイメージセンサの読み取り回路などの作製に際して実施することもできる。。このように本発明の適用範囲はきわめて広く、あらゆる分野の電子装置の作製に際して実施することができる。

【0194】

〔実施例11〕

本実施例では、図27(A)、(B)に示した構造に対して、実施例1に示した条件でレーザー光を照射した場合について説明する。

【0195】

図27(A)の構造において、1601は1.1mm厚の石英基板、1602は200nm厚の窒化酸化シリコン膜、1603は55nm厚のアモルファスシリコン膜である。このように、図27(A)の構造では通常のレーザー結晶化を行った。

【0196】

また、図27(B)の構造において、1604は表面(反射面)が窒化タンタル膜でなる反射体、1605は1.1mm厚の石英基板、1606は200nm厚の窒化酸化シリコン膜、1607は55nm厚のアモルファスシリコン膜である。このように、図27(B)の構造では本発明を実施してレーザー結晶化を行った。

【0197】

その結果得られたポリシリコン膜のTEM(Transmission Electron Microscopy)写真を図28(A)、(B)に示す。図28(A)は、図27(A)の構造でアモルファスシリコン膜1603を結晶化して得たポリシリコン膜のTEM写真であり、図28(B)は、図27(B)の構造でアモルファスシリコン膜1607を結晶化して得たポリシリコン膜のTEM写真である。

【0198】

図28(A)と図28(B)とを比較すると、本発明を実施した図28(B)のポリシリコン膜の方が明らかに結晶粒径が大きいことを確認できる。以上のように、本発明を実施することで結晶質半導体膜の平均結晶粒径を拡大することができることがTEM写真からも確かめられた。

【0199】

〔実施例12〕

本出願人の実験によれば、実効エネルギー強度比(I0'/I0)が0<I0'/I0<1または1<I0'/I0の関係を満たす場合において、特に平均結晶粒径の拡大が顕著な条件が存在した。

【0200】

本実施例では、図6に示した構造において基板(全て1.1mm厚)または反射体(厳密には反射体の反射面)の材質を様々に変えて行った実験について説明する。まず、実験に用いた試料(A)〜(B)における基板及び反射体とその時の実効エネルギー強度比を表1に示す。

【0201】

【表1】

【0202】

なお、表1において、#1737はコーニング社製ガラス基板の商品名であり、AN100は旭ガラス社製ガラス基板の商品名である。

【0203】

このように実効エネルギー強度比が0.07〜1.0の範囲で作製された試料に対して実施例1〜3と同様の条件でXeClエキシマレーザー光を照射し、その結果得られたポリシリコン膜をSEM写真にて観察した。

【0204】

その結果、実効エネルギー強度比が0.29、0.33、0.53または0.67では平均結晶粒径が1μm程度となることが確認され、実効エネルギー強度比が1.0、0.16、0.11、0.07の場合においては、平均結晶粒径が0.3μm程度であることが確認された。即ち、第一次レーザー光と第二次レーザー光とで実効エネルギー強度が20%以上違う条件において、平均結晶粒径の拡大が顕著に起こると考えられる。従って、以上の結果は、実効エネルギー強度比がI0'/I0=0.2〜0.9(好ましくは0.3〜0.7)である時に最適な結晶化条件が存在することを示唆していると考えられる。

【0205】

〔実施例13〕

本実施例では、実施例12において、反射体の反射面における多重反射の影響を考慮して実効エネルギー強度比を求めた例を示す。なお、実験に用いた試料(A)〜(H)は実施例12と同一のものである。また、本実施例の場合、第二次レーザー光の実効エネルギー強度(I0')は、I0'=IaTsubRmirrorTsub(1−RSiON-Si)/1−RSiON-SiTsubRmirrorTsubで表される。

【0206】

但し、Tsubは基板の透過率、Rmirrorは反射体の表面での反射率、RSiON-SiはSiON膜中からアモルファスシリコン膜へ入射する際の反射率である。なお、空気中からSiON膜へ入射する際の反射率、SiON膜中の透過率、SiON膜中から基板へ入射する際の反射率及び基板中からSiON膜へ入射する際の反射率は、実験的に無視しうることが判明したので計算に含めなかった。

【0207】

上記数式から計算されたデータを表2に示す。表2に示すデータは表1のデータに多重反射の影響を考慮して修正を加えたものである。

【0208】

【表2】

【0209】

表2に示したデータを基にしても実施例7で述べた最適な結晶化条件、即ち実効エネルギー強度比がI0'/I0=0.2〜0.9(好ましくは0.3〜0.7)を満たす条件は変わらなかった。

【0210】

〔実施例14〕

本実施例では、本発明の効果について実験結果に基づいて説明を行う。なお、本実施例では、結晶性を相対的に5段階に分けて評価した。本明細書中において結晶状態は以下のように区別して評価することにした。

【0211】

結晶状態(0):膜がアブレーションにより消失するに至った状態。

結晶状態(1):図29(A)に示されるように、細かい結晶粒が見受けられる微結晶状態。

結晶状態(2):図29(B)に示されるように、平均結晶粒径が300〜450nm程度の結晶粒が見受けられる結晶状態。

結晶状態(3):図30(A)に示されるように、平均結晶粒径が600〜800nm程度の比較的大きな結晶粒が見受けられる結晶状態。

結晶状態(4):図30(B)に示されるように、長径で3μm程度を超える非常に大きな結晶粒が見受けられる結晶状態。なお、本実施例ではこの状態の結晶粒をSLG(Super Lateral Growth)により形成された結晶粒と呼ぶことにする。

【0212】

以上の評価に基づき、レーザー結晶化の条件と結晶状態の関係を調べた。図31に示されるデータは、照射エネルギー(アモルファスシリコン膜に到達する直前のレーザー光のエネルギー強度Iaに相当する)と結晶状態の関係をシングル照射とデュアル照射とで比較した結果である。なお、シングル照射とは表面のみへレーザー光を照射した場合であり、デュアル照射とは表面および裏面へレーザー光を照射した場合を指す。

【0213】

図31から明らかなように、デュアル照射の方が低い照射エネルギーで結晶状態の良好な膜が得られる。即ち、シングル照射の場合はSLGを起こすために510mJ/cm2前後の照射エネルギーが必要であるが、デュアル照射の場合は440〜460mJ/cm2前後の照射エネルギーで良い。このことは従来のシングル照射に比べて本発明で用いるデュアル照射の方が低い照射エネルギーでより結晶性の高い半導体膜が得られることを示している。

【0214】

また、実験的には照射エネルギーが高いほど第一次レーザー光の実効エネルギーが高くなり、形成された結晶質半導体膜の表面荒れが増すことが判っている。このことはSLGにより形成された結晶を得るにあたって、デュアル照射の方が膜表面に与えるダメージを少なくできることを示唆している。

【0215】

次に、デュアル照射の場合において、反射体の反射率を変えて実効エネルギー強度比を変えた実験結果を示す。図32(A)は照射エネルギーと結晶状態の関係を、図32(B)は実効入射エネルギーと結晶状態の関係を示している。

【0216】

図32(A)に示すように、反射体の反射率が高くなるほど(第二次レーザー光の実効エネルギー強度が強くなるほど)、同じ照射エネルギーでも結晶状態が良くなる結果が得られた。これは同じ照射エネルギーの場合、デュアル照射の方が実効入射エネルギーが高いためと考えられる。なお、実効入射エネルギーとは、非晶質半導体膜に入射した実効エネルギーの総和であり、第一次レーザー光の実効エネルギー強度と第二次実効エネルギー強度の和に相当する。

【0217】

そこで、同じ照射エネルギーに固定して実効入射エネルギーと結晶状態の関係を調べた。すると図32(B)に示すように、反射率が高くなるほどSLGにより形成された結晶(結晶状態4)を得るために必要な実効入射エネルギーが高エネルギー側へシフトしていた。換言すれば、反射体の反射率は低い方が、より少ない実効入射エネルギーでSLGにより形成された結晶粒を得やすい、即ちエネルギー損失の少ない結晶化が可能であることを意味している。

【0218】

また、図32(B)に示すように、反射体の反射率の低くしていくとSLGに必要な実効入射エネルギーも低くなっていくが、反射率がゼロではSLGは発生しないことが確認されている。このことから反射体の反射率には、SLGが発生する上での最適値が存在すると考えられる。

【0219】

【発明の効果】

本発明に示したように、非晶質半導体膜をレーザー結晶化する際に、レーザー光を非晶質半導体膜の表面及び裏面を同時に照射し、且つ、裏面側に照射される実効エネルギー強度と表面側に照射される実効エネルギー強度とを異なるものとすることにより、従来に比べて平均結晶粒径の大きい結晶質半導体膜を得ることが可能となる。

【0220】

そして、結晶粒径の大きい結晶質半導体膜を得ることにより、TFT又はTFTで形成されたアクティブマトリクス型表示装置に代表される半導体装置の性能を大幅に向上させうる。

【図面の簡単な説明】

【図1】 レーザー装置の構成を示す図。

【図2】 レーザー装置の光学系の構成を示す図。

【図3】 レーザーアニールの方法を示す図。

【図4】 レーザー装置の構成を示す図。

【図5】 レーザー装置の光学系の構成を示す図。

【図6】 第一次レーザー光と第二次レーザー光を説明するための図。

【図7】 ポリシリコン膜の結晶粒の様子を示すSEM写真。

【図8】 ポリシリコン膜の結晶粒の様子を示すSEM写真。

【図9】 ポリシリコン膜の結晶粒の様子を示すSEM写真。

【図10】 ポリシリコン膜の結晶粒の様子を示すSEM写真。

【図11】 ポリシリコン膜の結晶粒の様子を示すSEM写真。

【図12】 ポリシリコン膜の結晶粒の様子を示すSEM写真。

【図13】 TFTを用いたCMOS回路の作製工程を示す図。

【図14】 活性層の配置の例を示す図。

【図15】 アクティブマトリクス基板の作製工程を示す図。

【図16】 アクティブマトリクス基板の作製工程を示す図。

【図17】 アクティブマトリクス基板の作製工程を示す図。

【図18】 アクティブマトリクス基板の作製工程を示す図。

【図19】 アクティブマトリクス基板の作製工程を示す図。

【図20】 画素構造を示す図。

【図21】 アクティブマトリクス型液晶表示装置の断面構造を示す図。

【図22】 アクティブマトリクス型液晶表示装置の上面構造を示す図。

【図23】 アクティブマトリクス型液晶表示装置の斜視図。

【図24】 電子装置の一例を示す図。

【図25】 プロジェクターの一例を示す図。

【図26】 試料構造を示す図。

【図27】 ポリシリコン膜の結晶粒の様子を示すSEM写真。

【図28】 ポリシリコン膜の結晶粒の様子を示すTEM写真。

【図29】 ポリシリコン膜の結晶状態を示すSEM写真。

【図30】 ポリシリコン膜の結晶状態を示すSEM写真。

【図31】 照射エネルギーと結晶状態の関係を示す図。

【図32】 照射エネルギーまたは実効入射エネルギーと結晶状態の関係を示す図。

Claims (8)

- 基板上に半導体膜を形成し、

前記半導体膜を島状半導体層に形成し、

前記島状半導体層の表面及び裏面にレーザー光を照射して第1の領域と、第2の領域と、第3の領域と、を含む第1の形状の結晶質島状半導体層を形成し、

前記第1の領域が、チャネル形成領域となり、前記第2の領域および前記第3の領域の一部が、ソース領域となり、前記第2の領域および前記第3の領域の一部が、ドレイン領域となるように、第2の形状の結晶質島状半導体層を形成する半導体装置の作製方法であって、

前記第2の領域は、前記第1の領域と、前記第3の領域と、に挟まれ、且つ、前記第1の領域および前記第3の領域よりも平均結晶粒径が小さく、

前記島状半導体層の裏面に照射されるレーザー光は、前記島状半導体層の裏面側に設けられた反射体で反射されて前記島状半導体層の裏面に照射され、

前記島状半導体層の表面に照射されるレーザー光の実効エネルギー強度(I0)と前記島状半導体層の裏面に照射されるレーザー光の実効エネルギー強度(I0’)が異なることを特徴とする半導体装置の作製方法。 - 基板上に半導体膜を形成し、

前記半導体膜を島状半導体層に形成し、

前記島状半導体層の表面及び裏面にレーザー光を照射して第1の領域と、第2の領域と、第3の領域と、を含む第1の形状の結晶質島状半導体層を形成し、

前記第1の領域が、チャネル形成領域となり、前記第2の領域および前記第3の領域の一部が、ソース領域となり、前記第2の領域および前記第3の領域の一部が、ドレイン領域となるように、第2の形状の結晶質島状半導体層を形成する半導体装置の作製方法であって、

前記第2の領域は、前記第1の領域と、前記第3の領域と、に挟まれ、且つ、前記第1の領域および前記第3の領域よりも平均結晶粒径が小さく、

前記島状半導体層の裏面に照射されるレーザー光は、前記島状半導体層の裏面側に設けられた反射体で反射されて前記島状半導体層の裏面に照射され、

前記島状半導体層の表面に照射されるレーザー光の実効エネルギー強度(I0)と前記島状半導体層の裏面に照射されるレーザー光の実効エネルギー強度(I0’)との間に0<I0’/I0<1または1<I0’/I0の関係があることを特徴とする半導体装置の作製方法。 - 基板上に半導体膜を形成し、

前記半導体膜を島状半導体層に形成し、

前記島状半導体層の表面及び裏面にレーザー光を照射して第1の領域と、第2の領域と、第3の領域と、第4の領域と、を含む第1の形状の結晶質島状半導体層を形成し、

前記第1の領域が、チャネル形成領域となり、前記第2の領域および前記第3の領域の一部が、ソース領域となり、前記第2の領域および前記第3の領域の一部が、ドレイン領域となるように、且つ、第4の領域が除去されるように、第2の形状の結晶質島状半導体層を形成する半導体装置の作製方法であって、

前記第2の領域は、前記第1の領域と、前記第3の領域と、に挟まれ、且つ、前記第1の領域および前記第3の領域よりも平均結晶粒径が小さく、

前記第4の領域は、前記第1の領域乃至前記第3の領域を囲み、且つ、歪みが蓄積した領域であり、

前記島状半導体層の裏面に照射されるレーザー光は、前記島状半導体層の裏面側に設けられた反射体で反射されて前記島状半導体層の裏面に照射され、

前記島状半導体層の表面に照射されるレーザー光の実効エネルギー強度(I0)と前記島状半導体層の裏面に照射されるレーザー光の実効エネルギー強度(I0’)が異なることを特徴とする半導体装置の作製方法。 - 基板上に半導体膜を形成し、

前記半導体膜を島状半導体層に形成し、

前記島状半導体層の表面及び裏面にレーザー光を照射して第1の領域と、第2の領域と、第3の領域と、第4の領域と、を含む第1の形状の結晶質島状半導体層を形成し、

前記第1の領域が、チャネル形成領域となり、前記第2の領域および前記第3の領域の一部が、ソース領域となり、前記第2の領域および前記第3の領域の一部が、ドレイン領域となるように、且つ、第4の領域が除去されるように、第2の形状の結晶質島状半導体層を形成する半導体装置の作製方法であって、

前記第2の領域は、前記第1の領域と、前記第3の領域と、に挟まれ、且つ、前記第1の領域および前記第3の領域よりも平均結晶粒径が小さく、

前記第4の領域は、前記第1の領域乃至前記第3の領域を囲み、且つ、歪みが蓄積した領域であり、

前記島状半導体層の裏面に照射されるレーザー光は、前記島状半導体層の裏面側に設けられた反射体で反射されて前記島状半導体層の裏面に照射され、

前記島状半導体層の表面に照射されるレーザー光の実効エネルギー強度(I0)と前記島状半導体層の裏面に照射されるレーザー光の実効エネルギー強度(I0’)との間に0<I0’/I0<1または1<I0’/I0の関係があることを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項4のいずれか一において、

前記第2の形状の結晶質島状半導体層上に絶縁層を形成し、

前記絶縁層上にゲート電極を形成し、

前記ゲート電極上に層間絶縁膜を形成し、

前記層間絶縁膜に前記第2の領域および前記第3の領域に形成された前記ソース領域または前記ドレイン領域に達するコンタクトホールを形成することを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項5のいずれか一において、

保持容量の電極を前記第2の領域及び前記第3の領域に形成することを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項6のいずれか一において、

前記レーザー光が線状に変形されていることを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項7のいずれか一において、

前記半導体膜とは非晶質半導体膜若しくは微結晶半導体膜であることを特徴とする半導体装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000242575A JP4919530B2 (ja) | 1999-08-18 | 2000-08-10 | 半導体装置の作製方法 |

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP1999231165 | 1999-08-18 | ||

| JP23116599 | 1999-08-18 | ||

| JP11-231165 | 1999-08-18 | ||

| JP2000242575A JP4919530B2 (ja) | 1999-08-18 | 2000-08-10 | 半導体装置の作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001127304A JP2001127304A (ja) | 2001-05-11 |

| JP2001127304A5 JP2001127304A5 (ja) | 2007-09-06 |

| JP4919530B2 true JP4919530B2 (ja) | 2012-04-18 |

Family

ID=26529732

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000242575A Expired - Fee Related JP4919530B2 (ja) | 1999-08-18 | 2000-08-10 | 半導体装置の作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4919530B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4660074B2 (ja) * | 2003-05-26 | 2011-03-30 | 富士フイルム株式会社 | レーザアニール装置 |

| KR101484296B1 (ko) | 2007-06-26 | 2015-01-19 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 기판의 제작방법 |

| CN104282539A (zh) * | 2013-07-04 | 2015-01-14 | 上海和辉光电有限公司 | 一种多晶硅制作方法 |

-

2000

- 2000-08-10 JP JP2000242575A patent/JP4919530B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001127304A (ja) | 2001-05-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3897965B2 (ja) | レーザー装置及びレーザーアニール方法 | |

| US6548370B1 (en) | Method of crystallizing a semiconductor layer by applying laser irradiation that vary in energy to its top and bottom surfaces | |

| EP1054452B1 (en) | Method for fabricating a TFT | |

| US7179698B2 (en) | Laser apparatus, laser annealing method, and manufacturing method of a semiconductor device | |

| US6624013B2 (en) | Method for manufacturing a semiconductor device | |

| US7476937B2 (en) | Semiconductor device and method of fabricating the same | |

| KR101024959B1 (ko) | 빔 호모지나이저, 레이저 조사장치 및 반도체 장치의제조방법 | |

| JP4646368B2 (ja) | 液晶表示装置の作製方法 | |

| US7433568B2 (en) | Optical element and light irradiation apparatus | |

| JP4558748B2 (ja) | 半導体装置の作製方法及び表示装置の作製方法 | |

| JP4919530B2 (ja) | 半導体装置の作製方法 | |

| US7679131B1 (en) | Semiconductor device, manufacturing method thereof, and electronic device | |

| JP4776746B2 (ja) | 半導体装置の作製方法 | |

| JP3920065B2 (ja) | 薄膜トランジスタの作製方法 | |

| JP4637333B2 (ja) | 半導体装置の作製方法 | |

| JP3902101B2 (ja) | 半導体装置の作製方法 | |

| JP3920066B2 (ja) | 薄膜トランジスタの作製方法 | |

| JP3942855B2 (ja) | 薄膜トランジスタの作製方法 | |

| JP2002203863A (ja) | 薄膜トランジスタ及びその作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070720 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070720 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100809 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110315 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110418 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110816 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111010 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120131 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120131 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150210 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150210 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |