JP5259659B2 - 電子機器 - Google Patents

電子機器 Download PDFInfo

- Publication number

- JP5259659B2 JP5259659B2 JP2010191766A JP2010191766A JP5259659B2 JP 5259659 B2 JP5259659 B2 JP 5259659B2 JP 2010191766 A JP2010191766 A JP 2010191766A JP 2010191766 A JP2010191766 A JP 2010191766A JP 5259659 B2 JP5259659 B2 JP 5259659B2

- Authority

- JP

- Japan

- Prior art keywords

- pad

- detection

- bump bonding

- insulating

- electronic device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/2801—Testing of printed circuits, backplanes, motherboards, hybrid circuits or carriers for multichip packages [MCP]

- G01R31/2818—Testing of printed circuits, backplanes, motherboards, hybrid circuits or carriers for multichip packages [MCP] using test structures on, or modifications of, the card under test, made for the purpose of testing, e.g. additional components or connectors

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/50—Testing of electric apparatus, lines, cables or components for short-circuits, continuity, leakage current or incorrect line connections

- G01R31/66—Testing of connections, e.g. of plugs or non-disconnectable joints

- G01R31/68—Testing of releasable connections, e.g. of terminals mounted on a printed circuit board

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/50—Testing of electric apparatus, lines, cables or components for short-circuits, continuity, leakage current or incorrect line connections

- G01R31/66—Testing of connections, e.g. of plugs or non-disconnectable joints

- G01R31/70—Testing of connections between components and printed circuit boards

- G01R31/71—Testing of solder joints

Landscapes

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- General Engineering & Computer Science (AREA)

- Electric Connection Of Electric Components To Printed Circuits (AREA)

- Supply And Installment Of Electrical Components (AREA)

- Wire Bonding (AREA)

Description

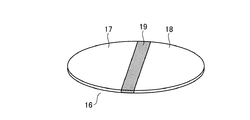

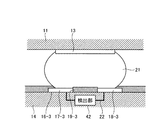

図1は、第1の実施形態の電子機器を模式的に示す断面図である。図2は、第1の実施形態の検出用バンプ接合部周辺の断面図である。図3は、回路基板上に形成された検出用バンプ接合部のパッドの形状を示す図である。

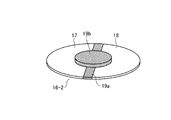

次に、第1の実施形態の変形例1について説明する。図5は、第1の実施形態の変形例1の電子機器における検出用バンプ接合部周辺の断面図である。図6は、第1の実施形態の変形例1のパッド16−2の形状を示す図である。なお、本変形例の説明では、第1の実施形態の電子機器と異なる箇所について説明する。

次に、第1の実施形態の変形例2について説明する。図7は、第1の実施形態の変形例2の電子機器における検出用バンプ接合部周辺の断面図である。図8は、第1の実施形態の変形例2のパッド16−3の形状を示す図である。なお、この変形例の説明では、第1の実施形態の電子機器と異なる箇所について説明する。

次に、第1の実施形態の変形例3について説明する。図9は、第1の実施形態の変形例3の電子機器における検出用バンプ接合部周辺の断面図である。図10は、第1の実施形態の変形例3のパッド16−4の形状を示す図である。なお、この変形例の説明では、第1の実施形態の電子機器と異なる箇所について説明する。

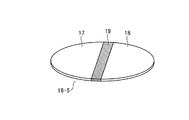

次に、第1の実施形態の変形例4について説明する。図11は、第1の実施形態の変形例4の電子機器における検出用バンプ接合部周辺の断面図である。図12は、第1の実施形態の変形例4のパッド16−5の形状を示す図である。なお、この変形例の説明では、第1の実施形態の電子機器と異なる箇所について説明する。

これまでは、検出用バンプ接合部21と接触する領域(接触領域)のうち、接触領域の中心を含む領域に絶縁部が形成される例を説明したが、絶縁部は、接触領域の中心を含む領域に形成される必要はない。図13は、第1の実施形態の変形例5のパッド16−6の形状を示す図である。

次に、第2の実施形態について説明する。図14は、第2の実施形態の電子機器における電子部品の検出用バンプ接合部周辺の断面図である。図15は、検出用バンプ接合部のパッドの形状を示す図である。

次に、第2の実施形態の変形例1について説明する。図16は、第2の実施形態の変形例1の電子機器における検出用バンプ接合部周辺の断面図である。図17は、第2の実施形態の変形例1の電子部品側パッドの形状を示す図である。なお、この変形例の説明では、第2の実施形態の電子機器と異なる箇所について説明する。

12、13 電子部品側パッド

14 回路基板

15、16 パッド

17、18 電極部

19 絶縁部

20 バンプ接合部

21 検出用バンプ接合部

22 配線

41 チップ

42 検出部

Claims (9)

- 電子機器であって、

回路基板と、

電子部品と、

前記回路基板上に形成された第1パッドと、

前記電子部品上に形成された第2パッドと、

前記第1パッドと前記第2パッドとを接合する接合部と、

前記第1パッドおよび前記第2のパッドの少なくとも一方と、前記接合部とを含む接続経路の電気特性に基づいて、前記接合部が前記電子機器の使用に伴い破断したことを検出する検出部と、を備え、

前記第1パッドおよび前記第2パッドの少なくとも一方は、前記接合部との接触領域の一部に絶縁部が形成され、

前記第1パッドと前記接合部との接触領域および前記第2パッドと前記接合部との接触領域の両方に前記絶縁部が形成されている場合は、2つの接触領域のうち一方の面積は他方の面積より小さく、

前記第1パッドと前記接合部との接触領域および前記第2パッドと前記接合部との接触領域の一方に前記絶縁部が形成されている場合は、前記絶縁部が形成されている接触領域の面積は、前記絶縁部が形成されていない接触領域の面積より小さいこと、

を特徴とする電子機器。 - 前記第1パッドおよび前記第2パッドの少なくとも一方は、前記接触領域の一部に絶縁部が形成され、前記絶縁部により互いに絶縁される複数の電極を備え、

前記検出部は、複数の前記電極のうち、少なくとも2つの電極を含む前記接続経路の電気特性に基づいて前記接合部の破断を検出すること、

を特徴とする請求項1に記載の電子機器。 - 前記第1パッドおよび前記第2パッドの少なくとも一方は、1の電極を備え、前記電極の前記接合部との接触領域の一部に絶縁部が形成されていること、

を特徴とする請求項1に記載の電子機器。 - 前記第1パッドおよび前記第2パッドの少なくとも一方は、前記接触領域のうち、前記接触領域の中心を含む領域に前記絶縁部が形成されていること、

を特徴とする請求項1〜3のいずれか1つに記載の電子機器。 - 前記絶縁部の熱膨張係数は、前記接合部の熱膨張係数と異なること、

を特徴とする請求項1〜4のいずれか1つに記載の電子機器。 - 前記接合部は、はんだバンプであること、

を特徴とする請求項1〜5のいずれか1つに記載の電子機器。 - 前記第1パッドは、前記回路基板上に複数形成され、

複数の前記第1パッドのうち、前記電子部品の周縁部に対向する前記第1パッドの少なくとも一部は、前記接触領域の一部に絶縁部が形成されていること、

を特徴とする請求項1〜6のいずれか1つに記載の電子機器。 - 前記第2パッドは、前記電子部品上に複数形成され、

複数の前記第2パッドのうち、前記電子部品の周縁部に形成された前記第2パッドの少なくとも一部は、前記接触領域の一部に絶縁部が形成されていること、

を特徴とする請求項1〜6のいずれか1つに記載の電子機器。 - 前記絶縁部は、ソルダーレジストにより被覆されていること、

を特徴とする請求項1〜8のいずれか1つに記載の電子機器。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010191766A JP5259659B2 (ja) | 2010-08-30 | 2010-08-30 | 電子機器 |

| US13/041,820 US8581616B2 (en) | 2010-08-30 | 2011-03-07 | Electronic device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010191766A JP5259659B2 (ja) | 2010-08-30 | 2010-08-30 | 電子機器 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013031017A Division JP5450852B2 (ja) | 2013-02-20 | 2013-02-20 | 電子機器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2012049418A JP2012049418A (ja) | 2012-03-08 |

| JP5259659B2 true JP5259659B2 (ja) | 2013-08-07 |

Family

ID=45696311

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010191766A Expired - Fee Related JP5259659B2 (ja) | 2010-08-30 | 2010-08-30 | 電子機器 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8581616B2 (ja) |

| JP (1) | JP5259659B2 (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5894515B2 (ja) * | 2012-09-28 | 2016-03-30 | 株式会社東芝 | 半導体装置、寿命推定装置、寿命推定方法 |

| JP6076208B2 (ja) * | 2013-06-21 | 2017-02-08 | 株式会社日本マイクロニクス | 配線基板の検査装置および配線基板の検査方法 |

| JP6235415B2 (ja) * | 2014-06-10 | 2017-11-22 | アルプス電気株式会社 | 湿度検知装置 |

| JP6532726B2 (ja) * | 2015-03-27 | 2019-06-19 | 株式会社東芝 | 電子機器、異常判定方法、およびプログラム |

| US20190011497A1 (en) * | 2017-07-09 | 2019-01-10 | Texas Instruments Incorporated | Test Fixture with Sintered Connections Between Mother Board and Daughter Board |

| EP3716747B1 (en) * | 2017-11-22 | 2023-03-29 | Fuji Corporation | Electronic component mounting machine and electronic component mounting method |

| DE102021209892A1 (de) * | 2021-09-08 | 2023-03-09 | Robert Bosch Gesellschaft mit beschränkter Haftung | Elektronisches Steuergerät und Verfahren zum Überwachen von Lötverbindungen eines elektronischen Steuergeräts |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03265197A (ja) | 1990-03-14 | 1991-11-26 | Kanegafuchi Chem Ind Co Ltd | 電波吸収体 |

| JPH05347473A (ja) | 1992-06-15 | 1993-12-27 | Toshiba Corp | 配線基板 |

| US5786701A (en) * | 1993-07-02 | 1998-07-28 | Mitel Semiconductor Limited | Bare die testing |

| JP2825085B2 (ja) * | 1996-08-29 | 1998-11-18 | 日本電気株式会社 | 半導体装置の実装構造、実装用基板および実装状態の検査方法 |

| JP3265197B2 (ja) | 1996-09-12 | 2002-03-11 | 株式会社東芝 | 半導体装置 |

| US6081429A (en) * | 1999-01-20 | 2000-06-27 | Micron Technology, Inc. | Test interposer for use with ball grid array packages assemblies and ball grid array packages including same and methods |

| JP2003121492A (ja) * | 2001-10-15 | 2003-04-23 | Matsushita Electric Ind Co Ltd | 球面バンプとの接触構造 |

| JP4172238B2 (ja) * | 2002-09-19 | 2008-10-29 | 日本電気株式会社 | 電子部品の実装構造 |

| JP2009257863A (ja) | 2008-04-15 | 2009-11-05 | Ricoh Elemex Corp | 電子回路基板 |

| JP2010093231A (ja) | 2008-09-11 | 2010-04-22 | Yokogawa Electric Corp | 半導体装置の実装構造 |

-

2010

- 2010-08-30 JP JP2010191766A patent/JP5259659B2/ja not_active Expired - Fee Related

-

2011

- 2011-03-07 US US13/041,820 patent/US8581616B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20120049885A1 (en) | 2012-03-01 |

| US8581616B2 (en) | 2013-11-12 |

| JP2012049418A (ja) | 2012-03-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5259659B2 (ja) | 電子機器 | |

| JP4901602B2 (ja) | プリント基板の製造方法及びプリント基板 | |

| CN108225963B (zh) | 基于bga焊点可靠性测试的pcb设计方法 | |

| JP5032213B2 (ja) | 電子機器 | |

| US9277657B2 (en) | Wiring board | |

| JP6466128B2 (ja) | プローブカード | |

| CN103219322A (zh) | 具有电阻测量结构的三维集成电路及其使用方法 | |

| CN101894819B (zh) | 基板结构 | |

| CN101411252A (zh) | 电路板、测试电路板的方法及制造电路板的方法 | |

| JP2016025159A (ja) | 配線基板構造体および配線基板構造体の製造方法 | |

| JP6236841B2 (ja) | 多層配線基板及びその製造方法 | |

| JP5450852B2 (ja) | 電子機器 | |

| WO2013094678A1 (ja) | 電子装置、電源制御システム、および寿命測定ユニット | |

| JP5355149B2 (ja) | 電子機器および、電子機器を用いた電子部品の接続不良検出方法 | |

| JP2009239027A (ja) | 不具合検出機能を備えた半導体装置 | |

| JP2010278212A (ja) | 電子部品用パッケージ、および電子部品用パッケージの異常検出方法 | |

| JP5370250B2 (ja) | 半導体装置の製造方法 | |

| CN103715167A (zh) | 半导体装置、估计寿命的设备和估计寿命的方法 | |

| KR102689407B1 (ko) | 방열성이 개선된 프로브카드용 공간변환부 | |

| KR102469361B1 (ko) | 온도퓨즈의 체결구조 | |

| JP2021185589A (ja) | 配線基板 | |

| CN203038917U (zh) | 芯片侦测单元 | |

| JP2014096506A (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP5540854B2 (ja) | 半導体基板 | |

| JP2011009322A (ja) | パターン引き出し構造体及び半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120817 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120821 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121016 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20121211 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130220 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20130227 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130402 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130424 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160502 Year of fee payment: 3 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5259659 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |