JP5141237B2 - 半導体記憶装置、その製造方法、書き込み方法及び読み出し方法 - Google Patents

半導体記憶装置、その製造方法、書き込み方法及び読み出し方法 Download PDFInfo

- Publication number

- JP5141237B2 JP5141237B2 JP2007330271A JP2007330271A JP5141237B2 JP 5141237 B2 JP5141237 B2 JP 5141237B2 JP 2007330271 A JP2007330271 A JP 2007330271A JP 2007330271 A JP2007330271 A JP 2007330271A JP 5141237 B2 JP5141237 B2 JP 5141237B2

- Authority

- JP

- Japan

- Prior art keywords

- tunnel junction

- magnetic tunnel

- transistor

- bit line

- source

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1659—Cell access

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1673—Reading or sensing circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1675—Writing or programming circuits or methods

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Mram Or Spin Memory Techniques (AREA)

- Hall/Mr Elements (AREA)

Description

トランジスタと、

前記トランジスタのソース・ドレイン拡散層の一方に電気的に接続される第1の磁気トンネル接合素子と、

前記ソース・ドレイン拡散層の他方に電気的に接続される第2の磁気トンネル接合素子と、

を有し、前記第1および第2の磁気トンネル接合素子は、外部から供給される書き込み電流が、前記第1の磁気トンネル接合素子と前記第2の磁気トンネル接合素子において逆方向に流れるように、前記トランジスタに接続される。

互いに隣接し、各々が1つのトランジスタと、前記トランジスタのソース・ドレインの両側に直列に接続される2つの磁気トンネル接合素子と、前記ソース・ドレインのいずれかの側に位置する読み出しノードとを有する第1及び第2のメモリセル、を含み、

前記第1および第2のメモリセルの前記2つの磁気トンネル接合素子の1つに共通に接続される第1のビット線と、

前記第1及び第2のメモリセルの前記読み出しノードに共通に接続される第2のビット線と、

を有する。

互いに隣接し、各々が1つのトランジスタと、前記トランジスタのソース・ドレインの両側に直列に接続される2つの磁気トンネル接合素子と、前記ソース・ドレインのいずれかの側に位置する読み出しノードとを有する第1及び第2のメモリセル、を含み、

前記第1のメモリセルの一方の磁気トンネル接合素子と、前記第2のメモリセルの前記読み出しノードとが接続される第1のビット線と、

前記第2のメモリセルの一方の磁気トンネル接合素子と、前記第1のメモリセルの前記読み出しノードとが接続される第2のビット線と、

を有する。

Vsig=2/7=0.29V

となる。このVsigの電圧を、読出し電圧Vreadの半分の電圧(Vread/2=0.5V)と比較すると、Vsigの方が小さく(Vsig<Vread/2)、データ“0”が書き込まれていたことが検出される。

Vsig=4/7=0.57V

となる。このVsigの電圧を、読出し電圧Vreadの半分の電圧(Vread/2=0.5V)と比較すると、Vsigの方が大きく(Vsig>Vread/2)、データ“1”が書き込まれていたことが検出される。

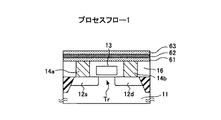

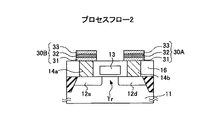

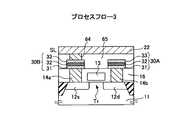

半導体基板に、トランジスタを形成し、

前記トランジスタのソースおよびドレインのそれぞれに達する第1及び第2の接続プラグを同時に形成し、

前記第1及び第2の接続プラグの各々に接続する磁気トンネル接合素子を同一プロセスで一括形成する、

工程を含む。この方法により、相補型の記憶素子を簡単な工程で作製することができる。

トランジスタのソース電極に第1の磁気トンネル接合素子を接続し、

前記トランジスタのドレイン電極に第2の磁気トンネル接合素子を接続してメモリセルを形成し、

前記メモリセルに書き込み電流を印加して、前記第1及び第2の磁気トンネル接合素子の一方を低抵抗状態にし、他方を高抵抗状態にする、

工程を含む。

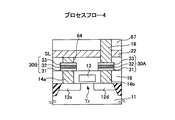

トランジスタのソース電極に第1の磁気トンネル接合素子を接続し、

前記トランジスタのドレイン電極に第2の磁気トンネル接合素子を接続してメモリセルを形成し、

前記第1の磁気トンネル接合素子と、前記第2の磁気トンネル接合素子の間に読み出し電圧を印加し、前記トランジスタと、前記第1又は第2の磁気トンネル接合素子との間の接続ノードの電位を検出し、

前記検出した電位を、前記読み出し電圧の1/2の参照電位と比較して、前記メモリセルの状態を検出する、

工程を含む。

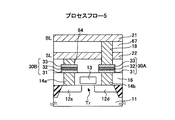

11 半導体基板

12 ソース・ドレイン拡散層

13 ワード線

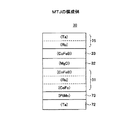

30、30A、30B MTJ(磁気トンネル接合素子)

31 ピンド層

32 トンネルバリア層

33 フリー層

21 ビット線(BL)

22 ソース線(SL)

Tr トランジスタ

ReadBL

読み出し専用ビット線

Claims (6)

- トランジスタのソース・ドレインの両側に、書き込み電流印加時に相補的な抵抗状態をとる2つの磁気トンネル接合素子が直列に接続され、

前記トランジスタの一方の側に接続される磁気トンネル接合素子は、ビット線方向に隣接するセルの読み出しノードに接続される第1ビット線に接続され、前記トランジスタの他方の側に配置される読み出しノードは、前記隣接するセルの磁気トンネル接合素子のひとつに接続される第2ビット線に接続されている半導体記憶装置。 - トランジスタと、

前記トランジスタのソース・ドレイン拡散層の一方に電気的に接続される第1の磁気トンネル接合素子と、

前記ソース・ドレイン拡散層の他方に電気的に接続される第2の磁気トンネル接合素子と、

前記第1の磁気トンネル接合素子に接続される第1ビット線と、

前記第2の磁気トンネル接合素子と前記トランジスタの間で、前記第1及び第2の磁気トンネル接合素子の抵抗状態を検出する読み出しノードと、

前記読み出しノードに接続される第2ビット線と、

を有し、

前記第1ビット線は、当該第1ビット線方向に隣接するセルの読み出しノードに接続され、

前記第1および第2の磁気トンネル接合素子は、外部から供給される書き込み電流が、前記第1の磁気トンネル接合素子と前記第2の磁気トンネル接合素子において逆方向に流れるように、前記トランジスタに接続されることを特徴とする半導体記憶装置。 - 前記書き込み電流により、前記第1及び第2の磁気トンネル接合素子の一方を低抵抗状態にし、他方を高抵抗状態にすることを特徴とする請求項2に記載の半導体記憶装置。

- 前記第2の磁気トンネル接合素子に接続されるソース線、

をさらに有することを特徴とする請求項2又は3に記載の半導体記憶装置。 - 前記第1及び第2の磁気トンネル接合素子は、磁化の方向が固定される第1の強磁性層と、磁化の方向が可変の第2の強磁性層と、前記第1および第2の強磁性層の間に挿入される絶縁層とを有することを特徴とする請求項2〜4のいずれか1項に記載の半導体記憶装置。

- 複数のメモリセルの配列を有する半導体記憶装置において、

互いに隣接し、各々が1つのトランジスタと、前記トランジスタのソース・ドレインの両側に直列に接続される2つの磁気トンネル接合素子と、前記ソース・ドレインのいずれかの側に位置する読み出しノードとを有する第1及び第2のメモリセル、を含み、

前記第1のメモリセルの一方の磁気トンネル接合素子と、前記第2のメモリセルの前記読み出しノードとが接続される第1のビット線と、

前記第2のメモリセルの一方の磁気トンネル接合素子と、前記第1のメモリセルの前記読み出しノードとが接続される第2のビット線と、

を有することを特徴とする半導体記憶装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007330271A JP5141237B2 (ja) | 2007-12-21 | 2007-12-21 | 半導体記憶装置、その製造方法、書き込み方法及び読み出し方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007330271A JP5141237B2 (ja) | 2007-12-21 | 2007-12-21 | 半導体記憶装置、その製造方法、書き込み方法及び読み出し方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009151885A JP2009151885A (ja) | 2009-07-09 |

| JP5141237B2 true JP5141237B2 (ja) | 2013-02-13 |

Family

ID=40920842

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007330271A Expired - Fee Related JP5141237B2 (ja) | 2007-12-21 | 2007-12-21 | 半導体記憶装置、その製造方法、書き込み方法及び読み出し方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5141237B2 (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5238430B2 (ja) * | 2008-09-25 | 2013-07-17 | 株式会社東芝 | 記憶装置 |

| JP5032611B2 (ja) | 2010-02-19 | 2012-09-26 | 株式会社東芝 | 半導体集積回路 |

| JP5664112B2 (ja) * | 2010-10-18 | 2015-02-04 | 富士通株式会社 | メモリセル、半導体メモリおよびシステム |

| JP5551129B2 (ja) * | 2011-09-07 | 2014-07-16 | 株式会社東芝 | 記憶装置 |

| JP2013058521A (ja) * | 2011-09-07 | 2013-03-28 | Toshiba Corp | 記憶装置及びその製造方法 |

| JP5444414B2 (ja) | 2012-06-04 | 2014-03-19 | 株式会社東芝 | 磁気ランダムアクセスメモリ |

| KR102235043B1 (ko) | 2014-06-09 | 2021-04-05 | 삼성전자주식회사 | 반도체 메모리 장치 |

| WO2019171872A1 (ja) * | 2018-03-06 | 2019-09-12 | ソニーセミコンダクタソリューションズ株式会社 | 半導体装置および撮像装置 |

| US11545202B2 (en) * | 2021-04-30 | 2023-01-03 | Taiwan Semiconductor Manufacturing Company, Ltd. | Circuit design and layout with high embedded memory density |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3873055B2 (ja) * | 2002-12-27 | 2007-01-24 | 株式会社東芝 | 半導体記憶装置 |

| US7289356B2 (en) * | 2005-06-08 | 2007-10-30 | Grandis, Inc. | Fast magnetic memory devices utilizing spin transfer and magnetic elements used therein |

-

2007

- 2007-12-21 JP JP2007330271A patent/JP5141237B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009151885A (ja) | 2009-07-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5233234B2 (ja) | 半導体装置およびその製造方法 | |

| JP5141237B2 (ja) | 半導体記憶装置、その製造方法、書き込み方法及び読み出し方法 | |

| JP4149647B2 (ja) | 半導体記憶装置及びその製造方法 | |

| CN102629659B (zh) | 半导体器件 | |

| US6909129B2 (en) | Magnetic random access memory | |

| US7382643B2 (en) | Magnetoresistive effect element and magnetic memory device | |

| US6657270B2 (en) | Magnetic random access memory using bipolar junction transistor, and method for fabricating the same | |

| JP2006185477A (ja) | 磁気メモリ装置並びにその読み出し方法及び書き込み方法 | |

| US20140301135A1 (en) | Mram having novelself-referenced read method | |

| KR100542849B1 (ko) | 자기 기억 장치, 그 제조 방법 및 자기 기억 장치의 데이터 판독 방법 | |

| JP5990130B2 (ja) | 半導体記憶装置 | |

| US6788570B2 (en) | Magnetic random access memory | |

| KR100951068B1 (ko) | 자기 기억 장치 및 그 제조 방법 | |

| WO2006095389A1 (ja) | 磁気メモリ装置並びにその読み出し方法及び書き込み方法 | |

| JP2006210396A (ja) | 磁気メモリ装置及びその読み出し方法 | |

| JP4408901B2 (ja) | 磁気メモリ装置及びその読み出し方法 | |

| JP4572102B2 (ja) | 状態の切り換えを容易化するための加熱式mramセル | |

| JP4415745B2 (ja) | 固体メモリ装置 | |

| JP2005340300A (ja) | 磁気メモリ装置及びその製造方法 | |

| JP2009218318A (ja) | 半導体記憶装置及びその製造方法 | |

| US7177179B2 (en) | Magnetic memory, and its operating method | |

| JP4744532B2 (ja) | 磁気メモリ装置及びその書き込み方法 | |

| KR100979350B1 (ko) | 마그네틱 램 및 그 제조 방법 | |

| US7366010B2 (en) | Magnetic memory | |

| JP3896072B2 (ja) | 磁気記憶装置及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100820 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120723 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120731 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120927 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121023 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121105 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151130 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |