JP5117791B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP5117791B2 JP5117791B2 JP2007216217A JP2007216217A JP5117791B2 JP 5117791 B2 JP5117791 B2 JP 5117791B2 JP 2007216217 A JP2007216217 A JP 2007216217A JP 2007216217 A JP2007216217 A JP 2007216217A JP 5117791 B2 JP5117791 B2 JP 5117791B2

- Authority

- JP

- Japan

- Prior art keywords

- metal layer

- seal ring

- film

- insulating film

- semiconductor device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

- H01L21/76807—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics for dual damascene structures

- H01L21/76811—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics for dual damascene structures involving multiple stacked pre-patterned masks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/58—Structural electrical arrangements for semiconductor devices not otherwise provided for, e.g. in combination with batteries

- H01L23/585—Structural electrical arrangements for semiconductor devices not otherwise provided for, e.g. in combination with batteries comprising conductive layers or plates or strips or rods or rings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

- H01L21/76807—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics for dual damascene structures

- H01L21/76808—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics for dual damascene structures involving intermediate temporary filling with material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Semiconductor Integrated Circuits (AREA)

Description

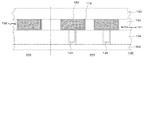

基板と、

前記基板上に形成され、ビアおよび配線が形成される素子形成領域と、

前記基板上に形成され、平面視において前記素子形成領域を囲むように当該素子形成領域の外周に形成されたシールリングと、

を含み、

前記シールリングは、平面視において前記素子形成領域を囲むように形成された貫通孔を有する第1のメタル層と、前記第1のメタル層上に当該第1のメタル層に接して形成された第2のメタル層と、を含み、

前記第1のメタル層の前記貫通孔の下部分には絶縁性材料が形成され、当該貫通孔の前記絶縁性材料が形成された箇所以外の上部分には前記第2のメタル層を構成するメタル材料がくい込んで形成された半導体装置が提供される。

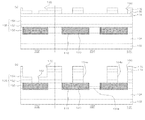

素子形成領域と、当該素子形成領域を囲むように当該素子形成領域の外周に形成されたシールリング部と、を含む半導体装置の製造方法であって、

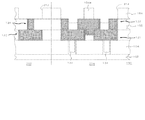

基板上に形成された第1の絶縁膜に、前記素子形成領域においてビアまたは配線を形成するための第1の溝、および前記シールリング部において平面視で前記素子形成領域を取り囲むように第1のシールリング溝を形成する工程と、

前記第1の溝および前記第1のシールリング溝をメタル材料で埋め込み、次いで前記第1の溝および前記第1のシールリング溝外部に露出した前記メタル材料を除去することにより、前記第1の溝内にビアまたは配線を形成するとともに、前記第1のシールリング溝内に第1のメタル層を形成する工程と、

前記第1の絶縁膜上に第2の絶縁膜を形成する工程と、

前記第2の絶縁膜に、前記素子形成領域においてビアまたは配線を形成するための第2の溝、および前記シールリング部において前記第1のシールリング溝上に第2のシールリング溝を形成する工程と、

前記第2の溝および前記第2のシールリング溝をメタル材料で埋め込み、次いで前記第2の溝および前記第2のシールリング溝外部に露出した前記メタル材料を除去することにより、前記第2の溝内にビアまたは配線を形成するとともに、前記第2のシールリング溝内に、前記第1のメタル層に接する第2のメタル層を形成する工程と、

を含み、

前記第1のシールリング溝を形成する工程において、当該第1のシールリング溝は、当該第1のシールリング溝内に、前記第1の絶縁膜を残して形成され、

前記第1のシールリング溝内に第1のメタル層を形成する工程において、前記第1のシールリング溝に残して形成された前記第1の絶縁膜により、当該第1のメタル層には貫通孔が形成され、

前記第2のシールリング溝を形成する工程において、前記第2のシールリング溝底面に前記第1の絶縁膜が露出した後、当該露出した前記第1の絶縁膜の上部分を除去して、前記第1のメタル層の前記貫通孔の下部分に前記第1の絶縁膜を残し、

前記第2のメタル層を形成する工程において、前記第1のメタル層の前記貫通孔の上部分に、当該第2のメタル層をくい込ませる半導体装置の製造方法が提供される。

なお、本発明は、以下の構成を適用することも可能である。

(1)

基板と、

前記基板上に形成され、ビアおよび配線が形成される素子形成領域と、

前記基板上に形成され、平面視において前記素子形成領域を囲むように当該素子形成領域の外周に形成されたシールリングと、

を含み、

前記シールリングは、平面視において前記素子形成領域を囲むように形成された貫通孔を有する第1のメタル層と、前記第1のメタル層上に当該第1のメタル層に接して形成された第2のメタル層と、を含み、

前記第1のメタル層の前記貫通孔の下部分には絶縁性材料が形成され、当該貫通孔の前記絶縁性材料が形成された箇所以外の上部分には前記第2のメタル層を構成するメタル材料がくい込んで形成された半導体装置。

(2)

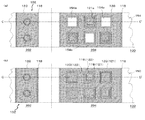

(1)に記載の半導体装置において、

前記第1のメタル層の前記貫通孔は、平面視で複数の貫通孔が前記素子形成領域を囲むように分散配置されることにより構成され、前記複数の貫通孔の下部分にはそれぞれ前記絶縁性材料が形成され、当該複数の貫通孔の前記絶縁性材料が形成された箇所以外の上部分には、それぞれ前記第2のメタル層がくい込んで形成された半導体装置。

(3)

(2)に記載の半導体装置において、

前記第1のメタル層の前記複数の貫通孔は、平面視において格子状に配置された半導体装置。

(4)

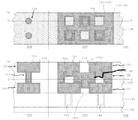

(1)から(3)いずれかに記載の半導体装置において、

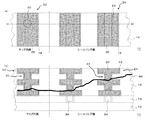

前記シールリングは前記第2のメタル層上に、当該第2のメタル層に接して形成された第3のメタル層をさらに含み、

前記第2のメタル層は、平面視において前記第1のメタル層の前記貫通孔とは重ならない位置において、前記素子形成領域を囲むように形成された貫通孔を有し、当該貫通孔の下部分には絶縁性材料が形成され、当該貫通孔の前記絶縁性材料が形成された箇所以外の上部分には前記第3のメタル層を構成するメタル材料がくい込んで形成された半導体装置。

(5)

(4)に記載の半導体装置において、

前記第2のメタル層の前記貫通孔は、平面視で複数の貫通孔が前記素子形成領域を囲むように分散配置されることにより構成され、前記複数の貫通孔の下部分にはそれぞれ前記絶縁性材料が形成され、当該複数の貫通孔の前記絶縁性材料が形成された箇所以外の上部分には、それぞれ前記第3のメタル層がくい込んで形成された半導体装置。

(6)

(5)に記載の半導体装置において、

前記第2のメタル層の前記複数の貫通孔は、平面視において格子状に配置された半導体装置。

(7)

(4)から(6)いずれかに記載の半導体装置において、

前記シールリングは、前記第1のメタル層下に、当該第1のメタル層に接して形成された下層メタル層をさらに含み、

前記シールリングは、内周から外周に延在する直線で切断した断面において、前記下層メタル層、前記第1のメタル層、前記第2のメタル層、および前記第3のメタル層をそれぞれ構成するメタル材料中に前記絶縁性材料が島状に分散配置された構造を有する半導体装置。

(8)

(4)から(7)いずれかに記載の半導体装置において、

前記シールリングは、内周から外周に延在する直線で切断した断面において、内周から外周の方向に、前記第1のメタル層の前記貫通孔が形成された列と前記第2のメタル層の前記貫通孔が形成された列とが交互に配置された半導体装置。

(9)

素子形成領域と、当該素子形成領域を囲むように当該素子形成領域の外周に形成されたシールリング部と、を含む半導体装置の製造方法であって、

基板上に形成された第1の絶縁膜に、前記素子形成領域においてビアまたは配線を形成するための第1の溝、および前記シールリング部において平面視で前記素子形成領域を取り囲むように第1のシールリング溝を形成する工程と、

前記第1の溝および前記第1のシールリング溝をメタル材料で埋め込み、次いで前記第1の溝および前記第1のシールリング溝外部に露出した前記メタル材料を除去することにより、前記第1の溝内にビアまたは配線を形成するとともに、前記第1のシールリング溝内に第1のメタル層を形成する工程と、

前記第1の絶縁膜上に第2の絶縁膜を形成する工程と、

前記第2の絶縁膜に、前記素子形成領域においてビアまたは配線を形成するための第2の溝、および前記シールリング部において前記第1のシールリング溝上に第2のシールリング溝を形成する工程と、

前記第2の溝および前記第2のシールリング溝をメタル材料で埋め込み、次いで前記第2の溝および前記第2のシールリング溝外部に露出した前記メタル材料を除去することにより、前記第2の溝内にビアまたは配線を形成するとともに、前記第2のシールリング溝内に、前記第1のメタル層に接する第2のメタル層を形成する工程と、

を含み、

前記第1のシールリング溝を形成する工程において、当該第1のシールリング溝は、当該第1のシールリング溝内に、前記第1の絶縁膜を残して形成され、

前記第1のシールリング溝内に第1のメタル層を形成する工程において、前記第1のシールリング溝に残して形成された前記第1の絶縁膜により、当該第1のメタル層には貫通孔が形成され、

前記第2のシールリング溝を形成する工程において、前記第2のシールリング溝底面に前記第1の絶縁膜が露出した後、当該露出した前記第1の絶縁膜の上部分を除去して、前記第1のメタル層の前記貫通孔の下部分に前記第1の絶縁膜を残し、

前記第2のメタル層を形成する工程において、前記第1のメタル層の前記貫通孔の上部分に、当該第2のメタル層をくい込ませる半導体装置の製造方法。

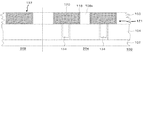

(10)

(9)に記載の半導体装置の製造方法において、

前記第1のシールリング溝を形成する工程において、当該第1のシールリング溝は、当該第1のシールリング溝内に、平面視で前記素子形成領域を取り囲むように前記第1の絶縁膜が島状に分散配置されるように当該第1の絶縁膜を残して形成され、

前記第1のシールリング溝内に第1のメタル層を形成する工程において、前記第1のシールリング溝に残して形成された前記第1の絶縁膜により、当該第1のメタル層には複数の貫通孔が形成される半導体装置の製造方法。

(11)

(9)または(10)に記載の半導体装置の製造方法において、

前記第2の絶縁膜上に第3の絶縁膜を形成する工程と、

前記第3の絶縁膜に、前記素子形成領域においてビアまたは配線を形成するための第3の溝、および前記シールリング部において前記第2のシールリング溝上に第3のシールリング溝を形成する工程と、

前記第3の溝および前記第3のシールリング溝をメタル材料で埋め込み、次いで前記第3の溝および前記第3のシールリング溝外部に露出した前記メタル材料を除去することにより、前記第3の溝内にビアまたは配線を形成するとともに、前記第3のシールリング溝内に、前記第2のメタル層に接する第3のメタル層を形成する工程と、

をさらに含み、

前記第2のシールリング溝を形成する工程において、当該第2のシールリング溝は、当該第2のシールリング溝内に、平面視で前記第1のメタル層の前記貫通孔とは重ならない位置において、前記素子形成領域を取り囲むように当該第2の絶縁膜を残して形成され、

前記第2のシールリング溝内に第2のメタル層を形成する工程において、前記第2のシールリング溝に残して形成された前記第2の絶縁膜により、当該第2のメタル層には貫通孔が形成され、

前記第3のシールリング溝を形成する工程において、前記第3のシールリング溝底面に前記第2の絶縁膜が露出した後、当該露出した前記第2の絶縁膜の上部分を除去して、前記第2のメタル層の前記貫通孔の下部分に前記第2の絶縁膜を残し、

前記第3のメタル層を形成する工程において、前記第2のメタル層の前記貫通孔の上部分に、当該第3のメタル層をくい込ませる半導体装置の製造方法。

(12)

(11)に記載の半導体装置の製造方法において、

前記第2のシールリング溝を形成する工程において、当該第2のシールリング溝は、当該第2のシールリング溝内に、平面視で前記素子形成領域を取り囲むように前記第2の絶縁膜が島状に分散配置されるように当該第2の絶縁膜を残して形成され、

前記第2のシールリング溝内に第2のメタル層を形成する工程において、前記第2のシールリング溝に残して形成された前記第2の絶縁膜により、当該第2のメタル層には複数の貫通孔が形成される半導体装置の製造方法。

102 基板

104 下層絶縁膜

106 層間絶縁膜

118 バリアメタル膜

120 銅含有メタル膜

121 下層メタル層

121a 貫通孔

122 第1のメタル層

122a 貫通孔

124 第2のメタル層

124a 貫通孔

130 ビア層

132 配線層

134 Wシールリング

140 クラックや膜剥離

150 第1の層間絶縁膜

150a 島状絶縁膜

152 第2の層間絶縁膜

152a 島状絶縁膜

152’ 層間絶縁膜

154 第3の層間絶縁膜

154a 島状絶縁膜

154’ 層間絶縁膜

156 反射防止膜

156’ 反射防止膜

158 レジスト膜

158a パターン

158b パターン

158c 部分

158d 部分

158’ レジスト膜

158’a パターン

158’b パターン

158’c 部分

160 シールリング溝

162 ビアホール

164 下層レジスト膜

166 低温酸化膜

168 反射防止膜

170 上層レジスト膜

170a パターン

172 配線溝

174 第1のハードマスク

176 第2のハードマスク

178 第3のハードマスク

180 反射防止膜

182 レジスト膜

182a パターン

182b パターン

182c 部分

182d 部分

183 反射防止膜

184 レジスト膜

184a パターン

190 配線溝

192 シールリング溝

194 ビアホールパターン

196 開口部

198 配線溝パターン

202 チップ内部

203 チップ

204 シールリング部

206 ダイシングライン

208 アライメントマーク

300 反射防止膜

302 レジスト膜

302a パターン

302b パターン

302c 部分

302d 部分

304 ビアホール

306 シールリング溝

308 反射防止膜

310 レジスト膜

310a パターン

310b パターン

310c 部分

312 配線溝

314 シールリング溝

Claims (9)

- 基板と、

前記基板上に形成され、ビアおよび配線が形成される素子形成領域と、

前記基板上に形成され、平面視において前記素子形成領域を囲むように当該素子形成領域の外周に形成されたシールリングと、

を含み、

前記シールリングは、平面視において前記素子形成領域を囲むように形成された貫通孔を有する第1のメタル層と、前記第1のメタル層上に当該第1のメタル層に接して形成された第2のメタル層と、を含み、

前記第1のメタル層の前記貫通孔の下部分には絶縁性材料が形成され、当該貫通孔の前記絶縁性材料が形成された箇所以外の上部分には前記第2のメタル層を構成するメタル材料がくい込んで形成され、

前記第1のメタル層の前記貫通孔は、平面視で複数の貫通孔が前記素子形成領域を囲むように分散配置されることにより構成され、前記複数の貫通孔の下部分にはそれぞれ前記絶縁性材料が形成され、当該複数の貫通孔の前記絶縁性材料が形成された箇所以外の上部分には、それぞれ前記第2のメタル層がくい込んで形成された半導体装置。 - 基板と、

前記基板上に形成され、ビアおよび配線が形成される素子形成領域と、

前記基板上に形成され、平面視において前記素子形成領域を囲むように当該素子形成領域の外周に形成されたシールリングと、

を含み、

前記シールリングは、平面視において前記素子形成領域を囲むように形成された貫通孔を有する第1のメタル層と、前記第1のメタル層上に当該第1のメタル層に接して形成された第2のメタル層と、を含み、

前記第1のメタル層の前記貫通孔の下部分には絶縁性材料が形成され、当該貫通孔の前記絶縁性材料が形成された箇所以外の上部分には前記第2のメタル層を構成するメタル材料がくい込んで形成され、

前記シールリングは前記第2のメタル層上に、当該第2のメタル層に接して形成された第3のメタル層をさらに含み、

前記第2のメタル層は、平面視において前記第1のメタル層の前記貫通孔とは重ならない位置において、前記素子形成領域を囲むように形成された貫通孔を有し、当該貫通孔の下部分には絶縁性材料が形成され、当該貫通孔の前記絶縁性材料が形成された箇所以外の上部分には前記第3のメタル層を構成するメタル材料がくい込んで形成され、

前記第2のメタル層の前記貫通孔は、平面視で複数の貫通孔が前記素子形成領域を囲むように分散配置されることにより構成され、前記複数の貫通孔の下部分にはそれぞれ前記絶縁性材料が形成され、当該複数の貫通孔の前記絶縁性材料が形成された箇所以外の上部分には、それぞれ前記第3のメタル層がくい込んで形成された半導体装置。 - 基板と、

前記基板上に形成され、ビアおよび配線が形成される素子形成領域と、

前記基板上に形成され、平面視において前記素子形成領域を囲むように当該素子形成領域の外周に形成されたシールリングと、

を含み、

前記シールリングは、平面視において前記素子形成領域を囲むように形成された貫通孔を有する第1のメタル層と、前記第1のメタル層上に当該第1のメタル層に接して形成された第2のメタル層と、を含み、

前記第1のメタル層の前記貫通孔の下部分には絶縁性材料が形成され、当該貫通孔の前記絶縁性材料が形成された箇所以外の上部分には前記第2のメタル層を構成するメタル材料がくい込んで形成され、

前記シールリングは前記第2のメタル層上に、当該第2のメタル層に接して形成された第3のメタル層をさらに含み、

前記第2のメタル層は、平面視において前記第1のメタル層の前記貫通孔とは重ならない位置において、前記素子形成領域を囲むように形成された貫通孔を有し、当該貫通孔の下部分には絶縁性材料が形成され、当該貫通孔の前記絶縁性材料が形成された箇所以外の上部分には前記第3のメタル層を構成するメタル材料がくい込んで形成され、

前記シールリングは、前記第1のメタル層下に、当該第1のメタル層に接して形成された下層メタル層をさらに含み、

前記シールリングは、内周から外周に延在する直線で切断した断面において、前記下層メタル層、前記第1のメタル層、前記第2のメタル層、および前記第3のメタル層をそれぞれ構成するメタル材料中に前記絶縁性材料が島状に分散配置された構造を有する半導体装置。 - 請求項2または3に記載の半導体装置において、

前記第1のメタル層の前記貫通孔は、平面視で複数の貫通孔が前記素子形成領域を囲むように分散配置されることにより構成され、前記複数の貫通孔の下部分にはそれぞれ前記絶縁性材料が形成され、当該複数の貫通孔の前記絶縁性材料が形成された箇所以外の上部分には、それぞれ前記第2のメタル層がくい込んで形成された半導体装置。 - 請求項1、請求項2に従属する請求項4、請求項3に従属する請求項4いずれかに記載の半導体装置において、

前記第1のメタル層の前記複数の貫通孔は、平面視において格子状に配置された半導体装置。 - 請求項1または請求項1に従属する請求項5に記載の半導体装置において、

前記シールリングは前記第2のメタル層上に、当該第2のメタル層に接して形成された第3のメタル層をさらに含み、

前記第2のメタル層は、平面視において前記第1のメタル層の前記貫通孔とは重ならない位置において、前記素子形成領域を囲むように形成された貫通孔を有し、当該貫通孔の下部分には絶縁性材料が形成され、当該貫通孔の前記絶縁性材料が形成された箇所以外の上部分には前記第3のメタル層を構成するメタル材料がくい込んで形成された半導体装置。 - 請求項2、請求項2に従属する請求項4、請求項2に従属する請求項4に従属する請求項5いずれかに記載の半導体装置において、

前記第2のメタル層の前記複数の貫通孔は、平面視において格子状に配置された半導体装置。 - 請求項2、7、請求項2に従属する請求項4、請求項2に従属する請求項4に従属する請求項5いずれかに記載の半導体装置において、

前記シールリングは、前記第1のメタル層下に、当該第1のメタル層に接して形成された下層メタル層をさらに含み、

前記シールリングは、内周から外周に延在する直線で切断した断面において、前記下層メタル層、前記第1のメタル層、前記第2のメタル層、および前記第3のメタル層をそれぞれ構成するメタル材料中に前記絶縁性材料が島状に分散配置された構造を有する半導体装置。 - 請求項2から4、6から8、請求項2に従属する請求項4に従属する請求項5、請求項3に従属する請求項4に従属する請求項5いずれかに記載の半導体装置において、

前記シールリングは、内周から外周に延在する直線で切断した断面において、内周から外周の方向に、前記第1のメタル層の前記貫通孔が形成された列と前記第2のメタル層の前記貫通孔が形成された列とが交互に配置された半導体装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007216217A JP5117791B2 (ja) | 2007-08-22 | 2007-08-22 | 半導体装置 |

| US12/219,527 US8039963B2 (en) | 2007-08-22 | 2008-07-23 | Semiconductor device having seal ring structure |

| TW097129661A TWI398913B (zh) | 2007-08-22 | 2008-08-05 | 具有密封環結構之半導體裝置及其製造方法 |

| CN200810144560.9A CN101373742B (zh) | 2007-08-22 | 2008-08-22 | 具有密封环结构的半导体器件及其形成方法 |

| US13/137,847 US8617914B2 (en) | 2007-08-22 | 2011-09-16 | Method of forming semiconductor device having seal ring structure |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007216217A JP5117791B2 (ja) | 2007-08-22 | 2007-08-22 | 半導体装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012173758A Division JP5504311B2 (ja) | 2012-08-06 | 2012-08-06 | 半導体装置およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009049313A JP2009049313A (ja) | 2009-03-05 |

| JP5117791B2 true JP5117791B2 (ja) | 2013-01-16 |

Family

ID=40381389

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007216217A Active JP5117791B2 (ja) | 2007-08-22 | 2007-08-22 | 半導体装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US8039963B2 (ja) |

| JP (1) | JP5117791B2 (ja) |

| CN (1) | CN101373742B (ja) |

| TW (1) | TWI398913B (ja) |

Families Citing this family (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8434220B2 (en) | 2007-06-27 | 2013-05-07 | Rf Micro Devices, Inc. | Heat sink formed with conformal shield |

| US8959762B2 (en) | 2005-08-08 | 2015-02-24 | Rf Micro Devices, Inc. | Method of manufacturing an electronic module |

| US20080265445A1 (en) * | 2007-04-30 | 2008-10-30 | International Business Machines Corporation | Marks for the Alignment of Wafer-Level Underfilled Silicon Chips and Method to Produce Same |

| JP2009259967A (ja) * | 2008-04-15 | 2009-11-05 | Nec Corp | 配線構造、半導体装置及び半導体装置の製造方法 |

| US8227708B2 (en) * | 2009-12-14 | 2012-07-24 | Qualcomm Incorporated | Via structure integrated in electronic substrate |

| US8304863B2 (en) * | 2010-02-09 | 2012-11-06 | International Business Machines Corporation | Electromigration immune through-substrate vias |

| US9137934B2 (en) | 2010-08-18 | 2015-09-15 | Rf Micro Devices, Inc. | Compartmentalized shielding of selected components |

| US8835226B2 (en) | 2011-02-25 | 2014-09-16 | Rf Micro Devices, Inc. | Connection using conductive vias |

| US9627230B2 (en) | 2011-02-28 | 2017-04-18 | Qorvo Us, Inc. | Methods of forming a microshield on standard QFN package |

| CN102853081B (zh) * | 2011-06-29 | 2015-07-15 | 麦丰密封科技股份有限公司 | 一种用于半导体制造设备中的密封环 |

| US9807890B2 (en) | 2013-05-31 | 2017-10-31 | Qorvo Us, Inc. | Electronic modules having grounded electromagnetic shields |

| JP6212720B2 (ja) * | 2013-09-20 | 2017-10-18 | パナソニックIpマネジメント株式会社 | 半導体装置及びその製造方法 |

| CN105336710B (zh) * | 2014-07-10 | 2018-03-23 | 中芯国际集成电路制造(上海)有限公司 | 一种芯片的密封环 |

| CN105448857B (zh) * | 2014-09-02 | 2018-04-17 | 中芯国际集成电路制造(上海)有限公司 | 一种芯片密封环结构及其制作方法 |

| US10014234B2 (en) | 2016-12-02 | 2018-07-03 | Globalfoundries Inc. | Semiconductor device comprising a die seal including long via lines |

| US10490513B2 (en) | 2018-03-28 | 2019-11-26 | International Business Machines Corporation | Advanced crack stop structure |

| JP7367669B2 (ja) * | 2018-04-02 | 2023-10-24 | 株式会社ソシオネクスト | 半導体装置 |

| US11127689B2 (en) | 2018-06-01 | 2021-09-21 | Qorvo Us, Inc. | Segmented shielding using wirebonds |

| US11219144B2 (en) | 2018-06-28 | 2022-01-04 | Qorvo Us, Inc. | Electromagnetic shields for sub-modules |

| US11114363B2 (en) | 2018-12-20 | 2021-09-07 | Qorvo Us, Inc. | Electronic package arrangements and related methods |

| US11515282B2 (en) | 2019-05-21 | 2022-11-29 | Qorvo Us, Inc. | Electromagnetic shields with bonding wires for sub-modules |

| CN111162058A (zh) * | 2020-02-24 | 2020-05-15 | 杭州立昂东芯微电子有限公司 | 一种砷化镓器件金属保护环 |

| CN111564411B (zh) * | 2020-06-08 | 2022-12-23 | 深圳铨力半导体有限公司 | 一种半导体装置及其形成方法 |

| CN113053828B (zh) * | 2021-03-12 | 2022-05-27 | 长鑫存储技术有限公司 | 密封环及其形成方法 |

| CN115084039B (zh) * | 2021-03-12 | 2023-06-27 | 长鑫存储技术有限公司 | 保护环结构、半导体结构及其制造方法 |

| US12482753B2 (en) * | 2022-03-23 | 2025-11-25 | Taiwan Semiconductor Manufacturing Company Limited | Semiconductor device having redistribution layers formed on an active wafer and methods of making the same |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5861670A (en) * | 1979-10-04 | 1999-01-19 | Fujitsu Limited | Semiconductor device package |

| JPH11354637A (ja) * | 1998-06-11 | 1999-12-24 | Oki Electric Ind Co Ltd | 配線の接続構造及び配線の接続部の形成方法 |

| JP4250006B2 (ja) * | 2002-06-06 | 2009-04-08 | 富士通マイクロエレクトロニクス株式会社 | 半導体装置及びその製造方法 |

| JP4360881B2 (ja) * | 2003-03-24 | 2009-11-11 | Necエレクトロニクス株式会社 | 多層配線を含む半導体装置およびその製造方法 |

| JP2004363376A (ja) * | 2003-06-05 | 2004-12-24 | Renesas Technology Corp | 配線及びビアプラグ間の接続構造、及び配線及びビアプラグ間の接続構造を有する半導体装置の製造方法 |

| JP4041785B2 (ja) * | 2003-09-26 | 2008-01-30 | 松下電器産業株式会社 | 半導体装置の製造方法 |

| JP3962402B2 (ja) | 2003-11-10 | 2007-08-22 | 松下電器産業株式会社 | 半導体装置 |

| JP4280204B2 (ja) | 2004-06-15 | 2009-06-17 | Okiセミコンダクタ株式会社 | 半導体装置 |

| JP4382687B2 (ja) * | 2005-03-22 | 2009-12-16 | パナソニック株式会社 | 半導体装置およびその製造方法 |

| CN100481455C (zh) * | 2005-12-22 | 2009-04-22 | 中芯国际集成电路制造(上海)有限公司 | 具有不全接触通孔栈的密封环结构 |

-

2007

- 2007-08-22 JP JP2007216217A patent/JP5117791B2/ja active Active

-

2008

- 2008-07-23 US US12/219,527 patent/US8039963B2/en not_active Expired - Fee Related

- 2008-08-05 TW TW097129661A patent/TWI398913B/zh not_active IP Right Cessation

- 2008-08-22 CN CN200810144560.9A patent/CN101373742B/zh not_active Expired - Fee Related

-

2011

- 2011-09-16 US US13/137,847 patent/US8617914B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US8617914B2 (en) | 2013-12-31 |

| CN101373742B (zh) | 2011-12-14 |

| US20120009789A1 (en) | 2012-01-12 |

| CN101373742A (zh) | 2009-02-25 |

| TWI398913B (zh) | 2013-06-11 |

| TW200926279A (en) | 2009-06-16 |

| US8039963B2 (en) | 2011-10-18 |

| JP2009049313A (ja) | 2009-03-05 |

| US20090051011A1 (en) | 2009-02-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5117791B2 (ja) | 半導体装置 | |

| US8513776B2 (en) | Semiconductor device and method capable of scribing chips with high yield | |

| JP5235378B2 (ja) | 半導体装置 | |

| JP5175066B2 (ja) | 半導体装置 | |

| JP4401874B2 (ja) | 半導体装置 | |

| CN100355067C (zh) | 半导体器件 | |

| JP5106933B2 (ja) | 半導体装置 | |

| US7714413B2 (en) | Semiconductor device and method of manufacture thereof | |

| JP4360881B2 (ja) | 多層配線を含む半導体装置およびその製造方法 | |

| KR101735912B1 (ko) | 공기 간극 구조를 구비한 반도체 장치 및 그 제조 방법 | |

| US20050093169A1 (en) | Semiconductor device and method of manufacturing semiconductor device | |

| JP4280204B2 (ja) | 半導体装置 | |

| JP4050876B2 (ja) | 半導体集積回路装置とその製造方法 | |

| JP5504311B2 (ja) | 半導体装置およびその製造方法 | |

| US11244911B2 (en) | Chip including a scribe lane | |

| JP5932079B2 (ja) | 半導体装置 | |

| JP5483772B2 (ja) | 半導体装置 | |

| CN111092068B (zh) | 包括对准图案的半导体芯片 | |

| JP5041088B2 (ja) | 半導体装置 | |

| JP4211910B2 (ja) | 半導体装置の製造方法 | |

| JP5801329B2 (ja) | 半導体装置 | |

| JP2010004085A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100514 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120531 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120605 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120806 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121016 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121018 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5117791 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151026 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |