JP4894183B2 - ノイズ除去回路およびこれを用いたマトリックス表示装置、ならびに解像度弁別回路 - Google Patents

ノイズ除去回路およびこれを用いたマトリックス表示装置、ならびに解像度弁別回路 Download PDFInfo

- Publication number

- JP4894183B2 JP4894183B2 JP2005214580A JP2005214580A JP4894183B2 JP 4894183 B2 JP4894183 B2 JP 4894183B2 JP 2005214580 A JP2005214580 A JP 2005214580A JP 2005214580 A JP2005214580 A JP 2005214580A JP 4894183 B2 JP4894183 B2 JP 4894183B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- circuit

- counter

- count

- value

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000011159 matrix material Substances 0.000 title claims description 14

- 238000001514 detection method Methods 0.000 claims description 58

- 230000004913 activation Effects 0.000 claims description 16

- 230000008030 elimination Effects 0.000 claims description 4

- 238000003379 elimination reaction Methods 0.000 claims description 4

- 230000003247 decreasing effect Effects 0.000 claims description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 31

- 230000000630 rising effect Effects 0.000 description 28

- 238000003708 edge detection Methods 0.000 description 15

- 238000010586 diagram Methods 0.000 description 13

- 102000004137 Lysophosphatidic Acid Receptors Human genes 0.000 description 10

- 108090000642 Lysophosphatidic Acid Receptors Proteins 0.000 description 10

- 230000007257 malfunction Effects 0.000 description 10

- 230000003111 delayed effect Effects 0.000 description 9

- 101001021281 Homo sapiens Protein HEXIM1 Proteins 0.000 description 5

- 101000693265 Homo sapiens Sphingosine 1-phosphate receptor 1 Proteins 0.000 description 5

- 102100025750 Sphingosine 1-phosphate receptor 1 Human genes 0.000 description 5

- 238000000034 method Methods 0.000 description 5

- 101000685663 Homo sapiens Sodium/nucleoside cotransporter 1 Proteins 0.000 description 4

- 101000821827 Homo sapiens Sodium/nucleoside cotransporter 2 Proteins 0.000 description 4

- 102100023116 Sodium/nucleoside cotransporter 1 Human genes 0.000 description 4

- 102100021541 Sodium/nucleoside cotransporter 2 Human genes 0.000 description 4

- 230000005856 abnormality Effects 0.000 description 4

- 101000966782 Homo sapiens Lysophosphatidic acid receptor 1 Proteins 0.000 description 3

- 102100040607 Lysophosphatidic acid receptor 1 Human genes 0.000 description 3

- 230000008859 change Effects 0.000 description 2

- 230000009849 deactivation Effects 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 230000001360 synchronised effect Effects 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 1

- 101150021225 cynS gene Proteins 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000001914 filtration Methods 0.000 description 1

- 238000007429 general method Methods 0.000 description 1

- 238000009434 installation Methods 0.000 description 1

- 230000000873 masking effect Effects 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 230000001568 sexual effect Effects 0.000 description 1

- 230000011664 signaling Effects 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3685—Details of drivers for data electrodes

- G09G3/3688—Details of drivers for data electrodes suitable for active matrices only

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/06—Handling electromagnetic interferences [EMI], covering emitted as well as received electromagnetic radiation

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2011—Display of intermediate tones by amplitude modulation

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Crystallography & Structural Chemistry (AREA)

- Chemical & Material Sciences (AREA)

- Computer Hardware Design (AREA)

- Nonlinear Science (AREA)

- Optics & Photonics (AREA)

- Mathematical Physics (AREA)

- Liquid Crystal Display Device Control (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Electronic Switches (AREA)

- Liquid Crystal (AREA)

Description

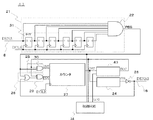

図1に本実施の形態1のおけるノイズ除去回路6を採用したタイミングコントローラ5を採用した液晶表示装置1のシステム構成図を示す。図1において、液晶パネル10は、XGA(Extra Graphic Array)の解像度を有しており、代表して図示した画素12およびそれを駆動するTFT11が、夫々縦768個、横1024×3個(R,G,B分)マトリックス状に、配置されており(図示せず)、それらの画素を駆動するために複数の走査線および信号線に夫々接続される走査線駆動回路2および信号線駆動回路3が液晶パネル10のマトリックス表示部周辺に配置されている。

本実施の形態2では、前記実施の形態1にて採用した規定値検出回路において、図8で示したように、予めノイズ除去回路41の外部に設置された制御回路34から規定値出力LODを入力可能な仕様としておき、液晶パネルの様々な解像度にも対応できるようにした例である。

本実施の形態3では、図8に示したように前記実施の形態2にて採用した前記ノイズ除去回路41に内蔵された水平画素数検出部43の検出出力EOCを制御回路34に入力するよう構成し、制御回路34にて液晶パネルを表示するための信号DENA入力の長さから表示すべき液晶パネルの解像度について、予め決められた解像度と合致するかどうかを段階的に判別し、前記規定値を設定するよう構成する。

図9にDENA信号および前記ノイズが除去された前記DENA2信号から液晶パネルの解像度を弁別する解像度弁別回路50の実施の形態について、その構成を示す。まず、DENA信号の立下りエッジを検出するエッジ検出回路部100の立下りエッジ検出出力EDG1出力、DENAおよびDCLKが第一のカウンタ101に入力される。カウンタ101はDENAが活性化(High)されるとDCLKのカウントを開始し、立下りエッジEDG1が入力すると停止し、第一のカウント値CNT1をカウンタ値保持回路部102に出力する。また、カウンタ101に入力するDENAが非活性(Low)となると、リセットされ第一のカウント値出力CNT1は零となる。カウント値保持回路部102はDENA信号の立下りエッジEDG1が入力されると、そのときのCNT1を保持すると同時に、保持しているカウント保持値MTNをDENAパルス幅判別回路104に出力する。エッジ検出回路部103は、前記エッジ検出回路部100と同様の回路で構成されており、DENA2の立下りエッジを検出し、該エッジEDG2をDENAパルス幅判別回路部104に出力する。DENAパルス幅判別回路部104には、前記EDG2信号とMTN信号が入力し、前記EDG2パルスが入力された時点におけるMTN値が予め定められた所定の閾値より大きいか、小さいかをPDT信号としてEDG2信号の立上りに同期して第二のカウンタ即ちアップダウンカウンタ105に出力する。アップダウンカウンタ105は、前記PDT信号とEDG2信号を入力して、EDG2信号の立上りエッジが入力される毎にそのカウントを増減させる4ビットのカウンタで、前記PDT信号がHighの時はカウント値を増加しLowの時はカウント値を減少させる。また、アップダウンカウンタ105のカウント値CNT2即ち第二のカウント値は、最小値0から最大値15までであり、0から15及び15から0への循環(キャリーオーバ)は実行しない回路構成となっている。前記第二のカウント値CNT2は、解像度判別回路106へ入力され、解像度判別回路106にて解像度が判別されて判別結果DSTとして出力される。該判別結果DSTは、図1で示したタイミングコントローラを構成するディジタル回路内、例えば前記タイミング制御回路4などで液晶パネル10の水平解像度を規定する信号として使用される。

5 タイミングコントローラ

6、40、41 ノイズ除去回路

7 遅延回路

8 データイネーブル信号(DENA)

9 表示データ(DATA)

16 データイネーブル出力(DENA2)

17 ドットクロック(DCLK)

21 DENA立上り検出部

22 7入力AND回路部

23、33、43 水平画素数検出部

24、35 初期状態検出部

25 初期化回路部

26 カウントイネーブル回路部

27、32、101 カウンタ

28 反転バッファ

29 AND回路

30 AND回路

31 遅延回路ブロック

34 制御回路

50 解像度弁別回路

100、103 エッジ検出回路部

102 カウンタ値保持回路部

104 DENAパルス幅判別回路

105 アップダウンカウンタ

106 解像度判別回路

DENA データイネーブル入力

DCLK ドットクロック

DATA 表示データ

DENA2 データイネーブル出力

PEG 立上り検出出力

INT 初期化信号

ENV カウント許可信号

CNT、CNT1、CNT2 カウント出力

EOC カウント停止信号

ITS カウンタ初期状態信号

LOD 規定値出力

EDG1 DENAの立下りエッジ

EDG2 DENA2の立下りエッジ

MTN カウント値保値

PDT パルス幅判別出力

DST 解像度判別結果

Claims (9)

- マトリックス表示装置の表示制御信号のノイズ除去回路であって、

前記表示制御信号を入力し、該表示制御信号を順次遅延する複数段の遅延回路と、該複数段の遅延回路の出力の全てが同じ論理となった場合にのみ活性化検出信号を出力する論理回路から成る連続活性化検出部と、

前記マトリックス表示装置のドットクロック信号をカウントし、カウンタ初期化信号により初期化され、カウント許可信号によりカウントを実行するカウンタと、

該カウンタから出力されるカウント値を入力して、該カウント値が前記マトリックス表示装置の水平画素数に対応した所定の値に到達するとカウント停止信号を出力する水平画素数検出部と、

前記カウント停止信号を受けて前記活性化検出信号が非活性化時に、前記カウンタを初期化して前記カウント値が初期値となる前記カウンタ初期化信号を出力する初期化回路部と、

前記カウント値を入力して、該カウント値が前記初期値と等しいか否か検知し、等しい時に初期化状態信号を出力し、等しくない時には該信号を出力しない初期状態検出回路と、

前記活性化検出信号が活性状態かまたは前記初期化状態信号が非活性状態であって、かつ前記水平画素数検出部から入力する前記カウント停止信号が非活性状態の期間に前記カウント許可信号を前記カウンタに出力するカウントイネーブル回路部とを具備し、

前記カウンタが前記カウント許可信号の活性状態を受けて前記初期値からカウントを開始し、前記水平画素数に対応したカウント値分のカウントを終了後、前記カウンタ初期化信号によって前記カウンタを再び初期化するよう構成し、

前記初期化状態信号を用いてノイズが除去された表示制御信号を得ることを特徴とするノイズ除去回路。 - ノイズを除去する前記表示制御信号はデータイネーブル信号であることを特徴とする請求項1に記載の表示制御信号のノイズ除去回路。

- 前記複数段の遅延回路は2個ないし30個のDフリップフロップ回路で構成されていることを特徴とする請求項1または2に記載のノイズ除去回路。

- 前記カウンタは、アップカウンタ式であって、前記初期値は、零であることを特徴とする請求項1ないし3のいずれか一項に記載のノイズ除去回路。

- 前記カウンタは、ダウンカウンタ式であって、前記初期値は、マトリックス表示装置の水平画素数に対応した所定の値であることを特徴とする請求項1ないし3のいずれか一項に記載のノイズ除去回路。

- 前記水平画素数検出部のカウント停止信号および前記連続活性化検出部の前記活性化検出信号を入力する制御回路部をさらに備え、

該制御回路部の規定値出力を用いて前記水平画素数検出部に任意の水平画素数に対応した値を規定値として設定できるよう構成し、

前記制御回路部は、前記カウント停止信号が入力されると、前記活性化検出信号が非活性状態である場合は、前記規定値を増加させることを特徴とする請求項1ないし4のいずれか一項に記載のノイズ除去回路。 - 表示データ信号は、前記連続活性化検出部におけるノイズを除去する信号の遅延量と同等の遅延量を有する遅延回路を通過することを特徴とする請求項1ないし6のいずれか一項に記載のノイズ除去回路。

- 請求項2に記載のノイズ除去回路と、

前記データイネーブル信号波形のエッジから次のエッジ間のドットクロック数をカウントする第一のカウンタと、

該第一のカウンタの第一のカウント値を保持するカウント保持回路と、

前記ノイズ除去回路のデータイネーブル出力に同期して前記保持回路に保持された前記第一のカウント値が所定の閾値との大小を判別し、前記閾値より大であれば第二のカウント値を増加させ、閾値より小さければ前記第二のカウント値を減少させる第二のカウンタ回路と、を具備することを特徴とする解像度弁別回路。 - 請求項1ないし7のいずれか一項に記載のノイズ除去回路を用いたマトリックス表示装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005214580A JP4894183B2 (ja) | 2005-07-25 | 2005-07-25 | ノイズ除去回路およびこれを用いたマトリックス表示装置、ならびに解像度弁別回路 |

| US11/340,632 US7554534B2 (en) | 2005-07-25 | 2006-01-27 | Noise elimination circuit of matrix display device and matrix display device using the same |

| TW095114107A TW200705356A (en) | 2005-07-25 | 2006-04-20 | Noise elimination circuit of matrix display device and matrix display device using the same |

| KR1020060048011A KR100802459B1 (ko) | 2005-07-25 | 2006-05-29 | 매트릭스 표시장치의 노이즈 제거 회로 및 이것을 이용한매트릭스 표시장치 |

| CN200610088625A CN100583221C (zh) | 2005-07-25 | 2006-05-31 | 矩阵显示装置的噪声除去电路及使用该电路的矩阵显示装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005214580A JP4894183B2 (ja) | 2005-07-25 | 2005-07-25 | ノイズ除去回路およびこれを用いたマトリックス表示装置、ならびに解像度弁別回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007033659A JP2007033659A (ja) | 2007-02-08 |

| JP2007033659A5 JP2007033659A5 (ja) | 2009-07-23 |

| JP4894183B2 true JP4894183B2 (ja) | 2012-03-14 |

Family

ID=37674244

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005214580A Active JP4894183B2 (ja) | 2005-07-25 | 2005-07-25 | ノイズ除去回路およびこれを用いたマトリックス表示装置、ならびに解像度弁別回路 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7554534B2 (ja) |

| JP (1) | JP4894183B2 (ja) |

| KR (1) | KR100802459B1 (ja) |

| CN (1) | CN100583221C (ja) |

| TW (1) | TW200705356A (ja) |

Families Citing this family (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5161426B2 (ja) * | 2006-01-31 | 2013-03-13 | 株式会社ジャパンディスプレイセントラル | 表示制御装置 |

| JP4305533B2 (ja) * | 2007-03-12 | 2009-07-29 | エプソンイメージングデバイス株式会社 | 表示装置 |

| JP4903074B2 (ja) * | 2007-03-27 | 2012-03-21 | ラピスセミコンダクタ株式会社 | 同期信号生成回路 |

| KR101377463B1 (ko) * | 2007-05-10 | 2014-04-02 | 삼성디스플레이 주식회사 | 노이즈 제거회로와, 이를 구비한 게이트 구동회로 및 표시장치 |

| US8072394B2 (en) * | 2007-06-01 | 2011-12-06 | National Semiconductor Corporation | Video display driver with data enable learning |

| KR101544916B1 (ko) * | 2008-08-05 | 2015-08-18 | 삼성디스플레이 주식회사 | 정전기 방전 내성이 강화된 액정 표시 장치 |

| TWI397896B (zh) * | 2009-01-14 | 2013-06-01 | Novatek Microelectronics Corp | 使用單一資料致能訊號來控制顯示器時序之方法及相關時序控制電路 |

| JP5235819B2 (ja) * | 2009-08-12 | 2013-07-10 | キヤノン株式会社 | 画像処理装置、画像処理方法 |

| CN102024435B (zh) * | 2009-09-22 | 2013-03-06 | 群康科技(深圳)有限公司 | 电压调整模块、电压调整方法及液晶显示装置 |

| CN102034444B (zh) * | 2009-09-30 | 2013-01-23 | 北京京东方光电科技有限公司 | 液晶显示器源驱动方法及驱动装置 |

| JP5431907B2 (ja) | 2009-12-18 | 2014-03-05 | ラピスセミコンダクタ株式会社 | 同期処理システム及び半導体集積回路 |

| US8654259B2 (en) | 2010-02-18 | 2014-02-18 | Sharp Kabushiki Kaisha | Image processing system and display device |

| US8687125B2 (en) | 2010-05-18 | 2014-04-01 | Sharp Kabushiki Kaisha | Image processing system and display device for carrying out subtraction or addition of a pixel value of a target pixel in accordance with a value equivalent to a noise quantity |

| CN103997335B (zh) * | 2014-05-13 | 2017-04-05 | 合肥鑫晟光电科技有限公司 | 时序控制器的信号频率的设定装置、方法以及显示设备 |

| JP6425115B2 (ja) * | 2014-07-03 | 2018-11-21 | Tianma Japan株式会社 | タイミングコントローラ及び表示装置 |

| JP6349171B2 (ja) * | 2014-07-07 | 2018-06-27 | ローム株式会社 | ノイズ除去回路、タイミングコントローラ、ディスプレイ装置、電子機器、ソースドライバの制御方法 |

| US9379743B2 (en) * | 2014-07-30 | 2016-06-28 | Intel Corporation | Method and apparatus for signal edge boosting |

| CN107612539B (zh) * | 2017-09-30 | 2020-04-10 | 深圳市华星光电技术有限公司 | 一种电平转化器的时钟输入信号异常的处理方法 |

| CN107947786A (zh) * | 2017-11-16 | 2018-04-20 | 湖南工业大学 | 翻斗式雨量计计数脉冲产生方法 |

| US11367390B2 (en) * | 2018-12-24 | 2022-06-21 | Novatek Microelectronics Corp. | Display apparatus and method for noise reduction |

| US11423829B2 (en) * | 2020-03-02 | 2022-08-23 | Silicon Works Co., Ltd. | Clock generating circuit for LED driving device and method for driving |

| TWI724840B (zh) * | 2020-03-26 | 2021-04-11 | 友達光電股份有限公司 | 顯示面板 |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01172998A (ja) * | 1987-12-28 | 1989-07-07 | Matsushita Electric Ind Co Ltd | ディスプレイ制御回路 |

| JP2733664B2 (ja) * | 1988-04-25 | 1998-03-30 | 富士通株式会社 | マトリクス表示装置 |

| KR0169618B1 (ko) * | 1995-04-27 | 1999-03-20 | 김광호 | 스큐 보상 및 잡음을 제거하기 위한 영상신호 처리장치 |

| US5835542A (en) * | 1996-07-19 | 1998-11-10 | Utek Semiconductor Corporation | Digital data separator for separating data signals from clock signals in an encoded data stream |

| KR100281108B1 (ko) | 1997-12-26 | 2001-02-01 | 김영환 | 노이즈제거장치 |

| JPH11214964A (ja) | 1998-01-21 | 1999-08-06 | Sony Corp | ノイズ除去装置 |

| JP3516332B2 (ja) * | 1998-02-20 | 2004-04-05 | 三洋電機株式会社 | 表示装置 |

| KR100315011B1 (ko) * | 1998-03-27 | 2002-02-28 | 주식회사 현대 디스플레이 테크놀로지 | 액정표시장치의모드검출회로 |

| JPH11282401A (ja) | 1998-03-30 | 1999-10-15 | Toshiba Corp | 平面表示装置 |

| JP2000209076A (ja) | 1999-01-18 | 2000-07-28 | Mitsubishi Electric Corp | ノイズ検出回路 |

| JP3555501B2 (ja) | 1999-05-27 | 2004-08-18 | 三菱電機株式会社 | ノイズフィルタ回路 |

| KR100631112B1 (ko) * | 1999-09-04 | 2006-10-04 | 엘지.필립스 엘시디 주식회사 | 인버젼 방식의 액정패널 구동방법 및 장치 |

| JP2001282198A (ja) * | 2000-03-31 | 2001-10-12 | Digital Electronics Corp | プログラム式表示装置の誤動作防止方法 |

| JP2002271427A (ja) | 2001-03-09 | 2002-09-20 | Ricoh Co Ltd | ノイズ除去回路 |

| JP4487437B2 (ja) * | 2001-03-29 | 2010-06-23 | 三菱電機株式会社 | 映像信号処理装置及び映像信号処理方法 |

| JP4598355B2 (ja) * | 2002-10-10 | 2010-12-15 | ソニー株式会社 | ディスクドライブ装置、プリピット検出方法 |

| JP4508583B2 (ja) * | 2003-09-05 | 2010-07-21 | 三洋電機株式会社 | 液晶表示制御装置 |

-

2005

- 2005-07-25 JP JP2005214580A patent/JP4894183B2/ja active Active

-

2006

- 2006-01-27 US US11/340,632 patent/US7554534B2/en active Active

- 2006-04-20 TW TW095114107A patent/TW200705356A/zh unknown

- 2006-05-29 KR KR1020060048011A patent/KR100802459B1/ko active IP Right Grant

- 2006-05-31 CN CN200610088625A patent/CN100583221C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| KR20070013203A (ko) | 2007-01-30 |

| TW200705356A (en) | 2007-02-01 |

| US20070018932A1 (en) | 2007-01-25 |

| US7554534B2 (en) | 2009-06-30 |

| JP2007033659A (ja) | 2007-02-08 |

| CN100583221C (zh) | 2010-01-20 |

| CN1904994A (zh) | 2007-01-31 |

| KR100802459B1 (ko) | 2008-02-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4894183B2 (ja) | ノイズ除去回路およびこれを用いたマトリックス表示装置、ならびに解像度弁別回路 | |

| KR101319088B1 (ko) | 평판 패널용 화상 모드 제어기 및 그를 포함한 평판 표시장치 | |

| US8248349B2 (en) | Liquid crystal display having endurance against electrostatic discharge | |

| US8711076B2 (en) | Timing controller capable of removing surge signal and display apparatus including the same | |

| US9691316B2 (en) | Display device capable of clock synchronization recovery | |

| JP2006268260A (ja) | データ転送制御装置及び電子機器 | |

| JP6425115B2 (ja) | タイミングコントローラ及び表示装置 | |

| US20120072773A1 (en) | Panel Driving Circuit That Generates Panel Test Pattern and Panel Test Method Thereof | |

| US10070018B2 (en) | Device for vertical and horizontal synchronization in display system | |

| JP2016177279A (ja) | 液晶表示装置及び液晶表示システム | |

| US7215312B2 (en) | Semiconductor device, display device, and signal transmission system | |

| CN111694456B (zh) | 时序控制电路及其操作方法 | |

| CN109427276B (zh) | 显示装置、时序控制电路及其信号重建方法 | |

| JP2008180830A (ja) | 表示装置 | |

| JP5299734B2 (ja) | 画像処理方法、画像表示装置及びそのタイミングコントローラ | |

| JP7232739B2 (ja) | 表示ドライバ、表示装置及び半導体装置 | |

| JP2019219221A (ja) | 半導体集積回路、ブリッジチップ、ディスプレイシステム、自動車 | |

| JP2006113384A (ja) | 液晶表示装置及び液晶表示装置における誤動作防止方法 | |

| JP2006267452A (ja) | 液晶表示装置、制御回路、及び液晶表示データ検査方法 | |

| KR100935821B1 (ko) | 도트 클럭 생성 회로, 반도체 디바이스, 및 도트 클럭 생성방법 | |

| JP2007041437A (ja) | 表示装置 | |

| JPH10301544A (ja) | 液晶表示装置 | |

| JP2007206231A (ja) | 表示制御装置 | |

| JP4216848B2 (ja) | 映像信号処理回路、映像信号処理回路の制御方法、及び集積回路 | |

| JP5121140B2 (ja) | パリティ信号生成装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080225 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090609 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110324 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110426 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110616 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111129 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111212 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 4894183 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150106 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |