JP4865360B2 - 半導体記憶装置 - Google Patents

半導体記憶装置 Download PDFInfo

- Publication number

- JP4865360B2 JP4865360B2 JP2006054614A JP2006054614A JP4865360B2 JP 4865360 B2 JP4865360 B2 JP 4865360B2 JP 2006054614 A JP2006054614 A JP 2006054614A JP 2006054614 A JP2006054614 A JP 2006054614A JP 4865360 B2 JP4865360 B2 JP 4865360B2

- Authority

- JP

- Japan

- Prior art keywords

- memory cell

- power supply

- supply voltage

- memory device

- semiconductor memory

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/41—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger

- G11C11/413—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing, timing or power reduction

Description

フリップフロップを有するメモリセルと、

上記メモリセルに低電圧側のセル電源電圧を供給するメモリセル電源回路とを有する半導体記憶装置であって、

上記メモリセル電源回路は、

カラムアドレス信号、および書き込みイネーブル制御信号に基づいて、少なくとも互いに異なる2つのセル電源電圧を供給するように構成され、

データの読み出しサイクルにおいてセル電源電圧を供給する場合、および書き込みサイクルにおいてセル電源電圧を供給するメモリセルにデータが書き込まれない場合に、所定の第1の電源電圧を供給する一方、

書き込みサイクルにおいてセル電源電圧を供給するメモリセルにデータが書き込まれる場合に、上記第1の電源電圧よりも高い第2の電源電圧を供給することを特徴とする。

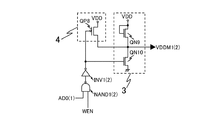

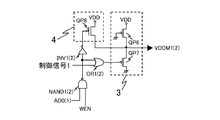

図1は、参考例1に係る半導体記憶装置の構成図である。簡単化のために、読み出し系の回路は省略してある。

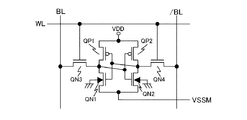

前記参考例1において、プロセスバラツキ等によって、N型MOSトランジスタの特性が変動し、N型MOSトランジスタの閾値電圧が変化した場合を考える。例えば、N型MOSトランジスタの閾値電圧が上昇した場合、メモリセル1を構成するトランジスタのうちの、N型MOSトランジスタであるアクセストランジスタQN3とQN4、ドライブトランジスタQN1とQN2の閾値電圧が上昇する。N型MOSトランジスタの閾値電圧が上昇すると、メモリセルのスタティックノイズマージンは大きくなるが、逆に、メモリセルの書き込みレベルが低下し、メモリセルにデータが書き込みにくくなる。この場合、メモリセルへデータを書き込みやすくするためには、メモリセル電源を更に低下させればよい。

前記参考例1において、メモリセル電源制御回路3を構成するトランジスタは、全てP型MOSトランジスタで構成されている(図1)。メモリセル電源を供給するだけであれば、P型MOSトランジスタとN型MOSトランジスタを直列に接続して構成してもよいし、2個のN型MOSトランジスタを直列に接続して構成しても問題はない。

また、図4に示すように、メモリセル1を構成するロードトランジスタQP1とQP2の基板ノードは、VDD電源に接続される(ロードトランジスタQP1とQP2のソースノードと基板ノードを分離する)ことが望ましい。書き込み動作時において、選択されるビット線に接続されているメモリセル1のメモリセル電源は、上記のようにVDDレベルから低下する。このとき、ロードトランジスタQP1とQP2の基板ノードがVDDレベルであれば、ロードトランジスタQP1とQP2には基板バイアス効果が生じ、ロードトランジスタQP1とQP2の閾値電圧の絶対値が上昇し、駆動能力が低下する。よって、書き込み動作時に、メモリセルに対してデータが更に書き込み易くなる(書き込みレベルが改善される)。また、ロードトランジスタQP1とQP2の閾値電圧の絶対値が上昇するため、選択ビット線で、かつ、書き込み対象でないメモリセル(ワード線が活性化されないメモリセル)に接続したメモリセルを流れるリーク電流が減少するため、低消費電力化が可能である。

更に、メモリセルのスタティックノイズマージンも同時に改善するには、書き込み動作時においては、非選択ビット線に接続したメモリセル電源を、書き込み動作時以外(読み出し動作時)では、全てのメモリセルのメモリセル電源をVDDレベル以上に制御してやればよい。具体的には、図1のリーク補償回路4を構成するP型MOSトランジスタQP8のソース端子に入力されている電源VDDのレベルを、VDDレベル以上に置き換えることで簡単に実現可能である。VDDレベル以上を印加するには、SRAMマクロ内部にVDDレベル以上の電圧を発生できる昇圧回路を設けて供給してもよいし、SRAMマクロ外部から供給しても良い。

次に、上記のような半導体記憶装置におけるメモリセル電源制御回路3の出力電圧(P型MOSトランジスタQP6、QP7等による分圧比)、および駆動能力等について説明する。

P型MOSトランジスタQP6、QP7等による分圧比は、書き込み動作時にメモリセル電源制御回路3から出力される電源電圧によって、所定の時間内に確実に書き込みを完了することが可能で、かつ、誤書き込みに対する十分に大きなマージンが得られるように設定されればよい。具体的には、以下のように設定される。

P型MOSトランジスタQP6、QP7等の駆動能力は、電源電圧が供給されるメモリセルの数や要求される書き込み速度などに応じて、やはり、所定の時間内に確実に書き込みを完了することが可能で、かつ、誤書き込みに対する十分に大きなマージンが得られるように設定されればよい。具体的には、以下のように設定される。

メモリセル電源をVDDレベルから低下(メモリセルの書き込みレベルを上昇)させなくても、メモリセルに対して問題なくデータの書き込みが可能な場合には、メモリセル電源制御回路3を構成するP型MOSトランジスタQP7のゲート入力をHレベルに固定できるように制御し、メモリセル電源制御回路3が常に非活性状態、すなわち、常時オンしているP型MOSトランジスタQP6によって、メモリセル電源が常にVDDレベルのみを出力する状態にしておけばよい。

次に、リーク補償回路4の駆動能力等について説明する。

図7は、参考例6に係る半導体記憶装置の構成図である。簡単化のために、読み出し系の回路は省略してある。

前記参考例1では、メモリセルを構成するフリップフロップの電源であるロードトランジスタQP1とQP2のソースノード(メモリセル電源VDDM)をVDDレベルから低下させる場合を例に説明したが、メモリセルを構成するフリップフロップの電源であるドライブトランジスタQN1とQN2のソースノード(メモリセル電源VSSM)を接地レベルから上昇させた場合においても、同様に、メモリセルへの書き込み可能な電圧は改善し、半導体記憶装置の動作下限電圧の改善や、メモリセルへのデータの書き込み速度の高速化がなされる。

なお、MOSトランジスタQN11〜13の極性は、上記に限らず、参考例2、3(図2、3)で説明したのと同様に、P型とN型とを種々組み合わせるようにしてもよい。これらによって、例えば、分圧比をドライブトランジスタQN1、QN2や、ロードトランジスタQP1、QP2、アクセストランジスタQN3〜4の閾値電圧に応じて設定することなどが容易にできる。

例えば参考例1(図1)で説明したSRAMのような、フリップフロップ型のメモリセルを備えた半導体記憶装置では、メモリセル部(フリップフロップ)のみにメモリセル電源VDDMが供給されていれば、メモリセル電源VDDM以外の電源(周辺回路電源:例えば図1のAND1、NAND1、INV1等への電源)が遮断されても、メモリセルに書き込まれたデータの記憶保持が可能である。そこで、メモリセル電源VDDMと、周辺回路電源とを分離し、例えば、半導体記憶装置が非活性状態(データの記憶保持のみを行い、データの書き込みも読み出しも行わない状態)の場合には、周辺回路電源を遮断してメモリセル電源VDDMの電源のみを供給することで、半導体記憶装置の低消費電力化が可能となる。

そこで、例えば図10に示すように構成すれば、メモリセル電源VDDMを確実に供給することができる。すなわち、メモリセル電源制御回路3Aは、メモリセル電源制御回路3に対して、P型MOSトランジスタQP7のドレイン端子と接地との間に、周辺回路電源遮断信号PD(周辺回路電源遮断時に周辺回路電源とは無関係にHレベルとなる信号)によって制御されるP型MOSトランジスタQP9を直列に挿入した構成である。P型MOSトランジスタQP9を直列に挿入することで、周辺回路電源遮断時に、2入力NAND回路NAND1(NAND2)の不定な出力レベルとは無関係に、メモリセル電源制御回路3Aは、その機能(メモリセル電源VDDMに分圧レベルを出力すること)を確実に停止することが可能になる。

周辺回路電源を遮断することによって、上記と同様にアクセストランジスタQN3〜4を制御するワード線WLのレベルが不安定になる場合、同一ビット線上に存在するメモリセル同士は、アクセストランジスタQN3〜4を介してショートし、メモリセルの保持データが破壊されてしまう恐れがある。そこで、周辺回路の電源が遮断されている場合には、メモリセルのアクセストランジスタが確実にオフするように制御されていることが望ましい。具体的には、例えば図11に示すように、周辺回路電源の遮断時には、周辺回路電源遮断信号PD(周辺回路電源遮断時に周辺回路電源とは無関係にHレベルとなる信号)で制御され、全てのワード線WLを強制的に接地レベルに制御することが可能なトランジスタQN15を配置することで、より安定したメモリセルデータの記憶保持が可能となる。

メモリセルのデータが正常に記憶保持されるためには、メモリセルを構成するフリップフロップが正常に動作すればよい。つまり、フリップフロップを構成する、ロードトランジスタQP1とドライブトランジスタQN2、またはロードトランジスタQP2とドライブトランジスタQN1の組み合わせがオン状態にできるように、メモリセル電源が印加されていればよい。

2 プリチャージ回路

3 メモリセル電源制御回路

3’ メモリセル電源制御回路

3A メモリセル電源制御回路

4 リーク補償回路

4’ リーク補償回路

4A リーク補償回路

4B リーク補償回路

5 正規回路ブロック

6 冗長救済用回路ブロック

AND1〜4 2入力AND回路

AND5〜8 3入力AND回路

ANDR5〜8 3入力AND回路

INV1〜3 インバータ

NAND1〜2 2入力NAND回路

NAND3〜4 2入力NAND回路

NAND5〜6 3入力NAND回路

NAND7〜8 3入力NAND回路

NANDR5〜6 3入力NAND回路

NANDR7〜8 3入力NAND回路

OR1〜2 2入力OR回路

QN1 ドライブトランジスタ

QN2 ドライブトランジスタ

QN3 アクセストランジスタ

QN4 アクセストランジスタ

QN5〜8 N型MOSトランジスタ

QN9 N型MOSトランジスタ

QN17 N型MOSトランジスタ

QNR5〜8 N型MOSトランジスタ

QP1 ロードトランジスタ

QP2 ロードトランジスタ

QP3 プリチャージトランジスタ

QP4 プリチャージトランジスタ

QP5 イコライズトランジスタ

QP6〜10 P型MOSトランジスタ

BL1〜2 ビット線

/BL1〜2 ビット線

/BLR1〜2 冗長用ビット線

BLR1〜2 冗長用ビット線

VDD 電源

VDDM1〜2 メモリセル電源

VDDMR1〜2 冗長用メモリセル電源

VSSM1〜2 メモリセル電源

WL1〜2 ワード線

1〜2 制御信号

AD0〜1 カラムアドレス信号

DIN 入力データ

/DIN 入力データ

PCG プリチャージ制御信号

REDEN 冗長救済信号、

/REDEN 冗長救済反転信号

WEN 書き込みイネーブル制御信号

Claims (18)

- フリップフロップを有するメモリセルと、

上記メモリセルに低電圧側のセル電源電圧を供給するメモリセル電源回路とを有する半導体記憶装置であって、

上記メモリセル電源回路は、

カラムアドレス信号、および書き込みイネーブル制御信号に基づいて、少なくとも互いに異なる2つのセル電源電圧を供給するように構成され、

データの読み出しサイクルにおいてセル電源電圧を供給する場合、および書き込みサイクルにおいてセル電源電圧を供給するメモリセルにデータが書き込まれない場合に、所定の第1の電源電圧を供給する一方、

書き込みサイクルにおいてセル電源電圧を供給するメモリセルにデータが書き込まれる場合に、上記第1の電源電圧よりも高い第2の電源電圧を供給することを特徴とする半導体記憶装置。 - フリップフロップを有するメモリセルと、

上記メモリセルに高電圧側のセル電源電圧を供給するメモリセル電源回路とを有する半導体記憶装置であって、

上記メモリセル電源回路は、

カラムアドレス信号、および書き込みイネーブル制御信号に基づいて、少なくとも互いに異なる2つのセル電源電圧を供給するように構成され、

データの読み出しサイクルにおいてセル電源電圧を供給する場合、および書き込みサイクルにおいてセル電源電圧を供給するメモリセルにデータが書き込まれない場合に、所定の第1の電源電圧を供給する一方、

書き込みサイクルにおいてセル電源電圧を供給するメモリセルにデータが書き込まれる場合に、上記第1の電源電圧よりも低い第2の電源電圧を供給することを特徴とする半導体記憶装置。 - 請求項1および請求項2のうち何れか1項の半導体記憶装置であって、

上記メモリセル電源回路は、所定の電圧を分圧することによって、上記第2の電源電圧を出力するように構成されていることを特徴とする半導体記憶装置。 - 請求項3の半導体記憶装置であって、

上記メモリセル電源回路は、

所定の駆動能力を有し、上記第1の電源電圧を出力する第1のトランジスタと、

上記第1のトランジスタとによって分圧された電圧を上記第2の電源電圧として出力する第2のトランジスタとを有することを特徴とする半導体記憶装置。 - 請求項1および請求項2のうち何れか1項の半導体記憶装置であって、

上記メモリセル電源回路は、ソースフォロワ回路で構成され、少なくともそのソースフォロワを構成するトランジスタの極性は、上記メモリセルを構成するドライブトランジスタと同極性のトランジスタで構成されていることを特徴とする半導体記憶装置。 - 請求項1の半導体記憶装置であって、

上記第2の電源電圧が、上記メモリセルを構成するドライブトランジスタのソース端子に供給されるとともに、上記ドライブトランジスタの基板に、上記第2の電源電圧より低い電圧が供給されるように構成されていることを特徴とする半導体記憶装置。 - 請求項2の半導体記憶装置であって、

上記第2の電源電圧が、上記メモリセルを構成するロードトランジスタのソース端子に供給されるとともに、上記ロードトランジスタの基板に、上記第2の電源電圧より高い電圧が供給されるように構成されていることを特徴とする半導体記憶装置。 - 請求項3の半導体記憶装置であって、

メモリセルのサイズが互いに異なる複数組のメモリセル組が設けられ、

各メモリセル組に上記第2の電源電圧を供給するメモリセル電源回路の上記分圧の分圧比が、上記メモリセルのサイズに応じて設定されていることを特徴とする半導体記憶装置。 - 請求項1および請求項2のうち何れか1項の半導体記憶装置であって、

ビット線に接続されるメモリセルの数が互いに異なる複数組のメモリセル組が設けられ、

各メモリセル組に上記第2の電源電圧を供給する場合の上記メモリセル電源回路の駆動能力が、上記ビット線に接続されるメモリセルの数、またはビット線の長さの少なくとも一方に応じて設定されていることを特徴とする半導体記憶装置。 - 請求項1および請求項2のうち何れか1項の半導体記憶装置であって、

メモリセルのサイズが互いに異なる複数組のメモリセル組が設けられ、

各メモリセル組に上記第2の電源電圧を供給する場合の上記メモリセル電源回路の駆動能力が、上記メモリセルのサイズに応じて設定されていることを特徴とする半導体記憶装置。 - 請求項1および請求項2のうち何れか1項の半導体記憶装置であって、

ビット線に接続されるメモリセルの数が互いに異なる複数組のメモリセル組が設けられ、

各メモリセル組に上記第1の電源電圧を供給する場合の上記メモリセル電源回路の駆動能力が、上記ビット線に接続されるメモリセルの数、またはビット線の長さの少なくとも一方に応じて設定されていることを特徴とする半導体記憶装置。 - 請求項1および請求項2のうち何れか1項の半導体記憶装置であって、

冗長救済機能を有し、

冗長救済が行われる場合に、冗長救済されるメモリセルに対応したメモリセル電源回路による電源電圧の供給が停止されるように構成されていることを特徴とする半導体記憶装置。 - 請求項1および請求項2のうち何れか1項の半導体記憶装置であって、

冗長救済機能を有し、

冗長救済が行われない場合に、使用されない冗長救済メモリセルに対応したメモリセル電源回路による電源電圧の供給が停止されるように構成されていることを特徴とする半導体記憶装置。 - 請求項1および請求項2のうち何れか1項の半導体記憶装置を複数備えたことを特徴とする半導体集積回路。

- 請求項1および請求項2のうち何れか1項の半導体記憶装置であって、

さらに、

上記メモリセルの周辺回路に電源電圧を供給する周辺回路電源とを備え、

上記メモリセル電源回路は、さらに、上記周辺回路への電源電圧の供給が遮断される場合に、上記第1の電源電圧を供給するように構成されたことを特徴とする半導体記憶装置。 - 請求項15の半導体記憶装置であって、

上記周辺回路への電源電圧の供給が遮断される場合に、上記メモリセルが有するアクセストランジスタがオフするように制御されることを特徴とする半導体記憶装置。 - 請求項16の半導体記憶装置であって、

上記アクセストランジスタを制御するワード線と接地との間に接続されたワード線接地トランジスタを備え、上記周辺回路への電源電圧の供給が遮断される場合に上記ワード線接地トランジスタがオンすることによってアクセストランジスタがオフするように制御されることを特徴とする半導体記憶装置。 - 請求項15の半導体記憶装置であって、

上記メモリセルに記憶データを保持させ得る電源電圧が、ダイオード型にゲートが接続されたトランジスタと、上記周辺回路への電源電圧の供給を制御する制御信号によって制御されるトランジスタとが直列接続されて生成されるように構成されたことを特徴とする半導体記憶装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006054614A JP4865360B2 (ja) | 2006-03-01 | 2006-03-01 | 半導体記憶装置 |

| US11/650,482 US7577014B2 (en) | 2006-03-01 | 2007-01-08 | Semiconductor memory device |

| CN2007100070235A CN101030447B (zh) | 2006-03-01 | 2007-02-07 | 半导体存储器件 |

| US12/503,523 US7817460B2 (en) | 2006-03-01 | 2009-07-15 | Semiconductor memory device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006054614A JP4865360B2 (ja) | 2006-03-01 | 2006-03-01 | 半導体記憶装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007234126A JP2007234126A (ja) | 2007-09-13 |

| JP2007234126A5 JP2007234126A5 (ja) | 2009-03-19 |

| JP4865360B2 true JP4865360B2 (ja) | 2012-02-01 |

Family

ID=38471292

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006054614A Active JP4865360B2 (ja) | 2006-03-01 | 2006-03-01 | 半導体記憶装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US7577014B2 (ja) |

| JP (1) | JP4865360B2 (ja) |

| CN (1) | CN101030447B (ja) |

Families Citing this family (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009064482A (ja) * | 2007-09-04 | 2009-03-26 | Nec Electronics Corp | 半導体記憶装置 |

| US7760576B2 (en) * | 2007-11-08 | 2010-07-20 | Qualcomm Incorporated | Systems and methods for low power, high yield memory |

| JP2009123258A (ja) * | 2007-11-12 | 2009-06-04 | Panasonic Corp | 半導体記憶装置 |

| JP5200506B2 (ja) * | 2007-11-28 | 2013-06-05 | 富士通セミコンダクター株式会社 | メモリ装置 |

| JP4579965B2 (ja) * | 2007-12-19 | 2010-11-10 | パナソニック株式会社 | 半導体記憶装置 |

| US7733687B2 (en) * | 2008-02-20 | 2010-06-08 | Taiwan Semiconductor Manufacturing Company, Ltd. | WAK devices in SRAM cells for improving VCCMIN |

| KR20090097712A (ko) * | 2008-03-12 | 2009-09-16 | 주식회사 하이닉스반도체 | 컬럼 선택 신호 전위 조절 회로 및 이를 이용한 반도체메모리 장치 |

| US7911826B1 (en) * | 2008-03-27 | 2011-03-22 | Altera Corporation | Integrated circuits with clearable memory elements |

| CN101552035B (zh) * | 2008-04-02 | 2012-04-04 | 世界先进积体电路股份有限公司 | 存储器系统 |

| US8120951B2 (en) * | 2008-05-22 | 2012-02-21 | Micron Technology, Inc. | Memory devices, memory device constructions, constructions, memory device forming methods, current conducting devices, and memory cell programming methods |

| CN101727954B (zh) * | 2008-10-24 | 2012-08-22 | 中芯国际集成电路制造(上海)有限公司 | 存储器装置及其提供电压供给的方法 |

| US7876600B2 (en) * | 2008-11-17 | 2011-01-25 | AiceStar Technology (Suzhou) Corporation | SRAM and method of controlling the SRAM |

| JP4857367B2 (ja) * | 2009-07-06 | 2012-01-18 | 株式会社沖データ | 駆動回路及び画像形成装置 |

| US8259486B2 (en) * | 2009-08-03 | 2012-09-04 | Stmicroelectronics International N.V. | Self-timed write boost for SRAM cell with self mode control |

| CN101699561B (zh) * | 2009-11-06 | 2012-09-05 | 东南大学 | 用于亚阈值存储单元阵列的位线漏电流补偿电路 |

| US9858986B2 (en) * | 2010-08-02 | 2018-01-02 | Texas Instruments Incorporated | Integrated circuit with low power SRAM |

| JP5777991B2 (ja) * | 2011-09-22 | 2015-09-16 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| WO2013084385A1 (ja) * | 2011-12-08 | 2013-06-13 | パナソニック株式会社 | 半導体記憶装置 |

| US8724374B1 (en) * | 2012-10-18 | 2014-05-13 | Stmicroelectronics International N.V. | Data-dependent pullup transistor supply and body bias voltage application for a static random access memory (SRAM) cell |

| US9263122B2 (en) * | 2013-10-21 | 2016-02-16 | Taiwan Semiconductor Manufacturing Company Ltd. | Data-controlled auxiliary branches for SRAM cell |

| CN104795029B (zh) * | 2014-01-16 | 2017-06-06 | 矽创电子股份有限公司 | 栅极驱动器及其电路缓冲器 |

| US9305633B2 (en) | 2014-04-17 | 2016-04-05 | Stmicroelectronics International N.V. | SRAM cell and cell layout method |

| US9916874B2 (en) | 2014-08-15 | 2018-03-13 | Taiwan Semiconductor Manufacturing Company, Ltd. | Memory architecture having first and second voltages |

| US9251875B1 (en) * | 2014-09-26 | 2016-02-02 | Qualcomm Incorporated | Register file circuit and method for improving the minimum operating supply voltage |

| US9741452B2 (en) | 2015-02-23 | 2017-08-22 | Qualcomm Incorporated | Read-assist circuits for memory bit cells employing a P-type field-effect transistor (PFET) read port(s), and related memory systems and methods |

| US9984730B2 (en) | 2015-02-23 | 2018-05-29 | Qualcomm Incorporated | Negative supply rail positive boost write-assist circuits for memory bit cells employing a P-type field-effect transistor (PFET) write port(s), and related systems and methods |

| US10037400B2 (en) * | 2016-06-02 | 2018-07-31 | Marvell World Trade Ltd. | Integrated circuit manufacturing process for aligning threshold voltages of transistors |

| US9817601B1 (en) * | 2016-07-07 | 2017-11-14 | Nxp Usa, Inc. | Method and apparatus for determining feasibility of memory operating condition change using different back bias voltages |

| JP6220935B2 (ja) * | 2016-08-12 | 2017-10-25 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US10033388B1 (en) * | 2017-03-21 | 2018-07-24 | Xilinx, Inc. | Circuit for and method of enabling the selection of a circuit |

| JP2018142397A (ja) * | 2018-06-20 | 2018-09-13 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| CN114121073B (zh) | 2020-08-27 | 2023-09-12 | 长鑫存储技术有限公司 | 存储器的调节方法、调节系统以及半导体器件 |

| CN114121072B (zh) | 2020-08-27 | 2023-12-12 | 长鑫存储技术有限公司 | 存储器的调节方法、调节系统以及半导体器件 |

| CN114121058B (zh) | 2020-08-27 | 2023-08-29 | 长鑫存储技术有限公司 | 存储器的调节方法、调节系统以及半导体器件 |

| CN114121096B (zh) | 2020-08-27 | 2024-03-26 | 长鑫存储技术有限公司 | 存储器的调节方法、调节系统以及半导体器件 |

Family Cites Families (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5564686A (en) | 1978-11-08 | 1980-05-15 | Nec Corp | Memory unit |

| US5159571A (en) * | 1987-12-29 | 1992-10-27 | Hitachi, Ltd. | Semiconductor memory with a circuit for testing characteristics of flip-flops including selectively applied power supply voltages |

| JP2837682B2 (ja) * | 1989-01-13 | 1998-12-16 | 株式会社日立製作所 | 半導体記憶装置 |

| US5301147A (en) * | 1993-01-08 | 1994-04-05 | Aptix Corporation | Static random access memory cell with single logic-high voltage level bit-line and address-line drivers |

| US5396469A (en) * | 1994-03-31 | 1995-03-07 | Hewlett-Packard Company | SRAM memory requiring reduced voltage swing during write |

| US5490105A (en) * | 1994-09-27 | 1996-02-06 | Regents Of The University Of Michigan | High speed current mirror memory cell architecture |

| US5544097A (en) | 1995-03-31 | 1996-08-06 | Sgs-Thomson Microelectronics, Inc. | SRAM memory cell with reduced internal cell voltage |

| JP4198201B2 (ja) | 1995-06-02 | 2008-12-17 | 株式会社ルネサステクノロジ | 半導体装置 |

| TW299448B (ja) * | 1995-07-20 | 1997-03-01 | Matsushita Electric Ind Co Ltd | |

| US6034886A (en) | 1998-08-31 | 2000-03-07 | Stmicroelectronics, Inc. | Shadow memory for a SRAM and method |

| US6205049B1 (en) | 1999-08-26 | 2001-03-20 | Integrated Device Technology, Inc. | Five-transistor SRAM cell |

| JP3486590B2 (ja) * | 1999-12-03 | 2004-01-13 | キヤノン株式会社 | 堆積膜形成装置 |

| JP3589168B2 (ja) | 2000-09-04 | 2004-11-17 | セイコーエプソン株式会社 | 半導体装置 |

| US6678202B2 (en) | 2000-12-22 | 2004-01-13 | Texas Instruments Incorporated | Reduced standby power memory array and method |

| JP2003059273A (ja) | 2001-08-09 | 2003-02-28 | Hitachi Ltd | 半導体記憶装置 |

| JP4162076B2 (ja) | 2002-05-30 | 2008-10-08 | 株式会社ルネサステクノロジ | 半導体記憶装置 |

| KR100460459B1 (ko) | 2002-07-30 | 2004-12-08 | 삼성전자주식회사 | 향상된 테스트 모드를 갖는 반도체 메모리 장치 |

| JP4286634B2 (ja) | 2002-11-20 | 2009-07-01 | パナソニック株式会社 | メモリ故障救済回路 |

| JP2005078741A (ja) * | 2003-09-02 | 2005-03-24 | Renesas Technology Corp | 半導体記憶装置 |

| US6990035B2 (en) | 2003-12-03 | 2006-01-24 | Texas Instruments Incorporated | Circuit and method for reducing SRAM standby power |

| US7177176B2 (en) * | 2004-06-30 | 2007-02-13 | Intel Corporation | Six-transistor (6T) static random access memory (SRAM) with dynamically variable p-channel metal oxide semiconductor (PMOS) strength |

| JP2006209877A (ja) * | 2005-01-28 | 2006-08-10 | Nec Electronics Corp | 半導体記憶装置 |

| DE102006062834B4 (de) | 2005-06-30 | 2016-07-14 | Denso Corporation | Ejektorkreislaufsystem |

| JP4917767B2 (ja) * | 2005-07-01 | 2012-04-18 | パナソニック株式会社 | 半導体記憶装置 |

| US7394714B2 (en) * | 2006-09-07 | 2008-07-01 | Taiwan Semiconductor Manufacturing Co., Ltd. | Circuit implementation of a dynamic power supply for SRAM core array |

| US7440313B2 (en) * | 2006-11-17 | 2008-10-21 | Freescale Semiconductor, Inc. | Two-port SRAM having improved write operation |

-

2006

- 2006-03-01 JP JP2006054614A patent/JP4865360B2/ja active Active

-

2007

- 2007-01-08 US US11/650,482 patent/US7577014B2/en active Active

- 2007-02-07 CN CN2007100070235A patent/CN101030447B/zh active Active

-

2009

- 2009-07-15 US US12/503,523 patent/US7817460B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN101030447B (zh) | 2012-04-11 |

| JP2007234126A (ja) | 2007-09-13 |

| US20070206404A1 (en) | 2007-09-06 |

| US20090279347A1 (en) | 2009-11-12 |

| US7817460B2 (en) | 2010-10-19 |

| CN101030447A (zh) | 2007-09-05 |

| US7577014B2 (en) | 2009-08-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4865360B2 (ja) | 半導体記憶装置 | |

| JP4917767B2 (ja) | 半導体記憶装置 | |

| JP5220303B2 (ja) | スタティック・ランダム・アクセス・メモリ(sram)およびsramに供給される電圧レベルを制御する方法 | |

| JP4873182B2 (ja) | 半導体記憶装置及びその駆動方法 | |

| US7839697B2 (en) | Semiconductor memory device | |

| JP4988588B2 (ja) | 静的ランダムアクセスメモリ用のワード線ドライバ回路 | |

| JP2007193928A (ja) | 半導体記憶装置 | |

| JP2009505315A (ja) | 独立の読み書き回路を有するsramセル | |

| JP5104123B2 (ja) | 半導体メモリ | |

| JP4330516B2 (ja) | 半導体記憶装置 | |

| JP2007172715A (ja) | 半導体記憶装置およびその制御方法 | |

| JPH11219589A (ja) | スタティック型半導体記憶装置 | |

| US8345470B2 (en) | Semiconductor memory device | |

| JP4090967B2 (ja) | 半導体記憶装置 | |

| WO2012098900A1 (ja) | 半導体記憶装置 | |

| JP2008027493A (ja) | 半導体記憶装置 | |

| JP5980229B2 (ja) | 半導体記憶装置 | |

| JP4071680B2 (ja) | 半導体記憶装置 | |

| JP2008176907A (ja) | 半導体記憶装置 | |

| JP2007164888A (ja) | 半導体記憶装置 | |

| KR20090096122A (ko) | 리드 어시스트 회로 및 이를 구비한 에스램 | |

| KR100721014B1 (ko) | 반도체 메모리 장치의 제어수단 및 방법 | |

| JP2011146121A (ja) | 半導体記憶装置およびその制御方法 | |

| JP2013246858A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090202 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090202 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110809 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111007 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111101 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111110 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141118 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4865360 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |