JP4162076B2 - 半導体記憶装置 - Google Patents

半導体記憶装置 Download PDFInfo

- Publication number

- JP4162076B2 JP4162076B2 JP2002156646A JP2002156646A JP4162076B2 JP 4162076 B2 JP4162076 B2 JP 4162076B2 JP 2002156646 A JP2002156646 A JP 2002156646A JP 2002156646 A JP2002156646 A JP 2002156646A JP 4162076 B2 JP4162076 B2 JP 4162076B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- power supply

- voltage

- channel mos

- mos transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/02—Detection or location of defective auxiliary circuits, e.g. defective refresh counters

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/41—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger

- G11C11/412—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger using field-effect transistors only

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/41—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger

- G11C11/413—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing, timing or power reduction

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/41—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger

- G11C11/413—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing, timing or power reduction

- G11C11/417—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing, timing or power reduction for memory cells of the field-effect type

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/41—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger

- G11C11/413—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing, timing or power reduction

- G11C11/417—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing, timing or power reduction for memory cells of the field-effect type

- G11C11/419—Read-write [R-W] circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/02—Detection or location of defective auxiliary circuits, e.g. defective refresh counters

- G11C29/021—Detection or location of defective auxiliary circuits, e.g. defective refresh counters in voltage or current generators

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/02—Detection or location of defective auxiliary circuits, e.g. defective refresh counters

- G11C29/028—Detection or location of defective auxiliary circuits, e.g. defective refresh counters with adaption or trimming of parameters

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

- G11C5/145—Applications of charge pumps; Boosted voltage circuits; Clamp circuits therefor

- G11C5/146—Substrate bias generators

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

- G11C5/147—Voltage reference generators, voltage or current regulators; Internally lowered supply levels; Compensation for voltage drops

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/41—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C2029/0409—Online test

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Static Random-Access Memory (AREA)

Description

【発明の属する技術分野】

この発明は、スタティックメモリ(SRAM)回路が半導体チップ上に集積された半導体集積回路に関する。より特定的には、この発明はSRAM集積回路装置の動作電圧を低減する構成に関する。

【0002】

【従来の技術】

特開平6-139779号では、メモリセルのトランジスタのしきい値電圧をあらかじめ設定した基準電圧と比較し、基準電圧と同一のしきい値電圧になるような基板バイアスを発生させる回路が開示されている。特開2000-268574号では、トランジスタのしきい値検出回路と電圧検出回路から発生する信号を用いて基板バイアスを変化させ、メモリセルのトランジスタのしきい値を設定値に近付ける回路が開示されている。

【0003】

【発明が解決しようとする課題】

LSI(Large Scale Integrated circuit: 大規模集積回路)の低消費電力化およびLSI中のトランジスタの微細化により、LSI の電源電圧が低下している。たとえば、0.13μmプロセスでは、電源電圧1.2V で動作するLSIが製造される。LSIの電源電圧を下げる場合には、回路性能(回路の動作速度)を低下させないために、トランジスタのしきい値電圧を下げてトランジスタの電流を増加させている。トランジスタのしきい値電圧を下げるとSRAMメモリセルのデータ読み出し時の動作マージンであるスタティックノイズマージン(SNM)が低下し回路動作が難しくなる。さらに電源電圧が下がると読み出し時のみならず書き込み時の動作マージンが低下しSRAM回路が動作しなくなる。このため、低電源電圧のもとにおいてもSRAMメモリセルのデータ読出しおよび書込み時の動作マージンを大きくとる方法が必要となる。

【0004】

【課題を解決するための手段】

複数のスタティック型メモリセルを具備するメモリアレイと、上記メモリアレイを制御する周辺回路と、上記スタティック型メモリセル内のトランジスタのしきい値電圧の大きさに応じて上記メモリアレイの電源電圧を変換する回路とを具備させた半導体記憶装置を用いることで読み出し時、または書き込み時の動作マージンの量を増減する。動作マージンはトランジスタ性能により変化するため、LSI製造後またはLSI動作中にトランジスタのしきい値電圧を検出し最適なメモリアレイの電源電圧を決定し、最適なメモリアレイの電圧を印加する。別の手段としては、LSI製造後のトランジスタの特性を検出してメモリアレイの電源電圧を調整し、さらにメモリセルの基板電位を変化させてメモリセルを構成するトランジスタのしきい値を変化させる。また、メモリアレイの電源電圧と、メモリアレイ周辺回路の電源電圧とを分離させ、メモリアレイ内のトランジスタのしきい値電圧に応じた電圧をメモリアレイの電源電圧を印加し、それぞれに別の電圧を印加させることも可能である。

【0005】

【発明の実施の形態】

[実施例1]

図1に本発明を用いたSRAM回路とその電源構成の一例を概略的に示す。図1において、MAはSRAMのメモリセルをアレイ状に並べたメモリセルアレイ、WDはワードドライバ、ロウアドレスデコーダ等のワード線を制御する回路、SAはセンスアンプ、プリチャージ回路、カラムデコーダ等ビット線を制御する回路、DTVT1はトランジスタのしきい値電圧を検出しメモリアレイ電源電圧を発生するための参照電位信号sigref1を発生する回路、CTVAはDTVT1からの信号sigref1にしたがって電源電圧Vddに対して昇圧や降圧を行ってメモリアレイの電源電圧Vaを出力する電源回路である。メモリセルアレイMA中のwlはメモリセルのワード線、blおよびblbはビット線、Vssは接地電位線、Vbpはメモリセル内のpMOSの基板電極が接続されたノード、Vbnはメモリセル内のnMOSの基板電極が接続されたノードである。メモリセルは、1対のCMOSインバータの入力と出力が互いに接続されて構成されるフリップ・フロップ(2つのpチャネル型負荷MOSトランジスタと2つのnチャネル型駆動MOSトランジスタと有する)と、前記フリップ・フロップの2つの記憶ノードをデータ線に選択的に接続する2つのnチャネル型転送MOSトランジスタとで構成される。nチャネル型MOSトランジスタのゲート電極には、ワード線が接続され、nチャネル型駆動MOSトランジスタと、nチャネル型転送MOSトランジスタとの基板電位は、同じ信号線により制御されている。これは、nチャネル型転送MOSトランジスタと、nチャネル型駆動MOSトランジスタとを同じウェルに生成しているためであり、これにより基板電位を容易に制御することが可能となる。なお、上記のnチャネル型転送MOSトランジスタと、nチャネル型駆動MOSトランジスタとを異なるウェルに生成し、別の制御信号を与えることにより、両者のしきい値電圧の変動を別々に調整することも可能である。

参照電位発生回路DTVT1中のI1およびI2は定電流源、BOOST1は昇圧回路、Vthp1はpMOS トランジスタMP1のしきい値電圧の大きさ、Vthn1はnMOSトランジスタMN1のしきい値電圧の大きさ、Vddは周辺回路の電源電圧、nd1 はMP1のソース電極と接続されているノードである。上記pMOSトランジスタおよびnMOSトランジスタは上記メモリセル内のpMOS負荷トランジスタ、nMOS駆動トランジスタ、およびnMOS転送トランジスタと同じ工程を経たものを使用しており、酸化膜厚、不純物のインプラ濃度が同じトランジスタである。このため、DTVT1内で使用しているトランジスタのしきい値電圧とMA内で使用しているトランジスタのしきい値電圧とは一定の比例関係にある。例えばMA内のトランジスタのしきい値電圧が上昇すれば、それに応じてDTVT1のトランジスタのしきい値電圧も上昇し、MA内のトランジスタのしきい値電圧が下降すれば、同様にDTVT1のトランジスタのしきい値電圧も下降する。ゲート長、ゲート幅等をメモリセルより変えて、しきい値の変化を検出しやすくすることも可能である。これによりメモリセル自身に影響を及ぼすことなく、トランジスタのしきい値を検出することができる。電源回路CTVAにおいてVdduはメモリアレイ電源Vaの最大電圧よりも高い電圧の電源、Vssは接地電位である。DTVT1中のI1およびI2は電流量の等しい電流源であり、Vdduは、メモリアレイ電源Vaの最大電圧よりも高い電圧であり、昇圧回路BOOST1にVddを供給しVddを昇圧することによって生成される。BOOST1はキャパシタ等を用いたチャージポンプ回路で構成される回路である。ノードnd1 の電位はVdd からpMOS トランジスタMP1 のしきい値の大きさ分上昇しVdd+Vthp1となる。ノードnd1 はnMOSトランジスタMN1 のゲート電極に接続されており、それゆえにMN1のソース電極の電位はVdd+Vthp1-Vthn1となり、pMOSのしきい値電圧の大きさとnMOSのしきい値電圧の大きさの差に周辺回路の電源電圧を加えた電圧がsigref1として出力される。よって、DTVT1において、pMOSトランジスタのしきい値電圧の絶対値がnMOSトランジスタのしきい値電圧の絶対値よりも高くなった場合にはメモリアレイの電源電圧を高くし、逆にpMOSトランジスタのしきい値電圧の絶対値がnMOSトランジスタのしきい値電圧の絶対値よりも低くなった場合にはメモリアレイの電源電圧を低くすることが可能となる。通常のSRAMメモリセルにおいては、nMOSトランジスタのしきい値電圧の大きさが一定の場合pMOSトランジスタのしきい値電圧の大きさが高くなると書き込みマージンが大きくなり、pMOSトランジスタのしきい値電圧の大きさが低くなると書き込みマージンが小さくなる。したがって、図の回路によってメモリアレイ電圧を制御することによって書き込みマージンの増減を考慮したSRAM動作が実現可能である。回路DTVT1を用いると、回路動作中にLSIの温度変化等によるトランジスタのしきい値電圧の大きさの変化もメモリアレイの電源電圧に反映され、動作中のトランジスタ特性の変化による動作マージンの減少も補正することが可能となる。電源回路CTVAでは、入力された信号sigref1の電圧と出力されるVaの電圧を比較して、sigref1の電圧とVaが等しくなるようにVaが調節され、メモリアレイには周辺回路の電源電圧にpMOS のしきい値電圧の大きさを加えnMOSのしきい値電圧の大きさを引いた電圧が電源電圧として印加される。動作時にsonにハイの電位がかけられることによって、電源回路CTVAが活性化される。sonがロウの場合には回路CTVAは活性化されず、回路が動作していない場合にはsonをロウとすることで消費電力を下げることができる。回路DTVT1および回路CTVAを用いた場合には、pMOSのしきい値電圧の大きさとnMOS のしきい値電圧の大きさの電圧差と等しい電圧だけメモリアレイ電源Vaを昇圧または降圧し、pMOS のしきい値電圧の大きさがnMOSのしきい値電圧の大きさよりも高い場合に昇圧、pMOSのしきい値電圧の大きさがnMOSのしきい値電圧の大きさよりも低い場合に降圧となる。図1の回路中において、電圧Vddの電源はSRAM 回路の周辺回路WDおよびSAと参照電位を出力する回路DTVT1に供給され、また、電源電圧Vddを昇圧した電源Vdduは、VddをDTVT1内の昇圧回路で生成し参照電位を生成する回路DTVT1および電源Vaを出力する回路CTVAに供給される。CTVAで出力した電源電圧Vaの電源はメモリセルアレイMAに供給されている。回路を動作させている時には、しきい値電圧検出回路DTVT1 は、LSI 中のnMOSとpMOSのしきい値電圧の設計したしきい値電圧からのずれを検出し、最適なメモリアレイの電圧を信号sigref1としてCTVAに入力する。電源回路CTVAは、メモリアレイの電源電圧Vaが入力された信号sigref1の値となるように、Vdduを昇圧または降圧し電源Vaとしてメモリセルアレイに印加する。これによって、メモリセルの動作電圧マージンが大きくとれ低電圧での動作が可能となる。なお、図1では昇圧回路を用いてメモリアレイ周辺回路の電源電圧を昇圧しているが、DTVT1またはCTVAにダイオード接続されたトランジスタ等を用いた降圧回路を含ませ、昇圧電圧を降圧することも可能である。さらに上記メモリアレイに印加するための電圧を降圧させてから昇圧電圧を生成することも可能であることは言うまでもない。

例として、図2に周辺回路の電源電圧Vddとメモリアレイの電圧Vaの関係を示す。曲線RRは読み出し動作が律速して動作しなくなる限界の電圧を示し、RRよりもVaが高い領域(図2中上方)において読み出し動作が正常に行われ、RR よりもVaが低い領域において読み出しが正常に動作しない。また曲線WRは書き込み動作が律速して動作しなくなる限界の電圧を示し、WRよりもVddが高い領域(図2中右方)において書き込み動作が正常に行われ、WRよりもVddが低い領域において書き込みが正常に動作しない。読み出しおよび書き込みの動作ができるのは図中の網かけ部分である。よって、図2の性能のメモリセルを設計しVdd=0.4Vで動作させようとした場合にはVa=0.5V程度に昇圧した点、つまり図中の黒点の電圧において動作させると最大の電圧マージンがとれる。しかし製造時にトランジスタの性能がばらついてメモリセルの特性が図3で示す状態となった場合には、Va=0.5Vではほとんど電圧マージンがなくなり、この状態では、Vaをさらに昇圧した電圧0.6V程度で動作させる場合に電圧マージンが大きくとれることがわかる。よって、図1の回路においてVaを0.6Vに変更することによりSRAM 回路の動作マージンが大きくなる。また図3とは異なりメモリセルの特性が図4で示す状態となった場合には、Va>0.5Vの領域ではメモリセルで書き込みが正常に行われず、VaをVddよりも降圧し電圧0.35V程度で動作させる場合に電圧マージンが大きくとれることがわかる。この場合にも図1の回路においてVaを0.35Vに変更することによりSRAM回路の動作マージンが大きくなる。このように本発明では、製造工程時においてばらついたトランジスタの性能を、トランジスタのしきい値が検出可能な回路等を同一チップまたはウェハ上に設けることによって評価し、メモリセルに使用されているトランジスタの特性を考慮した電源電圧をメモリアレイに供給することが可能となる。

図5にDTVT1回路の別の一例を示す。図5の回路は図1中の回路DTVT1とほぼ同等であり、Vddより高い電位のVdduの生成の方法が異なる。現在、一般に製造されているLSIにおいては、内部回路用の電圧と入出力回路用の2種類の電源を使用して動作している。図5において、Vddは内部回路用の電源を、Vccは入出力回路用の電源を表し、VccはVddよりも高い電圧である。DBST1は降圧回路であり、ダイオード接続したトランジスタ等を用いてVccを降圧してVddよりも高い電圧Vdduを生成している。また、Vccの電圧がVddと比較してそれほど大きくない場合には降圧回路を用いずVccをそのままVdduとして用いることも可能である。図6以降の図の回路においてもVdduが用いられているが、Vdduの生成方法は図1中の回路DTVT1または図5のどちらを用いてもよい。また図1中のDTVT1 と図5の回路とを同時に用いる場合には、DTVT1または図5の昇圧または降圧回路を同時に使用することも可能である。

また、図5については、内部回路用の電源Vddと入出力用電源Vccとの2種の電源を使用しているが、入出力用電源Vccにさらに降圧回路を接続して内部回路用の電源を用いてもよい。

図6に図1の回路を用いた場合のシステムLSI全体の構成例の概略を電源の関係も含めて示す。ここでシステムLSIとは、現在広く製造されているメモリ回路とロジック回路とが混載されている回路である。図6では、システムLSIの回路構成を示すが、ロジック回路を含まないメモリLSIについての構成もロジック回路を除いて考えれば同等と考えることができる。図6において、システムLSIであるCHIPは、データに所定の処理を実行するロジック回路LGCと、データを記憶するスタティックメモリ回路SRMと、トランジスタのしきい値電圧を検出する回路DTVT1と、メモリアレイの電源を生成する回路CTVAとで構成されている。SRAM回路SRMは、メモリセルアレイMAと、周辺回路WDとSAで構成されている。内部回路の電源電圧VddはLSI外部から入力され、LGC、WD、SA、CTVA、DTVT1に供給されている。入出力回路用のVddよりも高い電圧Vccは、外部から入力されIOに供給されるとともに、CTVAおよびDTVT1に供給され、その電圧を用いてメモリアレイ用のVddとは異なった電源電圧がCTVAにおいて生成されメモリアレイMAに供給される。

図14に本発明を用いたSRAM回路の電源配線のレイアウトの例を示す。図14において、NETDDは内部回路の電源ネットであり電圧はVdd、NETAはメモリセルアレイの電源ネットであり電圧はVa、MAはSRAMメモリセルアレイ、PERI1およびPERI2はSRAM回路中のメモリセル以外の回路でワードドライバ、センスアンプ等を含む回路、CTVAは電源電圧Vddの電源に対して昇降圧を行いメモリアレイの電源電圧Vaを生成する昇降圧回路である。メモリアレイの電源ネットNETAはメモリアレイ内のメモリセルに電源Vaを供給し、周辺回路の電源ネットNETDDからは分離されており昇降圧回路CTVAおよびメモリアレイMAにのみ接続されている。

また、実施例1においてはメモリアレイの高電位側のp負荷MOSトランジスタのソースノードの電位を変化させてメモリアレイに最適な電圧を印加する方法を提示したが、低電位側のn駆動MOSトランジスタのソースノードの接地電位Vssを昇圧または降圧することも可能であり、このことは実施例2以降についても同様である。

[実施例2]

図7に本発明を用いたSRAM回路とその電源構成の一例を概略的に示す。図7において、MAはSRAMのメモリセルをアレイ状に並べたメモリセルアレイ、WDはワードドライバ、ロウアドレスデコーダ等のワード線を制御する回路、SAはセンスアンプ、プリチャージ回路、カラムデコーダ等ビット線を制御する回路、BOOST2はVdd を昇圧した電圧Vdduを生成する昇圧回路、CTVAは参照電位信号sigref2にしたがってメモリアレイ用の電源電圧Vaを出力する電源回路、DREG1は参照電位選択信号によりswcont1によって指示された参照電位を出力する回路、DTVT2はトランジスタのしきい値電圧の大きさにしたがって参照電位選択信号swcont1を出力する回路である。この回路は、動作中にはしきい値電圧検出回路DTVT2でnMOSトランジスタおよびpMOSトランジスタのしきい値電圧の大きさから最適なメモリアレイの電圧を選択する信号swcont1を出力し、参照電位出力回路DREG1においてswcont1によって最適なメモリアレイの電圧を参照電位信号sigref2として出力する。電源回路CTVAは、参照電位信号sigref2と等しい電圧をメモリアレイ電源Vaとして出力する。これによって、メモリセルの動作電圧マージンが大きくとれ低電圧での動作が可能となる。

図8に参照電位を出力する回路DREG1の一例を示す。図8において、RREF1からRREF6は抵抗、SW1からSW5は制御信号swcont1によって開閉が制御されるスイッチである。図8にはRREF1〜RREF6の6個の抵抗が記述されているが、実際には複数の最適な数の抵抗が使用される。図8において、抵抗RREF1からRREF6はVdduとVss間の電位を分割し、メモリアレイに印加する可能性のある電位を生成する。抵抗で分割されたノードはスイッチSW1からSW5 を介して出力ノードと接続されており、トランジスタのしきい値電圧の大きさを検出して生成される信号swcont1によって信号sigref2の電位が決定され出力される。信号swcont1はスイッチSW1からSW5の個数ビットの信号であり、SWC1からSWC5は信号swcont1を転送するバスである。

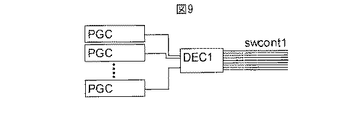

図9に制御回路DTVT2の構成の一例を示す。図9において、PGCはプログラム素子、DEC1はPGCの個数ビット分のデータをデコードし制御信号swcont1に変換する回路である。PGCにはメタルヒューズやフラッシュメモリ等の不揮発性のプログラム素子を用い、LSI製造後のテスト時に出来上がったLSIのトランジスタ特性を測定し、最適なメモリアレイ電圧Vaを決定し、その電圧に制御する値をPGC に書き込むことによって、LSI動作時に最適なメモリアレイ電圧でLSIを動作させる。図9の回路では、不揮発なプログラム素子を用いているため製造後にトランジスタ特性を記憶させる工程が必要となる。

プログラム素子ではトランジスタのしきい値電圧の大きさにしたがって参照電位を制御するデータを記憶するが、記憶回路のかわりにトランジスタのしきい値電圧の大きさを検出する回路と比較するための参照しきい値電圧の大きさを出力する回路および2つの電圧の比較回路の組合せでも同等の動作が可能である。これらの回路を用いた場合、電源投入とともにトランジスタのしきい値電圧の大きさと設計された参照しきい値電圧の大きさが比較され比較結果に従って最適なメモリアレイ電圧となるように制御信号swcont1が生成される。

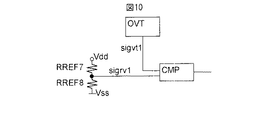

図10に図9中のプログラム回路PGCを置き換える回路の例を示す。図10において、OVTはMOSトランジスタのしきい値電圧の大きさを検知して信号sigvt1として出力する回路、CMPは入力された2つの信号の大小を比較してハイかロウの信号を出力する回路である。図10の回路では、CMPは抵抗RREF7およびRREF8によってしきい値電圧比較用の参照電位を生成し、比較用の参照電位と実際のトランジスタのしきい値電圧の大きさを大小を比較し結果を出力することによってトランジスタのしきい値電圧の大きさを検出する。信号sigvt1は実際のしきい値電圧の大きさを出力する必要はなくしきい値電圧の大きさにしたがって変化する電圧を出力する回路であればよく、その電圧にしたがってsigrv1の電位が決定され、その電位によってRREF7およびRREF8の抵抗値が決定される。例えば、図10の回路によってトランジスタのしきい値電圧の大きさが0.5Vよりも高いまたは低いかを判別する必要がある場合、トランジスタのしきい値電圧の大きさの1/2の電位をOVTがsigvt1として出力する回路であれば、RREF7およびRREF8の抵抗値をsigrv1の電位が0.25Vとなるように設計する。回路動作時にはsigrv1の電位は0.25Vとなり、sigvt1にはトランジスタのしきい値電圧の大きさの1/2の電位が出力されるため、sigvt1が0.25Vより高いすなわちMOSトランジスタのしきい値電圧の大きさが0.5Vよりも高ければCMPからハイが出力され、MOSトランジスタのしきい値電圧の大きさが0.5Vよりも低ければCMPからロウが出力される。よって、図10の回路はトランジスタのしきい値電圧の大きさによってデータを記憶する回路を置き換えることが可能である。

プログラム回路を用いた回路の場合は、LSI製造後にトランジスタのしきい値電圧の大きさ等の特性を測定しプログラム回路にその特性を保存する。したがって、LSI製造時の特性ばらつきを補正できるが、LSI動作時の温度等によるトランジスタの特性ばらつきは補正することができない。しかし、製造後にしきい値電圧の大きさとメモリアレイの電圧の関係を決定できるため、設計時と異なる条件でメモリアレイの電源電圧を決定することが可能となる。図10の回路を用いた場合には、LSIの動作中にトランジスタ特性を検出しているため、温度変化等によるLSI動作中のトランジスタの特性の変化も補正することが可能となり、動作マージンを大きく補償することが可能である。

[実施例3]

図11に本発明を用いたSRAM回路の一例の概略を示す。図11において、MAはSRAMのメモリセルをアレイ状に並べたメモリセルアレイ、WDはワードドライバ、ロウアドレスデコーダ等のワード線を制御する回路、SAはセンスアンプ、プリチャージ回路、カラムデコーダ等ビット線を制御する回路、DTVT3はトランジスタのしきい値電圧の大きさを検出しメモリアレイ電源電圧を発生するための参照電位信号sigref3およびメモリアレイの基板電位を発生するための参照電位信号sigref4 およびsigref5を発生する回路、CTVAはDTVT3からの信号sigref3にしたがって電源電圧Vddに対して昇圧または降圧を行ってメモリアレイの電源電圧Vaを出力する電源回路、CTVBBはDTVT3からの信号sigref4およびsigref5にしたがってメモリアレイの基板電位であるVbnおよびVbpを発生する回路である。VbnはメモリセルのnMOSトランジスタの基板であるpウエルの電位、VbpはメモリセルのpMOSトランジスタの基板であるnウエルの電位である。

図12に参照電位sigref3からsigref5を発生する回路DTVT3の構成の一例を示す。PGVTNおよびPGVTPはnMOSトランジスタおよびpMOSトランジスタのしきい値電圧の大きさを記憶する回路であり、nMOSのしきい値電圧の大きさを信号sigvtn、pMOSのしきい値電圧の大きさを信号sigvtpとして出力する。記憶回路PGVTNおよびPGVTPには、メモリの欠陥救済等で用いられているヒューズ回路やフラッシュメモリなどの不揮発性の記憶回路が用いられ、LSI製造後のLSIテスト時にMOSトランジスタのしきい値電圧の大きさを測定し記憶回路にデータを書き込む。DEC2はnMOSおよびpMOSのしきい値電圧の大きさである信号sigvtnとsigvtpをデコードしDREG2を制御する信号swcont2を生成する。DREG2は図8と同等の回路であり、複数の抵抗によってVdduとVss間の電位を分割し、制御信号swcont2によって分割して生成された電位のうち適切な電位を選択しメモリアレイの電源電圧Vaを生成するための参照電位信号sigref3として出力する。DEC3はnMOSのしきい値電圧の大きさである信号sigvtnをデコードしDREG3を制御する信号swcont3を生成する。DREG3は図8と同等の回路であり、複数の抵抗によってVddと-Vdd間の電位を分割し、制御信号swcont3によって分割して生成された電位のうち適切な電位を選択し、メモリアレイのnMOSの基板電位Vbnを生成するための参照電位信号sigref4として出力する。設計時にnMOSの基板電位Vbnを0Vに設定していた場合、デコーダ回路DEC3はnMOSのしきい値電圧の大きさが設計値よりも高くなっている場合には参照電位を0Vよりも高くなるように制御し順方向の基板バイアスをnMOSに印加してしきい値電圧を下げる。逆にnMOS のしきい値電圧の大きさが設計値より低くなっている場合には参照電位を0Vよりも低くなるように制御し逆方向の基板バイアスをnMOS に印加してしきい値電圧をあげる。-Vddの電位は一般的に使用されている基板バイアスを制御する回路同様チャージポンプ等を用いて比較的容易に生成することが可能であり、SRAM 回路とは別に同一LSI上に基板バイアスを制御する回路が搭載されている場合には-Vdd の電位をその回路中で生成していると考えられ、その電位を使用することも可能である。DEC4はpMOSのしきい値電圧である信号sigvtp をデコードしDREG4を制御する信号swcont4を生成する。DREG4は図8と同等の回路であり、複数の抵抗によってVdduとVss間の電位を分割し、制御信号swcont4によって分割して生成された電位のうち適切な電位を選択し、メモリアレイのpMOSの基板電位Vbp を生成するための参照電位信号sigref5として出力する。設計時にpMOSの基板電位VbpをVddに設定していた場合、デコーダ回路DEC4はpMOSのしきい値電圧の大きさが設計値よりも高くなっている場合には参照電位をVddよりも低くなるように制御し順方向の基板バイアスをpMOSに印加してしきい値電圧を下げる。逆にpMOSのしきい値電圧が設計値より低くなっている場合には参照電位をVddよりも高くなるように制御し逆方向の基板バイアスをpMOS に印加してしきい値電圧をあげる。

図11および図12の回路を用いることによって、基板バイアスを制御することによって製造したLSI中のメモリセルの特性が図3または図4の状態になった場合にも、図2の状態に近付けることが可能となり、さらにメモリアレイの電源電圧をもっとも動作マージンの大きい電圧にすることが可能となる。

図12において、回路PGVTNおよびPGVTPは不揮発性の記憶素子を用いた回路としLSI製造後のLSIテスト時にMOSトランジスタのしきい値電圧を測定して書き込む回路としたが、図13のような回路で置き換えることも可能である。図13において、OVTはMOSトランジスタのしきい値電圧の大きさを検知して信号sigvt2として出力する回路、CMP1、CMP2は入力された2つの信号の大小を比較してハイかロウの信号を出力する回路である。この回路は、図13においては、複数の抵抗によってしきい値電圧比較用の参照電位を生成し、比較用の参照電位と実際のトランジスタのしきい値電圧の大きさの大小を比較し結果を出力することによってメモリアレイの電源電圧や基板バイアスを制御するための信号とする。信号sigvt2は実際のしきい値電圧を出力する必要はなくしきい値電圧にしたがって変化する電圧を出力する。

例えばsigvtnが2ビットの信号の場合、図13の回路の動作は以下のとおりである。トランジスタのしきい値電圧が設計値よりも高い場合にはsigvt2の電位がsigrv2およびsigrv3の電位よりも高くなり出力信号sigvtnとして"00"が出力される。トランジスタのしきい値電圧が設計値に近い値の場合にはsigvt2の電位がsigrv2の電位よりも低くsigrv3の電位よりも高くなり出力信号sigvtnとして"10"が出力される。トランジスタのしきい値電圧が設計値よりも低い場合にはsigvt2の電位がsigrv2およびsigrv3の電位よりも低くなり出力信号sigvtnとして"11"が出力される。この例では、sigvtnが2ビットの場合であったため、しきい値電圧の大きさの状態は3通りの状態で検出されたが、分割する抵抗および比較回路を増やすことによりさらに多くの状態を検出することが可能となり、細かくメモリセルアレイの電源電圧および基板バイアスを制御することが可能となる。

プログラム回路を用いた回路の場合は、LSI製造後にトランジスタのしきい値電圧等の特性を測定しプログラム回路にその特性を保存するため、LSI製造時の特性ばらつきを補正できるが、LSI動作時の温度等によるトランジスタの特性ばらつきは補正することができない。トランジスタのしきい値電圧は動作温度にも大きく影響を受けて変化するが、図13の回路を用いた場合には、LSIの動作中にトランジスタ特性を検出しているため、温度変化等によるLSI動作中のトランジスタの特性の変化をメモリアレイの電源電圧および基板バイアスを用いて補償し、動作マージンを大きく補償する。

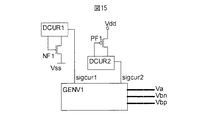

図15に本発明を用いたSRAM回路の電源制御方式の一例の概略図を示す。図15において、NF1はnチャネル型トランジスタ、PF1はpチャネル型トランジスタ、DCUR1およびDCUR2はトランジスタの電流を検出する回路、GENV1は入力された信号により3つの電源電圧を変化させる回路である。図15の回路の動作は以下の通りである。nチャネル型トランジスタNF1は、ソース電極が接地電位Vssのノードに接続されており、電流検知回路DCUR1はNF1のゲート電圧を制御してドレイン電極の電流を検出し、検出した電流値から電源電圧変化させる回路GENV1を制御する信号sigcur1を発生する。pチャネル型トランジスタPF1は、ソース電極が電源電位Vddのノードに接続されており、電流検知回路DCUR2はPF1のゲート電圧を制御してドレイン電極の電流を検出し、検出した電流値から電源電圧変化させる回路GENV1を制御する信号sigcur2を発生する。GENV1は、信号sigcur1およびsigcur2によって、メモリセルの電源電圧であるVaおよびnチャネル型トランジスタの基板電位Vbnおよびpチャネル型トランジスタの基板電位Vbpを制御する。これによって、nチャネル型およびp チャネル型トランジスタのしきい値電圧と関係する電流特性にしたがって、3種類の電源電圧を調整することが可能となる。

【0006】

【発明の効果】

本発明によれば、SRAM回路の動作マージンを増加させ動作マージンが低減する条件下とくに0.5V以下の低電圧の電源下でもSRAM回路を動作させることが可能となる。

【図面の簡単な説明】

【図1】本発明が適用されたSRAM回路の回路構成および電源構成の概略図である。

【図2】 SRAM回路が動作する周辺回路の電源電圧とメモリセルアレイの電源電圧の関係を図示したグラフである。

【図3】トランジスタの特性が図2の特性から変化した時のSRAM回路が動作する周辺回路の電源電圧とメモリセルアレイの電源電圧の関係を図示したグラフである。

【図4】トランジスタの特性が図2および図3の特性から変化した時のSRAM回路が動作する周辺回路の電源電圧とメモリセルアレイの電源電圧の関係を図示したグラフである。

【図5】図1中の電源回路CTVAの例を示した回路図である。

【図6】本発明を適用したシステムLSIの回路配置および電源配置の概略図である。

【図7】本発明が適用されたSRAM回路の回路構成および電源構成の図1とは異なる構成の概略図である。

【図8】図7中の参照電位出力回路DREG1の例を示した回路図である。

【図9】図7中のMOSトランジスタのしきい値電圧によって参照電位出力回路DREG1を制御する信号を出力する回路DTVT2の例を示した概略図である。

【図10】図9中のプログラム回路PGCを置き換えるトランジスタのしきい値検出回路の例を示した概略図である。

【図11】本発明が適用されたSRAM回路の回路構成、電源構成および基板電位を制御する回路の概略図である。

【図12】図9中のトランジスタのしきい値電圧を検出しメモリアレイ電源電圧を発生するための参照電位信号およびメモリアレイの基板電位を発生するための参照電位信号を発生する回路の概略図である。

【図13】トランジスタのしきい値検出回路の例を示した概略図である。

【図14】 SRAM回路の電源配線のレイアウトの例を示したレイアウト図である。

【図15】 SRAM回路の電源制御方式の概略図である。

【符号の説明】

Vdd…メモリ周辺回路電源電圧、Vss…接地電位、Va…メモリアレイ電源電圧、WR…読み出し律速線、RR…書き込み律速線、CTVA…電源回路、DTVT1〜DTVT3…参照電位生成回路、MA…メモリセルアレイ、WD・SA…SRAM周辺回路、wl…ワード線、bl・blb…ビット線、sigref1〜sigref5…参照電位、BOOST1…昇圧回路、DBST1…降圧回路、Vcc…入出力回路用電源電圧、Vddu…Vddよりも高い電圧、I1・I2…定電流源、MN1…nMOSトランジスタ、MP1…pMOSトランジスタ、nd1…ノード、Vthn1…nMOSトランジスタのしきい値電圧、Vthp1…pMOSトランジスタのしきい値電圧、son…電源回路活性化信号、IO…入出力回路、LGC…ロジック回路、SRM…SRAM回路、RREF1〜RREF10…抵抗素子、SW1〜SW5…スイッチ、DREG1〜DREG4…参照電位出力回路、swcont1〜swcont4…参照電位選択信号、PGC…記憶回路、DEC1〜DEC4…デコーダ回路、Vbn…nMOS基板バイアス、Vbp…pMOS基板バイアス、CTVBB…基板バイアス発生回路、PGVTN…nMOSのしきい値電圧記憶回路、PGVTP…pMOSのしきい値電圧記憶回路、sigvtn・sigvtp・sigvt1・sigvt2…トランジスタのしきい値出力信号、OVT…トランジスタしきい値電圧検出回路、CMP…電圧比較回路、sigrv1〜sigrv3…参照電位生成用信号、NETDD・NETA…電源ネット、PERI1・PERI2…SRAM周辺回路、DCUR1・DCUR2…電流量検知回路、NF1…nチャネル型トランジスタ、PF1…pチャネル型トランジスタ、sigcur1・sigcur2…電流量を表す信号、GENV1…電源電圧調整回路。

Claims (12)

- 複数のスタティック型メモリセルを具備するメモリアレイと、

上記メモリアレイを制御する周辺回路と、

上記メモリアレイの第1電源電圧を形成する第1回路とを具備し、

上記スタティック型メモリセルは、

第1pチャネル型MOSトランジスタと第1nチャネル型MOSトランジスタとにより構成された第1CMOSインバータ回路と、第2pチャネル型MOSトランジスタと第2nチャネル型MOSトランジスタとにより構成された第2CMOSインバータ回路とを含み、

上記第1CMOSインバータ回路と第2CMOSインバータ回路は、入力と出力とが交差接続され、

上記第1回路は、上記第1,第2pチャネル型MOSトランジスタのしきい値電圧の絶対値が上記第1,第2nチャネル型MOSトランジスタのしきい値電圧の絶対値よりも高くなった場合には、上記第1電源電圧を上記周辺回路の第2電源電圧よりも高くし、上記第1,第2pチャネル型MOSトランジスタのしきい値電圧の絶対値が上記第1,第2nチャネル型MOSトランジスタのしきい値電圧の絶対値よりも低くなった場合には、上記第1電源電圧を上記第2電源電圧よりも低くすることを特徴とする半導体記憶装置。 - 請求項1において、

上記第1回路は、上記第2電源電圧の昇圧電圧を形成する昇圧回路を具備し、上記昇圧電圧を降圧して上記第1電源電圧を形成することを特徴とする半導体記憶装置。 - 請求項1において、

上記第2電源電圧よりも高い第3電源電圧で動作する入出力回路を更に有し、

上記第1回路は、上記第3電源電圧を降圧して上記第1電源電圧を形成することを特徴とする半導体記憶装置。 - 請求項1において、

上記第1回路は、

上記スタティック型メモリセル内の上記第1、第2pチャネル型MOSトランジスタのしきい値電圧の大きさに応じてしきい値電圧の大きさが変化する第3pチャネル型MOSトランジスタと、上記第1、第2nチャネル型MOSトランジスタのしきい値電圧の大きさに応じてしきい値電圧の大きさが変化する第3nチャネル型MOSトランジスタとを有し、

上記第2電源電圧に対して上記第3pチャネル型MOSトランジスタのしきい値電圧の大きさ分だけ高くした電圧から上記第3nチャネル型MOSトランジスタのしきい値電圧の大きさ分だけ低くした基準電圧を形成し、

上記基準電圧を電力増幅して上記第1電源電圧を形成することを特徴とする半導体記憶装置。 - 請求項1において、

上記スタティック型メモリセルは、アドレス選択用の第4及び第5nチャネル型MOSトランジスタを有することを特徴とする半導体記憶装置。 - 複数のスタティック型メモリセルを具備するメモリアレイと、

上記メモリアレイを制御する周辺回路と、

上記メモリアレイの第1電源電圧を形成する第1回路とを具備し、

上記スタティック型メモリセルは、

第1pチャネル型MOSトランジスタと第1nチャネル型MOSトランジスタとに より構成された第1CMOSインバータ回路と、第2pチャネル型MOSトランジスタと第2nチャネル型MOSトランジスタとにより構成された第2CMOSインバータ回路とを含み、

上記第1CMOSインバータ回路と第2CMOSインバータ回路は、入力と出力とが交差接続され、

上記第1回路は、

上記周辺回路に供給される第2電源電圧よりも高い電源電圧を分圧して複数の基準電圧を形成する基準電圧発生回路と、

上記第1,第2pチャネル型MOSトランジスタのしきい値電圧と上記第1,第2nチャネル型MOSトランジスタのしきい値電圧との大きさを検出して、上記複数の基準電圧の中から最適な上記第1電源電圧に対応した基準電圧の選択信号を形成するしきい値電圧検出回路と、

上記選択信号により上記基準電圧を出力する参照電位出力回路と、

上記参照電位出力回路の出力信号に対応して上記第1電源電圧を形成する電源回路とを有することを特徴とする半導体記憶装置。 - 複数のスタティック型メモリセルを具備するメモリアレイと、

上記メモリアレイを制御する周辺回路と、

上記メモリアレイの第1電源電圧を形成する第1回路とを具備し、

上記スタティック型メモリセルは、

第1pチャネル型MOSトランジスタと第1nチャネル型MOSトランジスタとにより構成された第1CMOSインバータ回路と、第2pチャネル型MOSトランジスタと第2nチャネル型MOSトランジスタとにより構成された第2CMOSインバータ回路とを含み、

上記第1CMOSインバータ回路と第2CMOSインバータ回路は、入力と出力とが交差接続され、

上記第1回路は、

上記周辺回路に供給される第2電源電圧よりも高い電源電圧を分圧して複数の基準電圧を形成する基準電圧発生回路と、

上記第1,第2pチャネル型MOSトランジスタのしきい値電圧と上記第1,第2nチャネル型MOSトランジスタのしきい値電圧に対応してプログラムされたプログラム素子の記憶情報に従って上記複数の基準電圧の中から最適な上記第1電源電圧に対応した基準電圧の選択信号を形成する制御回路と、

上記選択信号により上記基準電圧を出力する参照電位出力回路と、

上記参照電位出力回路の出力信号に対応して上記第1電源電圧を形成する電源回路とを有することを特徴とする半導体記憶装置。 - 複数のスタティック型メモリセルを具備するメモリアレイと、

上記メモリアレイを制御する周辺回路と、

上記メモリアレイの第1電源電圧を形成する第1回路とを具備し、

上記スタティック型メモリセルは、

第1pチャネル型MOSトランジスタと第1nチャネル型MOSトランジスタとにより構成された第1CMOSインバータ回路と、第2pチャネル型MOSトランジスタと第2nチャネル型MOSトランジスタとにより構成された第2CMOSインバータ回路とを含み、

上記第1CMOSインバータ回路と第2CMOSインバータ回路は、入力と出力とが交差接続され、

上記第1回路は、

上記第1,第2pチャネル型MOSトランジスタのしきい値電圧と上記第1,第2nチャネル型MOSトランジスタのしきい値電圧に対応して記憶情報がプログラムされた プログラム素子と、

上記プログラム素子の記憶情報に従って複数の第1基準電圧の中から最適な上記第1電源電圧に対応した第1基準電圧の第1選択信号を形成する第1制御回路と、

上記プログラム素子の記憶情報に従って複数の第2基準電圧の中から最適な上記メモリアレイのnチャネル型MOSトランジスタが形成される第1ウェル電位に対応した第2基準電圧の第2選択信号を形成する第2制御回路と、

上記複数の第1基準電圧を形成し、上記第1選択信号に従って上記第1基準電圧を出力する第1参照電位出力回路と、

上記複数の第2基準電圧を形成し、上記第2選択信号に従って上記第2基準電圧を出力する第2参照電位出力回路と、

上記第1,第2参照電位出力回路の出力信号に対応して上記第1電源電圧と上記第1ウェル電圧とを形成する電源回路とを有することを特徴とする半導体記憶装置。 - 複数のスタティック型メモリセルを具備するメモリアレイと、

上記メモリアレイを制御する周辺回路と、

上記メモリアレイの第1電源電圧を形成する第1回路とを具備し、

上記スタティック型メモリセルは、

第1pチャネル型MOSトランジスタと第1nチャネル型MOSトランジスタとにより構成された第1CMOSインバータ回路と、第2pチャネル型MOSトランジスタと第2nチャネル型MOSトランジスタとにより構成された第2CMOSインバータ回路とを含み、

上記第1CMOSインバータ回路と第2CMOSインバータ回路は、入力と出力とが交差接続され、

上記第1回路は、

上記第1,第2pチャネル型MOSトランジスタのしきい値電圧と上記第1,第2nチャネル型MOSトランジスタのしきい値電圧に対応して記憶情報がプログラムされたプログラム素子と、

上記プログラム素子の記憶情報に従って複数の第1基準電圧の中から最適な上記第1電源電圧に対応した第1基準電圧の第1選択信号を形成する第1制御回路と、

上記プログラム素子の記憶情報に従って複数の第3基準電圧の中から最適な上記メモリアレイのpチャネル型MOSトランジスタが形成される第2ウェル電位に対応した第3基準電圧の第3選択信号を形成する第3制御回路と、

上記複数の第1基準電圧を形成し、上記第1選択信号に従って上記第1基準電圧を出力する第1参照電位出力回路と、

上記複数の第3基準電圧を形成し、上記第3選択信号に従って上記第3基準電圧を出力する第3参照電位出力回路と、

上記第1,第3参照電位出力回路の出力信号に対応して上記第1電源電圧と上記第2ウェル電圧とを形成する電源回路とを有することを特徴とする半導体記憶装置。 - 複数のスタティック型メモリセルを具備するメモリアレイと、

上記メモリアレイを制御する周辺回路と、

上記メモリアレイの第1電源電圧を形成する第1回路とを具備し、

上記スタティック型メモリセルは、

第1pチャネル型MOSトランジスタと第1nチャネル型MOSトランジスタとにより構成された第1CMOSインバータ回路と、第2pチャネル型MOSトランジスタと第2nチャネル型MOSトランジスタとにより構成された第2CMOSインバータ回路とを含み、

上記第1CMOSインバータ回路と第2CMOSインバータ回路は、入力と出力とが交差接続され、

上記第1回路は、

上記第1,第2pチャネル型MOSトランジスタのしきい値電圧と上記第1,第2nチャネル型MOSトランジスタのしきい値電圧に対応して記憶情報がプログラムされたプログラム素子と、

上記プログラム素子の記憶情報に従って複数の第1基準電圧の中から最適な上記第1電源電圧に対応した第1基準電圧の第1選択信号を形成する第1制御回路と、

上記プログラム素子の記憶情報に従って複数の第2基準電圧の中から最適な上記メモリアレイのnチャネル型MOSトランジスタが形成される第1ウェル電位に対応した第2基準電圧の第2選択信号を形成する第2制御回路と、

上記プログラム素子の記憶情報に従って複数の第3基準電圧の中から最適な上記メモリアレイのpチャネル型MOSトランジスタが形成される第2ウェル電位に対応した第3基準電圧の第3選択信号を形成する第3制御回路と、

上記複数の第1基準電圧を形成し、上記第1選択信号に従って上記第1基準電圧を出力する第1参照電位出力回路と、

上記複数の第2基準電圧を形成し、上記第2選択信号に従って上記第2基準電圧を出力する第2参照電位出力回路と、

上記複数の第3基準電圧を形成し、上記第3選択信号に従って上記第3基準電圧を出力する第3参照電位出力回路と、

上記第1、第2及び第3参照電位出力回路の出力信号に対応して上記第1電源電圧、上記第1ウェル電位及び上記第2ウェル電圧を形成する電源回路とを有することを特徴とする半導体記憶装置。 - 請求項1ないし11のいずれか1において、

上記周辺回路は、センスアンプとワードドライバのいずれか少なくとも1つを含むことを特徴とする半導体記憶装置。 - 請求項1ないし12のいずれか1において、

上記メモリアレイ及び周辺回路は、それぞれの電源電圧が0.5V以下となるように設計されることを特徴とする半導体記憶装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002156646A JP4162076B2 (ja) | 2002-05-30 | 2002-05-30 | 半導体記憶装置 |

| US10/445,919 US6862227B2 (en) | 2002-05-30 | 2003-05-28 | Semiconductor memory device having the operating voltage of the memory cell controlled |

| US11/049,243 US6954396B2 (en) | 2002-05-30 | 2005-02-03 | Semiconductor memory device having the operating voltage of the memory cell controlled |

| US11/204,024 US7333385B2 (en) | 2002-05-30 | 2005-08-16 | Semiconductor memory device having the operating voltage of the memory cell controlled |

| US12/003,970 US7920438B2 (en) | 2002-05-30 | 2008-01-04 | Semiconductor memory device having the operating voltage of the memory cell controlled |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002156646A JP4162076B2 (ja) | 2002-05-30 | 2002-05-30 | 半導体記憶装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004005777A JP2004005777A (ja) | 2004-01-08 |

| JP2004005777A5 JP2004005777A5 (ja) | 2005-10-06 |

| JP4162076B2 true JP4162076B2 (ja) | 2008-10-08 |

Family

ID=29561497

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002156646A Expired - Lifetime JP4162076B2 (ja) | 2002-05-30 | 2002-05-30 | 半導体記憶装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (4) | US6862227B2 (ja) |

| JP (1) | JP4162076B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9595307B2 (en) | 2014-05-22 | 2017-03-14 | Samsung Electronics Co., Ltd. | Volatile memory device and system-on-chip including the same |

Families Citing this family (42)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7497827B2 (en) * | 2004-07-13 | 2009-03-03 | Dexcom, Inc. | Transcutaneous analyte sensor |

| JP4162076B2 (ja) * | 2002-05-30 | 2008-10-08 | 株式会社ルネサステクノロジ | 半導体記憶装置 |

| US7474553B2 (en) * | 2002-09-02 | 2009-01-06 | Nxp B.V. | Device writing to a plurality of rows in a memory matrix simultaneously |

| JP4290457B2 (ja) * | 2003-03-31 | 2009-07-08 | 株式会社ルネサステクノロジ | 半導体記憶装置 |

| FR2877143A1 (fr) * | 2004-10-25 | 2006-04-28 | St Microelectronics Sa | Cellule de memoire volatile preenregistree |

| US7085175B2 (en) * | 2004-11-18 | 2006-08-01 | Freescale Semiconductor, Inc. | Word line driver circuit for a static random access memory and method therefor |

| US7394708B1 (en) * | 2005-03-18 | 2008-07-01 | Xilinx, Inc. | Adjustable global tap voltage to improve memory cell yield |

| US7099230B1 (en) * | 2005-04-15 | 2006-08-29 | Texas Instruments Incorporated | Virtual ground circuit for reducing SRAM standby power |

| US20060259840A1 (en) | 2005-05-12 | 2006-11-16 | International Business Machines Corporation | Self-test circuitry to determine minimum operating voltage |

| JP4917767B2 (ja) * | 2005-07-01 | 2012-04-18 | パナソニック株式会社 | 半導体記憶装置 |

| US7872927B2 (en) * | 2005-09-27 | 2011-01-18 | Nec Corporation | Semiconductor memory device and method of controlling power source |

| JP4822791B2 (ja) * | 2005-10-04 | 2011-11-24 | ルネサスエレクトロニクス株式会社 | 半導体記憶装置 |

| FR2895556A1 (fr) * | 2005-12-26 | 2007-06-29 | St Microelectronics Sa | Dispositif de stockage d'informations a memoires sram et procede de mise en oeuvre |

| JP4865360B2 (ja) * | 2006-03-01 | 2012-02-01 | パナソニック株式会社 | 半導体記憶装置 |

| JP2007328900A (ja) * | 2006-05-09 | 2007-12-20 | Matsushita Electric Ind Co Ltd | スタティック型半導体記憶装置 |

| US7512908B2 (en) * | 2006-06-09 | 2009-03-31 | International Business Machines Corporation | Method and apparatus for improving SRAM cell stability by using boosted word lines |

| US20070286745A1 (en) * | 2006-06-09 | 2007-12-13 | Maynard Chance | Integrated mixing pump |

| US7292485B1 (en) | 2006-07-31 | 2007-11-06 | Freescale Semiconductor, Inc. | SRAM having variable power supply and method therefor |

| US7679947B2 (en) * | 2006-08-02 | 2010-03-16 | Taiwan Semiconductor Manufacturing Co., Ltd. | Semiconductor devices with source and bulk coupled to separate voltage supplies |

| JP2008103028A (ja) * | 2006-10-19 | 2008-05-01 | Matsushita Electric Ind Co Ltd | 半導体記憶装置 |

| JP5057757B2 (ja) | 2006-11-30 | 2012-10-24 | 株式会社東芝 | 半導体集積回路 |

| JP5057430B2 (ja) * | 2006-12-18 | 2012-10-24 | ルネサスエレクトロニクス株式会社 | 半導体集積回路とその製造方法 |

| EP1953762B1 (en) * | 2007-01-25 | 2013-09-18 | Imec | Memory device with reduced standby power consumption and method for operating same |

| US8705300B1 (en) * | 2007-02-27 | 2014-04-22 | Altera Corporation | Memory array circuitry with stability enhancement features |

| US7616509B2 (en) * | 2007-07-13 | 2009-11-10 | Freescale Semiconductor, Inc. | Dynamic voltage adjustment for memory |

| US8099688B2 (en) * | 2007-11-19 | 2012-01-17 | International Business Machines Corporation | Circuit design |

| US7864600B2 (en) * | 2008-06-19 | 2011-01-04 | Texas Instruments Incorporated | Memory cell employing reduced voltage |

| US8379466B2 (en) | 2009-03-31 | 2013-02-19 | Freescale Semiconductor, Inc. | Integrated circuit having an embedded memory and method for testing the memory |

| US8315117B2 (en) * | 2009-03-31 | 2012-11-20 | Freescale Semiconductor, Inc. | Integrated circuit memory having assisted access and method therefor |

| US8634263B2 (en) * | 2009-04-30 | 2014-01-21 | Freescale Semiconductor, Inc. | Integrated circuit having memory repair information storage and method therefor |

| WO2010143707A1 (ja) * | 2009-06-12 | 2010-12-16 | 国立大学法人東京大学 | ラッチ回路の電圧特性調整方法および半導体装置の電圧特性調整方法並びにラッチ回路の電圧特性調整器 |

| JP2011054255A (ja) * | 2009-09-04 | 2011-03-17 | Panasonic Corp | 半導体集積回路 |

| JP5395009B2 (ja) * | 2010-07-30 | 2014-01-22 | 株式会社半導体理工学研究センター | サブスレッショルドsramのための電源電圧制御回路及び制御方法 |

| US8811068B1 (en) | 2011-05-13 | 2014-08-19 | Suvolta, Inc. | Integrated circuit devices and methods |

| US8467233B2 (en) * | 2011-06-06 | 2013-06-18 | Texas Instruments Incorporated | Asymmetric static random access memory cell with dual stress liner |

| US8819603B1 (en) | 2011-12-15 | 2014-08-26 | Suvolta, Inc. | Memory circuits and methods of making and designing the same |

| KR102275497B1 (ko) | 2014-10-20 | 2021-07-09 | 삼성전자주식회사 | 전원 경로 제어기를 포함하는 시스템 온 칩 및 전자 기기 |

| JP2018010707A (ja) * | 2016-07-12 | 2018-01-18 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP7195133B2 (ja) * | 2018-12-19 | 2022-12-23 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| CN109785884A (zh) * | 2019-01-15 | 2019-05-21 | 上海华虹宏力半导体制造有限公司 | 静态随机存取存储器存储单元 |

| JP2020149746A (ja) * | 2019-03-14 | 2020-09-17 | キオクシア株式会社 | 半導体記憶装置 |

| TWI764759B (zh) * | 2021-06-11 | 2022-05-11 | 円星科技股份有限公司 | 具備可靠容限設定的電路模組 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5197033A (en) * | 1986-07-18 | 1993-03-23 | Hitachi, Ltd. | Semiconductor device incorporating internal power supply for compensating for deviation in operating condition and fabrication process conditions |

| JPS62289994A (ja) | 1986-06-06 | 1987-12-16 | Nec Corp | 半導体メモリ装置 |

| EP0320556B1 (en) * | 1987-12-15 | 1991-02-27 | International Business Machines Corporation | Improved reference voltage generator for cmos memories |

| JPH06103748A (ja) * | 1992-09-16 | 1994-04-15 | Mitsubishi Electric Corp | Icメモリカードの電源制御回路 |

| JPH06139779A (ja) | 1992-10-29 | 1994-05-20 | Toshiba Corp | 基板バイアス回路 |

| US5394077A (en) * | 1993-04-30 | 1995-02-28 | Kabushiki Kaisha Toshiba | Internal power supply circuit for use in a semiconductor device |

| US5493231A (en) * | 1994-10-07 | 1996-02-20 | University Of North Carolina | Method and apparatus for measuring the barrier height distribution in an insulated gate field effect transistor |

| JP3135859B2 (ja) * | 1997-04-11 | 2001-02-19 | 株式会社リコー | 基板バイアス回路 |

| JP3853513B2 (ja) * | 1998-04-09 | 2006-12-06 | エルピーダメモリ株式会社 | ダイナミック型ram |

| JP4587500B2 (ja) * | 1998-11-11 | 2010-11-24 | ルネサスエレクトロニクス株式会社 | 半導体集積回路、メモリモジュール、記憶媒体、及び半導体集積回路の救済方法 |

| JP4392894B2 (ja) | 1999-03-12 | 2010-01-06 | Okiセミコンダクタ株式会社 | 半導体記憶装置 |

| JP2001093275A (ja) * | 1999-09-20 | 2001-04-06 | Mitsubishi Electric Corp | 半導体集積回路装置 |

| US6683805B2 (en) * | 2002-02-05 | 2004-01-27 | Ibm Corporation | Suppression of leakage currents in VLSI logic and memory circuits |

| US6493257B1 (en) * | 2002-03-27 | 2002-12-10 | International Business Machines Corporation | CMOS state saving latch |

| JP4162076B2 (ja) * | 2002-05-30 | 2008-10-08 | 株式会社ルネサステクノロジ | 半導体記憶装置 |

-

2002

- 2002-05-30 JP JP2002156646A patent/JP4162076B2/ja not_active Expired - Lifetime

-

2003

- 2003-05-28 US US10/445,919 patent/US6862227B2/en not_active Expired - Lifetime

-

2005

- 2005-02-03 US US11/049,243 patent/US6954396B2/en not_active Expired - Lifetime

- 2005-08-16 US US11/204,024 patent/US7333385B2/en not_active Expired - Lifetime

-

2008

- 2008-01-04 US US12/003,970 patent/US7920438B2/en not_active Expired - Lifetime

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9595307B2 (en) | 2014-05-22 | 2017-03-14 | Samsung Electronics Co., Ltd. | Volatile memory device and system-on-chip including the same |

| US10236056B2 (en) | 2014-05-22 | 2019-03-19 | Samsung Electronics Co., Ltd. | Volatile memory device and system-on-chip including the same |

Also Published As

| Publication number | Publication date |

|---|---|

| US20080117692A1 (en) | 2008-05-22 |

| US6862227B2 (en) | 2005-03-01 |

| US20030223276A1 (en) | 2003-12-04 |

| US6954396B2 (en) | 2005-10-11 |

| US7333385B2 (en) | 2008-02-19 |

| US7920438B2 (en) | 2011-04-05 |

| US20060034143A1 (en) | 2006-02-16 |

| US20050141289A1 (en) | 2005-06-30 |

| JP2004005777A (ja) | 2004-01-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4162076B2 (ja) | 半導体記憶装置 | |

| JP4768437B2 (ja) | 半導体記憶装置 | |

| US6108246A (en) | Semiconductor memory device | |

| US7233531B2 (en) | SRAM cell with horizontal merged devices | |

| US7564725B2 (en) | SRAM bias for read and write | |

| US7436732B2 (en) | Internal power supply generating circuit without a dead band | |

| US7642843B2 (en) | Reference voltage generating circuit and semiconductor integrated circuit device | |

| US20040022115A1 (en) | Semiconductor memory device with improved test mode | |

| US7907456B2 (en) | Memory having circuitry controlling the voltage differential between the word line and array supply voltage | |

| US7266010B2 (en) | Compact static memory cell with non-volatile storage capability | |

| JP2000149547A (ja) | 半導体記憶装置 | |

| JP2007066463A (ja) | 半導体装置 | |

| US7619947B2 (en) | Integrated circuit having a supply voltage controller capable of floating a variable supply voltage | |

| US10679714B2 (en) | ROM cell with transistor body bias control circuit | |

| JP4455562B2 (ja) | 半導体装置 | |

| US6611468B2 (en) | Non-volatile semiconductor memory device having sensitive sense amplifier structure | |

| US8264897B2 (en) | SRAM and method for accessing SRAM | |

| JPH10144879A (ja) | ワード線ドライバ回路及び半導体記憶装置 | |

| JP2009193666A (ja) | 半導体装置 | |

| CN111341364A (zh) | 半导体器件 | |

| JPH10302468A (ja) | 半導体記憶装置 | |

| JP2001093993A (ja) | 半導体装置 | |

| JPH07201199A (ja) | 半導体集積回路 | |

| JPH10302464A (ja) | 半導体集積回路とその電源電圧降圧回路 | |

| KR100861302B1 (ko) | 칼럼 선택 드라이버의 동작전압 공급 장치 및 그 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050526 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050526 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20050526 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080404 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080416 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080614 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080716 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080716 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110801 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4162076 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110801 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110801 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120801 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120801 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130801 Year of fee payment: 5 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| EXPY | Cancellation because of completion of term |