JP4769429B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP4769429B2 JP4769429B2 JP2004155881A JP2004155881A JP4769429B2 JP 4769429 B2 JP4769429 B2 JP 4769429B2 JP 2004155881 A JP2004155881 A JP 2004155881A JP 2004155881 A JP2004155881 A JP 2004155881A JP 4769429 B2 JP4769429 B2 JP 4769429B2

- Authority

- JP

- Japan

- Prior art keywords

- wafer

- manufacturing

- semiconductor device

- semiconductor wafer

- tape

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B23—MACHINE TOOLS; METAL-WORKING NOT OTHERWISE PROVIDED FOR

- B23K—SOLDERING OR UNSOLDERING; WELDING; CLADDING OR PLATING BY SOLDERING OR WELDING; CUTTING BY APPLYING HEAT LOCALLY, e.g. FLAME CUTTING; WORKING BY LASER BEAM

- B23K26/00—Working by laser beam, e.g. welding, cutting or boring

- B23K26/36—Removing material

- B23K26/40—Removing material taking account of the properties of the material involved

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B23—MACHINE TOOLS; METAL-WORKING NOT OTHERWISE PROVIDED FOR

- B23K—SOLDERING OR UNSOLDERING; WELDING; CLADDING OR PLATING BY SOLDERING OR WELDING; CUTTING BY APPLYING HEAT LOCALLY, e.g. FLAME CUTTING; WORKING BY LASER BEAM

- B23K26/00—Working by laser beam, e.g. welding, cutting or boring

- B23K26/50—Working by transmitting the laser beam through or within the workpiece

- B23K26/53—Working by transmitting the laser beam through or within the workpiece for modifying or reforming the material inside the workpiece, e.g. for producing break initiation cracks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/683—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L21/6835—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support

- H01L21/6836—Wafer tapes, e.g. grinding or dicing support tapes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/544—Marks applied to semiconductor devices or parts, e.g. registration marks, alignment structures, wafer maps

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B23—MACHINE TOOLS; METAL-WORKING NOT OTHERWISE PROVIDED FOR

- B23K—SOLDERING OR UNSOLDERING; WELDING; CLADDING OR PLATING BY SOLDERING OR WELDING; CUTTING BY APPLYING HEAT LOCALLY, e.g. FLAME CUTTING; WORKING BY LASER BEAM

- B23K2103/00—Materials to be soldered, welded or cut

- B23K2103/16—Composite materials, e.g. fibre reinforced

- B23K2103/166—Multilayered materials

- B23K2103/172—Multilayered materials wherein at least one of the layers is non-metallic

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B23—MACHINE TOOLS; METAL-WORKING NOT OTHERWISE PROVIDED FOR

- B23K—SOLDERING OR UNSOLDERING; WELDING; CLADDING OR PLATING BY SOLDERING OR WELDING; CUTTING BY APPLYING HEAT LOCALLY, e.g. FLAME CUTTING; WORKING BY LASER BEAM

- B23K2103/00—Materials to be soldered, welded or cut

- B23K2103/50—Inorganic material, e.g. metals, not provided for in B23K2103/02 – B23K2103/26

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L22/00—Testing or measuring during manufacture or treatment; Reliability measurements, i.e. testing of parts without further processing to modify the parts as such; Structural arrangements therefor

- H01L22/30—Structural arrangements specially adapted for testing or measuring during manufacture or treatment, or specially adapted for reliability measurements

- H01L22/34—Circuits for electrically characterising or monitoring manufacturing processes, e. g. whole test die, wafers filled with test structures, on-board-devices incorporated on each die, process control monitors or pad structures thereof, devices in scribe line

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2221/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof covered by H01L21/00

- H01L2221/67—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere

- H01L2221/683—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L2221/68304—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support

- H01L2221/68327—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support used during dicing or grinding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2221/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof covered by H01L21/00

- H01L2221/67—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere

- H01L2221/683—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L2221/68304—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support

- H01L2221/68327—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support used during dicing or grinding

- H01L2221/68336—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support used during dicing or grinding involving stretching of the auxiliary support post dicing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2221/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof covered by H01L21/00

- H01L2221/67—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere

- H01L2221/683—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L2221/68304—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support

- H01L2221/6834—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support used to protect an active side of a device or wafer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2221/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof covered by H01L21/00

- H01L2221/67—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere

- H01L2221/683—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L2221/68304—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support

- H01L2221/68381—Details of chemical or physical process used for separating the auxiliary support from a device or wafer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2223/00—Details relating to semiconductor or other solid state devices covered by the group H01L23/00

- H01L2223/544—Marks applied to semiconductor devices or parts

- H01L2223/5442—Marks applied to semiconductor devices or parts comprising non digital, non alphanumeric information, e.g. symbols

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2223/00—Details relating to semiconductor or other solid state devices covered by the group H01L23/00

- H01L2223/544—Marks applied to semiconductor devices or parts

- H01L2223/54426—Marks applied to semiconductor devices or parts for alignment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2223/00—Details relating to semiconductor or other solid state devices covered by the group H01L23/00

- H01L2223/544—Marks applied to semiconductor devices or parts

- H01L2223/54453—Marks applied to semiconductor devices or parts for use prior to dicing

- H01L2223/5446—Located in scribe lines

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0555—Shape

- H01L2224/05552—Shape in top view

- H01L2224/05554—Shape in top view being square

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32135—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/32145—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32245—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48245—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

- H01L2224/48247—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73253—Bump and layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/8319—Arrangement of the layer connectors prior to mounting

- H01L2224/83192—Arrangement of the layer connectors prior to mounting wherein the layer connectors are disposed only on another item or body to be connected to the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/91—Methods for connecting semiconductor or solid state bodies including different methods provided for in two or more of groups H01L2224/80 - H01L2224/90

- H01L2224/92—Specific sequence of method steps

- H01L2224/922—Connecting different surfaces of the semiconductor or solid-state body with connectors of different types

- H01L2224/9222—Sequential connecting processes

- H01L2224/92242—Sequential connecting processes the first connecting process involving a layer connector

- H01L2224/92247—Sequential connecting processes the first connecting process involving a layer connector the second connecting process involving a wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/94—Batch processes at wafer-level, i.e. with connecting carried out on a wafer comprising a plurality of undiced individual devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/73—Means for bonding being of different types provided for in two or more of groups H01L24/10, H01L24/18, H01L24/26, H01L24/34, H01L24/42, H01L24/50, H01L24/63, H01L24/71

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Optics & Photonics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Plasma & Fusion (AREA)

- Mechanical Engineering (AREA)

- Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Oil, Petroleum & Natural Gas (AREA)

- Laser Beam Processing (AREA)

- Dicing (AREA)

Description

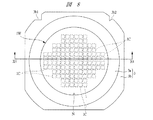

本実施の形態1の半導体装置の製造方法を図1のフロー図に沿って図2〜図31により説明する。

図33は本実施の形態2の半導体装置の製造工程中のウエハ1Wの切断領域CRの拡大平面図を示している。本実施の形態2では、パッド1LBtおよび前記アライメントターゲットAm(以下、パッド1LBt等という)の中心線がステルスダイシング時のレーザ光LBが照射される切断線CLからずれて配置されている。図33では、パッド1BLtが切断線CLを跨がずに切断線CLの上下に互いに斜め方向の位置になるように配置されている。なお、パッド1LBtと電気的に接続されるTEG用の素子や配線1L1も切断線CLを跨がないように上下に分離されて配置されている。

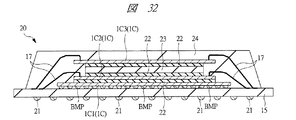

本実施の形態3では、チップ1Cの裏面にダイアタッチフィルム22を設ける場合について説明する。

本実施の形態4では、一般的な後工程への適用例を図38の半導体装置の製造装置のフロー図に沿って説明する。

1C 半導体チップ

1S 半導体基板

1L 配線層

1Li 層間絶縁膜

1L1,1L2 配線

1LB ボンディングパッド

1LBt テスト用のボンディングパッド(金属パターン)

1Lp 保護膜

2 開口部

3 治具

3a テープ

3a1 テープベース

3a2 接着層

3b リング(枠体)

3b1,3b2 切り欠き部

4 吸着ステージ

5a レーザ変位計

5b 赤外線カメラ

6 研削研磨工具

7 吸着ステージ

9 レーザ発生部

10 載置台

11 押上ピン

12 コレット

13 多突起吸着駒

15 プリント配線基板

16 接着材

17 ボンディングワイヤ

20 半導体装置

21 バンプ電極

22 ダイアタッチフィルム

23 スペーサ

24 封止体

27 治具

27a テープ

27a1 テープベース

27a2 接着層

27b リング

N ノッチ

Am アライメントターゲット(金属パターン)

S 溝

LB レーザ光(エネルギービーム)

PL 改質層

Claims (9)

- 以下の工程を含むことを特徴とする半導体装置の製造方法:

(a)複数のチップ領域と、前記複数のチップ領域のうちの互いに隣り合うチップ領域間に設けられた切断領域とを備えた半導体ウエハを準備する工程;

(b)前記(a)工程の後、前記半導体ウエハにテープを貼り付ける工程;

(c)前記(b)工程の後、前記半導体ウエハの前記切断領域に形成された金属パターンを認識する工程;

(d)前記(c)工程の後、前記半導体ウエハの内部に集光点を合わせ、前記切断領域にレーザを照射し、前記切断領域における前記半導体ウエハの前記内部に改質層を形成する工程;

(e)前記(d)工程の後、前記テープを引き伸ばすことにより、前記改質層を起点として前記半導体ウエハを分割する工程;

ここで、

前記(d)工程では、平面視において前記金属パターンと重ならないように、前記切断領域に沿ってレーザを照射し、平面視において前記金属パターンと重ならない位置に前記改質層を形成する。 - 請求項1記載の半導体装置の製造方法において、

前記半導体ウエハは、主面と、前記主面とは反対側の裏面とを有し、

前記(b)工程の後、かつ、前記(c)工程の前に、前記テープに前記半導体ウエハの前記主面を貼り付けた状態で、前記半導体ウエハの前記裏面を研削する工程を有することを特徴とする半導体装置の製造方法。 - 請求項2記載の半導体装置の製造方法において、

前記半導体ウエハを研削した後に、前記半導体ウエハを研磨することを特徴とする半導体装置の製造方法。 - 請求項3記載の半導体装置の製造方法において、

前記半導体ウエハを研磨した後の前記半導体ウエハの厚さは、100μmまたは100μmより薄いことを特徴とする半導体装置の製造方法。 - 請求項3記載の半導体装置の製造方法において、

前記研磨する工程は、研磨パッドを用いて行われることを特徴とする半導体装置の製造方法。 - 請求項3記載の半導体装置の製造方法において、

前記研磨する工程は、エッチング法により行われることを特徴とする半導体装置の製造方法。 - 請求項1記載の半導体装置の製造方法において、

前記金属パターンは、前記切断領域の幅方向において、中心からずれて配置されていることを特徴とする半導体装置の製造方法。 - 請求項1記載の半導体装置の製造方法において、

前記テープには、枠体が貼り付けられており、

前記(b)工程では、平面視において前記枠体の内側に前記半導体ウエハが位置するように、前記半導体ウエハに前記テープを貼り付けることを特徴とする半導体装置の製造方法。 - 請求項8記載の半導体装置の製造方法において、

前記半導体ウエハの主面は、前記テープの主面に形成された接着層を介して貼り付けられていることを特徴とする半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004155881A JP4769429B2 (ja) | 2004-05-26 | 2004-05-26 | 半導体装置の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004155881A JP4769429B2 (ja) | 2004-05-26 | 2004-05-26 | 半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005340423A JP2005340423A (ja) | 2005-12-08 |

| JP2005340423A5 JP2005340423A5 (ja) | 2007-07-05 |

| JP4769429B2 true JP4769429B2 (ja) | 2011-09-07 |

Family

ID=35493652

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004155881A Expired - Fee Related JP4769429B2 (ja) | 2004-05-26 | 2004-05-26 | 半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4769429B2 (ja) |

Families Citing this family (31)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4833657B2 (ja) * | 2005-12-19 | 2011-12-07 | 株式会社ディスコ | ウエーハの分割方法 |

| JP2007207871A (ja) * | 2006-01-31 | 2007-08-16 | Denso Corp | 複数の半導体装置を備えた半導体ウェハ |

| JP2007250598A (ja) * | 2006-03-14 | 2007-09-27 | Renesas Technology Corp | 半導体装置の製造方法 |

| JP4480728B2 (ja) | 2006-06-09 | 2010-06-16 | パナソニック株式会社 | Memsマイクの製造方法 |

| JP4910746B2 (ja) * | 2007-02-13 | 2012-04-04 | セイコーエプソン株式会社 | 基材の分割方法、及び液滴吐出ヘッドの製造方法。 |

| JP4835583B2 (ja) * | 2007-11-26 | 2011-12-14 | パナソニック株式会社 | ダイアタッチフィルム付きの半導体装置の製造方法 |

| JP5163358B2 (ja) * | 2008-03-26 | 2013-03-13 | 日立化成株式会社 | 半導体ウエハのダイシング方法 |

| JP5217557B2 (ja) * | 2008-03-27 | 2013-06-19 | パナソニック株式会社 | 電子部品の製造方法 |

| US8017942B2 (en) | 2008-11-25 | 2011-09-13 | Infineon Technologies Ag | Semiconductor device and method |

| JP2010177277A (ja) * | 2009-01-27 | 2010-08-12 | Tokyo Seimitsu Co Ltd | レーザーダイシング方法及びレーザーダイシング装置 |

| JP5401301B2 (ja) | 2009-12-28 | 2014-01-29 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法及び半導体装置 |

| JP2012089709A (ja) * | 2010-10-20 | 2012-05-10 | Disco Abrasive Syst Ltd | ワークの分割方法 |

| JP2012134333A (ja) * | 2010-12-22 | 2012-07-12 | Disco Abrasive Syst Ltd | 測定方法 |

| US8809120B2 (en) | 2011-02-17 | 2014-08-19 | Infineon Technologies Ag | Method of dicing a wafer |

| JP2012070004A (ja) * | 2011-12-21 | 2012-04-05 | Mitsumi Electric Co Ltd | 半導体装置の製造方法 |

| US9040389B2 (en) | 2012-10-09 | 2015-05-26 | Infineon Technologies Ag | Singulation processes |

| JP2015056605A (ja) | 2013-09-13 | 2015-03-23 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| JP5770245B2 (ja) * | 2013-10-28 | 2015-08-26 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP5906265B2 (ja) * | 2014-03-03 | 2016-04-20 | 株式会社ディスコ | ウエーハの分割方法 |

| JP6633446B2 (ja) * | 2016-04-27 | 2020-01-22 | 株式会社ディスコ | ウエーハの加工方法 |

| JP6633447B2 (ja) * | 2016-04-27 | 2020-01-22 | 株式会社ディスコ | ウエーハの加工方法 |

| JP2018074083A (ja) * | 2016-11-02 | 2018-05-10 | 株式会社ディスコ | ウエーハの加工方法 |

| KR102399356B1 (ko) * | 2017-03-10 | 2022-05-19 | 삼성전자주식회사 | 기판, 기판의 쏘잉 방법, 및 반도체 소자 |

| JP6888809B2 (ja) * | 2017-03-30 | 2021-06-16 | 三星ダイヤモンド工業株式会社 | 金属膜付き脆性材料基板の分断方法並びに分断装置 |

| JP6903532B2 (ja) * | 2017-09-20 | 2021-07-14 | キオクシア株式会社 | 半導体装置およびその製造方法 |

| JP7049941B2 (ja) * | 2018-06-22 | 2022-04-07 | 株式会社ディスコ | ウエーハの加工方法 |

| JP7401183B2 (ja) * | 2018-08-07 | 2023-12-19 | 株式会社ディスコ | ウェーハの加工方法 |

| KR102653165B1 (ko) | 2018-11-22 | 2024-04-01 | 삼성전자주식회사 | 반도체 장치, 반도체 칩 및 반도체 기판의 반도체 기판의 소잉 방법 |

| US11031308B2 (en) * | 2019-05-30 | 2021-06-08 | Sandisk Technologies Llc | Connectivity detection for wafer-to-wafer alignment and bonding |

| JP7459490B2 (ja) * | 2019-11-28 | 2024-04-02 | 株式会社ソシオネクスト | 半導体ウェハ及び半導体装置 |

| CN113972143A (zh) * | 2021-10-18 | 2022-01-25 | 长鑫存储技术有限公司 | 半导体结构的键合方法和半导体设备 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000216123A (ja) * | 1999-01-22 | 2000-08-04 | Okamoto Machine Tool Works Ltd | ウエハの裏面研削およびダイシング方法 |

| JP3368876B2 (ja) * | 1999-11-05 | 2003-01-20 | 株式会社東京精密 | 半導体チップ製造方法 |

| JP3339485B2 (ja) * | 2000-01-24 | 2002-10-28 | 日本電気株式会社 | 半導体装置 |

| JP2002093750A (ja) * | 2000-09-13 | 2002-03-29 | Toshiba Microelectronics Corp | 半導体装置 |

| JP3624909B2 (ja) * | 2002-03-12 | 2005-03-02 | 浜松ホトニクス株式会社 | レーザ加工方法 |

| JP2004079746A (ja) * | 2002-08-16 | 2004-03-11 | Tokyo Seimitsu Co Ltd | チップ製造方法 |

| JP2004111601A (ja) * | 2002-09-18 | 2004-04-08 | Tokyo Seimitsu Co Ltd | ダイボンダ |

| JP3825753B2 (ja) * | 2003-01-14 | 2006-09-27 | 株式会社東芝 | 半導体装置の製造方法 |

-

2004

- 2004-05-26 JP JP2004155881A patent/JP4769429B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005340423A (ja) | 2005-12-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4769429B2 (ja) | 半導体装置の製造方法 | |

| CN101297394B (zh) | 半导体器件的制造方法以及半导体器件 | |

| JP2005332982A (ja) | 半導体装置の製造方法 | |

| JP5608521B2 (ja) | 半導体ウエハの分割方法と半導体チップ及び半導体装置 | |

| JP3831287B2 (ja) | 半導体装置の製造方法 | |

| US6841454B2 (en) | Chip-like electronic components, a method of manufacturing the same, a pseudo wafer therefor and a method of manufacturing thereof | |

| JP2007048958A (ja) | 半導体装置の製造方法および半導体装置 | |

| US7285864B2 (en) | Stack MCP | |

| US20070275543A1 (en) | Manufacturing method of a semiconductor device | |

| US9059225B2 (en) | Semiconductor device and the method of manufacturing the same | |

| JP4848153B2 (ja) | 半導体装置の製造方法 | |

| JP5352624B2 (ja) | 半導体装置の製造方法 | |

| JP5798834B2 (ja) | 半導体装置の製造方法 | |

| KR20040036654A (ko) | 반도체 장치의 제조 방법 | |

| JP2011181822A (ja) | 半導体装置の製造方法 | |

| US10490531B2 (en) | Manufacturing method of semiconductor device and semiconductor device | |

| JP2013080972A (ja) | 半導体装置の製造方法 | |

| TWI381485B (zh) | Semiconductor device manufacturing method and semiconductor device | |

| JP2014146829A (ja) | 半導体チップおよび半導体装置 | |

| JP2005340431A (ja) | 半導体装置の製造方法 | |

| JP2020136650A (ja) | チップ転写板ならびに半導体チップ積層方法および半導体装置の製造方法 | |

| WO2021084902A1 (ja) | チップ付き基板の製造方法、及び基板処理装置 | |

| JP5297491B2 (ja) | 半導体装置 | |

| WO2007049356A1 (ja) | 半導体装置およびその製造方法 | |

| JP2007266421A (ja) | 半導体装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070522 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070522 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100121 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100528 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100831 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101101 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110531 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110620 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140624 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |